Welcome to **E-XFL.COM**

Understanding <u>Embedded - CPLDs (Complex Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                              |

|---------------------------------|------------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                     |

| Programmable Type               | In System Programmable                                                       |

| Delay Time tpd(1) Max           | 4.7 ns                                                                       |

| Voltage Supply - Internal       | 1.7V ~ 1.9V                                                                  |

| Number of Logic Elements/Blocks | 4                                                                            |

| Number of Macrocells            | 64                                                                           |

| Number of Gates                 | -                                                                            |

| Number of I/O                   | 64                                                                           |

| Operating Temperature           | 0°C ~ 90°C (TJ)                                                              |

| Mounting Type                   | Surface Mount                                                                |

| Package / Case                  | 100-LQFP                                                                     |

| Supplier Device Package         | 100-TQFP (14x14)                                                             |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc4064ze-4tcn100c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Introduction

The high performance ispMACH 4000ZE family from Lattice offers an ultra low power CPLD solution. The new family is based on Lattice's industry-leading ispMACH 4000 architecture. Retaining the best of the previous generation, the ispMACH 4000ZE architecture focuses on significant innovations to combine high performance with low power in a flexible CPLD family. For example, the family's new Power Guard feature minimizes dynamic power consumption by preventing internal logic toggling due to unnecessary I/O pin activity.

The ispMACH 4000ZE combines high speed and low power with the flexibility needed for ease of design. With its robust Global Routing Pool and Output Routing Pool, this family delivers excellent First-Time-Fit, timing predictability, routing, pin-out retention and density migration.

The ispMACH 4000ZE family offers densities ranging from 32 to 256 macrocells. There are multiple density-I/O combinations in Thin Quad Flat Pack (TQFP), Chip Scale BGA (csBGA), and Ultra Chip Scale BGA (ucBGA) packages ranging from 32 to 144 pins/balls. Table 1 shows the macrocell, package and I/O options, along with other key parameters.

A user programmable internal oscillator and a timer are included in the device for tasks like LED control, keyboard scanner and similar housekeeping type state machines. This feature can be optionally disabled to save power.

The ispMACH 4000ZE family has enhanced system integration capabilities. It supports a 1.8V supply voltage and 3.3V, 2.5V, 1.8V and 1.5V interface voltages. Additionally, inputs can be safely driven up to 5.5V when an I/O bank is configured for 3.3V operation, making this family 5V tolerant. The ispMACH 4000ZE also offers enhanced I/O features such as slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis. The ispMACH 4000ZE family members are 1.8V in-system programmable through the IEEE Standard 1532 interface. IEEE Standard 1149.1 boundary scan testing capability also allows product testing on automated test equipment. The 1532 interface signals TCK, TMS, TDI and TDO are referenced to V<sub>CC</sub> (logic core).

#### **Overview**

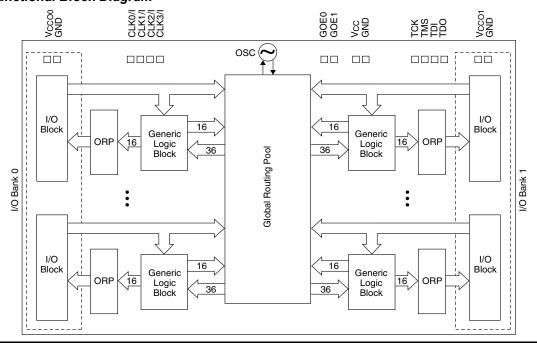

The ispMACH 4000ZE devices consist of multiple 36-input, 16-macrocell Generic Logic Blocks (GLBs) interconnected by a Global Routing Pool (GRP). Output Routing Pools (ORPs) connect the GLBs to the I/O Blocks (IOBs), which contain multiple I/O cells. This architecture is shown in Figure 1.

Figure 1. Functional Block Diagram

The I/Os in the ispMACH 4000ZE are split into two banks. Each bank has a separate I/O power supply. Inputs can support a variety of standards independent of the chip or bank power supply. Outputs support the standards compatible with the power supply provided to the bank. Support for a variety of standards helps designers implement designs in mixed voltage environments. In addition, 5V tolerant inputs are specified within an I/O bank that is connected to a  $V_{CCO}$  of 3.0V to 3.6V for LVCMOS 3.3, LVTTL and PCI interfaces.

#### **Architecture**

There are a total of two GLBs in the ispMACH 4032ZE, increasing to 16 GLBs in the ispMACH 4256ZE. Each GLB has 36 inputs. All GLB inputs come from the GRP and all outputs from the GLB are brought back into the GRP to be connected to the inputs of any other GLB on the device. Even if feedback signals return to the same GLB, they still must go through the GRP. This mechanism ensures that GLBs communicate with each other with consistent and predictable delays. The outputs from the GLB are also sent to the ORP. The ORP then sends them to the associated I/O cells in the I/O block.

#### **Generic Logic Block**

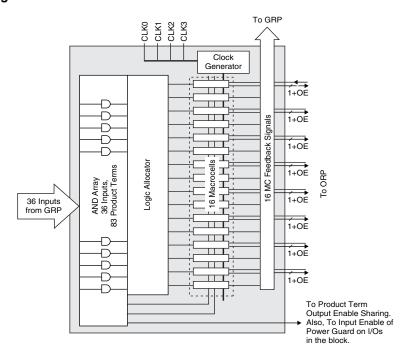

The ispMACH 4000ZE GLB consists of a programmable AND array, logic allocator, 16 macrocells and a GLB clock generator. Macrocells are decoupled from the product terms through the logic allocator and the I/O pins are decoupled from macrocells through the ORP. Figure 2 illustrates the GLB.

Figure 2. Generic Logic Block

#### **AND Array**

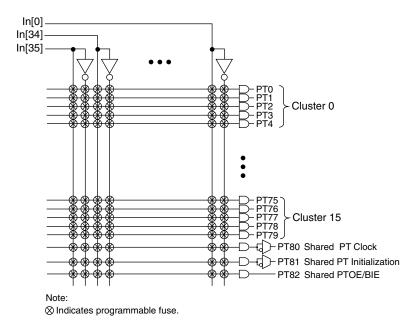

The programmable AND Array consists of 36 inputs and 83 output product terms. The 36 inputs from the GRP are used to form 72 lines in the AND Array (true and complement of the inputs). Each line in the array can be connected to any of the 83 output product terms via a wired-AND. Each of the 80 logic product terms feed the logic allocator with the remaining three control product terms feeding the Shared PT Clock, Shared PT Initialization and Shared PT OE. The Shared PT Clock and Shared PT Initialization signals can optionally be inverted before being fed to the macrocells.

Every set of five product terms from the 80 logic product terms forms a product term cluster starting with PT0. There is one product term cluster for every macrocell in the GLB. Figure 3 is a graphical representation of the AND Array.

Figure 3. AND Array

#### **Enhanced Logic Allocator**

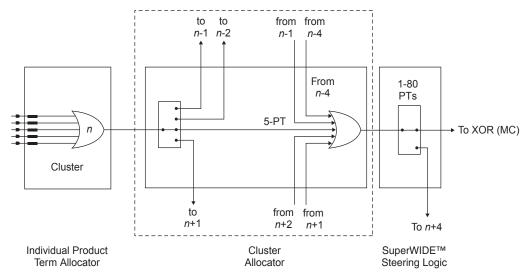

Within the logic allocator, product terms are allocated to macrocells in product term clusters. Each product term cluster is associated with a macrocell. The cluster size for the ispMACH 4000ZE family is 4+1 (total 5) product terms. The software automatically considers the availability and distribution of product term clusters as it fits the functions within a GLB. The logic allocator is designed to provide two speed paths: 20-PT Speed Locking path and an up to 80-PT path. The availability of these two paths lets designers trade timing variability for increased performance.

The enhanced Logic Allocator of the ispMACH 4000ZE family consists of the following blocks:

- Product Term Allocator

- Cluster Allocator

- Wide Steering Logic

Figure 4 shows a macrocell slice of the Logic Allocator. There are 16 such slices in the GLB.

Figure 4. Macrocell Slice

- Block CLK2

- Block CLK3

- PT Clock

- PT Clock Inverted

- Shared PT Clock

- Ground

### **Clock Enable Multiplexer**

Each macrocell has a 4:1 clock enable multiplexer. This allows the clock enable signal to be selected from the following four sources:

- PT Initialization/CE

- PT Initialization/CE Inverted

- Shared PT Clock

- Logic High

#### **Initialization Control**

The ispMACH 4000ZE family architecture accommodates both block-level and macrocell-level set and reset capability. There is one block-level initialization term that is distributed to all macrocell registers in a GLB. At the macrocell level, two product terms can be "stolen" from the cluster associated with a macrocell to be used for set/reset functionality. A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing flexibility.

Note that the reset/preset swapping selection feature affects power-up reset as well. All flip-flops power up to a known state for predictable system initialization. If a macrocell is configured to SET on a signal from the block-level initialization, then that macrocell will be SET during device power-up. If a macrocell is configured to RESET on a signal from the block-level initialization or is not configured for set/reset, then that macrocell will RESET on power-up. To guarantee initialization values, the  $V_{CC}$  rise must be monotonic, and the clock must be inactive until the reset delay time has elapsed.

#### **GLB Clock Generator**

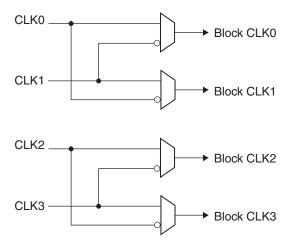

Each ispMACH 4000ZE device has up to four clock pins that are also routed to the GRP to be used as inputs. These pins drive a clock generator in each GLB, as shown in Figure 6. The clock generator provides four clock signals that can be used anywhere in the GLB. These four GLB clock signals can consist of a number of combinations of the true and complement edges of the global clock signals.

Figure 6. GLB Clock Generator

#### **Output Routing Pool (ORP)**

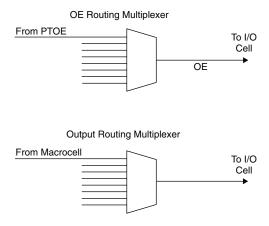

The Output Routing Pool allows macrocell outputs to be connected to any of several I/O cells within an I/O block. This provides greater flexibility in determining the pinout and allows design changes to occur without affecting the pinout. The output routing pool also provides a parallel capability for routing macrocell-level OE product terms. This allows the OE product term to follow the macrocell output as it is switched between I/O cells. The enhanced ORP of the ispMACH 4000ZE family consists of the following elements:

- Output Routing Multiplexers

- OE Routing Multiplexers

Figure 7 shows the structure of the ORP from the I/O cell perspective. This is referred to as an ORP slice. Each ORP has as many ORP slices as there are I/O cells in the corresponding I/O block.

Figure 7. ORP Slice

### **Output Routing Multiplexers**

The details of connections between the macrocells and the I/O cells vary across devices and within a device dependent on the maximum number of I/Os available. Tables 5-7 provide the connection details.

Table 5. GLB/MC/ORP Combinations for ispMACH 4256ZE

| GLB/MC       | ORP Mux Input Macrocells             |

|--------------|--------------------------------------|

| [GLB] [MC 0] | M0, M1, M2, M3, M4, M5, M6, M7       |

| [GLB] [MC 1] | M2, M3, M4, M5, M6, M7, M8, M9       |

| [GLB] [MC 2] | M4, M5, M6, M7, M8, M9, M10, M11     |

| [GLB] [MC 3] | M6, M7, M8, M9, M10, M11, M12, M13   |

| [GLB] [MC 4] | M8, M9, M10, M11, M12, M13, M14, M15 |

| [GLB] [MC 5] | M10, M11, M12, M13, M14, M15, M0, M1 |

| [GLB] [MC 6] | M12, M13, M14, M15, M0, M1, M2, M3   |

| [GLB] [MC 7] | M14, M15, M0, M1, M2, M3, M4, M5     |

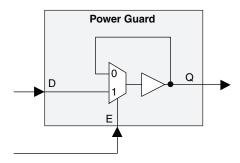

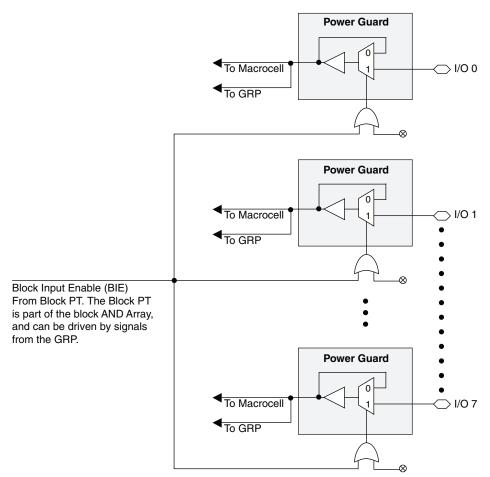

Figure 9. Power Guard

All the I/O pins in a block share a common Power Guard Enable signal. For a block of I/Os, this signal is called a Block Input Enable (BIE) signal. BIE can be internally generated using MC logic, or could come from external sources using one of the user I/O or input pins.

Any I/O pin in the block can be programmed to ignore the BIE signal. Thus, the feature can be enabled or disabled on a pin-by-pin basis.

Figure 10 shows Power Guard and BIE across multiple I/Os in a block that has eight I/Os.

Figure 10. Power Guard and BIE in a Block with 8 I/Os

### I/O Recommended Operating Conditions

|                     | V <sub>CCO</sub> (V) <sup>1</sup> |      |  |

|---------------------|-----------------------------------|------|--|

| Standard            | Min.                              | Max. |  |

| LVTTL               | 3.0                               | 3.6  |  |

| LVCMOS 3.3          | 3.0                               | 3.6  |  |

| Extended LVCMOS 3.3 | 2.7                               | 3.6  |  |

| LVCMOS 2.5          | 2.3                               | 2.7  |  |

| LVCMOS 1.8          | 1.65                              | 1.95 |  |

| LVCMOS 1.5          | 1.4                               | 1.6  |  |

| PCI 3.3             | 3.0                               | 3.6  |  |

<sup>1.</sup> Typical values for  $\ensuremath{V_{\text{CCO}}}$  are the average of the min. and max. values.

### **DC Electrical Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                            | Parameter                             | Condition                                        | Min.                    | Тур. | Max.                    | Units |

|---------------------------------------------------|---------------------------------------|--------------------------------------------------|-------------------------|------|-------------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 2</sup> | Input Leakage Current                 | $0 \le V_{IN} < V_{CCO}$                         | _                       | 0.5  | 1                       | μΑ    |

| I <sub>IH</sub> <sup>1</sup>                      | Input High Leakage Current            | $V_{CCO} < V_{IN} \le 5.5V$                      | _                       | _    | 10                      | μΑ    |

| I <sub>PU</sub>                                   | I/O Weak Pull-up Resistor Current     | $0 \le V_{IN} \le 0.7V_{CCO}$                    | -20                     |      | -150                    | μΑ    |

| I <sub>PD</sub>                                   | I/O Weak Pull-down Resistor Current   | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)   | 30                      | _    | 150                     | μΑ    |

| I <sub>BHLS</sub>                                 | Bus Hold Low Sustaining Current       | V <sub>IN</sub> = V <sub>IL</sub> (MAX)          | 30                      |      | _                       | μΑ    |

| I <sub>BHHS</sub>                                 | Bus Hold High Sustaining Current      | $V_{IN} = 0.7 V_{CCO}$                           | -20                     | _    | _                       | μΑ    |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive Current        | $0V \le V_{IN} \le V_{BHT}$                      | _                       | _    | 150                     | μΑ    |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive Current       | $V_{BHT} \le V_{IN} \le V_{CCO}$                 | _                       |      | -150                    | μΑ    |

| V <sub>BHT</sub>                                  | Bus Hold Trip Points                  | _                                                | V <sub>CCO</sub> * 0.35 | _    | V <sub>CCO</sub> * 0.65 | V     |

| C <sub>1</sub>                                    | I/O Capacitance <sup>3</sup>          | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V, 1.5V        | _                       | 8    | _                       | pf    |

| O <sub>1</sub>                                    | 1/O Capacitance                       | $V_{CC}$ = 1.8V, $V_{IO}$ = 0 to $V_{IH}$ (MAX)  | _                       | 0    | _                       | ρι    |

| C                                                 | Clock Capacitance <sup>3</sup>        | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V, 1.5V        | _                       | 6    | _                       | nf    |

| C <sub>2</sub>                                    | Опоск Сараспансе                      | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX) | _                       | O    | _                       | pf    |

| C-                                                | Global Input Capacitance <sup>3</sup> | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V, 1.5V        | _                       | 6    | _                       | nf    |

| C <sub>3</sub>                                    |                                       | $V_{CC} = 1.8V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX) | _                       | O    | _                       | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup> I<sub>IH</sub> excursions of up to 1.5μA maximum per pin above the spec limit may be observed for certain voltage conditions on no more than 10% of the device's I/O pins.

<sup>3.</sup> Measured  $T_A = 25$ °C, f = 1.0MHz.

### **Boundary Scan Waveforms and Timing Specifications**

| Symbol              | Parameter                                                      | Min. | Max. | Units |

|---------------------|----------------------------------------------------------------|------|------|-------|

| t <sub>BTCP</sub>   | TCK [BSCAN test] clock cycle                                   | 40   | _    | ns    |

| t <sub>BTCH</sub>   | TCK [BSCAN test] pulse width high                              | 20   | _    | ns    |

| t <sub>BTCL</sub>   | TCK [BSCAN test] pulse width low                               | 20   | _    | ns    |

| t <sub>BTSU</sub>   | TCK [BSCAN test] setup time                                    | 8    | _    | ns    |

| t <sub>BTH</sub>    | TCK [BSCAN test] hold time                                     | 10   | _    | ns    |

| t <sub>BRF</sub>    | TCK [BSCAN test] rise and fall time                            | 50   | _    | mV/ns |

| t <sub>BTCO</sub>   | TAP controller falling edge of clock to valid output           | _    | 10   | ns    |

| t <sub>BTOZ</sub>   | TAP controller falling edge of clock to data output disable    | _    | 10   | ns    |

| t <sub>BTVO</sub>   | TAP controller falling edge of clock to data output enable     | _    | 10   | ns    |

| t <sub>BTCPSU</sub> | BSCAN test Capture register setup time                         | 8    | _    | ns    |

| t <sub>BTCPH</sub>  | BSCAN test Capture register hold time                          | 10   | _    | ns    |

| t <sub>BTUCO</sub>  | BSCAN test Update reg, falling edge of clock to valid output   | _    | 25   | ns    |

| t <sub>BTUOZ</sub>  | BSCAN test Update reg, falling edge of clock to output disable | _    | 25   | ns    |

| t <sub>BTUOV</sub>  | BSCAN test Update reg, falling edge of clock to output enable  |      | 25   | ns    |

### **Switching Test Conditions**

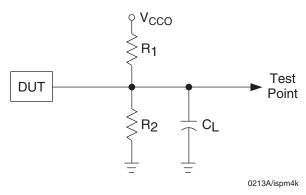

Figure 17 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 13.

Figure 17. Output Test Load, LVTTL and LVCMOS Standards

Table 13. Test Fixture Required Components

| Test Condition               | R <sub>1</sub> | R <sub>2</sub> | C <sub>L</sub> <sup>1</sup> | Timing Ref.                      | V <sub>cco</sub>   |

|------------------------------|----------------|----------------|-----------------------------|----------------------------------|--------------------|

|                              |                |                |                             | LVCMOS 3.3 = 1.5V                | LVCMOS 3.3 = 3.0V  |

|                              |                |                |                             | LVCMOS $2.5 = \frac{V_{CCO}}{2}$ | LVCMOS 2.5 = 2.3V  |

| LVCMOS I/O, (L -> H, H -> L) | 106Ω           | 106Ω           | 35pF                        | LVCMOS 1.8 = $\frac{V_{CCO}}{2}$ | LVCMOS 1.8 = 1.65V |

|                              |                |                |                             | LVCMOS 1.5 = $\frac{V_{CCO}}{2}$ | LVCMOS 1.5 = 1.4V  |

| LVCMOS I/O (Z -> H)          | ∞              | 106Ω           | 35pF                        | 1.5V                             | 3.0V               |

| LVCMOS I/O (Z -> L)          | 106Ω           | $\infty$       | 35pF                        | 1.5V                             | 3.0V               |

| LVCMOS I/O (H -> Z)          | ∞              | 106Ω           | 5pF                         | V <sub>OH</sub> - 0.3            | 3.0V               |

| LVCMOS I/O (L -> Z)          | 106Ω           | 8              | 5pF                         | V <sub>OL</sub> + 0.3            | 3.0V               |

<sup>1.</sup> C<sub>L</sub> includes test fixtures and probe capacitance.

### ispMACH 4000ZE Power Supply and NC Connections<sup>1</sup> (Cont.)

| Signal                 | 132 ucBGA³           | 144 csBGA³                                                                                                                                                                                                                                                        | 144 TQFP <sup>2</sup>                 |

|------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| VCC                    | M1, M7, A12, B5      | H5, H8, E8, E5                                                                                                                                                                                                                                                    | 36, 57, 108, 129                      |

| VCCO0<br>VCCO (Bank 0) | B1, H4, L2, J5, A4   | E4, F4, G4, J5, D5                                                                                                                                                                                                                                                | 3, 19, 34, 47, 136                    |

| VCCO1<br>VCCO (Bank 1) | K9, L12, F12, D9, C7 | J8, H9, G9, F9, D8                                                                                                                                                                                                                                                | 64, 75, 91, 106, 119                  |

| GND                    | E5, E8, H5, H8       | F6, G6, G7, F7                                                                                                                                                                                                                                                    | 1, 37, 73, 109                        |

| GND (Bank 0)           | E2, H2, M4, B7, B3   | G5, H4, H6, E6, F5                                                                                                                                                                                                                                                | 10, 184, 27, 46, 127, 137             |

| GND (Bank 1)           | L7, J9, H12, E9, A9  | H7, J9, G8, F8, E7                                                                                                                                                                                                                                                | 55, 65, 82, 90 <sup>4</sup> , 99, 118 |

| NC                     | _                    | 4064ZE: E4, B2, B1, D2, D3, E1, H1, H3, H2, L1, G4, M1, K3, M2, M4, L5, H7, L8, M8, L10, K9, M11, H9, L12, L11, J12, J11, H10, D10, F10, D12, B12, F9, A12, C10, B10, A9, B8, E6, B5, A5, C4, B3, A2 4128ZE: D2, D3, H2, M1, K3, M11, J12, J11, D12, A12, C10, A2 | ,                                     |

<sup>1.</sup> All grounds must be electrically connected at the board level. However, for the purposes of I/O current loading, grounds are associated with the bank shown.

<sup>2.</sup> Pin orientation follows the conventional order from pin 1 marking of the top side view and counter-clockwise.

<sup>3.</sup> Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

<sup>4.</sup> For the LC4256ZE, pins 18 and 90 are no connects.

### ispMACH 4032ZE and 4064ZE Logic Signal Connections: 64 csBGA

|             |             | ispMACH 4032ZE | ispMACH 4064ZE |

|-------------|-------------|----------------|----------------|

| Ball Number | Bank Number | GLB/MC/Pad     | GLB/MC/Pad     |

| B2          | -           | TDI            | TDI            |

| B1          | 0           | A5             | A8             |

| C2          | 0           | A6             | A10            |

| C1          | 0           | A7             | A11            |

| GND*        | 0           | GND (Bank 0)   | GND (Bank 0)   |

| C3          | 0           | NC             | A12            |

| E3          | 0           | VCCO (Bank 0)  | VCCO (Bank 0)  |

| D1          | 0           | A8             | B15            |

| D2          | 0           | NC             | B14            |

| E1          | 0           | A9             | B13            |

| D3          | 0           | A10            | B12            |

| F1          | 0           | A11            | B11            |

| E2          | 0           | NC             | B10            |

| G1          | 0           | NC             | B9             |

| F2          | 0           | NC             | B8             |

| H1          | -           | TCK            | TCK            |

| E4          | -           | VCC            | VCC            |

| GND*        | -           | GND            | GND            |

| G2          | 0           | A12            | B6             |

| H2          | 0           | NC             | B5             |

| H3          | 0           | A13            | B4             |

| GND*        | 0           | NC             | GND (Bank 0)   |

| F4          | 0           | NC             | VCCO (Bank 0)  |

| G3          | 0           | A14            | B3             |

| F3          | 0           | NC             | B2             |

| H4          | 0           | A15            | В0             |

| G4          | 0           | CLK1/I         | CLK1/I         |

| H5          | 1           | CLK2/I         | CLK2/I         |

| F5          | 1           | В0             | C0             |

| G5          | 1           | B1             | C1             |

| G6          | 1           | B2             | C2             |

| H6          | 1           | B3             | C4             |

| F6          | 1           | B4             | C5             |

| H7          | 1           | NC             | C6             |

| H8          | -           | TMS            | TMS            |

| G7          | 1           | B5             | C8             |

| F7          | 1           | B6             | C10            |

| G8          | 1           | B7             | C11            |

| GND*        | 1           | GND (Bank 0)   | GND (Bank 1)   |

| F8          | 1           | NC             | C12            |

| D6          | 1           | VCCO (Bank 1)  | VCCO (Bank 1)  |

| E8          | 1           | B8             | D15            |

### ispMACH 4032ZE and 4064ZE Logic Signal Connections: 64 csBGA (Cont.)

|             |             | ispMACH 4032ZE | ispMACH 4064ZE |

|-------------|-------------|----------------|----------------|

| Ball Number | Bank Number | GLB/MC/Pad     | GLB/MC/Pad     |

| E7          | 1           | NC             | D14            |

| E6          | 1           | B9             | D13            |

| D7          | 1           | B10            | D12            |

| D8          | 1           | NC             | D11            |

| C5          | 1           | NC             | D10            |

| C7          | 1           | B11            | D9             |

| C8          | 1           | NC             | D8             |

| B8          | -           | TDO            | TDO            |

| D5          | -           | VCC            | VCC            |

| GND*        | -           | GND            | GND            |

| A8          | 1           | B12            | D7             |

| A7          | 1           | NC             | D6             |

| B7          | 1           | NC             | D5             |

| A6          | 1           | B13            | D4             |

| GND*        | 1           | NC             | GND (Bank 1)   |

| C6          | 1           | NC             | VCCO (Bank 1)  |

| B6          | 1           | B14            | D3             |

| A5          | 1           | NC             | D2             |

| B5          | 1           | B15/GOE1       | D0/GOE1        |

| A4          | 1           | CLK3/I         | CLK3/I         |

| C4          | 0           | CLK0/I         | CLK0/I         |

| B4          | 0           | A0/GOE0        | A0/GOE0        |

| B3          | 0           | A1             | A1             |

| A3          | 0           | A2             | A2             |

| A2          | 0           | A3             | A4             |

| A1          | 0           | A4             | A6             |

<sup>\*</sup> All bonded grounds are connected to the following two balls, D4 and E5.

### ispMACH 4128ZE Logic Signal Connections: 132 ucBGA

| Ball Number | Bank Number | GLB/MC/Pad    |

|-------------|-------------|---------------|

| GND*        | -           | GND           |

| A1          | -           | TDI           |

| B1          | 0           | VCCO (Bank 0) |

| D3          | 0           | В0            |

| C1          | 0           | B1            |

| D2          | 0           | B2            |

| D1          | 0           | B4            |

| E4          | 0           | B5            |

| F3          | 0           | B6            |

| E2          | 0           | GND (Bank 0)  |

| E1          | 0           | B8            |

| E3          | 0           | В9            |

| F4          | 0           | B10           |

| G4          | 0           | B12           |

| F2          | 0           | B13           |

| G3          | 0           | B14           |

| H4          | 0           | VCCO (Bank 0) |

| F1          | 0           | C14           |

| G2          | 0           | C13           |

| G1          | 0           | C12           |

| H3          | 0           | C10           |

| J4          | 0           | C9            |

| H1          | 0           | C8            |

| H2          | 0           | GND (Bank 0)  |

| J3          | 0           | C6            |

| J1          | 0           | C5            |

| J2          | 0           | C4            |

| КЗ          | 0           | C2            |

| K2          | 0           | C1            |

| K1          | 0           | C0            |

| L2          | 0           | VCCO (Bank 0) |

| L1          | -           | TCK           |

| M1          | -           | VCC           |

| GND*        | -           | GND           |

| L3          | 0           | D14           |

| M2          | 0           | D13           |

| K4          | 0           | D12           |

| M3          | 0           | D10           |

| K5          | 0           | D9            |

| L4          | 0           | D8            |

| M4          | 0           | GND (Bank 0)  |

| J5          | 0           | VCCO (Bank 0) |

| L5          | 0           | D6            |

### ispMACH 4128ZE Logic Signal Connections: 132 ucBGA (Cont.)

| Ball Number | Bank Number | GLB/MC/Pad    |

|-------------|-------------|---------------|

| M5          | 0           | D5            |

| J6          | 0           | D4            |

| K6          | 0           | D2            |

| L6          | 0           | D1            |

| M6          | 0           | D0            |

| K7          | 0           | CLK1/I        |

| L7          | 1           | GND (Bank 1)  |

| J7          | 1           | CLK2/I        |

| M7          | -           | VCC           |

| K8          | 1           | E0            |

| L8          | 1           | E1            |

| M8          | 1           | E2            |

| J8          | 1           | E4            |

| L9          | 1           | E5            |

| M9          | 1           | E6            |

| K9          | 1           | VCCO (Bank 1) |

| J9          | 1           | GND (Bank 1)  |

| L10         | 1           | E8            |

| K10         | 1           | E9            |

| M10         | 1           | E10           |

| L11         | 1           | E12           |

| K12         | 1           | E13           |

| M11         | 1           | E14           |

| GND*        | -           | GND           |

| M12         | -           | TMS           |

| L12         | 1           | VCCO (Bank 1) |

| K11         | 1           | F0            |

| J10         | 1           | F1            |

| H9          | 1           | F2            |

| J12         | 1           | F4            |

| J11         | 1           | F5            |

| H10         | 1           | F6            |

| H12         | 1           | GND (Bank 1)  |

| G9          | 1           | F8            |

| H11         | 1           | F9            |

| F9          | 1           | F10           |

| G12         | 1           | F12           |

| G11         | 1           | F13           |

| G10         | 1           | F14           |

| F12         | 1           | VCCO (Bank 1) |

| F10         | 1           | G14           |

| F11         | 1           | G13           |

| E11         | 1           | G12           |

| E10         | 1           | G10           |

### ispMACH 4128ZE Logic Signal Connections: 132 ucBGA (Cont.)

| Ball Number | Bank Number | GLB/MC/Pad    |

|-------------|-------------|---------------|

| D10         | 1           | G9            |

| E12         | 1           | G8            |

| E9          | 1           | GND (Bank 1)  |

| D12         | 1           | G6            |

| D11         | 1           | G5            |

| C12         | 1           | G4            |

| C10         | 1           | G2            |

| C11         | 1           | G1            |

| B11         | 1           | G0            |

| D9          | 1           | VCCO (Bank 1) |

| B12         | -           | TDO           |

| A12         | -           | VCC           |

| GND*        | -           | GND           |

| A10         | 1           | H14           |

| A11         | 1           | H13           |

| B10         | 1           | H12           |

| C9          | 1           | H10           |

| D8          | 1           | H9            |

| C8          | 1           | H8            |

| A9          | 1           | GND (Bank 1)  |

| C7          | 1           | VCCO (Bank 1) |

| B9          | 1           | H6            |

| B8          | 1           | H5            |

| D7          | 1           | H4            |

| A8          | 1           | H2            |

| A7          | 1           | H1            |

| B6          | 1           | H0/GOE1       |

| C6          | 1           | CLK3/I        |

| B7          | 0           | GND (Bank 0)  |

| D6          | 0           | CLK0/I        |

| B5          | -           | VCC           |

| A6          | 0           | A0/GOE0       |

| C5          | 0           | A1            |

| B4          | 0           | A2            |

| A5          | 0           | A4            |

| C4          | 0           | A5            |

| D5          | 0           | A6            |

| A4          | 0           | VCCO (Bank 0) |

| B3          | 0           | GND (Bank 0)  |

| D4          | 0           | A8            |

| A3          | 0           | A9            |

| C3          | 0           | A10           |

| B2          | 0           | A12           |

| C2          | 0           | A13           |

## ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 144 csBGA

| Ball   | Bank   | LC4064ZE      | LC4128ZE      | LC4256ZE      |  |  |

|--------|--------|---------------|---------------|---------------|--|--|

| Number | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |  |  |

| F6     | -      | GND           | GND           | GND           |  |  |

| A1     | -      | TDI           | TDI           | TDI           |  |  |

| E4     | 0      | NC Ball       | VCCO (Bank 0) | VCCO (Bank 0) |  |  |

| B2     | 0      | NC Ball       | В0            | C12           |  |  |

| B1     | 0      | NC Ball       | B1            | C10           |  |  |

| C3     | 0      | A8            | B2            | C8            |  |  |

| C2     | 0      | A9            | B4            | C6            |  |  |

| C1     | 0      | A10           | B5            | C4            |  |  |

| D1     | 0      | A11           | B6            | C2            |  |  |

| G5     | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |  |  |

| D2     | 0      | NC Ball       | NC Ball       | D14           |  |  |

| D3     | 0      | NC Ball       | NC Ball       | D12           |  |  |

| E1     | 0      | NC Ball       | B8            | D10           |  |  |

| E2     | 0      | A12           | B9            | D8            |  |  |

| F2     | 0      | A13           | B10           | D6            |  |  |

| D4     | 0      | A14           | B12           | D4            |  |  |

| F1     | 0      | A15           | B13           | D2            |  |  |

| F3*    | 0      | I             | B14           | D0            |  |  |

| F4     | 0      | VCCO (Bank 0) | VCCO (Bank 0) | VCCO (Bank 0) |  |  |

| G1     | 0      | B15           | C14           | E0            |  |  |

| E3     | 0      | B14           | C13           | E2            |  |  |

| G2     | 0      | B13           | C12           | E4            |  |  |

| G3     | 0      | B12           | C10           | E6            |  |  |

| H1     | 0      | NC Ball       | C9            | E8            |  |  |

| НЗ     | 0      | NC Ball       | C8            | E10           |  |  |

| H2     | 0      | NC Ball       | NC Ball       | E12           |  |  |

| H4     | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |  |  |

| J1     | 0      | B11           | C6            | F2            |  |  |

| J3     | 0      | B10           | C5            | F4            |  |  |

| J2     | 0      | B9            | C4            | F6            |  |  |

| K1     | 0      | B8            | C2            | F8            |  |  |

| K2*    | 0      | I             | C1            | F10           |  |  |

| L1     | 0      | NC Ball       | C0            | F12           |  |  |

| G4     | 0      | NC Ball       | VCCO (Bank 0) | VCCO (Bank 0) |  |  |

| L2     | -      | TCK           | TCK           | TCK           |  |  |

| H5     | -      | VCC           | VCC           | VCC           |  |  |

| G6     | -      | GND           | GND           | GND           |  |  |

| M1     | 0      | NC Ball       | NC Ball       | G14           |  |  |

| K3     | 0      | NC Ball       | NC Ball       | G12           |  |  |

| M2     | 0      | NC Ball       | D14           | G10           |  |  |

| L3*    | 0      | I             | D13           | G8            |  |  |

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 144 csBGA (Cont.)

| J12 J11 H10 H12 G11 H11 G12 G10* G9 F12 | Bank Number                     | GLB/MC/Pad  NC Ball  NC Ball  NC Ball  C12  C13  C14  C15 | GLB/MC/Pad  NC Ball  NC Ball  F8  F9  F10  F12 | GLB/MC/Pad  L14  L12  L10  L8  L6  L4 |

|-----------------------------------------|---------------------------------|-----------------------------------------------------------|------------------------------------------------|---------------------------------------|

| J11 H10 H12 G11 H11 G12 G10* G9 F12     | 1<br>1<br>1<br>1<br>1<br>1<br>1 | NC Ball NC Ball C12 C13 C14 C15                           | NC Ball<br>F8<br>F9<br>F10<br>F12              | L12<br>L10<br>L8<br>L6                |

| H10 H12 G11 H11 G12 G10* G9 F12         | 1<br>1<br>1<br>1<br>1           | NC Ball<br>C12<br>C13<br>C14<br>C15                       | F8<br>F9<br>F10<br>F12                         | L10<br>L8<br>L6                       |

| H12 G11 H11 G12 G10* G9 F12             | 1<br>1<br>1<br>1                | C12<br>C13<br>C14<br>C15                                  | F9<br>F10<br>F12                               | L8<br>L6                              |

| G11<br>H11<br>G12<br>G10*<br>G9<br>F12  | 1<br>1<br>1                     | C13<br>C14<br>C15                                         | F10<br>F12                                     | L6                                    |

| H11 G12 G10* G9 F12                     | 1 1 1                           | C14<br>C15                                                | F12                                            |                                       |

| G12<br>G10*<br>G9<br>F12                | 1 1                             | C15                                                       |                                                | Ι /                                   |

| G10*<br>G9<br>F12                       | 1                               |                                                           | E40                                            | L <del>4</del>                        |

| G9<br>F12                               |                                 | ı                                                         | F13                                            | L2                                    |

| F12                                     | 1                               | I .                                                       | F14                                            | LO                                    |

|                                         |                                 | VCCO (Bank 1)                                             | VCCO (Bank 1)                                  | VCCO (Bank 1)                         |

|                                         | 1                               | D15                                                       | G14                                            | MO                                    |

| F11                                     | 1                               | D14                                                       | G13                                            | M2                                    |

| E11                                     | 1                               | D13                                                       | G12                                            | M4                                    |

| E12                                     | 1                               | D12                                                       | G10                                            | M6                                    |

| D10                                     | 1                               | NC Ball                                                   | G9                                             | M8                                    |

| F10                                     | 1                               | NC Ball                                                   | G8                                             | M10                                   |

| D12                                     | 1                               | NC Ball                                                   | NC Ball                                        | M12                                   |

| F8                                      | 1                               | GND (Bank 1)                                              | GND (Bank 1)                                   | GND (Bank 1)                          |

| E10                                     | 1                               | D11                                                       | G6                                             | N2                                    |

| D11                                     | 1                               | D10                                                       | G5                                             | N4                                    |

| E9                                      | 1                               | D9                                                        | G4                                             | N6                                    |

| C12                                     | 1                               | D8                                                        | G2                                             | N8                                    |

| C11*                                    | 1                               |                                                           | G1                                             | N10                                   |

| B12                                     | 1                               | NC Ball                                                   | G0                                             | N12                                   |

| F9                                      | 1                               | NC Ball                                                   | VCCO (Bank 1)                                  | VCCO (Bank 1)                         |

| B11                                     | -                               | TDO                                                       | TDO                                            | TDO                                   |

| E8                                      | -                               | VCC                                                       | VCC                                            | VCC                                   |

| F7                                      | -                               | GND                                                       | GND                                            | GND                                   |

| A12                                     | 1                               | NC Ball                                                   | NC Ball                                        | 014                                   |

| C10                                     | 1                               | NC Ball                                                   | NC Ball                                        | 012                                   |

| B10                                     | 1                               | NC Ball                                                   | H14                                            | O10                                   |

| A11*                                    | 1                               | I                                                         | H13                                            | O8                                    |

| D9                                      | 1                               | D7                                                        | H12                                            | O6                                    |

| B9                                      | 1                               | D6                                                        | H10                                            | 04                                    |

| C9                                      | 1                               | D5                                                        | H9                                             | 02                                    |

| A10                                     | 1                               | D4                                                        | H8                                             | 00                                    |

| E7                                      | 1                               | GND (Bank 1)                                              | GND (Bank 1)                                   | GND (Bank 1)                          |

| D8                                      | 1                               | VCCO (Bank 1)                                             | VCCO (Bank 1)                                  | VCCO (Bank 1)                         |

| A9                                      | 1                               | NC Ball                                                   | H6                                             | P12                                   |

| B8                                      | 1                               | NC Ball                                                   | H5                                             | P10                                   |

| C8                                      | 1                               | D3                                                        | H4                                             | P8                                    |

| A8                                      | 1                               | D2                                                        | H2                                             | P6                                    |

| D7                                      | 1                               | D1                                                        | H1                                             | P4                                    |

| B7                                      | 1                               | D0/G0F1                                                   | H0/G0F1                                        | P2/GOF1                               |

### ispMACH 4128ZE and 4256ZE Logic Signal Connections: 144 TQFP

|            |             |               | LC4256ZE      |  |  |

|------------|-------------|---------------|---------------|--|--|

| Pin Number | Bank Number | GLB/MC/Pad    | GLB/MC/Pad    |  |  |

| 1          | -           | GND           | GND           |  |  |

| 2          | -           | TDI           | TDI           |  |  |

| 3          | 0           | VCCO (Bank 0) | VCCO (Bank 0) |  |  |

| 4          | 0           | В0            | C12           |  |  |

| 5          | 0           | B1            | C10           |  |  |

| 6          | 0           | B2            | C8            |  |  |

| 7          | 0           | B4            | C6            |  |  |

| 8          | 0           | B5            | C4            |  |  |

| 9          | 0           | B6            | C2            |  |  |

| 10         | 0           | GND (Bank 0)  | GND (Bank 0)  |  |  |

| 11         | 0           | B8            | D14           |  |  |

| 12         | 0           | B9            | D12           |  |  |

| 13         | 0           | B10           | D10           |  |  |

| 14         | 0           | B12           | D8            |  |  |

| 15         | 0           | B13           | D6            |  |  |

| 16         | 0           | B14           | D4            |  |  |

| 17*        | 0           | NC            | I             |  |  |

| 18         | 0           | GND (Bank 0)  | NC            |  |  |

| 19         | 0           | VCCO (Bank 0) | VCCO (Bank 0) |  |  |

| 20*        | 0           | NC            | I             |  |  |

| 21         | 0           | C14           | E2            |  |  |

| 22         | 0           | C13           | E4            |  |  |

| 23         | 0           | C12           | E6            |  |  |

| 24         | 0           | C10           | E8            |  |  |

| 25         | 0           | C9            | E10           |  |  |

| 26         | 0           | C8            | E12           |  |  |

| 27         | 0           | GND (Bank 0)  | GND (Bank 0)  |  |  |

| 28         | 0           | C6            | F2            |  |  |

| 29         | 0           | C5            | F4            |  |  |

| 30         | 0           | C4            | F6            |  |  |

| 31         | 0           | C2            | F8            |  |  |

| 32         | 0           | C1            | F10           |  |  |

| 33         | 0           | C0            | F12           |  |  |

| 34         | 0           | VCCO (Bank 0) | VCCO (Bank 0) |  |  |

| 35         | -           | TCK           | TCK           |  |  |

| 36         | -           | VCC           | VCC           |  |  |

| 37         | -           | GND           | GND           |  |  |

| 38*        | 0           | NC            | I             |  |  |

| 39         | 0           | D14           | G12           |  |  |

| 40         | 0           | D13           | G10           |  |  |

| 41         | 0           | D12           | G8            |  |  |

| 42         | 0           | D10           | G6            |  |  |

Figure 20. Mark Format for 64 ucBGA and 132 ucBGA Packages

LC4064ZE 4UN-5I Datecode

**Dual Mark**

Single Mark

### **Lead-Free Packaging**

#### Commercial

| Device    | Part Number       | Macrocells | Voltage | t <sub>PD</sub> | Package         | Pin/Ball<br>Count | I/O | Grade |

|-----------|-------------------|------------|---------|-----------------|-----------------|-------------------|-----|-------|

|           | LC4032ZE-4TN48C   | 32         | 1.8     | 4.4             | Lead-Free TQFP  | 48                | 32  | С     |

| LC4032ZE  | LC4032ZE-5TN48C   | 32         | 1.8     | 5.8             | Lead-Free TQFP  | 48                | 32  | С     |

|           | LC4032ZE-7TN48C   | 32         | 1.8     | 7.5             | Lead-Free TQFP  | 48                | 32  | С     |

|           | LC4032ZE-4MN64C   | 32         | 1.8     | 4.4             | Lead-Free csBGA | 64                | 32  | С     |

|           | LC4032ZE-5MN64C   | 32         | 1.8     | 5.8             | Lead-Free csBGA | 64                | 32  | С     |

|           | LC4032ZE-7MN64C   | 32         | 1.8     | 7.5             | Lead-Free csBGA | 64                | 32  | С     |

|           | LC4064ZE-4TN48C   | 64         | 1.8     | 4.7             | Lead-Free TQFP  | 48                | 32  | С     |

|           | LC4064ZE-5TN48C   | 64         | 1.8     | 5.8             | Lead-Free TQFP  | 48                | 32  | С     |

|           | LC4064ZE-7TN48C   | 64         | 1.8     | 7.5             | Lead-Free TQFP  | 48                | 32  | С     |

|           | LC4064ZE-4TN100C  | 64         | 1.8     | 4.7             | Lead-Free TQFP  | 100               | 64  | С     |

|           | LC4064ZE-5TN100C  | 64         | 1.8     | 5.8             | Lead-Free TQFP  | 100               | 64  | С     |

| 1.0406475 | LC4064ZE-7TN100C  | 64         | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | С     |

| LC4064ZE  | LC4064ZE-4MN64C   | 64         | 1.8     | 4.7             | Lead-Free csBGA | 64                | 48  | С     |

|           | LC4064ZE-5MN64C   | 64         | 1.8     | 5.8             | Lead-Free csBGA | 64                | 48  | С     |

|           | LC4064ZE-7MN64C   | 64         | 1.8     | 7.5             | Lead-Free csBGA | 64                | 48  | С     |

|           | LC4064ZE-4MN144C  | 64         | 1.8     | 4.7             | Lead-Free csBGA | 144               | 64  | С     |

|           | LC4064ZE-5MN144C  | 64         | 1.8     | 5.8             | Lead-Free csBGA | 144               | 64  | С     |

|           | LC4064ZE-7MN144C  | 64         | 1.8     | 7.5             | Lead-Free csBGA | 144               | 64  | С     |

|           | LC4128ZE-5TN100C  | 128        | 1.8     | 5.8             | Lead-Free TQFP  | 100               | 64  | С     |

|           | LC4128ZE-7TN100C  | 128        | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | С     |

|           | LC4128ZE-5TN144C  | 128        | 1.8     | 5.8             | Lead-Free TQFP  | 144               | 96  | С     |

| 10410075  | LC4128ZE-7TN144C  | 128        | 1.8     | 7.5             | Lead-Free TQFP  | 144               | 96  | С     |

| LC4128ZE  | LC4128ZE-5UMN132C | 128        | 1.8     | 5.8             | Lead-Free ucBGA | 132               | 96  | С     |

|           | LC4128ZE-7UMN132C | 128        | 1.8     | 7.5             | Lead-Free ucBGA | 132               | 96  | С     |

|           | LC4128ZE-5MN144C  | 128        | 1.8     | 5.8             | Lead-Free csBGA | 144               | 96  | С     |

|           | LC4128ZE-7MN144C  | 128        | 1.8     | 7.5             | Lead-Free csBGA | 144               | 96  | С     |

| 1.0405075 | LC4256ZE-5TN100C  | 256        | 1.8     | 5.8             | Lead-Free TQFP  | 100               | 64  | С     |

|           | LC4256ZE-7TN100C  | 256        | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | С     |

|           | LC4256ZE-5TN144C  | 256        | 1.8     | 5.8             | Lead-Free TQFP  | 144               | 96  | С     |

| LC4256ZE  | LC4256ZE-7TN144C  | 256        | 1.8     | 7.5             | Lead-Free TQFP  | 144               | 96  | С     |

|           | LC4256ZE-5MN144C  | 256        | 1.8     | 5.8             | Lead-Free csBGA | 144               | 108 | С     |

|           | LC4256ZE-7MN144C  | 256        | 1.8     | 7.5             | Lead-Free csBGA | 144               | 108 | С     |

### **Revision History**

| Date           | Version | Change Summary                                                                                                                                  |  |  |  |

|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| April 2008     | 01.0    | Initial release.                                                                                                                                |  |  |  |

| July 2008      | 01.1    | Updated Features bullets.                                                                                                                       |  |  |  |

|                |         | Updated typical Hysteresis voltage.                                                                                                             |  |  |  |

|                |         | Updated Power Guard for Dedicated Inputs section.                                                                                               |  |  |  |

|                |         | Updated DC Electrical Characteristics table.                                                                                                    |  |  |  |

|                |         | Updated Supply Current table.                                                                                                                   |  |  |  |

|                |         | Updated I/O DC Electrical Characteristics table and note 2.                                                                                     |  |  |  |

|                |         | Updated ispMACH 4000ZE Timing Model.                                                                                                            |  |  |  |

|                |         | Added new parameters for the Internal Oscillator.                                                                                               |  |  |  |

|                |         | Updated ORP Reference table.                                                                                                                    |  |  |  |

|                |         | Updated Power Supply and NC Connections table.                                                                                                  |  |  |  |

|                |         | Updated 100 TQFP Logic Signal Connections table with LC4128ZE and 4256ZE.                                                                       |  |  |  |

|                |         | Updated 144 csBGA Logic Signal Connections table with LC4128ZE and 4256ZE.                                                                      |  |  |  |

|                |         | Added 144 TQFP Logic Signal Connections table.                                                                                                  |  |  |  |

| August 2008    | 01.2    | Data sheet status changed from advance to final.                                                                                                |  |  |  |

|                |         | Updated Supply Current table.                                                                                                                   |  |  |  |

|                |         | Updated External Switching Characteristics.                                                                                                     |  |  |  |

|                |         | Updated Internal Timing Parameters.                                                                                                             |  |  |  |

|                |         | Updated Power Consumption graph and Power Estimation Coefficients table.                                                                        |  |  |  |

|                |         | Updated Ordering Information mark format example.                                                                                               |  |  |  |

| December 2008  | 01.3    | Updated ispMACH 4000ZE Family Selection Guide table to include 64-ball ucBGA and 132-ball ucBGA packages.                                       |  |  |  |

|                |         | Updated ispMACH 4000ZE Power Supply and NC Connections table to include 64-ball ucBGA and 132-ball ucBGA packages.                              |  |  |  |

|                |         | Added Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                            |  |  |  |

|                |         | Updated Part Number Description diagram for 64-ball ucBGA and 132-ball ucBGA packages.                                                          |  |  |  |

|                |         | Updated Ordering Information tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                              |  |  |  |

| May 2009       | 01.4    | Correction to t <sub>CW</sub> , t <sub>GW</sub> , t <sub>WIR</sub> and f <sub>MAX</sub> parameters in External Switching Characteristics table. |  |  |  |

| June 2011 01.5 |         | Added copper bond package part numbers.                                                                                                         |  |  |  |

|                |         | Added footnote 4 to Absolute Maximum Ratings.                                                                                                   |  |  |  |

| February 2012  | 01.6    | Updated document with new corporate logo.                                                                                                       |  |  |  |

| February 2012  | 01.7    | Removed copper bond packaging information. Refer to PCN 04A-12 for further information.                                                         |  |  |  |

|                |         | Updated topside marks with new logos in the Ordering Information section.                                                                       |  |  |  |