# E: Lattice Semiconductor Corporation - <u>LC4064ZE-4TN100C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### Applications of Embedded - CPLDs

#### Details

| Product Status                  | Active                                                                      |

|---------------------------------|-----------------------------------------------------------------------------|

| Programmable Type               | In System Programmable                                                      |

| Delay Time tpd(1) Max           | 4.7 ns                                                                      |

| Voltage Supply - Internal       | 1.7V ~ 1.9V                                                                 |

| Number of Logic Elements/Blocks | 4                                                                           |

| Number of Macrocells            | 64                                                                          |

| Number of Gates                 | -                                                                           |

| Number of I/O                   | 64                                                                          |

| Operating Temperature           | 0°C ~ 90°C (TJ)                                                             |

| Mounting Type                   | Surface Mount                                                               |

| Package / Case                  | 100-LQFP                                                                    |

| Supplier Device Package         | 100-TQFP (14x14)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc4064ze-4tn100c |

|                                 |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Product Term Allocator**

The product term allocator assigns product terms from a cluster to either logic or control applications as required by the design being implemented. Product terms that are used as logic are steered into a 5-input OR gate associated with the cluster. Product terms that used for control are steered either to the macrocell or I/O cell associated with the cluster. Table 2 shows the available functions for each of the five product terms in the cluster.

| Product Term   | Logic    | Control                                                                     |

|----------------|----------|-----------------------------------------------------------------------------|

| PT <i>n</i>    | Logic PT | Single PT for XOR/OR                                                        |

| PT <i>n</i> +1 | Logic PT | Individual Clock (PT Clock)                                                 |

| PT <i>n</i> +2 | Logic PT | Individual Initialization or Individual Clock Enable (PT Initialization/CE) |

| PT <i>n</i> +3 | Logic PT | Individual Initialization (PT Initialization)                               |

| PT <i>n</i> +4 | Logic PT | Individual OE (PTOE)                                                        |

### **Cluster Allocator**

The cluster allocator allows clusters to be steered to neighboring macrocells, thus allowing the creation of functions with more product terms. Table 3 shows which clusters can be steered to which macrocells. Used in this manner, the cluster allocator can be used to form functions of up to 20 product terms. Additionally, the cluster allocator accepts inputs from the wide steering logic. Using these inputs, functions up to 80 product terms can be created.

| Macrocell |     | Available Clusters |     |     |  |  |

|-----------|-----|--------------------|-----|-----|--|--|

| MO        | —   | C0                 | C1  | C2  |  |  |

| M1        | C0  | C1                 | C2  | C3  |  |  |

| M2        | C1  | C2                 | C3  | C4  |  |  |

| M3        | C2  | C3                 | C4  | C5  |  |  |

| M4        | C3  | C4                 | C5  | C6  |  |  |

| M5        | C4  | C5                 | C6  | C7  |  |  |

| M6        | C5  | C6                 | C7  | C8  |  |  |

| M7        | C6  | C7                 | C8  | C9  |  |  |

| M8        | C7  | C8                 | C9  | C10 |  |  |

| M9        | C8  | C9                 | C10 | C11 |  |  |

| M10       | C9  | C10                | C11 | C12 |  |  |

| M11       | C10 | C11                | C12 | C13 |  |  |

| M12       | C11 | C12                | C13 | C14 |  |  |

| M13       | C12 | C13                | C14 | C15 |  |  |

| M14       | C13 | C14                | C15 | —   |  |  |

| M15       | C14 | C15                | _   | _   |  |  |

#### Table 3. Available Clusters for Each Macrocell

## Wide Steering Logic

The wide steering logic allows the output of the cluster allocator n to be connected to the input of the cluster allocator n+4. Thus, cluster chains can be formed with up to 80 product terms, supporting wide product term functions and allowing performance to be increased through a single GLB implementation. Table 4 shows the product term chains.

| Expansion<br>Chains | Macrocells Associated with Expansion Chain<br>(with Wrap Around) | Max PT/<br>Macrocell |

|---------------------|------------------------------------------------------------------|----------------------|

| Chain-0             | M0 Õ M4 Õ M8 Õ M12 Õ M0                                          | 75                   |

| Chain-1             | M1 Õ M5 Õ M9 Õ M13 Õ M1                                          | 80                   |

| Chain-2             | M2 Õ M6 Õ M10 Õ M14 Õ M2                                         | 75                   |

| Chain-3             | M3 Õ M7 Õ M11 Õ M15 Õ M3                                         | 70                   |

#### Table 4. Product Term Expansion Capability

Every time the super cluster allocator is used, there is an incremental delay of  $t_{EXP}$ . When the super cluster allocator is used, all destinations other than the one being steered to, are given the value of ground (i.e., if the super cluster is steered to M (n+4), then M (n) is ground).

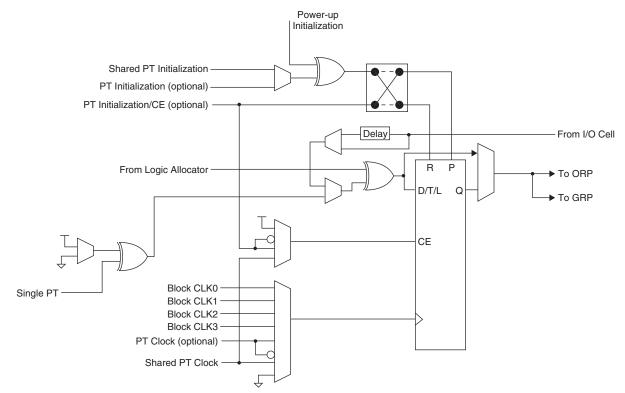

### Macrocell

The 16 macrocells in the GLB are driven by the 16 outputs from the logic allocator. Each macrocell contains a programmable XOR gate, a programmable register/latch, along with routing for the logic and control functions. Figure 5 shows a graphical representation of the macrocell. The macrocells feed the ORP and GRP. A direct input from the I/O cell allows designers to use the macrocell to construct high-speed input registers. A programmable delay in this path allows designers to choose between the fastest possible set-up time and zero hold time.

#### Figure 5. Macrocell

### **Enhanced Clock Multiplexer**

The clock input to the flip-flop can select any of the four block clocks along with the shared PT clock, and true and complement forms of the optional individual term clock. An 8:1 multiplexer structure is used to select the clock. The eight sources for the clock multiplexer are as follows:

- Block CLK0

- Block CLK1

# Absolute Maximum Ratings<sup>1, 2, 3, 4</sup>

| Supply Voltage (V_CC) $\ldots$                          |

|---------------------------------------------------------|

| Output Supply Voltage (V_{CCO})                         |

| Input or I/O Tristate Voltage Applied <sup>5, 6</sup>   |

| Storage Temperature65 to 150°C                          |

| Junction Temperature (Tj) with Power Applied55 to 150°C |

- 1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Compliance with Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- 4. Please refer to the Lattice ispMACH 4000V/B/C/ZC/ZE Product Family Qualification Summary for complete data, including the ESD performance data.

- 5. Undershoot of -2V and overshoot of ( $V_{IH}$  (MAX) + 2V), up to a total pin voltage of 6V is permitted for a duration of <20ns.

- 6. Maximum of 64 I/Os per device with VIN > 3.6V is allowed.

## **Recommended Operating Conditions**

| Symbol          | Parameter                         |                            |                  | Max. | Units |

|-----------------|-----------------------------------|----------------------------|------------------|------|-------|

|                 |                                   | Standard Voltage Operation | 1.7              | 1.9  | V     |

| V <sub>CC</sub> | Supply Voltage                    | Extended Voltage Operation | 1.6 <sup>1</sup> | 1.9  | V     |

| т               | Junction Temperature (Commercial) |                            | 0                | 90   | °C    |

| ۱j              | Junction Temperature (Industrial) |                            | -40              | 105  | °C    |

1. Devices operating at 1.6V can expect performance degradation up to 35%.

## **Erase Reprogram Specifications**

| Parameter             | Min.  | Max. | Units  |

|-----------------------|-------|------|--------|

| Erase/Reprogram Cycle | 1,000 |      | Cycles |

Note: Valid over commercial temperature range.

## Hot Socketing Characteristics<sup>1,2,3</sup>

| Symbol | Parameter                    | Condition                                     | Min. | Тур. | Max. | Units |

|--------|------------------------------|-----------------------------------------------|------|------|------|-------|

| I      | Input or I/O Leakage Current | $0 \le V_{IN} \le 3.0V$ , Tj = 105°C          |      | ±30  | ±150 | μΑ    |

| DK     | Input of I/O Leakage Current | $0 \le V_{IN} \le 3.0V$ , Tj = $130^{\circ}C$ | _    | ±30  | ±200 | μA    |

1. Insensitive to sequence of V<sub>CC</sub> or V<sub>CCO.</sub> However, assumes monotonic rise/fall rates for V<sub>CC</sub> and V<sub>CCO,</sub> provided (V<sub>IN</sub> - V<sub>CCO</sub>)  $\leq$  3.6V.

2.  $0 < V_{CC} < V_{CC}$  (MAX),  $0 < V_{CCO} < V_{CCO}$  (MAX).

3.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ . Device defaults to pull-up until fuse circuitry is active.

## ispMACH 4000ZE Internal Timing Parameters (Cont.)

### **Over Recommended Operating Conditions**

|              |                                                 |                                                       | LC40 | 32ZE | LC40 | 64ZE |       |

|--------------|-------------------------------------------------|-------------------------------------------------------|------|------|------|------|-------|

|              |                                                 |                                                       | -    | 4    | -    | 4    |       |

| Parameter    | Description                                     |                                                       | Min. | Max. | Min. | Max. | Units |

| LVCMOS15_out | Output Configured as 1.5V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.20 | _    | 0.20 | ns    |

| LVCMOS18_out | Output Configured as 1.8V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | —    | 0.00 | _    | 0.00 | ns    |

| LVCMOS25_out | Output Configured as 2.5V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.10 | _    | 0.10 | ns    |

| LVCMOS33_out | Output Configured as 3.3V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.20 | _    | 0.20 | ns    |

| PCI_out      | Output Configured as PCI Compati-<br>ble Buffer | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.20 | _    | 0.20 | ns    |

| Slow Slew    | Output Configured for Slow Slew<br>Rate         | t <sub>EN</sub> , t <sub>BUF</sub>                    | _    | 1.00 | _    | 1.00 | ns    |

Note: Internal Timing Parameters are not tested and are for reference only. Refer to the timing model in this data sheet for further details. Timing v.0.8

# ispMACH 4000ZE Internal Timing Parameters (Cont.)

|                       |                                                                 | All Devices |          |      |      |       |

|-----------------------|-----------------------------------------------------------------|-------------|----------|------|------|-------|

|                       |                                                                 | -5          |          | -7   |      | ]     |

| Parameter             | Description                                                     |             | Max.     | Min. | Max. | Units |

| In/Out Delays         |                                                                 |             |          |      |      |       |

| t <sub>IN</sub>       | Input Buffer Delay                                              | —           | 1.05     | —    | 1.90 | ns    |

| t <sub>GCLK_IN</sub>  | Global Clock Input Buffer Delay                                 | _           | 1.95     | —    | 2.15 | ns    |

| t <sub>GOE</sub>      | Global OE Pin Delay                                             |             | 3.00     | —    | 4.30 | ns    |

| t <sub>BUF</sub>      | Delay through Output Buffer                                     | _           | 1.10     | —    | 1.30 | ns    |

| t <sub>EN</sub>       | Output Enable Time                                              |             | 2.50     | —    | 2.70 | ns    |

| t <sub>DIS</sub>      | Output Disable Time                                             |             | 2.50     | —    | 2.70 | ns    |

| t <sub>PGSU</sub>     | Input Power Guard Setup Time                                    | _           | 4.30     | —    | 5.60 | ns    |

| t <sub>PGH</sub>      | Input Power Guard Hold Time                                     |             | 0.00     | —    | 0.00 | ns    |

| t <sub>PGPW</sub>     | Input Power Guard BIE Minimum Pulse Width                       | _           | 6.00     | —    | 8.00 | ns    |

| t <sub>PGRT</sub>     | Input Power Guard Recovery Time Following BIE Dis-<br>sertation | _           | 5.00     | —    | 7.00 | ns    |

| Routing Delays        |                                                                 |             |          |      |      | 1     |

| t <sub>ROUTE</sub>    | Delay through GRP                                               | _           | 2.25     | —    | 2.50 | ns    |

| t <sub>PDi</sub>      | Macrocell Propagation Delay                                     | _           | 0.45     | —    | 0.50 | ns    |

| t <sub>MCELL</sub>    | Macrocell Delay                                                 | _           | 0.65     | _    | 1.00 | ns    |

| t <sub>INREG</sub>    | Input Buffer to Macrocell Register Delay                        | _           | 1.00     | —    | 1.00 | ns    |

| t <sub>FBK</sub>      | Internal Feedback Delay                                         | _           | 0.75     | _    | 0.30 | ns    |

| t <sub>ORP</sub>      | Output Routing Pool Delay                                       | _           | 0.30     | _    | 0.30 | ns    |

| Register/Latch        |                                                                 |             |          |      |      |       |

| t <sub>S</sub>        | D-Register Setup Time (Global Clock)                            | 0.90        | _        | 1.25 |      | ns    |

| t <sub>S_PT</sub>     | D-Register Setup Time (Product Term Clock)                      | 2.00        | _        | 2.35 |      | ns    |

| t <sub>H</sub>        | D-Register Hold Time                                            | 2.00        | _        | 3.25 |      | ns    |

| t <sub>ST</sub>       | T-Register Setup Time (Global Clock)                            | 1.10        | _        | 1.45 |      | ns    |

| t <sub>ST_PT</sub>    | T-register Setup Time (Product Term Clock)                      | 2.20        | <u> </u> | 2.65 |      | ns    |

| <u>t<sub>HT</sub></u> | T-Resister Hold Time                                            | 2.00        | _        | 3.25 |      | ns    |

| t <sub>SIR</sub>      | D-Input Register Setup Time (Global Clock)                      | 1.20        | _        | 0.65 |      | ns    |

| t <sub>SIR_PT</sub>   | D-Input Register Setup Time (Product Term Clock)                | 1.45        | _        | 1.45 |      | ns    |

| t <sub>HIR</sub>      | D-Input Register Hold Time (Global Clock)                       | 1.40        | _        | 2.05 |      | ns    |

| t <sub>HIR_PT</sub>   | D-Input Register Hold Time (Product Term Clock)                 | 1.10        | _        | 1.20 |      | ns    |

| t <sub>COi</sub>      | Register Clock to Output/Feedback MUX Time                      | _           | 0.45     | _    | 0.75 | ns    |

| t <sub>CES</sub>      | Clock Enable Setup Time                                         | 2.00        | _        | 2.00 | _    | ns    |

| t <sub>CEH</sub>      | Clock Enable Hold Time                                          | 0.00        | _        | 0.00 | _    | ns    |

| t <sub>SL</sub>       | Latch Setup Time (Global Clock)                                 | 0.90        |          | 1.55 |      | ns    |

| t <sub>SL_PT</sub>    | Latch Setup Time (Product Term Clock)                           | 2.00        |          | 2.05 |      | ns    |

| t <sub>HL</sub>       | Latch Hold Time                                                 | 2.00        |          | 1.17 |      | ns    |

|                       | Latch Gate to Output/Feedback MUX Time                          |             | 0.35     |      | 0.33 | ns    |

| t <sub>GOi</sub>      | Propagation Delay through Transparent Latch to Output/          |             |          |      |      |       |

| t <sub>PDLi</sub>     | Feedback MUX                                                    |             | 0.25     |      | 0.25 | ns    |

| t <sub>SRi</sub>      | Asynchronous Reset or Set to Output/Feedback MUX<br>Delay       | _           | 0.95     | —    | 0.28 | ns    |

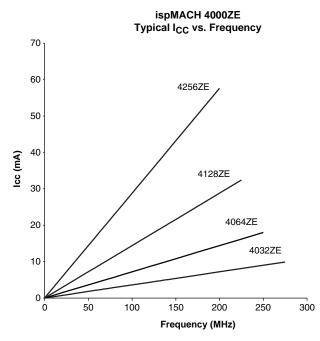

## **Power Consumption**

## **Power Estimation Coefficients**<sup>1</sup>

| Device         | Α     | В     |

|----------------|-------|-------|

| ispMACH 4032ZE | 0.010 | 0.009 |

| ispMACH 4064ZE | 0.011 | 0.009 |

| ispMACH 4128ZE | 0.012 | 0.009 |

| ispMACH 4256ZE | 0.013 | 0.009 |

1. For further information about the use of these coefficients, refer to TN1187, <u>Power Esti-</u> mation in ispMACH 4000ZE Devices.

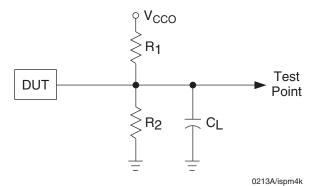

## **Switching Test Conditions**

Figure 17 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 13.

#### Figure 17. Output Test Load, LVTTL and LVCMOS Standards

Table 13. Test Fixture Required Components

| Test Condition               | R <sub>1</sub> | R <sub>2</sub> | CL1  | Timing Ref.                      | V <sub>cco</sub>   |

|------------------------------|----------------|----------------|------|----------------------------------|--------------------|

|                              |                |                |      | LVCMOS 3.3 = 1.5V                | LVCMOS 3.3 = 3.0V  |

|                              |                |                |      | LVCMOS 2.5 = $\frac{V_{CCO}}{2}$ | LVCMOS 2.5 = 2.3V  |

| LVCMOS I/O, (L -> H, H -> L) | 106Ω           | 106Ω           | 35pF | LVCMOS 1.8 = $\frac{V_{CCO}}{2}$ | LVCMOS 1.8 = 1.65V |

|                              |                |                |      | LVCMOS 1.5 = $\frac{V_{CCO}}{2}$ | LVCMOS 1.5 = 1.4V  |

| LVCMOS I/O (Z -> H)          | $\infty$       | 106Ω           | 35pF | 1.5V                             | 3.0V               |

| LVCMOS I/O (Z -> L)          | 106Ω           | ×              | 35pF | 1.5V                             | 3.0V               |

| LVCMOS I/O (H -> Z)          | $\infty$       | 106Ω           | 5pF  | V <sub>OH</sub> - 0.3            | 3.0V               |

| LVCMOS I/O (L -> Z)          | 106Ω           | 8              | 5pF  | V <sub>OL</sub> + 0.3            | 3.0V               |

1. C<sub>L</sub> includes test fixtures and probe capacitance.

# **Signal Descriptions**

| Signal Names                          | Desci                                                                                                | ription                                                                                                 |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| TMS                                   | Input – This pin is the IEEE 1149.1 Test M the state machine.                                        | Input – This pin is the IEEE 1149.1 Test Mode Select input, which is used to control the state machine. |  |  |  |

| тск                                   | Input – This pin is the IEEE 1149.1 Test C state machine.                                            | lock input pin, used to clock through the                                                               |  |  |  |

| TDI                                   | Input – This pin is the IEEE 1149.1 Test D                                                           | ata In pin, used to load data.                                                                          |  |  |  |

| TDO                                   | Output – This pin is the IEEE 1149.1 Test                                                            | Data Out pin used to shift data out.                                                                    |  |  |  |

| GOE0/IO, GOE1/IO                      | These pins are configured to be either Glo<br>pins.                                                  | These pins are configured to be either Global Output Enable Input or as general I/O pins.               |  |  |  |

| GND                                   | Ground                                                                                               |                                                                                                         |  |  |  |

| NC                                    | Not Connected                                                                                        |                                                                                                         |  |  |  |

| V <sub>CC</sub>                       | The power supply pins for logic core and J                                                           | The power supply pins for logic core and JTAG port.                                                     |  |  |  |

| CLK0/I, CLK1/I, CLK2/I, CLK3/I        | These pins are configured to be either CLI                                                           | K input or as an input.                                                                                 |  |  |  |

| V <sub>CCO0</sub> , V <sub>CCO1</sub> | The power supply pins for each I/O bank.                                                             |                                                                                                         |  |  |  |

|                                       | Input/Output <sup>1</sup> – These are the general pur reference (alpha) and z is macrocell reference |                                                                                                         |  |  |  |

|                                       | ispMACH 4032ZE                                                                                       | y: A-B                                                                                                  |  |  |  |

| yzz                                   | ispMACH 4064ZE                                                                                       | y: A-D                                                                                                  |  |  |  |

|                                       | ispMACH 4128ZE                                                                                       | y: A-H                                                                                                  |  |  |  |

|                                       | ispMACH 4256ZE                                                                                       | y: A-P                                                                                                  |  |  |  |

1. In some packages, certain I/Os are only available for use as inputs. See the Logic Signal Connections tables for details.

## **ORP Reference Table**

|                                          | 4032ZE |    | 4064ZE                         |    | 412 | 8ZE |    | 4256ZE |                       |

|------------------------------------------|--------|----|--------------------------------|----|-----|-----|----|--------|-----------------------|

| Number of I/Os                           | 32     | 32 | 48                             | 64 | 64  | 96  | 64 | 96     | 108                   |

| Number of GLBs                           | 2      | 4  | 4                              | 4  | 8   | 8   | 16 | 16     | 16                    |

| Number of<br>I/Os per GLB                | 16     | 8  | Mixture of<br>9, 10,<br>14, 15 | 16 | 8   | 12  | 4  | 6      | Mixture of<br>6, 7, 8 |

| Reference ORP<br>Table (I/Os per<br>GLB) | 16     | 8  | 9, 10,<br>14, 15               | 16 | 8   | 12  | 4  | 6      | 6, 7, 8               |

# ispMACH 4032ZE and 4064ZE Logic Signal Connections: 48 TQFP (Cont.)

|            |             | ispMACH 4032ZE | ispMACH 4064ZE |

|------------|-------------|----------------|----------------|

| Pin Number | Bank Number | GLB/MC/Pad     | GLB/MC/Pad     |

| 43         | 0           | CLK0/I         | CLK0/I         |

| 44         | 0           | A0/GOE0        | A0/GOE0        |

| 45         | 0           | A1             | A1             |

| 46         | 0           | A2             | A2             |

| 47         | 0           | A3             | A4             |

| 48         | 0           | A4             | A6             |

# ispMACH 4064ZE Logic Signal Connections: 64 ucBGA

| Ball Number | Bank Number | GLB/MC/Pad    |

|-------------|-------------|---------------|

| A1          | -           | TDI           |

| B1          | 0           | A8            |

| B2          | 0           | A10           |

| B3          | 0           | A11           |

| GND*        | 0           | GND (Bank 0)  |

| C1          | 0           | A12           |

| C3          | 0           | VCCO (Bank 0) |

| C2          | 0           | B15           |

| D1          | 0           | B14           |

| D2          | 0           | B13           |

| D3          | 0           | B12           |

| E1          | 0           | B11           |

| E2          | 0           | B10           |

| E3          | 0           | В9            |

| F1          | 0           | B8            |

| F2          | -           | ТСК           |

| E4          | -           | VCC           |

| GND*        | -           | GND           |

| H2          | 0           | B6            |

| H1          | 0           | B5            |

| G1          | 0           | B4            |

| GND*        | 0           | GND (Bank 0)  |

| F3          | 0           | VCCO (Bank 0) |

| G2          | 0           | B3            |

| G3          | 0           | B2            |

| H3          | 0           | B0            |

| G4          | 0           | CLK1/I        |

| F4          | 1           | CLK2/I        |

| H4          | 1           | C0            |

| H5          | 1           | C1            |

| G5          | 1           | C2            |

| H6          | 1           | C4            |

| H7          | 1           | C5            |

| H8          | 1           | C6            |

| G8          | -           | TMS           |

| G7          | 1           | C8            |

| G6          | 1           | C10           |

| F8          | 1           | C11           |

| GND*        | 1           | GND (Bank 1)  |

| F7          | 1           | C12           |

| F6          | 1           | VCCO (Bank 1) |

| F5          | 1           | D15           |

| E8          | 1           | D14           |

# ispMACH 4064ZE Logic Signal Connections: 64 ucBGA (Cont.)

| Ball Number | Bank Number | GLB/MC/Pad    |

|-------------|-------------|---------------|

| E7          | 1           | D13           |

| E6          | 1           | D12           |

| D8          | 1           | D11           |

| D7          | 1           | D10           |

| D6          | 1           | D9            |

| C8          | 1           | D8            |

| C7          | -           | TDO           |

| D5          | -           | VCC           |

| GND*        | -           | GND           |

| B8          | 1           | D7            |

| A8          | 1           | D6            |

| B7          | 1           | D5            |

| A7          | 1           | D4            |

| GND*        | 1           | GND (Bank 1)  |

| A6          | 1           | VCCO (Bank 1) |

| B6          | 1           | D3            |

| C6          | 1           | D2            |

| A5          | 1           | D0/GOE1       |

| B5          | 1           | CLK3/I        |

| C5          | 0           | CLK0/I        |

| A4          | 0           | A0/GOE0       |

| B4          | 0           | A1            |

| C4          | 0           | A2            |

| A3          | 0           | A4            |

| A2          | 0           | A6            |

\* All bonded grounds are connected to the following two balls, D4 and E5.

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 100 TQFP

| Pin Bank |        | LC4064ZE      | LC4128ZE      | LC4256ZE      |

|----------|--------|---------------|---------------|---------------|

| Number   | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |

| 1        | -      | GND           | GND           | GND           |

| 2        | -      | TDI           | TDI           | TDI           |

| 3        | 0      | A8            | B0            | C12           |

| 4        | 0      | A9            | B2            | C10           |

| 5        | 0      | A10           | B4            | C6            |

| 6        | 0      | A11           | B6            | C2            |

| 7        | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| 8        | 0      | A12           | B8            | D12           |

| 9        | 0      | A13           | B10           | D10           |

| 10       | 0      | A14           | B12           | D6            |

| 11       | 0      | A15           | B13           | D4            |

| 12*      | 0      |               | I             | I             |

| 13       | 0      | VCCO (Bank 0) | VCCO (Bank 0) | VCCO (Bank 0) |

| 14       | 0      | B15           | C14           | E4            |

| 15       | 0      | B14           | C12           | E6            |

| 16       | 0      | B13           | C10           | E10           |

| 17       | 0      | B12           | C8            | E12           |

| 18       | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| 19       | 0      | B11           | C6            | F2            |

| 20       | 0      | B10           | C5            | F6            |

| 21       | 0      | B9            | C4            | F10           |

| 22       | 0      | B8            | C2            | F12           |

| 23*      | 0      |               | I             | I             |

| 24       | -      | TCK           | ТСК           | ТСК           |

| 25       | -      | VCC           | VCC           | VCC           |

| 26       | -      | GND           | GND           | GND           |

| 27*      | 0      |               | I             |               |

| 28       | 0      | B7            | D13           | G12           |

| 29       | 0      | B6            | D12           | G10           |

| 30       | 0      | B5            | D10           | G6            |

| 31       | 0      | B4            | D8            | G2            |

| 32       | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| 33       | 0      | VCCO (Bank 0) | VCCO (Bank 0) | VCCO (Bank 0) |

| 34       | 0      | B3            | D6            | H12           |

| 35       | 0      | B2            | D4            | H10           |

| 36       | 0      | B1            | D2            | H6            |

| 37       | 0      | B0            | D0            | H2            |

| 38       | 0      | CLK1/I        | CLK1/I        | CLK1/I        |

| 39       | 1      | CLK2/I        | CLK2/I        | CLK2/I        |

| 40       | -      | VCC           | VCC           | VCC           |

| 41       | 1      | CO            | E0            | 12            |

# ispMACH 4128ZE Logic Signal Connections: 132 ucBGA

| Ball Number | Bank Number | GLB/MC/Pad    |

|-------------|-------------|---------------|

| GND*        | -           | GND           |

| A1          | -           | TDI           |

| B1          | 0           | VCCO (Bank 0) |

| D3          | 0           | B0            |

| C1          | 0           | B1            |

| D2          | 0           | B2            |

| D1          | 0           | B4            |

| E4          | 0           | B5            |

| F3          | 0           | B6            |

| E2          | 0           | GND (Bank 0)  |

| E1          | 0           | B8            |

| E3          | 0           | B9            |

| F4          | 0           | B10           |

| G4          | 0           | B12           |

| F2          | 0           | B13           |

| G3          | 0           | B14           |

| H4          | 0           | VCCO (Bank 0) |

| F1          | 0           | C14           |

| G2          | 0           | C13           |

| G1          | 0           | C12           |

| H3          | 0           | C10           |

| J4          | 0           | C9            |

| H1          | 0           | C8            |

| H2          | 0           | GND (Bank 0)  |

| J3          | 0           | C6            |

| J1          | 0           | C5            |

| J2          | 0           | C4            |

| K3          | 0           | C2            |

| K2          | 0           | C1            |

| K1          | 0           | CO            |

| L2          | 0           | VCCO (Bank 0) |

| L1          | -           | ТСК           |

| M1          | -           | VCC           |

| GND*        | -           | GND           |

| L3          | 0           | D14           |

| M2          | 0           | D13           |

| K4          | 0           | D12           |

| M3          | 0           | D10           |

| K5          | 0           | D9            |

| L4          | 0           | D8            |

| M4          | 0           | GND (Bank 0)  |

| J5          | 0           | VCCO (Bank 0) |

| L5          | 0           | D6            |

# ispMACH 4128ZE Logic Signal Connections: 132 ucBGA (Cont.)

| Ball Number | Bank Number | GLB/MC/Pad    |

|-------------|-------------|---------------|

| M5          | 0           | D5            |

| J6          | 0           | D4            |

| K6          | 0           | D2            |

| L6          | 0           | D1            |

| M6          | 0           | D0            |

| K7          | 0           | CLK1/I        |

| L7          | 1           | GND (Bank 1)  |

| J7          | 1           | CLK2/I        |

| M7          | -           | VCC           |

| K8          | 1           | E0            |

| L8          | 1           | E1            |

| M8          | 1           | E2            |

| J8          | 1           | E4            |

| L9          | 1           | E5            |

| M9          | 1           | E6            |

| K9          | 1           | VCCO (Bank 1) |

| J9          | 1           | GND (Bank 1)  |

| L10         | 1           | E8            |

| K10         | 1           | E9            |

| M10         | 1           | E10           |

| L11         | 1           | E12           |

| K12         | 1           | E13           |

| M11         | 1           | E14           |

| GND*        | -           | GND           |

| M12         | -           | TMS           |

| L12         | 1           | VCCO (Bank 1) |

| K11         | 1           | F0            |

| J10         | 1           | F1            |

| H9          | 1           | F2            |

| J12         | 1           | F4            |

| J11         | 1           | F5            |

| H10         | 1           | F6            |

| H12         | 1           | GND (Bank 1)  |

| G9          | 1           | F8            |

| H11         | 1           | F9            |

| F9          | 1           | F10           |

| G12         | 1           | F12           |

| G11         | 1           | F13           |

| G10         | 1           | F14           |

| F12         | 1           | VCCO (Bank 1) |

| F10         | 1           | G14           |

| F11         | 1           | G13           |

| E11         | 1           | G12           |

| E10         | 1           | G10           |

# ispMACH 4128ZE Logic Signal Connections: 132 ucBGA (Cont.)

| Ball Number | Bank Number | GLB/MC/Pad |

|-------------|-------------|------------|

| A2          | 0           | A14        |

\* All bonded core grounds are connected to the following four balls, E5, E8, H5 and H8.

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 144 csBGA

| Ball Bank |        | LC4064ZE      | LC4128ZE      | LC4256ZE      |

|-----------|--------|---------------|---------------|---------------|

| Number    | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |

| F6        | -      | GND           | GND           | GND           |

| A1        | -      | TDI           | TDI           | TDI           |

| E4        | 0      | NC Ball       | VCCO (Bank 0) | VCCO (Bank 0) |

| B2        | 0      | NC Ball       | B0            | C12           |

| B1        | 0      | NC Ball       | B1            | C10           |

| C3        | 0      | A8            | B2            | C8            |

| C2        | 0      | A9            | B4            | C6            |

| C1        | 0      | A10           | B5            | C4            |

| D1        | 0      | A11           | B6            | C2            |

| G5        | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| D2        | 0      | NC Ball       | NC Ball       | D14           |

| D3        | 0      | NC Ball       | NC Ball       | D12           |

| E1        | 0      | NC Ball       | B8            | D10           |

| E2        | 0      | A12           | B9            | D8            |

| F2        | 0      | A13           | B10           | D6            |

| D4        | 0      | A14           | B12           | D4            |

| F1        | 0      | A15           | B13           | D2            |

| F3*       | 0      |               | B14           | D0            |

| F4        | 0      | VCCO (Bank 0) | VCCO (Bank 0) | VCCO (Bank 0) |

| G1        | 0      | B15           | C14           | E0            |

| E3        | 0      | B14           | C13           | E2            |

| G2        | 0      | B13           | C12           | E4            |

| G3        | 0      | B12           | C10           | E6            |

| H1        | 0      | NC Ball       | C9            | E8            |

| H3        | 0      | NC Ball       | C8            | E10           |

| H2        | 0      | NC Ball       | NC Ball       | E12           |

| H4        | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| J1        | 0      | B11           | C6            | F2            |

| J3        | 0      | B10           | C5            | F4            |

| J2        | 0      | B9            | C4            | F6            |

| K1        | 0      | B8            | C2            | F8            |

| K2*       | 0      |               | C1            | F10           |

| L1        | 0      | NC Ball       | CO            | F12           |

| G4        | 0      | NC Ball       | VCCO (Bank 0) | VCCO (Bank 0) |

| L2        | -      | ТСК           | ТСК           | ТСК           |

| H5        | -      | VCC           | VCC           | VCC           |

| G6        | -      | GND           | GND           | GND           |

| M1        | 0      | NC Ball       | NC Ball       | G14           |

| K3        | 0      | NC Ball       | NC Ball       | G12           |

| M2        | 0      | NC Ball       | D14           | G10           |

| L3*       | 0      |               | D13           | G8            |

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 144 csBGA (Cont.)

| Ball<br>Number | Bank   | LC4064ZE      | LC4128ZE      | LC4256ZE      |  |  |

|----------------|--------|---------------|---------------|---------------|--|--|

|                | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |  |  |

| C7             | 1      | CLK3/I        | CLK3/I        | CLK3/I        |  |  |

| E6             | 0      | NC Ball       | GND (Bank 0)  | GND (Bank 0)  |  |  |

| A7             | 0      | CLK0/I        | CLK0/I        | CLK0/I        |  |  |

| E5             | -      | VCC           | VCC           | VCC           |  |  |

| D6             | 0      | A0/GOE0       | A0/GOE0       | A2/GOE0       |  |  |

| B6             | 0      | A1            | A1            | A4            |  |  |

| A6             | 0      | A2            | A2            | A6            |  |  |

| C6             | 0      | A3            | A4            | A8            |  |  |

| B5             | 0      | NC Ball       | A5            | A10           |  |  |

| A5             | 0      | NC Ball       | A6            | A12           |  |  |

| D5             | 0      | VCCO (Bank 0) | VCCO (Bank 0) | VCCO (Bank 0) |  |  |

| F5             | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |  |  |

| A4             | 0      | A4            | A8            | B2            |  |  |

| B4             | 0      | A5            | A9            | B4            |  |  |

| C5             | 0      | A6            | A10           | B6            |  |  |

| A3             | 0      | A7            | A12           | B8            |  |  |

| C4             | 0      | NC Ball       | A13           | B10           |  |  |

| B3             | 0      | NC Ball       | A14           | B12           |  |  |

| A2             | 0      | NC Ball       | NC Ball       | B14           |  |  |

\* This pin is input only for the LC4064ZE.

# ispMACH 4128ZE and 4256ZE Logic Signal Connections: 144 TQFP (Cont.)

|            |             | LC4128ZE      | LC4256ZE<br>GLB/MC/Pad |  |

|------------|-------------|---------------|------------------------|--|

| Pin Number | Bank Number | GLB/MC/Pad    |                        |  |

| 43         | 0           | D9            | G4                     |  |

| 44         | 0           | D8            | G2                     |  |

| 45*        | 0           | NC            | I                      |  |

| 46         | 0           | GND (Bank 0)  | GND (Bank 0)           |  |

| 47         | 0           | VCCO (Bank 0) | VCCO (Bank 0)          |  |

| 48         | 0           | D6            | H12                    |  |

| 49         | 0           | D5            | H10                    |  |

| 50         | 0           | D4            | H8                     |  |

| 51         | 0           | D2            | H6                     |  |

| 52         | 0           | D1            | H4                     |  |

| 53         | 0           | D0            | H2                     |  |

| 54         | 0           | CLK1/I        | CLK1/I                 |  |

| 55         | 1           | GND (Bank 1)  | GND (Bank 1)           |  |

| 56         | 1           | CLK2/I        | CLK2/I                 |  |

| 57         | -           | VCC           | VCC                    |  |

| 58         | 1           | E0            | 12                     |  |

| 59         | 1           | E1            | 14                     |  |

| 60         | 1           | E2            | 16                     |  |

| 61         | 1           | E4            | 18                     |  |

| 62         | 1           | E5            | 110                    |  |

| 63         | 1           | E6            | 112                    |  |

| 64         | 1           | VCCO (Bank 1) | VCCO (Bank 1)          |  |

| 65         | 1           | GND (Bank 1)  | GND (Bank 1)           |  |

| 66         | 1           | E8            | J2                     |  |

| 67         | 1           | E9            | J4                     |  |

| 68         | 1           | E10           | J6                     |  |

| 69         | 1           | E12           | J8                     |  |

| 70         | 1           | E13           | J10                    |  |

| 71         | 1           | E14           | J12                    |  |

| 72*        | 1           | NC            | I                      |  |

| 73         | -           | GND           | GND                    |  |

| 74         | -           | TMS           | TMS                    |  |

| 75         | 1           | VCCO (Bank 1) | VCCO (Bank 1)          |  |

| 76         | 1           | F0            | K12                    |  |

| 77         | 1           | F1            | K10                    |  |

| 78         | 1           | F2            | K8                     |  |

| 79         | 1           | F4            | K6                     |  |

| 80         | 1           | F5            | K4                     |  |

| 81         | 1           | F6            | K2                     |  |

| 82         | 1           | GND (Bank 1)  | GND (Bank 1)           |  |

| 83         | 1           | F8            | L14                    |  |

| 84         | 1           | F9            | L12                    |  |

| 85         | 1           | F10           | L10                    |  |

## Figure 20. Mark Format for 64 ucBGA and 132 ucBGA Packages

| LC4064ZE<br>4UN-5I<br>Datecode | LC4128ZE<br>7UN<br>Datecode |

|--------------------------------|-----------------------------|

| Dual Mark                      | Single Mar                  |

## Lead-Free Packaging

#### Commercial

| Device   | Part Number       | Macrocells | Voltage | t <sub>PD</sub> | Package         | Pin/Ball<br>Count | I/O | Grade |

|----------|-------------------|------------|---------|-----------------|-----------------|-------------------|-----|-------|

| LC4032ZE | LC4032ZE-4TN48C   | 32         | 1.8     | 4.4             | Lead-Free TQFP  | 48                | 32  | С     |

|          | LC4032ZE-5TN48C   | 32         | 1.8     | 5.8             | Lead-Free TQFP  | 48                | 32  | С     |

|          | LC4032ZE-7TN48C   | 32         | 1.8     | 7.5             | Lead-Free TQFP  | 48                | 32  | С     |

|          | LC4032ZE-4MN64C   | 32         | 1.8     | 4.4             | Lead-Free csBGA | 64                | 32  | С     |

|          | LC4032ZE-5MN64C   | 32         | 1.8     | 5.8             | Lead-Free csBGA | 64                | 32  | С     |

|          | LC4032ZE-7MN64C   | 32         | 1.8     | 7.5             | Lead-Free csBGA | 64                | 32  | С     |

|          | LC4064ZE-4TN48C   | 64         | 1.8     | 4.7             | Lead-Free TQFP  | 48                | 32  | С     |

|          | LC4064ZE-5TN48C   | 64         | 1.8     | 5.8             | Lead-Free TQFP  | 48                | 32  | С     |

|          | LC4064ZE-7TN48C   | 64         | 1.8     | 7.5             | Lead-Free TQFP  | 48                | 32  | С     |

|          | LC4064ZE-4TN100C  | 64         | 1.8     | 4.7             | Lead-Free TQFP  | 100               | 64  | С     |

|          | LC4064ZE-5TN100C  | 64         | 1.8     | 5.8             | Lead-Free TQFP  | 100               | 64  | С     |

| LC4064ZE | LC4064ZE-7TN100C  | 64         | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | С     |

| LC40042E | LC4064ZE-4MN64C   | 64         | 1.8     | 4.7             | Lead-Free csBGA | 64                | 48  | С     |

|          | LC4064ZE-5MN64C   | 64         | 1.8     | 5.8             | Lead-Free csBGA | 64                | 48  | С     |

|          | LC4064ZE-7MN64C   | 64         | 1.8     | 7.5             | Lead-Free csBGA | 64                | 48  | С     |

|          | LC4064ZE-4MN144C  | 64         | 1.8     | 4.7             | Lead-Free csBGA | 144               | 64  | С     |

|          | LC4064ZE-5MN144C  | 64         | 1.8     | 5.8             | Lead-Free csBGA | 144               | 64  | С     |

|          | LC4064ZE-7MN144C  | 64         | 1.8     | 7.5             | Lead-Free csBGA | 144               | 64  | С     |

|          | LC4128ZE-5TN100C  | 128        | 1.8     | 5.8             | Lead-Free TQFP  | 100               | 64  | С     |

|          | LC4128ZE-7TN100C  | 128        | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | С     |

|          | LC4128ZE-5TN144C  | 128        | 1.8     | 5.8             | Lead-Free TQFP  | 144               | 96  | С     |

| LC4128ZE | LC4128ZE-7TN144C  | 128        | 1.8     | 7.5             | Lead-Free TQFP  | 144               | 96  | С     |

| LU41202E | LC4128ZE-5UMN132C | 128        | 1.8     | 5.8             | Lead-Free ucBGA | 132               | 96  | С     |

|          | LC4128ZE-7UMN132C | 128        | 1.8     | 7.5             | Lead-Free ucBGA | 132               | 96  | С     |

|          | LC4128ZE-5MN144C  | 128        | 1.8     | 5.8             | Lead-Free csBGA | 144               | 96  | С     |

|          | LC4128ZE-7MN144C  | 128        | 1.8     | 7.5             | Lead-Free csBGA | 144               | 96  | С     |

| LC4256ZE | LC4256ZE-5TN100C  | 256        | 1.8     | 5.8             | Lead-Free TQFP  | 100               | 64  | С     |

|          | LC4256ZE-7TN100C  | 256        | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | С     |

|          | LC4256ZE-5TN144C  | 256        | 1.8     | 5.8             | Lead-Free TQFP  | 144               | 96  | С     |

|          | LC4256ZE-7TN144C  | 256        | 1.8     | 7.5             | Lead-Free TQFP  | 144               | 96  | С     |

|          | LC4256ZE-5MN144C  | 256        | 1.8     | 5.8             | Lead-Free csBGA | 144               | 108 | С     |

|          | LC4256ZE-7MN144C  | 256        | 1.8     | 7.5             | Lead-Free csBGA | 144               | 108 | С     |

| Industrial |                   |            |         |                 |                 |                   |     |       |  |

|------------|-------------------|------------|---------|-----------------|-----------------|-------------------|-----|-------|--|

| Device     | Part Number       | Macrocells | Voltage | t <sub>PD</sub> | Package         | Pin/Ball<br>Count | I/O | Grade |  |

| LC4032ZE   | LC4032ZE-5TN48I   | 32         | 1.8     | 5.8             | Lead-Free TQFP  | 48                | 32  | Ι     |  |

|            | LC4032ZE-7TN48I   | 32         | 1.8     | 7.5             | Lead-Free TQFP  | 48                | 32  | Ι     |  |

|            | LC4032ZE-5MN64I   | 32         | 1.8     | 5.8             | Lead-Free csBGA | 64                | 32  | Ι     |  |

|            | LC4032ZE-7MN64I   | 32         | 1.8     | 7.5             | Lead-Free csBGA | 64                | 32  | Ι     |  |

|            | LC4064ZE-5TN48I   | 64         | 1.8     | 5.8             | Lead-Free TQFP  | 48                | 32  | Ι     |  |

|            | LC4064ZE-7TN48I   | 64         | 1.8     | 7.5             | Lead-Free TQFP  | 48                | 32  | Ι     |  |

|            | LC4064ZE-5TN100I  | 64         | 1.8     | 5.8             | Lead-Free TQFP  | 100               | 64  | Ι     |  |

|            | LC4064ZE-7TN100I  | 64         | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | Ι     |  |

|            | LC4064ZE-5MN64I   | 64         | 1.8     | 5.8             | Lead-Free csBGA | 64                | 48  | Ι     |  |

| LC4064ZE   | LC4064ZE-7MN64I   | 64         | 1.8     | 7.5             | Lead-Free csBGA | 64                | 48  | Ι     |  |

|            | LC4064ZE-5UMN64I  | 64         | 1.8     | 5.8             | Lead-Free ucBGA | 64                | 48  | Ι     |  |

|            | LC4064ZE-7UMN64I  | 64         | 1.8     | 7.5             | Lead-Free ucBGA | 64                | 48  | Ι     |  |

|            | LC4064ZE-5MN144I  | 64         | 1.8     | 5.8             | Lead-Free csBGA | 144               | 64  | Ι     |  |

|            | LC4064ZE-7MN144I  | 64         | 1.8     | 7.5             | Lead-Free csBGA | 144               | 64  | Ι     |  |

| LC4128ZE   | LC4128ZE-7TN100I  | 128        | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | I     |  |

|            | LC4128ZE-7UMN132I | 128        | 1.8     | 7.5             | Lead-Free ucBGA | 132               | 96  | Ι     |  |

|            | LC4128ZE-7TN144I  | 128        | 1.8     | 7.5             | Lead-Free TQFP  | 144               | 96  | Ι     |  |

|            | LC4128ZE-7MN144I  | 128        | 1.8     | 7.5             | Lead-Free csBGA | 144               | 96  | Ι     |  |

|            | LC4256ZE-7TN100I  | 256        | 1.8     | 7.5             | Lead-Free TQFP  | 100               | 64  | Ι     |  |

| LC4256ZE   | LC4256ZE-7TN144I  | 256        | 1.8     | 7.5             | Lead-Free TQFP  | 144               | 96  | Ι     |  |

|            | LC4256ZE-7MN144I  | 256        | 1.8     | 7.5             | Lead-Free csBGA | 144               | 108 | I     |  |

1. Contact factory for product availability.

## For Further Information

In addition to this data sheet, the following technical notes may be helpful when designing with the ispMACH 4000ZE family:

- TN1168, ispMACH 4000ZE Timing Model Design and Usage Guidelines

- TN1174, Advanced Features of the ispMACH 4000ZE Family

- TN1187, Power Estimation in ispMACH 4000ZE Devices

- Package Diagrams

## **Technical Support Assistance**

- Hotline: 1-800-LATTICE (North America)

- +1-503-268-8001 (Outside North America)

- e-mail: techsupport@latticesemi.com

- Internet: <u>www.latticesemi.com</u>