Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 56                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b120f128gm64-a |

|    | 3.10 Core and Memory                                 | .16  |

|----|------------------------------------------------------|------|

|    | 3.10.1 Processor Core                                |      |

|    | 3.10.2 Memory System Controller (MSC)                |      |

|    | 3.10.3 Linked Direct Memory Access Controller (LDMA) |      |

|    | 3.10.4 Bootloader                                    |      |

|    | 3.11 Memory Map                                      | .17  |

|    | 3.12 Configuration Summary                           | .18  |

| 4. | Electrical Specifications                            | . 19 |

|    | 4.1 Electrical Characteristics                       |      |

|    | 4.1.1 Absolute Maximum Ratings                       |      |

|    | 4.1.2 Operating Conditions                           |      |

|    | 4.1.3 Thermal Characteristics                        | .22  |

|    | 4.1.4 DC-DC Converter                                | .23  |

|    | 4.1.5 Backup Supply Domain                           | .25  |

|    | 4.1.6 Current Consumption                            |      |

|    | 4.1.7 Wake Up Times                                  |      |

|    | 4.1.8 Brown Out Detector (BOD)                       |      |

|    | 4.1.9 Oscillators                                    |      |

|    | 4.1.10 Flash Memory Characteristics                  |      |

|    | 4.1.11 General-Purpose I/O (GPIO)                    |      |

|    | 4.1.12 Voltage Monitor (VMON)                        |      |

|    | 4.1.13 Analog to Digital Converter (ADC)             |      |

|    | 4.1.14 Analog Comparator (ACMP)                      |      |

|    | 4.1.16 Capacitive Sense (CSEN)                       |      |

|    | 4.1.17 Operational Amplifier (OPAMP)                 |      |

|    | 4.1.18 LCD Driver                                    |      |

|    | 4.1.19 Pulse Counter (PCNT)                          |      |

|    | 4.1.20 Analog Port (APORT)                           |      |

|    | 4.1.21 I2C                                           |      |

|    | 4.1.22 USART SPI                                     |      |

|    | 4.2 Typical Performance Curves                       | .64  |

|    | 4.2.1 Supply Current                                 |      |

|    | 4.2.2 DC-DC Converter                                |      |

| 5. | Pin Definitions                                      | 72   |

| •  | 5.1 EFM32TG11B5xx in QFP80 Device Pinout             |      |

|    | 5.2 EFM32TG11B5xx in QFN80 Device Pinout             |      |

|    |                                                      |      |

|    | 5.3 EFM32TG11B5xx in QFP64 Device Pinout             | .78  |

|    | 5.4 EFM32TG11B3xx in QFP64 Device Pinout             | .80  |

|    | 5.5 EFM32TG11B1xx in QFP64 Device Pinout             | .82  |

|    | 5.6 EFM32TG11B5xx in QFN64 Device Pinout             | .84  |

|    | 5.7 EFM32TG11B3xx in QFN64 Device Pinout             | .86  |

|    | 5.8 FFM32TG11R1xx in OFN64 Device Pinout             | 88   |

#### 3.6.5 Controller Area Network (CAN)

The CAN peripheral provides support for communication at up to 1 Mbps over CAN protocol version 2.0 part A and B. It includes 32 message objects with independent identifier masks and retains message RAM in EM2. Automatic retransmittion may be disabled in order to support Time Triggered CAN applications.

### 3.6.6 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality such as simple logic operations (AND, OR, NOT) can be applied by the PRS to the signals. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

### 3.6.7 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface LESENSE<sup>TM</sup> is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators, ADC, and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable finite state machine which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

#### 3.7 Security Features

#### 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)

The GPCRC module implements a Cyclic Redundancy Check (CRC) function. It supports both 32-bit and 16-bit polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3), while the 16-bit polynomial can be programmed to any value, depending on the needs of the application.

#### 3.7.2 Crypto Accelerator (CRYPTO)

The Crypto Accelerator is a fast and energy-efficient autonomous hardware encryption and decryption accelerator. Tiny Gecko Series 1 devices support AES encryption and decryption with 128- or 256-bit keys, ECC over both GF(P) and GF(2m), and SHA-1 and SHA-2 (SHA-224 and SHA-256).

Supported block cipher modes of operation for AES include: ECB, CTR, CBC, PCBC, CFB, OFB, GCM, CBC-MAC, GMAC and CCM.

Supported ECC NIST recommended curves include P-192, P-224, P-256, K-163, K-233, B-163 and B-233.

The CRYPTO module allows fast processing of GCM (AES), ECC and SHA with little CPU intervention. CRYPTO also provides trigger signals for DMA read and write operations.

#### 3.7.3 True Random Number Generator (TRNG)

The TRNG module is a non-deterministic random number generator based on a full hardware solution. The TRNG is validated with NIST800-22 and AIS-31 test suites as well as being suitable for FIPS 140-2 certification (for the purposes of cryptographic key generation).

#### 3.7.4 Security Management Unit (SMU)

The Security Management Unit (SMU) allows software to set up fine-grained security for peripheral access, which is not possible in the Memory Protection Unit (MPU). Peripherals may be secured by hardware on an individual basis, such that only priveleged accesses to the peripheral's register interface will be allowed. When an access fault occurs, the SMU reports the specific peripheral involved and can optionally generate an interrupt.

### 3.8 Analog

#### 3.10 Core and Memory

#### 3.10.1 Processor Core

The ARM Cortex-M processor includes a 32-bit RISC processor integrating the following features and tasks in the system:

- ARM Cortex-M0+ RISC processor

- Memory Protection Unit (MPU) supporting up to 8 memory segments

- · Micro-Trace Buffer (MTB)

- Up to 128 kB flash program memory

- · Up to 32 kB RAM data memory

- · Configuration and event handling of all modules

- · 2-pin Serial-Wire debug interface

### 3.10.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block, whereas the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

#### 3.10.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling sophisticated operations to be implemented.

#### 3.10.4 Bootloader

All devices come pre-programmed with a UART bootloader. This bootloader resides in flash and can be erased if it is not needed. More information about the bootloader protocol and usage can be found in *AN0003: UART Bootloader*. Application notes can be found on the Silicon Labs website (www.silabs.com/32bit-appnotes) or within Simplicity Studio in the [**Documentation**] area.

# 4.1.8 Brown Out Detector (BOD)

Table 4.10. Brown Out Detector (BOD)

| Parameter              | Symbol                     | Test Condition               | Min | Тур | Max | Unit |

|------------------------|----------------------------|------------------------------|-----|-----|-----|------|

| DVDD BOD threshold     | V <sub>DVDDBOD</sub>       | DVDD rising                  | _   | _   | TBD | V    |

|                        |                            | DVDD falling (EM0/EM1)       | TBD | _   | _   | V    |

|                        |                            | DVDD falling (EM2/EM3)       | TBD | _   | _   | V    |

| DVDD BOD hysteresis    | V <sub>DVDDBOD_HYST</sub>  |                              | _   | 18  | _   | mV   |

| DVDD BOD response time | tDVDDBOD_DELAY             | Supply drops at 0.1V/µs rate | _   | 2.4 | _   | μs   |

| AVDD BOD threshold     | V <sub>AVDDBOD</sub>       | AVDD rising                  | _   | _   | TBD | V    |

|                        |                            | AVDD falling (EM0/EM1)       | TBD | _   | _   | V    |

|                        |                            | AVDD falling (EM2/EM3)       | TBD | _   | _   | V    |

| AVDD BOD hysteresis    | V <sub>AVDDBOD_HYST</sub>  |                              | _   | 20  | _   | mV   |

| AVDD BOD response time | t <sub>AVDDBOD_DELAY</sub> | Supply drops at 0.1V/µs rate | _   | 2.4 | _   | μs   |

| EM4 BOD threshold      | V <sub>EM4DBOD</sub>       | AVDD rising                  | _   | _   | TBD | V    |

|                        |                            | AVDD falling                 | TBD | _   | _   | V    |

| EM4 BOD hysteresis     | V <sub>EM4BOD_HYST</sub>   |                              | _   | 25  | _   | mV   |

| EM4 BOD response time  | t <sub>EM4BOD_DELAY</sub>  | Supply drops at 0.1V/µs rate | _   | 300 | _   | μs   |

### 4.1.9 Oscillators

### 4.1.9.1 Low-Frequency Crystal Oscillator (LFXO)

Table 4.11. Low-Frequency Crystal Oscillator (LFXO)

| Parameter                                                | Symbol               | Test Condition                                                              | Min | Тур    | Max | Unit |

|----------------------------------------------------------|----------------------|-----------------------------------------------------------------------------|-----|--------|-----|------|

| Crystal frequency                                        | f <sub>LFXO</sub>    |                                                                             | _   | 32.768 | _   | kHz  |

| Supported crystal equivalent series resistance (ESR)     | ESR <sub>LFXO</sub>  |                                                                             | _   | _      | 70  | kΩ   |

| Supported range of crystal load capacitance <sup>1</sup> | C <sub>LFXO_CL</sub> |                                                                             | 6   | _      | 18  | pF   |

| On-chip tuning cap range <sup>2</sup>                    | C <sub>LFXO_T</sub>  | On each of LFXTAL_N and LFXTAL_P pins                                       | 8   | _      | 40  | pF   |

| On-chip tuning cap step size                             | SS <sub>LFXO</sub>   |                                                                             | _   | 0.25   | _   | pF   |

| Current consumption after startup <sup>3</sup>           | I <sub>LFXO</sub>    | ESR = 70 kOhm, $C_L$ = 7 pF,<br>GAIN <sup>4</sup> = 2, AGC <sup>4</sup> = 1 | _   | 273    | _   | nA   |

| Start- up time                                           | t <sub>LFXO</sub>    | ESR = 70 kOhm, $C_L = 7 pF$ ,<br>$GAIN^4 = 2$                               | _   | 308    | _   | ms   |

- 1. Total load capacitance as seen by the crystal.

- 2. The effective load capacitance seen by the crystal will be  $C_{LFXO\_T}$  /2. This is because each XTAL pin has a tuning cap and the two caps will be seen in series by the crystal.

- 3. Block is supplied by AVDD if ANASW = 0, or DVDD if ANASW=1 in EMU\_PWRCTRL register.

- 4. In CMU\_LFXOCTRL register.

### 4.1.10 Flash Memory Characteristics<sup>5</sup>

Table 4.17. Flash Memory Characteristics<sup>5</sup>

| Parameter                                   | Symbol               | Test Condition                                | Min   | Тур | Max | Unit   |

|---------------------------------------------|----------------------|-----------------------------------------------|-------|-----|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                                               | 10000 | _   | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T ≤ 85 °C                                     | 10    | _   | _   | years  |

|                                             |                      | T ≤ 125 °C                                    | 10    | _   | _   | years  |

| Word (32-bit) programming time              | t <sub>W_PROG</sub>  | Burst write, 128 words, average time per word | 20    | 26  | 32  | μs     |

|                                             |                      | Single word                                   | 59    | 68  | 83  | μs     |

| Page erase time <sup>4</sup>                | t <sub>PERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Device erase time <sup>2 3</sup>            | t <sub>DERASE</sub>  | T ≤ 85 °C                                     | _     | 54  | 70  | ms     |

|                                             |                      | T ≤ 125 °C                                    | _     | 54  | 75  | ms     |

| Erase current <sup>6</sup>                  | I <sub>ERASE</sub>   | Page Erase                                    | _     | _   | 1.7 | mA     |

|                                             |                      | Mass or Device Erase                          | _     | _   | 2.0 | mA     |

| Write current <sup>6</sup>                  | I <sub>WRITE</sub>   |                                               | _     | _   | 3.5 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                                               | 1.62  | _   | 3.6 | V      |

- 1. Mass erase is issued by the CPU and erases all flash.

- 2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

- 3. From setting the DEVICEERASE bit in AAP\_CMD to 1 until the ERASEBUSY bit in AAP\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 4. From setting the ERASEPAGE bit in MSC\_WRITECMD to 1 until the BUSY bit in MSC\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 5. Flash data retention information is published in the Quarterly Quality and Reliability Report.

- 6. Measured at 25 °C.

| Parameter                                         | Symbol                    | Test Condition                                             | Min | Тур   | Max | Unit   |

|---------------------------------------------------|---------------------------|------------------------------------------------------------|-----|-------|-----|--------|

| ADC clock frequency                               | f <sub>ADCCLK</sub>       |                                                            | _   | _     | 16  | MHz    |

| Throughput rate                                   | f <sub>ADCRATE</sub>      |                                                            | _   | _     | 1   | Msps   |

| Conversion time <sup>1</sup>                      | t <sub>ADCCONV</sub>      | 6 bit                                                      | _   | 7     | _   | cycles |

|                                                   |                           | 8 bit                                                      | _   | 9     | _   | cycles |

|                                                   |                           | 12 bit                                                     | _   | 13    | _   | cycles |

| Startup time of reference generator and ADC core  | tadcstart                 | WARMUPMODE <sup>4</sup> = NORMAL                           | _   | _     | 5   | μs     |

| generator and ADC core                            |                           | WARMUPMODE <sup>4</sup> = KEEPIN-<br>STANDBY               | _   | _     | 2   | μs     |

|                                                   |                           | WARMUPMODE <sup>4</sup> = KEEPINSLO-<br>WACC               | _   | _     | 1   | μs     |

| SNDR at 1Msps and f <sub>IN</sub> = 10kHz         | SNDR <sub>ADC</sub>       | Internal reference <sup>7</sup> , differential measurement | TBD | 67    | _   | dB     |

|                                                   |                           | External reference <sup>6</sup> , differential measurement | _   | 68    | _   | dB     |

| Spurious-free dynamic range (SFDR)                | SFDR <sub>ADC</sub>       | 1 MSamples/s, 10 kHz full-scale sine wave                  | _   | 75    | _   | dB     |

| Differential non-linearity (DNL)                  | DNL <sub>ADC</sub>        | 12 bit resolution, No missing codes                        | TBD | _     | TBD | LSB    |

| Integral non-linearity (INL),<br>End point method | INL <sub>ADC</sub>        | 12 bit resolution                                          | TBD | _     | TBD | LSB    |

| Offset error                                      | V <sub>ADCOFFSETERR</sub> |                                                            | TBD | 0     | TBD | LSB    |

| Gain error in ADC                                 | V <sub>ADCGAIN</sub>      | Using internal reference                                   | _   | -0.2  | TBD | %      |

|                                                   |                           | Using external reference                                   | _   | -1    | _   | %      |

| Temperature sensor slope                          | V <sub>TS_SLOPE</sub>     |                                                            | _   | -1.84 | _   | mV/°C  |

- 1. Derived from ADCCLK.

- 2. PSRR is referenced to AVDD when ANASW=0 and to DVDD when ANASW=1 in EMU\_PWRCTRL.

- 3. In ADCn\_BIASPROG register.

- 4. In ADCn\_CNTL register.

- 5. The absolute voltage allowed at any ADC input is dictated by the power rail supplied to on-chip circuitry, and may be lower than the effective full scale voltage. All ADC inputs are limited to the ADC supply (AVDD or DVDD depending on EMU\_PWRCTRL\_ANASW). Any ADC input routed through the APORT will further be limited by the IOVDD supply to the pin.

- 6. External reference is 1.25 V applied externally to ADCnEXTREFP, with the selection CONF in the SINGLECTRL\_REF or SCANCTRL\_REF register field and VREFP in the SINGLECTRLX\_VREFSEL or SCANCTRLX\_VREFSEL field. The differential input range with this configuration is ± 1.25 V.

- 7. Internal reference option used corresponds to selection 2V5 in the SINGLECTRL\_REF or SCANCTRL\_REF register field. The differential input range with this configuration is ± 1.25 V. Typical value is characterized using full-scale sine wave input. Minimum value is production-tested using sine wave input at 1.5 dB lower than full scale.

# 4.1.14 Analog Comparator (ACMP)

Table 4.21. Analog Comparator (ACMP)

| Parameter                                                      | Symbol               | Test Condition                                                      | Min | Тур | Max                           | Unit |

|----------------------------------------------------------------|----------------------|---------------------------------------------------------------------|-----|-----|-------------------------------|------|

| Input voltage range                                            | V <sub>ACMPIN</sub>  | ACMPVDD = ACMPn_CTRL_PWRSEL <sup>1</sup>                            | _   | _   | V <sub>ACMPVDD</sub>          | V    |

| Supply voltage                                                 | V <sub>ACMPVDD</sub> | BIASPROG <sup>4</sup> $\leq$ 0x10 or FULL-<br>BIAS <sup>4</sup> = 0 | 1.8 | _   | V <sub>VREGVDD</sub> _<br>MAX | V    |

|                                                                |                      | $0x10 < BIASPROG^4 \le 0x20$ and FULLBIAS <sup>4</sup> = 1          | 2.1 | _   | V <sub>VREGVDD</sub> _        | V    |

| Active current not including                                   | I <sub>ACMP</sub>    | BIASPROG <sup>4</sup> = 1, FULLBIAS <sup>4</sup> = 0                | _   | 50  | _                             | nA   |

| voltage reference <sup>2</sup>                                 |                      | BIASPROG <sup>4</sup> = 0x10, FULLBIAS <sup>4</sup><br>= 0          | _   | 306 | _                             | nA   |

|                                                                |                      | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup> = 1             | _   | 6.5 | _                             | μΑ   |

|                                                                |                      | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup> = 1             | _   | 74  | TBD                           | μΑ   |

| Current consumption of internal voltage reference <sup>2</sup> | I <sub>ACMPREF</sub> | VLP selected as input using 2.5 V<br>Reference / 4 (0.625 V)        | _   | 50  | _                             | nA   |

|                                                                |                      | VLP selected as input using VDD                                     | _   | 20  | _                             | nA   |

|                                                                |                      | VBDIV selected as input using 1.25 V reference / 1                  | _   | 4.1 | _                             | μΑ   |

|                                                                |                      | VADIV selected as input using VDD/1                                 | _   | 2.4 | _                             | μΑ   |

| Parameter                                               | Symbol                   | Test Condition                                                                              | Min | Тур  | Max | Unit |

|---------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------|-----|------|-----|------|

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal 1.25V reference                                            | _   | 60.4 | _   | dB   |

| Noise band limited to 250 kHz                           |                          | 500 ksps, single-ended, internal 2.5V reference                                             | _   | 61.6 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                               | _   | 64.0 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 1.25V reference                                            | _   | 63.3 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 2.5V reference                                             | _   | 64.4 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                  | _   | 65.8 | _   | dB   |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference                                            | _   | 65.3 | _   | dB   |

| Noise band limited to 22 kHz                            | z                        | 500 ksps, single-ended, internal 2.5V reference                                             | _   | 66.7 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                  | _   | 68.5 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 1.25V reference                                            | _   | 67.8 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 2.5V reference                                             | _   | 69.0 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                               | _   | 70.0 | _   | dB   |

| Total harmonic distortion                               | THD                      |                                                                                             | _   | 70.2 | _   | dB   |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                                                             | TBD | _    | TBD | LSB  |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                                                             | TBD | _    | TBD | LSB  |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T = 25 °C                                                                                   | TBD | _    | TBD | mV   |

|                                                         |                          | Across operating temperature range                                                          | TBD | _    | TBD | mV   |

| Gain error <sup>5</sup>                                 | $V_{GAIN}$               | T = 25 °C, Low-noise internal reference (REFSEL = 1V25LN or 2V5LN)                          | TBD | _    | TBD | %    |

|                                                         |                          | Across operating temperature range, Low-noise internal reference (REFSEL = 1V25LN or 2V5LN) | TBD | _    | TBD | %    |

| External load capactiance,<br>OUTSCALE=0                | C <sub>LOAD</sub>        |                                                                                             | _   | _    | 75  | pF   |

# 4.1.16 Capacitive Sense (CSEN)

Table 4.23. Capacitive Sense (CSEN)

| Parameter                                                                | Symbol                | Test Condition                                                                                                                                                  | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Single conversion time (1x                                               | t <sub>CNV</sub>      | 12-bit SAR Conversions                                                                                                                                          | _   | 20.2 | _   | μs   |

| accumulation)                                                            |                       | 16-bit SAR Conversions                                                                                                                                          | _   | 26.4 | _   | μs   |

|                                                                          |                       | Delta Modulation Conversion (single comparison)                                                                                                                 | _   | 1.55 | _   | μs   |

| Maximum external capacitive load                                         | C <sub>EXTMAX</sub>   | CS0CG=7 (Gain = 1x), including routing parasitics                                                                                                               | _   | 68   | _   | pF   |

|                                                                          |                       | CS0CG=0 (Gain = 10x), including routing parasitics                                                                                                              | _   | 680  | _   | pF   |

| Maximum external series impedance                                        | R <sub>EXTMAX</sub>   |                                                                                                                                                                 | _   | 1    | _   | kΩ   |

| Supply current, EM2 bonded conversions, WARMUP-MODE=NORMAL, WAR-MUPCNT=0 | CSEN_BOND             | 12-bit SAR conversions, 20 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                      | _   | 326  | _   | nA   |

|                                                                          |                       | Delta Modulation conversions, 20 ms conversion rate, CS0CG=7 (Gain = 1x), 10 channels bonded (total capacitance of 330 pF) <sup>1</sup>                         | _   | 226  | _   | nA   |

|                                                                          |                       | 12-bit SAR conversions, 200 ms conversion rate, CS0CG=7 (Gain = 1x), 10 channels bonded (total capacitance of 330 pF) <sup>1</sup>                              | _   | 33   | _   | nA   |

|                                                                          |                       | Delta Modulation conversions,<br>200 ms conversion rate,<br>CS0CG=7 (Gain = 1x), 10 chan-<br>nels bonded (total capacitance of<br>330 pF) <sup>1</sup>          | _   | 25   | _   | nA   |

| Supply current, EM2 scan conversions, WARMUP-MODE=NORMAL, WAR-MUDCALT-0  | I <sub>CSEN_EM2</sub> | 12-bit SAR conversions, 20 ms scan rate, CS0CG=0 (Gain = 10x), 8 samples per scan <sup>1</sup>                                                                  | _   | 690  | _   | nA   |

| MUPCNT=0                                                                 |                       | Delta Modulation conversions, 20 ms scan rate, 8 comparisons per sample (DMCR = 1, DMR = 2), CS0CG=0 (Gain = 10x), 8 samples per scan <sup>1</sup>              | _   | 515  | _   | nA   |

|                                                                          |                       | 12-bit SAR conversions, 200 ms scan rate, CS0CG=0 (Gain = 10x), 8 samples per scan <sup>1</sup>                                                                 | _   | 79   | _   | nA   |

|                                                                          |                       | Delta Modulation conversions,<br>200 ms scan rate, 8 comparisons<br>per sample (DMCR = 1, DMR =<br>2), CS0CG=0 (Gain = 10x), 8<br>samples per scan <sup>1</sup> | _   | 57   | _   | nA   |

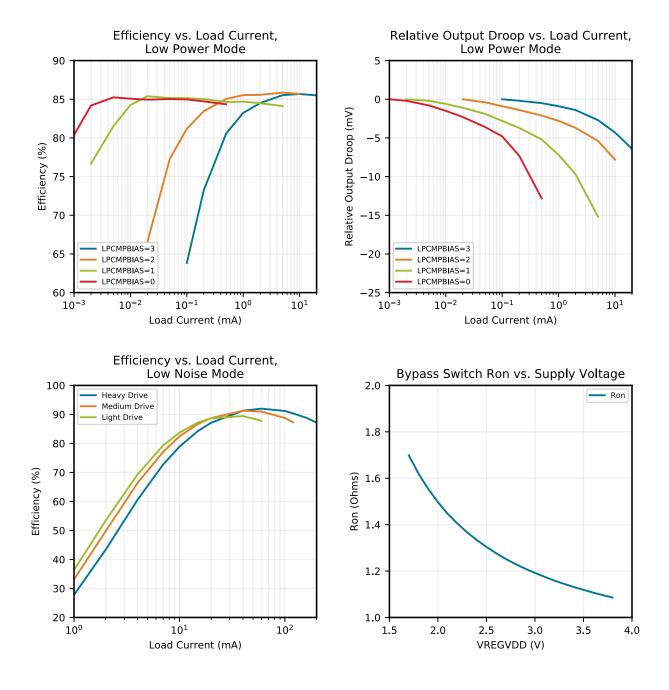

### 4.2.2 DC-DC Converter

Default test conditions: CCM mode, LDCDC =  $4.7 \mu H$ , CDCDC =  $4.7 \mu F$ , VDCDC\_I = 3.3 V, VDCDC\_O = 1.8 V, FDCDC\_LN = 7 MHz

Figure 4.8. DC-DC Converter Typical Performance Characteristics

### 5. Pin Definitions

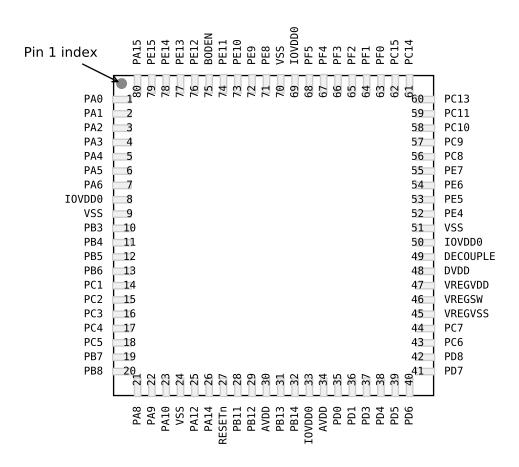

### 5.1 EFM32TG11B5xx in QFP80 Device Pinout

Figure 5.1. EFM32TG11B5xx in QFP80 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

Table 5.1. EFM32TG11B5xx in QFP80 Device Pinout

| Pin Name | Pin(s) | Description | Pin Name | Pin(s)              | Description                |

|----------|--------|-------------|----------|---------------------|----------------------------|

| PA0      | 1      | GPIO        | PA1      | 2                   | GPIO                       |

| PA2      | 3      | GPIO        | PA3      | 4                   | GPIO                       |

| PA4      | 5      | GPIO        | PA5      | 6                   | GPIO                       |

| PA6      | 7      | GPIO        | IOVDD0   | 8<br>33<br>50<br>69 | Digital IO power supply 0. |

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description |

|----------|--------|-------------|----------|--------|-------------|

| PE12     | 76     | GPIO        | PE13     | 77     | GPIO        |

| PE14     | 78     | GPIO        | PE15     | 79     | GPIO        |

| PA15     | 80     | GPIO        |          |        |             |

<sup>1.</sup> GPIO with 5V tolerance are indicated by (5V).

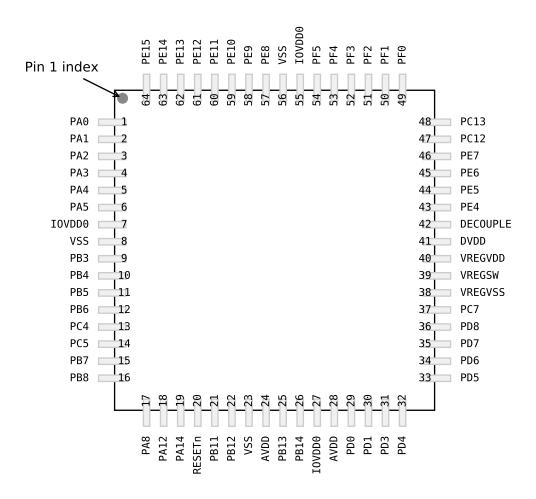

### 5.3 EFM32TG11B5xx in QFP64 Device Pinout

Figure 5.3. EFM32TG11B5xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

Table 5.3. EFM32TG11B5xx in QFP64 Device Pinout

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>27<br>55 | Digital IO power supply 0. | VSS      | 8<br>23<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

| Alternate     | LOCATION |       |                                    |

|---------------|----------|-------|------------------------------------|

| Functionality | 0 - 3    | 4 - 7 | Description                        |

| LCD_SEG35     | 0: PC9   |       | LCD segment line 35.               |

| LES_ALTEX0    | 0: PD6   |       | LESENSE alternate excite output 0. |

| LES_ALTEX1    | 0: PD7   |       | LESENSE alternate excite output 1. |

| LES_ALTEX2    | 0: PA3   |       | LESENSE alternate excite output 2. |

| LES_ALTEX3    | 0: PA4   |       | LESENSE alternate excite output 3. |

| LES_ALTEX4    | 0: PA5   |       | LESENSE alternate excite output 4. |

| LES_ALTEX5    | 0: PE11  |       | LESENSE alternate excite output 5. |

| LES_ALTEX6    | 0: PE12  |       | LESENSE alternate excite output 6. |

| LES_ALTEX7    | 0: PE13  |       | LESENSE alternate excite output 7. |

| LES_CH0       | 0: PC0   |       | LESENSE channel 0.                 |

| LES_CH1       | 0: PC1   |       | LESENSE channel 1.                 |

| LES_CH2       | 0: PC2   |       | LESENSE channel 2.                 |

| LES_CH3       | 0: PC3   |       | LESENSE channel 3.                 |

| Alternate     | LOCATION                                |                            |                                                      |

|---------------|-----------------------------------------|----------------------------|------------------------------------------------------|

| Functionality | 0 - 3                                   | 4 - 7                      | Description                                          |

|               | 0: PA0                                  | 4: PF0                     |                                                      |

| TIM0_CC0      | 2: PD1<br>3: PB6                        | 5: PC4<br>6: PA8<br>7: PA1 | Timer 0 Capture Compare input / output channel 0.    |

| TIM0_CC1      | 0: PA1                                  | 4: PF1<br>5: PC5           |                                                      |

|               | 2: PD2<br>3: PC0                        | 6: PA9<br>7: PA0           | Timer 0 Capture Compare input / output channel 1.    |

|               | 0: PA2                                  | 4: PF2                     |                                                      |

| TIM0_CC2      | 2: PD3<br>3: PC1                        | 6: PA10<br>7: PA13         | Timer 0 Capture Compare input / output channel 2.    |

| TIM0_CDTI0    | 0: PA3<br>1: PC13<br>2: PF3<br>3: PC2   | 4: PB7                     | Timer 0 Complimentary Dead Time Insertion channel 0. |

| TIM0_CDTI1    | 0: PA4<br>1: PC14<br>2: PF4<br>3: PC3   | 4: PB8                     | Timer 0 Complimentary Dead Time Insertion channel 1. |

| TIM0_CDTI2    | 0: PA5<br>1: PC15<br>2: PF5<br>3: PC4   | 4: PB11                    | Timer 0 Complimentary Dead Time Insertion channel 2. |

| TIM1_CC0      | 0: PC13<br>1: PE10                      | 4: PD6<br>5: PF2           | Timer 1 Capture Compare input / output channel 0.    |

|               | 3: PB7                                  |                            |                                                      |

| TIM1_CC1      | 0: PC14<br>1: PE11                      | 4: PD7<br>5: PF3           | Timer 1 Capture Compare input / output channel 1.    |

|               | 3: PB8                                  |                            |                                                      |

| TIM1_CC2      | 0: PC15<br>1: PE12                      | 4: PC13<br>5: PF4          | Timer 1 Capture Compare input / output channel 2.    |

|               | 3: PB11                                 |                            |                                                      |

| TIM1_CC3      | 0: PC12<br>1: PE13<br>2: PB3<br>3: PB12 | 4: PC14<br>6: PF5          | Timer 1 Capture Compare input / output channel 3.    |

| U0_CTS        | 2: PA5<br>3: PC13                       | 4: PB7<br>5: PD5           | UART0 Clear To Send hardware flow control input.     |

| U0_RTS        | 2: PA6<br>3: PC12                       | 4: PB8<br>5: PD6           | UART0 Request To Send hardware flow control output.  |

| U0_RX         | 2: PA4<br>3: PC15                       | 4: PC5<br>5: PF2<br>6: PE4 | UART0 Receive input.                                 |

| Alternate                      | LOCATION                                 |                             |                                                                    |

|--------------------------------|------------------------------------------|-----------------------------|--------------------------------------------------------------------|

| Functionality                  | 0 - 3                                    | 4 - 7                       | Description                                                        |

| VDAC0_OUT0 /<br>OPA0_OUT       | 0: PB11                                  |                             | Digital to Analog Converter DAC0 output channel number 0.          |

| VDAC0_OUT0ALT<br>/ OPA0_OUTALT | 0: PC0<br>1: PC1<br>2: PC2<br>3: PC3     | 4: PD0                      | Digital to Analog Converter DAC0 alternative output for channel 0. |

| VDAC0_OUT1 /<br>OPA1_OUT       | 0: PB12                                  |                             | Digital to Analog Converter DAC0 output channel number 1.          |

| VDAC0_OUT1ALT<br>/ OPA1_OUTALT | 0: PC12<br>1: PC13<br>2: PC14<br>3: PC15 | 4: PD1                      | Digital to Analog Converter DAC0 alternative output for channel 1. |

| WTIM0_CC0                      | 0: PE4<br>1: PA6                         | 4: PC15<br>6: PB3<br>7: PC1 | Wide timer 0 Capture Compare input / output channel 0.             |

| WTIM0_CC1                      | 0: PE5                                   | 4: PF0<br>6: PB4<br>7: PC2  | Wide timer 0 Capture Compare input / output channel 1.             |

| WTIM0_CC2                      | 0: PE6                                   | 4: PF1<br>6: PB5<br>7: PC3  | Wide timer 0 Capture Compare input / output channel 2.             |

| WTIM0_CDTI0                    | 0: PE10<br>2: PA12                       | 4: PD4                      | Wide timer 0 Complimentary Dead Time Insertion channel 0.          |

| WTIM0_CDTI1                    | 0: PE11<br>2: PA13                       | 4: PD5                      | Wide timer 0 Complimentary Dead Time Insertion channel 1.          |

| WTIM0_CDTI2                    | 0: PE12<br>2: PA14                       | 4: PD6                      | Wide timer 0 Complimentary Dead Time Insertion channel 2.          |

| WTIM1_CC0                      | 0: PB13<br>1: PD2<br>2: PD6<br>3: PC7    | 5: PE7                      | Wide timer 1 Capture Compare input / output channel 0.             |

| WTIM1_CC1                      | 0: PB14<br>1: PD3<br>2: PD7              | 4: PE4                      | Wide timer 1 Capture Compare input / output channel 1.             |

| WTIM1_CC2                      | 0: PD0<br>1: PD4<br>2: PD8               | 4: PE5                      | Wide timer 1 Capture Compare input / output channel 2.             |

| Alternate     | LOCATION                   |        |                                                        |

|---------------|----------------------------|--------|--------------------------------------------------------|

| Functionality | 0 - 3                      | 4 - 7  | Description                                            |

| WTIM1_CC3     | 0: PD1<br>1: PD5<br>2: PC6 | 4: PE6 | Wide timer 1 Capture Compare input / output channel 3. |

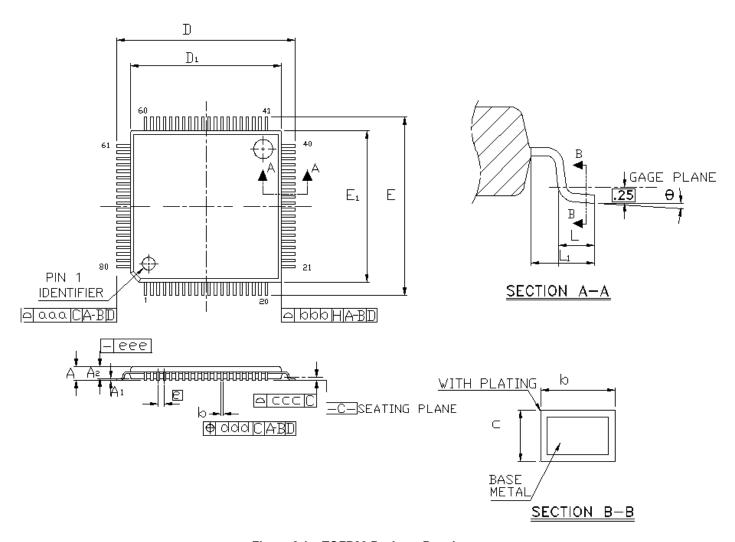

# 6. TQFP80 Package Specifications

# 6.1 TQFP80 Package Dimensions

Figure 6.1. TQFP80 Package Drawing

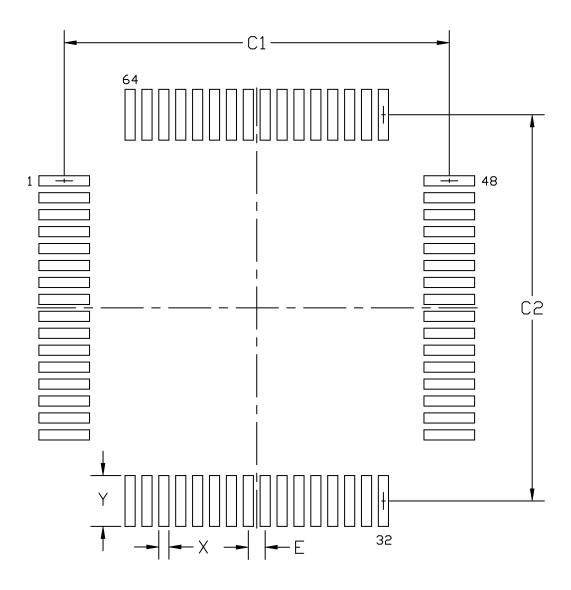

# 8.2 TQFP64 PCB Land Pattern

Figure 8.2. TQFP64 PCB Land Pattern Drawing