Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

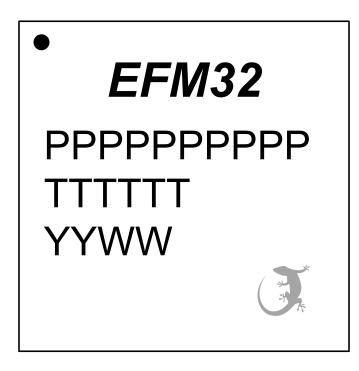

| Product Status             | Discontinued at Digi-Key                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 37                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

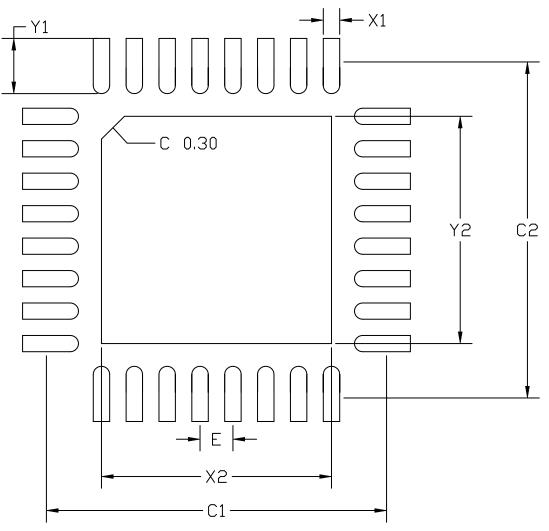

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b120f128gq48-ar |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4. Electrical Specifications

#### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on  $T_{AMB}$ =25 °C and  $V_{DD}$ = 3.3 V, by production test and/or technology characterization.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

Refer to 4.1.2.1 General Operating Conditions for more details about operational supply and temperature limits.

#### 4.1.1 Absolute Maximum Ratings

Stresses above those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

| Symbol                | Test Condition                                                                                                                                              | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Тур                                                  | Мах                                                  | Unit                                                 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| T <sub>STG</sub>      |                                                                                                                                                             | -50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                    | 150                                                  | °C                                                   |

| V <sub>DDMAX</sub>    |                                                                                                                                                             | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | 3.8                                                  | V                                                    |

| VDDRAMPMAX            |                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                    | 1                                                    | V / µs                                               |

| V <sub>DIGPIN</sub>   | 5V tolerant GPIO pins <sup>1 2 3</sup>                                                                                                                      | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                    | Min of 5.25<br>and IOVDD<br>+2                       | V                                                    |

|                       | LCD pins <sup>3</sup>                                                                                                                                       | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                    | Min of 3.8<br>and IOVDD<br>+2                        | V                                                    |

|                       | Standard GPIO pins                                                                                                                                          | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | IOVDD+0.3                                            | V                                                    |

| IVDDMAX               | Source                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                    | 200                                                  | mA                                                   |

| IVSSMAX               | Sink                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                    | 200                                                  | mA                                                   |

| I <sub>IOMAX</sub>    | Sink                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                    | 50                                                   | mA                                                   |

|                       | Source                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                    | 50                                                   | mA                                                   |

| I <sub>IOALLMAX</sub> | Sink                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                    | 200                                                  | mA                                                   |

|                       | Source                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      | 200                                                  | mA                                                   |

| TJ                    | -G grade devices                                                                                                                                            | -40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      | 105                                                  | °C                                                   |

|                       | Laurada da da a                                                                                                                                             | -40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      | 405                                                  | °C                                                   |

|                       | T <sub>STG</sub><br>V <sub>DDMAX</sub><br>V <sub>DDRAMPMAX</sub><br>V <sub>DIGPIN</sub><br>I <sub>VDDMAX</sub><br>I <sub>VSSMAX</sub><br>I <sub>IOMAX</sub> | TSTGImage: style | $\begin{array}{llllllllllllllllllllllllllllllllllll$ | $\begin{array}{llllllllllllllllllllllllllllllllllll$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

#### Table 4.1. Absolute Maximum Ratings

#### Note:

1. When a GPIO pin is routed to the analog module through the APORT, the maximum voltage = IOVDD.

Valid for IOVDD in valid operating range or when IOVDD is undriven (high-Z). If IOVDD is connected to a low-impedance source below the valid operating range (e.g. IOVDD shorted to VSS), the pin voltage maximum is IOVDD + 0.3 V, to avoid exceeding the maximum IO current specifications.

3. To operate above the IOVDD supply rail, over-voltage tolerance must be enabled according to the GPIO\_Px\_OVTDIS register. Pins with over-voltage tolerance disabled have the same limits as Standard GPIO.

## 4.1.2 Operating Conditions

When assigning supply sources, the following requirements must be observed:

- VREGVDD must be greater than or equal to AVDD, DVDD and all IOVDD supplies.

- VREGVDD = AVDD

- DVDD ≤ AVDD

- IOVDD ≤ AVDD

## 4.1.10 Flash Memory Characteristics<sup>5</sup>

| Parameter                                   | Symbol               | Test Condition                                | Min   | Тур | Мах | Unit   |

|---------------------------------------------|----------------------|-----------------------------------------------|-------|-----|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                                               | 10000 | _   | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T ≤ 85 °C                                     | 10    | _   | _   | years  |

|                                             |                      | T ≤ 125 °C                                    | 10    |     | _   | years  |

| Word (32-bit) programming time              | tw_prog              | Burst write, 128 words, average time per word | 20    | 26  | 32  | μs     |

|                                             |                      | Single word                                   | 59    | 68  | 83  | μs     |

| Page erase time <sup>4</sup>                | t <sub>PERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Device erase time <sup>2 3</sup>            | t <sub>DERASE</sub>  | T ≤ 85 °C                                     | _     | 54  | 70  | ms     |

|                                             |                      | T ≤ 125 °C                                    | _     | 54  | 75  | ms     |

| Erase current <sup>6</sup>                  | I <sub>ERASE</sub>   | Page Erase                                    | _     | _   | 1.7 | mA     |

|                                             |                      | Mass or Device Erase                          | _     |     | 2.0 | mA     |

| Write current <sup>6</sup>                  | I <sub>WRITE</sub>   |                                               | —     |     | 3.5 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                                               | 1.62  | _   | 3.6 | V      |

## Table 4.17. Flash Memory Characteristics<sup>5</sup>

# Note:

- 1. Mass erase is issued by the CPU and erases all flash.

- 2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

- 3. From setting the DEVICEERASE bit in AAP\_CMD to 1 until the ERASEBUSY bit in AAP\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 4. From setting the ERASEPAGE bit in MSC\_WRITECMD to 1 until the BUSY bit in MSC\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 5. Flash data retention information is published in the Quarterly Quality and Reliability Report.

6. Measured at 25 °C.

| Parameter                                         | Symbol                | Test Condition                                             | Min | Тур   | Max | Unit   |

|---------------------------------------------------|-----------------------|------------------------------------------------------------|-----|-------|-----|--------|

| ADC clock frequency                               | f <sub>ADCCLK</sub>   |                                                            | _   | _     | 16  | MHz    |

| Throughput rate                                   | <b>f</b> ADCRATE      |                                                            | _   | _     | 1   | Msps   |

| Conversion time <sup>1</sup>                      | t <sub>ADCCONV</sub>  | 6 bit                                                      | _   | 7     | _   | cycles |

|                                                   |                       | 8 bit                                                      | _   | 9     | _   | cycles |

|                                                   |                       | 12 bit                                                     | —   | 13    | _   | cycles |

| Startup time of reference generator and ADC core  | t <sub>ADCSTART</sub> | WARMUPMODE <sup>4</sup> = NORMAL                           | —   | —     | 5   | μs     |

| generator and ADC core                            |                       | WARMUPMODE <sup>4</sup> = KEEPIN-<br>STANDBY               | _   |       | 2   | μs     |

|                                                   |                       | WARMUPMODE <sup>4</sup> = KEEPINSLO-<br>WACC               | _   |       | 1   | μs     |

| SNDR at 1Msps and f <sub>IN</sub> =<br>10kHz      | SNDR <sub>ADC</sub>   | Internal reference <sup>7</sup> , differential measurement | TBD | 67    | _   | dB     |

|                                                   |                       | External reference <sup>6</sup> , differential measurement | _   | 68    | _   | dB     |

| Spurious-free dynamic range (SFDR)                | SFDR <sub>ADC</sub>   | 1 MSamples/s, 10 kHz full-scale sine wave                  | _   | 75    | _   | dB     |

| Differential non-linearity (DNL)                  | DNL <sub>ADC</sub>    | 12 bit resolution, No missing co-<br>des                   | TBD |       | TBD | LSB    |

| Integral non-linearity (INL),<br>End point method | INL <sub>ADC</sub>    | 12 bit resolution                                          | TBD |       | TBD | LSB    |

| Offset error                                      | VADCOFFSETERR         |                                                            | TBD | 0     | TBD | LSB    |

| Gain error in ADC                                 | VADCGAIN              | Using internal reference                                   | _   | -0.2  | TBD | %      |

|                                                   |                       | Using external reference                                   | _   | -1    | _   | %      |

| Temperature sensor slope                          | V <sub>TS_SLOPE</sub> |                                                            | _   | -1.84 | _   | mV/°C  |

Note:

1. Derived from ADCCLK.

2. PSRR is referenced to AVDD when ANASW=0 and to DVDD when ANASW=1 in EMU\_PWRCTRL.

3. In ADCn\_BIASPROG register.

4. In ADCn CNTL register.

5. The absolute voltage allowed at any ADC input is dictated by the power rail supplied to on-chip circuitry, and may be lower than the effective full scale voltage. All ADC inputs are limited to the ADC supply (AVDD or DVDD depending on EMU PWRCTRL ANASW). Any ADC input routed through the APORT will further be limited by the IOVDD supply to the pin.

6. External reference is 1.25 V applied externally to ADCnEXTREFP, with the selection CONF in the SINGLECTRL\_REF or SCANCTRL\_REF register field and VREFP in the SINGLECTRLX\_VREFSEL or SCANCTRLX\_VREFSEL field. The differential input range with this configuration is ± 1.25 V.

7. Internal reference option used corresponds to selection 2V5 in the SINGLECTRL\_REF or SCANCTRL\_REF register field. The differential input range with this configuration is ± 1.25 V. Typical value is characterized using full-scale sine wave input. Minimum value is production-tested using sine wave input at 1.5 dB lower than full scale.

## 4.1.14 Analog Comparator (ACMP)

| Parameter                                                           | Symbol              | Test Condition                                               | Min | Тур | Мах                         | Unit |

|---------------------------------------------------------------------|---------------------|--------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                                 | V <sub>ACMPIN</sub> | ACMPVDD =<br>ACMPn_CTRL_PWRSEL <sup>1</sup>                  | _   | _   | V <sub>ACMPVDD</sub>        | V    |

| Supply voltage                                                      | VACMPVDD            | $BIASPROG^4 \le 0x10 \text{ or } FULL-BIAS^4 = 0$            | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                                     |                     | $0x10 < BIASPROG^4 \le 0x20$ and FULLBIAS <sup>4</sup> = 1   | 2.1 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Active current not including                                        | I <sub>ACMP</sub>   | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                          | —   | 50  | —                           | nA   |

| voltage reference <sup>2</sup>                                      |                     | $BIASPROG^{4} = 0x10, FULLBIAS^{4} = 0$                      |     | 306 | _                           | nA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1   |     | 6.5 | —                           | μA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1   | _   | 74  | TBD                         | μA   |

| Current consumption of inter-<br>nal voltage reference <sup>2</sup> | IACMPREF            | VLP selected as input using 2.5 V<br>Reference / 4 (0.625 V) | _   | 50  | _                           | nA   |

|                                                                     |                     | VLP selected as input using VDD                              | _   | 20  | _                           | nA   |

|                                                                     |                     | VBDIV selected as input using 1.25 V reference / 1           | _   | 4.1 | _                           | μA   |

|                                                                     |                     | VADIV selected as input using VDD/1                          |     | 2.4 | -                           | μA   |

## Table 4.21. Analog Comparator (ACMP)

| Parameter                                               | Symbol                   | Test Condition                                                                                         | Min | Тур  | Мах | Unit |

|---------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| ratio (1 kHz sine wave),                                | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal 1.25V reference                                                       | _   | 60.4 | _   | dB   |

| Noise band limited to 250<br>kHz                        |                          | 500 ksps, single-ended, internal<br>2.5V reference                                                     | —   | 61.6 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 64.0 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 63.3 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 64.4 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 65.8 |     | dB   |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference                                                       | _   | 65.3 |     | dB   |

| Noise band limited to 22 kHz                            |                          | 500 ksps, single-ended, internal<br>2.5V reference                                                     | _   | 66.7 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 68.5 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 67.8 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 69.0 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 70.0 |     | dB   |

| Total harmonic distortion                               | THD                      |                                                                                                        |     | 70.2 |     | dB   |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                                                                        | TBD | _    | TBD | LSB  |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                                                                        | TBD | _    | TBD | LSB  |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T = 25 °C                                                                                              | TBD | _    | TBD | mV   |

|                                                         |                          | Across operating temperature range                                                                     | TBD | _    | TBD | mV   |

| Gain error <sup>5</sup>                                 | V <sub>GAIN</sub>        | T = 25 °C, Low-noise internal ref-<br>erence (REFSEL = 1V25LN or<br>2V5LN)                             | TBD | _    | TBD | %    |

|                                                         |                          | Across operating temperature<br>range, Low-noise internal refer-<br>ence (REFSEL = 1V25LN or<br>2V5LN) | TBD | _    | TBD | %    |

| External load capactiance,<br>OUTSCALE=0                | C <sub>LOAD</sub>        |                                                                                                        | —   | _    | 75  | pF   |

## 4.1.17 Operational Amplifier (OPAMP)

Unless otherwise indicated, specified conditions are: Non-inverting input configuration, VDD = 3.3 V, DRIVESTRENGTH = 2, MAIN-OUTEN = 1,  $C_{LOAD}$  = 75 pF with OUTSCALE = 0, or  $C_{LOAD}$  = 37.5 pF with OUTSCALE = 1. Unit gain buffer and 3X-gain connection as specified in table footnotes<sup>8 1</sup>.

| Parameter                     | Symbol            | Test Condition                                                                                                                                                                | Min              | Тур  | Мах                   | Unit |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----------------------|------|

| Supply voltage (from AVDD)    | V <sub>OPA</sub>  | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | 2                | _    | 3.8                   | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | 1.62             |      | 3.8                   | V    |

| Input voltage                 | V <sub>IN</sub>   | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | $V_{VSS}$        | _    | V <sub>OPA</sub>      | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | V <sub>VSS</sub> | _    | V <sub>OPA</sub> -1.2 | V    |

| Input impedance               | R <sub>IN</sub>   |                                                                                                                                                                               | 100              | _    | _                     | MΩ   |

| Output voltage                | V <sub>OUT</sub>  |                                                                                                                                                                               | V <sub>VSS</sub> |      | V <sub>OPA</sub>      | V    |

| Load capacitance <sup>2</sup> | C <sub>LOAD</sub> | OUTSCALE = 0                                                                                                                                                                  | _                |      | 75                    | pF   |

|                               |                   | OUTSCALE = 1                                                                                                                                                                  | _                | _    | 37.5                  | pF   |

| Output impedance              | R <sub>OUT</sub>  | DRIVESTRENGTH = 2 or 3, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -8 mA <<br>I <sub>OUT</sub> < 8 mA, Buffer connection,<br>Full supply range         | _                | 0.25 | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -400 µA $<$<br>I <sub>OUT</sub> $<$ 400 µA, Buffer connection,<br>Full supply range | _                | 0.6  | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 2 or 3, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -2 mA $<$<br>I <sub>OUT</sub> $<$ 2 mA, Buffer connection,<br>Full supply range     | _                | 0.4  | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -100 µA $<$<br>I <sub>OUT</sub> $<$ 100 µA, Buffer connection,<br>Full supply range | _                | 1    | _                     | Ω    |

| Internal closed-loop gain     | G <sub>CL</sub>   | Buffer connection                                                                                                                                                             | TBD              | 1    | TBD                   | -    |

|                               |                   | 3x Gain connection                                                                                                                                                            | TBD              | 2.99 | TBD                   | -    |

|                               |                   | 16x Gain connection                                                                                                                                                           | TBD              | 15.7 | TBD                   | -    |

| Active current <sup>4</sup>   | I <sub>OPA</sub>  | DRIVESTRENGTH = 3, OUT-<br>SCALE = 0                                                                                                                                          | _                | 580  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 2, OUT-<br>SCALE = 0                                                                                                                                          | _                | 176  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 1, OUT-<br>SCALE = 0                                                                                                                                          | _                | 13   | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 0, OUT-<br>SCALE = 0                                                                                                                                          | _                | 4.7  | -                     | μA   |

### Table 4.24. Operational Amplifier (OPAMP)

| Pin Name | Pin(s) | Description                                                                                              | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|----------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                                                                                                     | PC5      | 14       | GPIO                                                                                                                                                                                                        |

| PB7      | 15     | GPIO                                                                                                     | PB8      | 16       | GPIO                                                                                                                                                                                                        |

| PA8      | 17     | GPIO                                                                                                     | PA9      | 18       | GPIO                                                                                                                                                                                                        |

| PA10     | 19     | GPIO                                                                                                     | RESETn   | 20       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21     | GPIO                                                                                                     | AVDD     | 23<br>27 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 24     | GPIO                                                                                                     | PB14     | 25       | GPIO                                                                                                                                                                                                        |

| PD0      | 28     | GPIO (5V)                                                                                                | PD1      | 29       | GPIO                                                                                                                                                                                                        |

| PD2      | 30     | GPIO (5V)                                                                                                | PD3      | 31       | GPIO                                                                                                                                                                                                        |

| PD4      | 32     | GPIO                                                                                                     | PD5      | 33       | GPIO                                                                                                                                                                                                        |

| PD6      | 34     | GPIO                                                                                                     | PD7      | 35       | GPIO                                                                                                                                                                                                        |

| PD8      | 36     | GPIO                                                                                                     | PC6      | 37       | GPIO                                                                                                                                                                                                        |

| PC7      | 38     | GPIO                                                                                                     | DVDD     | 39       | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PC8      | 41       | GPIO                                                                                                                                                                                                        |

| PC9      | 42     | GPIO                                                                                                     | PC10     | 43       | GPIO (5V)                                                                                                                                                                                                   |

| PC11     | 44     | GPIO (5V)                                                                                                | PC12     | 45       | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 46     | GPIO (5V)                                                                                                | PC14     | 47       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 48     | GPIO (5V)                                                                                                | PF0      | 49       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50     | GPIO (5V)                                                                                                | PF2      | 51       | GPIO                                                                                                                                                                                                        |

| PF3      | 52     | GPIO                                                                                                     | PF4      | 53       | GPIO                                                                                                                                                                                                        |

| PF5      | 54     | GPIO                                                                                                     | PE8      | 57       | GPIO                                                                                                                                                                                                        |

| PE9      | 58     | GPIO                                                                                                     | PE10     | 59       | GPIO                                                                                                                                                                                                        |

| PE11     | 60     | GPIO                                                                                                     | PE12     | 61       | GPIO                                                                                                                                                                                                        |

| PE13     | 62     | GPIO                                                                                                     | PE14     | 63       | GPIO                                                                                                                                                                                                        |

| PE15     | 64     | GPIO                                                                                                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s)   | Description                                                                                                                                                                                                 | Pin Name | Pin(s) | Description                   |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-------------------------------|

| PB8      | 11       | GPIO                                                                                                                                                                                                        | PA8      | 12     | GPIO                          |

| PA12     | 13       | GPIO                                                                                                                                                                                                        | PA14     | 14     | GPIO                          |

| RESETn   | 15       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB11     | 16     | GPIO                          |

| AVDD     | 18<br>22 | Analog power supply.                                                                                                                                                                                        | PB13     | 19     | GPIO                          |

| PB14     | 20       | GPIO                                                                                                                                                                                                        | PD4      | 23     | GPIO                          |

| PD5      | 24       | GPIO                                                                                                                                                                                                        | PD6      | 25     | GPIO                          |

| PD7      | 26       | GPIO                                                                                                                                                                                                        | PD8      | 27     | GPIO                          |

| VREGVSS  | 28       | Voltage regulator VSS                                                                                                                                                                                       | VREGSW   | 29     | DCDC regulator switching node |

| VREGVDD  | 30       | Voltage regulator VDD input                                                                                                                                                                                 | DVDD     | 31     | Digital power supply.         |

| DECOUPLE | 32       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    | PE4      | 33     | GPIO                          |

| PE5      | 34       | GPIO                                                                                                                                                                                                        | PE6      | 35     | GPIO                          |

| PE7      | 36       | GPIO                                                                                                                                                                                                        | PF0      | 37     | GPIO (5V)                     |

| PF1      | 38       | GPIO (5V)                                                                                                                                                                                                   | PF2      | 39     | GPIO                          |

| PF3      | 40       | GPIO                                                                                                                                                                                                        | PF4      | 41     | GPIO                          |