Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 53                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b120f128gq64-a |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ordering Code           | Flash<br>(kB) | RAM<br>(kB) | DC-DC<br>Con-<br>verter | LCD | GPIO | Package | Temp Range    |

|-------------------------|---------------|-------------|-------------------------|-----|------|---------|---------------|

| EFM32TG11B320F128GQ48-A | 128           | 32          | No                      | Yes | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B320F128IQ48-A | 128           | 32          | No                      | Yes | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B340F64GQ48-A  | 64            | 32          | No                      | Yes | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B340F64IQ48-A  | 64            | 32          | No                      | Yes | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B120F128GM64-A | 128           | 32          | No                      | No  | 56   | QFN64   | -40 to +85°C  |

| EFM32TG11B120F128GQ64-A | 128           | 32          | No                      | No  | 53   | QFP64   | -40 to +85°C  |

| EFM32TG11B120F128IM64-A | 128           | 32          | No                      | No  | 56   | QFN64   | -40 to +125°C |

| EFM32TG11B120F128IQ64-A | 128           | 32          | No                      | No  | 53   | QFP64   | -40 to +125°C |

| EFM32TG11B140F64GM64-A  | 64            | 32          | No                      | No  | 56   | QFN64   | -40 to +85°C  |

| EFM32TG11B140F64GQ64-A  | 64            | 32          | No                      | No  | 53   | QFP64   | -40 to +85°C  |

| EFM32TG11B140F64IM64-A  | 64            | 32          | No                      | No  | 56   | QFN64   | -40 to +125°C |

| EFM32TG11B140F64IQ64-A  | 64            | 32          | No                      | No  | 53   | QFP64   | -40 to +125°C |

| EFM32TG11B120F128GQ48-A | 128           | 32          | No                      | No  | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B120F128IQ48-A | 128           | 32          | No                      | No  | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B140F64GQ48-A  | 64            | 32          | No                      | No  | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B140F64IQ48-A  | 64            | 32          | No                      | No  | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B120F128GM32-A | 128           | 32          | No                      | No  | 24   | QFN32   | -40 to +85°C  |

| EFM32TG11B120F128IM32-A | 128           | 32          | No                      | No  | 24   | QFN32   | -40 to +125°C |

| EFM32TG11B140F64GM32-A  | 64            | 32          | No                      | No  | 24   | QFN32   | -40 to +85°C  |

| EFM32TG11B140F64IM32-A  | 64            | 32          | No                      | No  | 24   | QFN32   | -40 to +125°C |

# 3. System Overview

### 3.1 Introduction

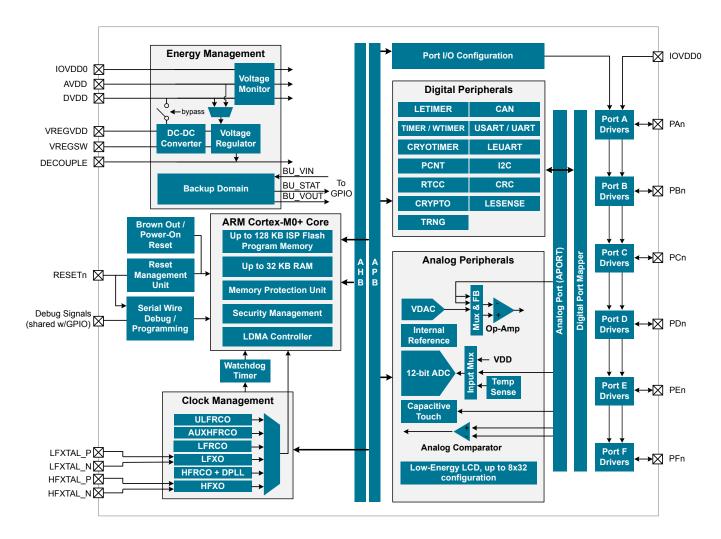

The Tiny Gecko Series 1 product family is well suited for any battery operated application as well as other systems requiring high performance and low energy consumption. This section gives a short introduction to the MCU system. The detailed functional description can be found in the Tiny Gecko Series 1 Reference Manual. Any behavior that does not conform to the specifications in this data sheet or the functional descriptions in the Tiny Gecko Series 1 Reference Manual are detailed in the EFM32TG11 Errata document.

A block diagram of the Tiny Gecko Series 1 family is shown in Figure 3.1 Detailed EFM32TG11 Block Diagram on page 10. The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Detailed EFM32TG11 Block Diagram

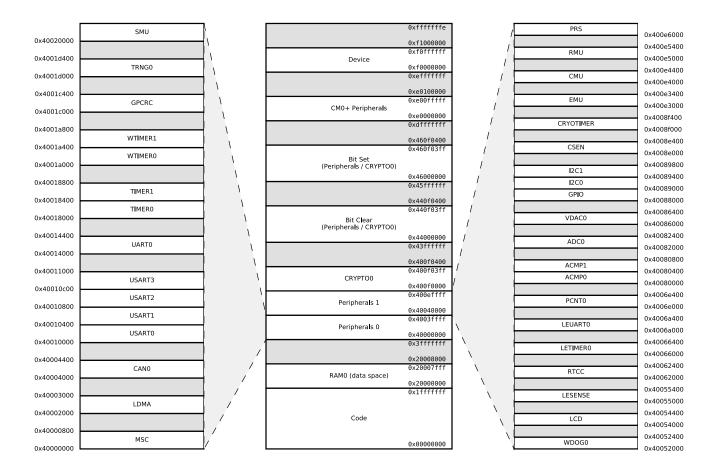

Figure 3.3. EFM32TG11 Memory Map — Peripherals

#### 3.12 Configuration Summary

The features of the EFM32TG11 are a subset of the feature set described in the device reference manual. The table below describes device specific implementation of the features. Remaining modules support full configuration.

| Table 3.2. | Configuration | Summary |

|------------|---------------|---------|

|------------|---------------|---------|

| Module  | Configuration               | Pin Connections                 |

|---------|-----------------------------|---------------------------------|

| USART0  | IrDA, SmartCard             | US0_TX, US0_RX, US0_CLK, US0_CS |

| USART1  | I <sup>2</sup> S, SmartCard | US1_TX, US1_RX, US1_CLK, US1_CS |

| USART2  | IrDA, SmartCard, High-Speed | US2_TX, US2_RX, US2_CLK, US2_CS |

| USART3  | I <sup>2</sup> S, SmartCard | US3_TX, US3_RX, US3_CLK, US3_CS |

| TIMER0  | with DTI                    | TIM0_CC[2:0], TIM0_CDTI[2:0]    |

| TIMER1  | -                           | TIM1_CC[3:0]                    |

| WTIMER0 | with DTI                    | WTIM0_CC[2:0], WTIM0_CDTI[2:0]  |

| WTIMER1 | -                           | WTIM1_CC[3:0]                   |

# 4.1.2 Operating Conditions

When assigning supply sources, the following requirements must be observed:

- VREGVDD must be greater than or equal to AVDD, DVDD and all IOVDD supplies.

- VREGVDD = AVDD

- DVDD ≤ AVDD

- IOVDD ≤ AVDD

| Parameter                                                                                                                                                                                                                                                                                 | Symbol                | Test Condition                                                        | Min                 | Тур              | Мах           | Unit    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------|---------------------|------------------|---------------|---------|

| Note:                                                                                                                                                                                                                                                                                     |                       |                                                                       |                     |                  |               |         |

|                                                                                                                                                                                                                                                                                           |                       | mode is calculated using $R_{BYP}$ _min+ILOAD * $R_{BYP}$ _max.       | from the DCDC spec  | cification table | e. Requiremer | nts for |

| 2. VREGVDD must be                                                                                                                                                                                                                                                                        | e tied to AVDD. Both  | VREGVDD and AVDD minimum                                              | voltages must be sa | atisfied for the | part to opera | te.     |

| 3. The system designer should consult the characteristic specs of the capacitor used on DECOUPLE to ensure its capacitance val-<br>ue stays within the specified bounds across temperature and DC bias.                                                                                   |                       |                                                                       |                     |                  |               |         |

| 4. VSCALE0 to VSCALE2 voltage change transitions occur at a rate of 10 mV / usec for approximately 20 usec. During this transition, peak currents will be dependent on the value of the DECOUPLE output capacitor, from 35 mA (with a 1 μF capacitor) to 70 mA (with a 2.7 μF capacitor). |                       |                                                                       |                     |                  |               |         |

| 5. When the CSEN pe                                                                                                                                                                                                                                                                       | ripheral is used with | chopping enabled (CSEN_CTRI                                           | CHOPEN = ENAB       | LE), IOVDD n     | nust be equal | to AVDE |

| cation. T <sub>A</sub> (max) =                                                                                                                                                                                                                                                            |                       | due to device self-heating, which<br>x PowerDissipation). Refer to th |                     | •                | -             |         |

# 4.1.3 Thermal Characteristics

| Parameter                  | Symbol                          | Test Condition                    | Min | Тур  | Мах | Unit |

|----------------------------|---------------------------------|-----------------------------------|-----|------|-----|------|

| Thermal resistance, QFN32  | THETA <sub>JA_QFN32</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 25.7 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 23.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 21.3 | _   | °C/W |

| Thermal resistance, TQFP48 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 44.1 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP48</sub>         | 4-Layer PCB, Air velocity = 1 m/s |     | 43.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 42.3 | _   | °C/W |

| Thermal resistance, QFN64  | THETA <sub>JA_QFN64</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP64 | THE-<br>TA <sub>JA_TQFP64</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 37.3 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 35.6 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 33.8 | _   | °C/W |

| Thermal resistance, QFN80  | THETA <sub>JA_QFN80</sub>       | 4-Layer PCB, Air velocity = 0 m/s |     | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP80 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 49.3 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP80</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 44.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 42.6 | _   | °C/W |

## Table 4.3. Thermal Characteristics

| Parameter                                                                                                               | Symbol  | Test Condition                                                                                          | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled,<br>DCDC in LP mode <sup>3</sup> | IPD1_VS | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>4</sup> |     | 0.18 | _   | μA   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled,<br>DCDC in LP mode <sup>3</sup> | IPD2_VS | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>4</sup> |     | 0.18 |     | μA   |

Note:

1. DCDC Low Noise CCM Mode = Light Drive (PFETCNT=NFETCNT=3), F=6.4 MHz (RCOBAND=4), ANASW=DVDD.

2. DCDC Low Noise DCM Mode = Light Drive (PFETCNT=NFETCNT=3), F=3.0 MHz (RCOBAND=0), ANASW=DVDD.

3. DCDC Low Power Mode = Medium Drive (PFETCNT=NFETCNT=7), LPOSCDIV=1, LPCMPBIASEM234H=0, LPCLIMILIM-SEL=1, ANASW=DVDD.

4. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.3 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

5. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

# 4.1.9.2 High-Frequency Crystal Oscillator (HFXO)

| Parameter                                                | Symbol               | Test Condition                                          | Min | Тур  | Max  | Unit |

|----------------------------------------------------------|----------------------|---------------------------------------------------------|-----|------|------|------|

| Crystal frequency                                        | f <sub>HFXO</sub>    |                                                         | 4   | —    | 48   | MHz  |

| Supported crystal equivalent                             | ESR <sub>HFXO</sub>  | 48 MHz crystal                                          | _   | _    | 50   | Ω    |

| series resistance (ESR)                                  |                      | 24 MHz crystal                                          |     | _    | 150  | Ω    |

|                                                          |                      | 4 MHz crystal                                           | _   | _    | 180  | Ω    |

| Supported range of crystal load capacitance <sup>1</sup> | C <sub>HFXO_CL</sub> |                                                         | TBD | _    | TBD  | pF   |

| Nominal on-chip tuning cap range <sup>2</sup>            | C <sub>HFXO_T</sub>  | On each of HFXTAL_N and HFXTAL_P pins                   | 8.7 | _    | 51.7 | pF   |

| On-chip tuning capacitance step                          | SS <sub>HFXO</sub>   |                                                         | _   | 0.08 | _    | pF   |

| Startup time                                             | t <sub>HFXO</sub>    | 48 MHz crystal, ESR = 50 Ohm,<br>$C_L = 8 pF$           | _   | 350  | _    | μs   |

|                                                          |                      | 24 MHz crystal, ESR = 150 Ohm,<br>C <sub>L</sub> = 6 pF | _   | 700  | _    | μs   |

|                                                          |                      | 4 MHz crystal, ESR = 180 Ohm,<br>$C_L$ = 18 pF          | _   | 3    | _    | ms   |

| Current consumption after                                | I <sub>HFXO</sub>    | 48 MHz crystal                                          | _   | 880  | _    | μA   |

| startup                                                  |                      | 24 MHz crystal                                          |     | 420  | _    | μA   |

|                                                          |                      | 4 MHz crystal                                           |     | 80   | _    | μA   |

### Table 4.12. High-Frequency Crystal Oscillator (HFXO)

# Note:

1. Total load capacitance as seen by the crystal.

2. The effective load capacitance seen by the crystal will be C<sub>HFXO\_T</sub> /2. This is because each XTAL pin has a tuning cap and the two caps will be seen in series by the crystal.

| Parameter                                 | Symbol                 | Test Condition                                             | Min | Тур      | Мах | Unit |

|-------------------------------------------|------------------------|------------------------------------------------------------|-----|----------|-----|------|

| Hysteresis (V <sub>CM</sub> = 1.25 V,     | V <sub>ACMPHYST</sub>  | HYSTSEL <sup>5</sup> = HYST0                               | TBD | 0        | TBD | mV   |

| $BIASPROG^4 = 0x10, FULL-BIAS^4 = 1)$     |                        | HYSTSEL <sup>5</sup> = HYST1                               | TBD | 18       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST2                               | TBD | 33       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST3                               | TBD | 46       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST4                               | TBD | 57       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST5                               | TBD | 68       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST6                               | TBD | 79       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST7                               | TBD | 90       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST8                               | TBD | 0        | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST9                               | TBD | -18      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST10                              | TBD | -33      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST11                              | TBD | -45      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST12                              | TBD | -57      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST13                              | TBD | -67      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST14                              | TBD | -78      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST15                              | TBD | -88      | TBD | mV   |

| Comparator delay <sup>3</sup>             | t <sub>acmpdelay</sub> | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                        | _   | 30       | _   | μs   |

|                                           |                        | $BIASPROG^4 = 0x10, FULLBIAS^4 = 0$                        | _   | 3.7      | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1 |     | 360      | _   | ns   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1 | _   | 35       | _   | ns   |

| Offset voltage                            | VACMPOFFSET            | BIASPROG <sup>4</sup> =0x10, FULLBIAS <sup>4</sup><br>= 1  | TBD | _        | TBD | mV   |

| Reference voltage                         | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | TBD | 1.25     | TBD | V    |

|                                           |                        | Internal 2.5 V reference                                   | TBD | 2.5      | TBD | V    |

| Capacitive sense internal re-<br>sistance | R <sub>CSRES</sub>     | CSRESSEL <sup>6</sup> = 0                                  | —   | infinite | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 1                                  | —   | 15       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 2                                  |     | 27       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 3                                  | —   | 39       |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 4                                  |     | 51       |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 5                                  | _   | 100      | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 6                                  |     | 162      | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 7                                  |     | 235      | _   | kΩ   |

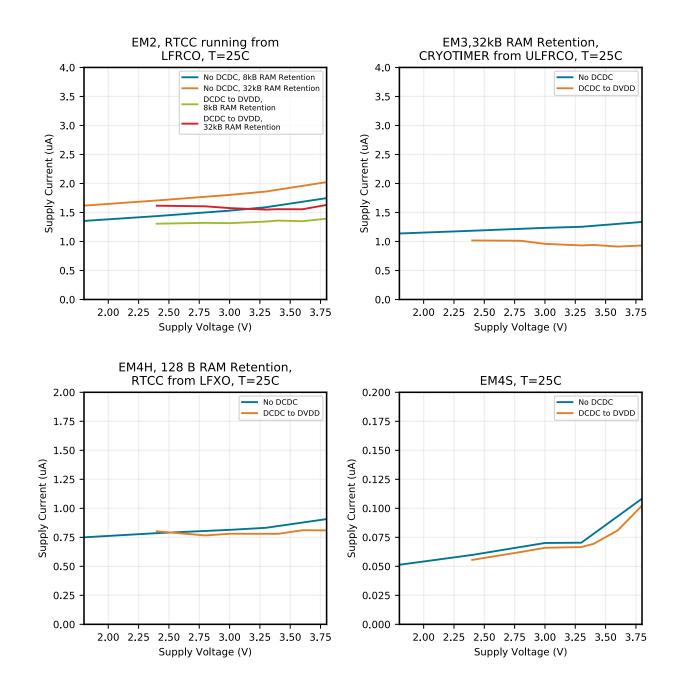

Figure 4.7. EM2, EM3, EM4H and EM4S Typical Supply Current vs. Supply

| Pin Name | Pin(s)   | Description                                                                                              | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|----------------------------------------------------------------------------------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13       | GPIO                                                                                                     | PC5      | 14     | GPIO                                                                                                                                                                                                        |

| PB7      | 15       | GPIO                                                                                                     | PB8      | 16     | GPIO                                                                                                                                                                                                        |

| PA8      | 17       | GPIO                                                                                                     | PA12     | 18     | GPIO                                                                                                                                                                                                        |

| PA14     | 19       | GPIO                                                                                                     | RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21       | GPIO                                                                                                     | PB12     | 22     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.                                                                                     | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26       | GPIO                                                                                                     | PD0      | 29     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 30       | GPIO                                                                                                     | PD3      | 31     | GPIO                                                                                                                                                                                                        |

| PD4      | 32       | GPIO                                                                                                     | PD5      | 33     | GPIO                                                                                                                                                                                                        |

| PD6      | 34       | GPIO                                                                                                     | PD7      | 35     | GPIO                                                                                                                                                                                                        |

| PD8      | 36       | GPIO                                                                                                     | PC7      | 37     | GPIO                                                                                                                                                                                                        |

| VREGVSS  | 38       | Voltage regulator VSS                                                                                    | VREGSW   | 39     | DCDC regulator switching node                                                                                                                                                                               |

| VREGVDD  | 40       | Voltage regulator VDD input                                                                              | DVDD     | 41     | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 42       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PE4      | 43     | GPIO                                                                                                                                                                                                        |

| PE5      | 44       | GPIO                                                                                                     | PE6      | 45     | GPIO                                                                                                                                                                                                        |

| PE7      | 46       | GPIO                                                                                                     | PC12     | 47     | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 48       | GPIO (5V)                                                                                                | PF0      | 49     | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50       | GPIO (5V)                                                                                                | PF2      | 51     | GPIO                                                                                                                                                                                                        |

| PF3      | 52       | GPIO                                                                                                     | PF4      | 53     | GPIO                                                                                                                                                                                                        |

| PF5      | 54       | GPIO                                                                                                     | PE8      | 57     | GPIO                                                                                                                                                                                                        |

| PE9      | 58       | GPIO                                                                                                     | PE10     | 59     | GPIO                                                                                                                                                                                                        |

| PE11     | 60       | GPIO                                                                                                     | PE12     | 61     | GPIO                                                                                                                                                                                                        |

| PE13     | 62       | GPIO                                                                                                     | PE14     | 63     | GPIO                                                                                                                                                                                                        |

| PE15     | 64       | GPIO                                                                                                     |          |        |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

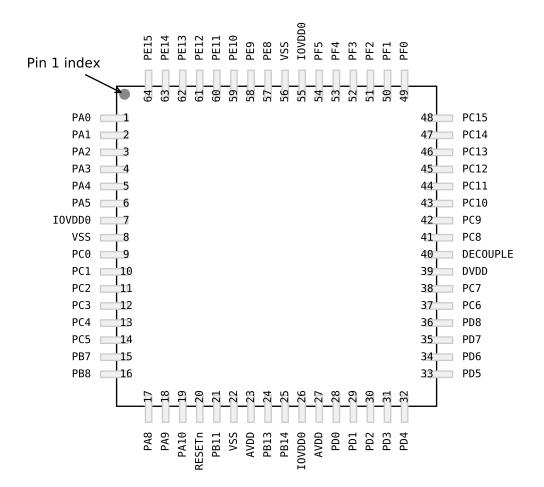

#### Figure 5.5. EFM32TG11B1xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.5. EFM32TG11B1xx in QFP64 Device Pi | nout |

|---------------------------------------------|------|

|---------------------------------------------|------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>26<br>55 | Digital IO power supply 0. | VSS      | 8<br>22<br>56 | Ground      |

| PC0      | 9             | GPIO (5V)                  | PC1      | 10            | GPIO (5V)   |

| PC2      | 11            | GPIO (5V)                  | PC3      | 12            | GPIO (5V)   |

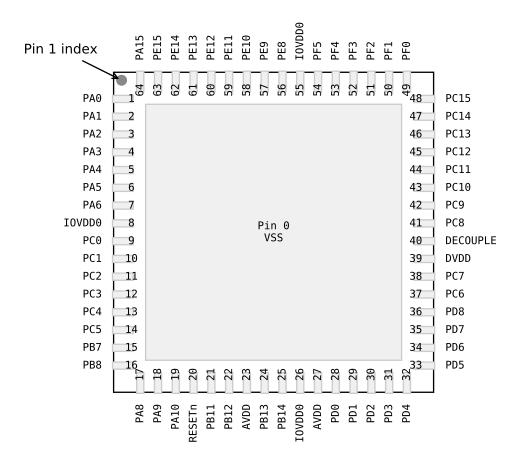

### Figure 5.8. EFM32TG11B1xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>26<br>55 | Digital IO power supply 0. | PC0      | 9      | GPIO (5V)   |

| PC1      | 10            | GPIO (5V)                  | PC2      | 11     | GPIO (5V)   |

| Pin Name | Pin(s)   | Description                                                                                                                                                                                                 | Pin Name     | Pin(s) | Description                   |  |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|-------------------------------|--|

| PB8      | 11       | GPIO                                                                                                                                                                                                        | PA8          | 12     | GPIO                          |  |

| PA12     | 13       | GPIO                                                                                                                                                                                                        | PA14         | 14     | GPIO                          |  |

| RESETn   | 15       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |              | GPIO   |                               |  |

| AVDD     | 18<br>22 | Analog power supply.                                                                                                                                                                                        | PB13         | 19     | GPIO                          |  |

| PB14     | 20       | GPIO                                                                                                                                                                                                        | PD4          | 23     | GPIO                          |  |

| PD5      | 24       | GPIO                                                                                                                                                                                                        | PD6          | 25     | GPIO                          |  |

| PD7      | 26       | GPIO                                                                                                                                                                                                        | PD8          | 27     | GPIO                          |  |

| VREGVSS  | 28       | Voltage regulator VSS                                                                                                                                                                                       | VREGSW       | 29     | DCDC regulator switching node |  |

| VREGVDD  | 30       | Voltage regulator VDD input                                                                                                                                                                                 | DVDD         | 31     | Digital power supply.         |  |

| DECOUPLE | 32       | Decouple output for on-chip voltage<br>regulator. An external decoupling ca-<br>pacitor is required at this pin.                                                                                            | PE4          | 33     | B GPIO                        |  |

| PE5      | 34       | GPIO                                                                                                                                                                                                        | PE6          | 35     | GPIO                          |  |

| PE7      | 36       | GPIO                                                                                                                                                                                                        | PF0          | 37     | GPIO (5V)                     |  |

| PF1      | 38       | GPIO (5V)                                                                                                                                                                                                   | PF2          | 39     | GPIO                          |  |

| PF3      | 40       | GPIO                                                                                                                                                                                                        | PF4          | 41     | GPIO                          |  |

| PF5      | 42       | GPIO                                                                                                                                                                                                        | PE10         | 45     | GPIO                          |  |

| PE11     | 46       | GPIO                                                                                                                                                                                                        | PE12 47 GPIO |        | GPIO                          |  |

| PE13     | 48       | GPIO                                                                                                                                                                                                        |              |        |                               |  |

1. GPIO with 5V tolerance are indicated by (5V).

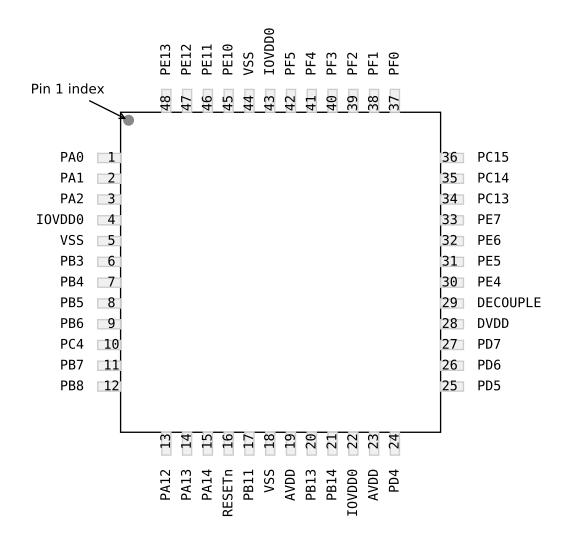

#### Figure 5.10. EFM32TG11B3xx in QFP48 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.10. | EFM32TG11B3xx in | <b>QFP48 Device Pinout</b> |

|-------------|------------------|----------------------------|

|-------------|------------------|----------------------------|

| Pin Name | Pin(s)        | Description | Pin Name | Pin(s)        | Description                |  |

|----------|---------------|-------------|----------|---------------|----------------------------|--|

| PA0      | 1             | GPIO        | PA1      | 2             | GPIO                       |  |

| PA2      | 3             | GPIO        | IOVDD0   | 4<br>22<br>43 | Digital IO power supply 0. |  |

| VSS      | 5<br>18<br>44 | Ground      | PB3      | 6             | GPIO                       |  |

| PB4      | 7             | GPIO        | PB5      | 8             | GPIO                       |  |

| PB6      | 9             | GPIO        | PC4      | 10            | GPIO                       |  |

| Pin Name              | Pin(s)      | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |  |

|-----------------------|-------------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PA14                  | 8           | GPIO                          | RESETn   | 9      | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |  |

| PB11                  | 10          | GPIO                          | AVDD     | 11     | Analog power supply.                                                                                                                                                                                        |  |

| PB13                  | 12          | GPIO                          | PB14     | 13     | GPIO                                                                                                                                                                                                        |  |

| PD4                   | 15          | GPIO                          | PD5      | 16     | GPIO                                                                                                                                                                                                        |  |

| PD6                   | 17          | GPIO                          | PD7      | 18     | GPIO                                                                                                                                                                                                        |  |

| VREGSW                | 20          | DCDC regulator switching node | VREGVDD  | 21     | Voltage regulator VDD input                                                                                                                                                                                 |  |

| DVDD                  | 22          | Digital power supply.         | DECOUPLE | 23     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |  |

| PE4                   | 24          | GPIO                          | PE5      | 25     | GPIO                                                                                                                                                                                                        |  |

| PC15                  | 26          | GPIO (5V)                     | PF0      | 27     | GPIO (5V)                                                                                                                                                                                                   |  |

| PF1                   | 28          | GPIO (5V)                     | PF2      | 29     | GPIO                                                                                                                                                                                                        |  |

| PE11                  | 31          | GPIO                          | PE12     | 32     | GPIO                                                                                                                                                                                                        |  |

| Note:<br>1. GPIO with | n 5V tolera | nce are indicated by (5V).    |          |        |                                                                                                                                                                                                             |  |

| Pin Name | Pin(s) | Description           | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |  |

|----------|--------|-----------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PB8      | 8      | GPIO                  | RESETn   | 9        | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |  |

| PB11     | 10     | GPIO                  | AVDD     | 11<br>15 | Analog power supply.                                                                                                                                                                                        |  |

| PB13     | 12     | GPIO                  | PB14     | 13       | GPIO                                                                                                                                                                                                        |  |

| PD4      | 16     | GPIO                  | PD5      | 17       | GPIO                                                                                                                                                                                                        |  |

| PD6      | 18     | GPIO                  | PD7      | 19       | GPIO                                                                                                                                                                                                        |  |

| DVDD     | 20     | Digital power supply. | DECOUPLE | 21       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |  |

| PC13     | 22     | GPIO (5V)             | PC14     | 23       | GPIO (5V)                                                                                                                                                                                                   |  |

| PC15     | 24     | GPIO (5V)             | PF0      | 25       | GPIO (5V)                                                                                                                                                                                                   |  |

| PF1      | 26     | GPIO (5V)             | PF2      | 27       | GPIO                                                                                                                                                                                                        |  |

| PE10     | 29     | GPIO                  | PE11     | 30       | GPIO                                                                                                                                                                                                        |  |

| PE12     | 31     | GPIO                  | PE13     | 32       | GPIO                                                                                                                                                                                                        |  |

| Note:    |        | ,                     |          |          |                                                                                                                                                                                                             |  |

1. GPIO with 5V tolerance are indicated by (5V).

### 5.14 GPIO Functionality Table

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of each GPIO pin, followed by the functionality available on that pin. Refer to 5.15 Alternate Functionality Overview for a list of GPIO locations available for each function.

| GPIO Name | Pin Alternate Functionality / Description                  |                                              |                                                                                     |                                                            |  |  |  |

|-----------|------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

|           | Analog                                                     | Timers                                       | Communication                                                                       | Other                                                      |  |  |  |

| PA0       | BUSBY BUSAX<br>LCD_SEG13                                   | TIM0_CC0 #0 TIM0_CC1<br>#7 PCNT0_S0IN #4     | US1_RX #5 US3_TX #0<br>LEU0_RX #4 I2C0_SDA<br>#0                                    | CMU_CLK2 #0 PRS_CH0<br>#0 PRS_CH3 #3<br>GPIO_EM4WU0        |  |  |  |

| PA1       | BUSAY BUSBX<br>LCD_SEG14                                   | TIM0_CC0 #7 TIM0_CC1<br>#0 PCNT0_S1IN #4     | US3_RX #0 I2C0_SCL #0                                                               | CMU_CLK1 #0 PRS_CH1<br>#0                                  |  |  |  |

| PA2       | BUSBY BUSAX<br>LCD_SEG15                                   | TIM0_CC2 #0                                  | US1_RX #6 US3_CLK #0                                                                | CMU_CLK0 #0                                                |  |  |  |

| PA3       | BUSAY BUSBX<br>LCD_SEG16                                   | TIM0_CDTI0 #0                                | US3_CS #0 U0_TX #2                                                                  | CMU_CLK2 #1<br>CMU_CLK2 #4<br>CMU_CLKI0 #1 LES_AL-<br>TEX2 |  |  |  |

| PA4       | BUSBY BUSAX<br>LCD_SEG17                                   | TIM0_CDTI1 #0                                | US3_CTS #0 U0_RX #2                                                                 | LES_ALTEX3                                                 |  |  |  |

| PA5       | BUSAY BUSBX<br>LCD_SEG18                                   | TIM0_CDTI2 #0                                | US3_RTS #0 U0_CTS #2                                                                | LES_ALTEX4 ACMP1_O<br>#7                                   |  |  |  |

| PA6       | BUSBY BUSAX<br>LCD_SEG19                                   | WTIM0_CC0 #1                                 | U0_RTS #2                                                                           | PRS_CH6 #0 ACMP0_O<br>#4 GPIO_EM4WU1                       |  |  |  |

| PB3       | BUSAY BUSBX<br>LCD_SEG20 /<br>LCD_COM4                     | TIM1_CC3 #2<br>WTIM0_CC0 #6                  | US2_TX #1 US3_TX #2                                                                 | ACMP0_O #7                                                 |  |  |  |

| PB4       | BUSBY BUSAX<br>LCD_SEG21 /<br>LCD_COM5                     | WTIM0_CC1 #6                                 | US2_RX #1                                                                           |                                                            |  |  |  |

| PB5       | BUSAY BUSBX<br>LCD_SEG22 /<br>LCD_COM6                     | WTIM0_CC2 #6<br>PCNT0_S0IN #6                | US0_RTS #4 US2_CLK<br>#1                                                            |                                                            |  |  |  |

| PB6       | BUSBY BUSAX<br>LCD_SEG23 /<br>LCD_COM7                     | TIM0_CC0 #3<br>PCNT0_S1IN #6                 | US0_CTS #4 US2_CS #1                                                                |                                                            |  |  |  |

| PC0       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #0 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC1 #3<br>PCNT0_S0IN #2                 | CAN0_RX #0 US0_TX #5<br>US1_TX #0 US1_CS #4<br>US2_RTS #0 US3_CS #3<br>I2C0_SDA #4  | LES_CH0 PRS_CH2 #0                                         |  |  |  |

| PC1       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #1 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC2 #3<br>WTIM0_CC0 #7<br>PCNT0_S1IN #2 | CAN0_TX #0 US0_RX #5<br>US1_TX #4 US1_RX #0<br>US2_CTS #0 US3_RTS<br>#1 I2C0_SCL #4 | LES_CH1 PRS_CH3 #0                                         |  |  |  |

| PC2       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #2 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI0 #3<br>WTIM0_CC1 #7                | US1_RX #4 US2_TX #0                                                                 | LES_CH2                                                    |  |  |  |

| PC3       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #3 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI1 #3<br>WTIM0_CC2 #7                | US1_CLK #4 US2_RX #0                                                                | LES_CH3                                                    |  |  |  |

### Table 5.14. GPIO Functionality Table

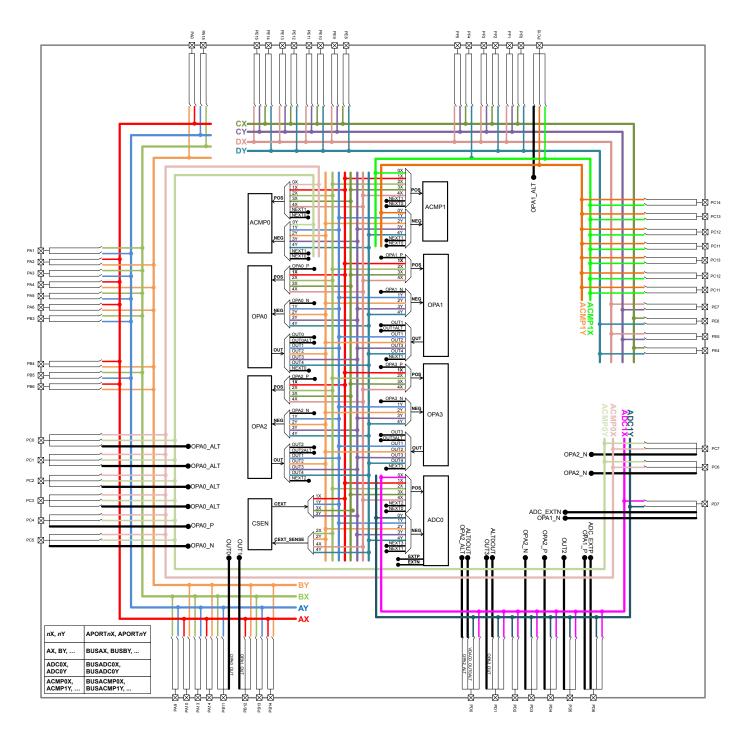

#### 5.16 Analog Port (APORT) Client Maps

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. Figure 5.14 APORT Connection Diagram on page 119 shows the APORT routing for this device family (note that available features may vary by part number). A complete description of APORT functionality can be found in the Reference Manual.

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin

Figure 7.3. QFN80 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

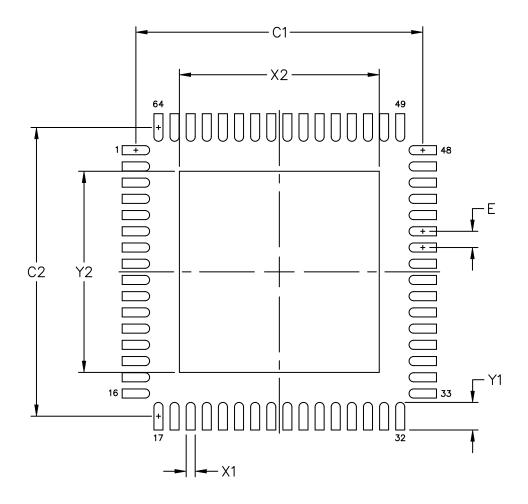

### 9.2 QFN64 PCB Land Pattern

Figure 9.2. QFN64 PCB Land Pattern Drawing