Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Discontinued at Digi-Key                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-WFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-QFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b120f128im32-ar |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Timers/Counters

- 2 × 16-bit Timer/Counter

- 3 or 4 Compare/Capture/PWM channels (4 + 4 on one timer instance)

- Dead-Time Insertion on one timer instance

- 2 × 32-bit Timer/Counter

- 32-bit Real Time Counter and Calendar (RTCC)

- 32-bit Ultra Low Energy CRYOTIMER for periodic wakeup from any Energy Mode

- 16-bit Low Energy Timer for waveform generation

- 16-bit Pulse Counter with asynchronous operation

- Watchdog Timer with dedicated RC oscillator

- Low Energy Sensor Interface (LESENSE)

- Autonomous sensor monitoring in Deep Sleep Mode

- Wide range of sensors supported, including LC sensors and capacitive buttons

- Up to 16 inputs

- Ultra efficient Power-on Reset and Brown-Out Detector

- Debug Interface

- 2-pin Serial Wire Debug interface

- 4-pin JTAG interface

- Micro Trace Buffer (MTB)

Pre-Programmed UART Bootloader

# Wide Operating Range

- 1.8 V to 3.8 V single power supply

- Integrated DC-DC, down to 1.8 V output with up to 200 mA load current for system

- Standard (-40  $^\circ C$  to 85  $^\circ C$   $T_A)$  and Extended (-40  $^\circ C$  to 125  $^\circ C$   $T_J)$  temperature grades available

- Packages

- QFN32 (5x5 mm)

- TQFP48 (7x7 mm)

- QFN64 (9x9 mm)

- TQFP64 (10x10 mm)

- QFN80 (9x9 mm)

- TQFP80 (12x12 mm)

### 3.6.5 Controller Area Network (CAN)

The CAN peripheral provides support for communication at up to 1 Mbps over CAN protocol version 2.0 part A and B. It includes 32 message objects with independent identifier masks and retains message RAM in EM2. Automatic retransmittion may be disabled in order to support Time Triggered CAN applications.

#### 3.6.6 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality such as simple logic operations (AND, OR, NOT) can be applied by the PRS to the signals. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

### 3.6.7 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface LESENSE<sup>TM</sup> is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators, ADC, and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable finite state machine which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

#### 3.7 Security Features

### 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)

The GPCRC module implements a Cyclic Redundancy Check (CRC) function. It supports both 32-bit and 16-bit polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3), while the 16-bit polynomial can be programmed to any value, depending on the needs of the application.

### 3.7.2 Crypto Accelerator (CRYPTO)

The Crypto Accelerator is a fast and energy-efficient autonomous hardware encryption and decryption accelerator. Tiny Gecko Series 1 devices support AES encryption and decryption with 128- or 256-bit keys, ECC over both GF(P) and GF(2<sup>m</sup>), and SHA-1 and SHA-2 (SHA-224 and SHA-256).

Supported block cipher modes of operation for AES include: ECB, CTR, CBC, PCBC, CFB, OFB, GCM, CBC-MAC, GMAC and CCM.

Supported ECC NIST recommended curves include P-192, P-224, P-256, K-163, K-233, B-163 and B-233.

The CRYPTO module allows fast processing of GCM (AES), ECC and SHA with little CPU intervention. CRYPTO also provides trigger signals for DMA read and write operations.

#### 3.7.3 True Random Number Generator (TRNG)

The TRNG module is a non-deterministic random number generator based on a full hardware solution. The TRNG is validated with NIST800-22 and AIS-31 test suites as well as being suitable for FIPS 140-2 certification (for the purposes of cryptographic key generation).

#### 3.7.4 Security Management Unit (SMU)

The Security Management Unit (SMU) allows software to set up fine-grained security for peripheral access, which is not possible in the Memory Protection Unit (MPU). Peripherals may be secured by hardware on an individual basis, such that only priveleged accesses to the peripheral's register interface will be allowed. When an access fault occurs, the SMU reports the specific peripheral involved and can optionally generate an interrupt.

#### 3.8 Analog

### 3.8.1 Analog Port (APORT)

The Analog Port (APORT) is an analog interconnect matrix allowing access to many analog modules on a flexible selection of pins. Each APORT bus consists of analog switches connected to a common wire. Since many clients can operate differentially, buses are grouped by X/Y pairs.

### 3.8.2 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs are selected from among internal references and external pins. The tradeoff between response time and current consumption is configurable by software. Two 6-bit reference dividers allow for a wide range of internally-programmable reference sources. The ACMP can also be used to monitor the supply voltage. An interrupt can be generated when the supply falls below or rises above the programmable threshold.

### 3.8.3 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to 1 Msps. The output sample resolution is configurable and additional resolution is possible using integrated hardware for averaging over multiple samples. The ADC includes integrated voltage references and an integrated temperature sensor. Inputs are selectable from a wide range of sources, including pins configurable as either single-ended or differential.

### 3.8.4 Capacitive Sense (CSEN)

The CSEN module is a dedicated Capacitive Sensing block for implementing touch-sensitive user interface elements such a switches and sliders. The CSEN module uses a charge ramping measurement technique, which provides robust sensing even in adverse conditions including radiated noise and moisture. The module can be configured to take measurements on a single port pin or scan through multiple pins and store results to memory through DMA. Several channels can also be shorted together to measure the combined capacitance or implement wake-on-touch from very low energy modes. Hardware includes a digital accumulator and an averaging filter, as well as digital threshold comparators to reduce software overhead.

### 3.8.5 Digital to Analog Converter (VDAC)

The Digital to Analog Converter (VDAC) can convert a digital value to an analog output voltage. The VDAC is a fully differential, 500 ksps, 12-bit converter. The opamps are used in conjunction with the VDAC, to provide output buffering. One opamp is used per singleended channel, or two opamps are used to provide differential outputs. The VDAC may be used for a number of different applications such as sensor interfaces or sound output. The VDAC can generate high-resolution analog signals while the MCU is operating at low frequencies and with low total power consumption. Using DMA and a timer, the VDAC can be used to generate waveforms without any CPU intervention. The VDAC is available in all energy modes down to and including EM3.

### 3.8.6 Operational Amplifiers

The opamps are low power amplifiers with a high degree of flexibility targeting a wide variety of standard opamp application areas, and are available down to EM3. With flexible built-in programming for gain and interconnection they can be configured to support multiple common opamp functions. All pins are also available externally for filter configurations. Each opamp has a rail to rail input and a rail to rail output. They can be used in conjunction with the VDAC module or in stand-alone configurations. The opamps save energy, PCB space, and cost as compared with standalone opamps because they are integrated on-chip.

### 3.8.7 Liquid Crystal Display Driver (LCD)

The LCD driver is capable of driving a segmented LCD display with up to 8x32 segments. A voltage boost function enables it to provide the LCD display with higher voltage than the supply voltage for the device. A patented charge redistribution driver can reduce the LCD module supply current by up to 40%. In addition, an animation feature can run custom animations on the LCD display without any CPU intervention. The LCD driver can also remain active even in Energy Mode 2 and provides a Frame Counter interrupt that can wake-up the device on a regular basis for updating data.

#### 3.9 Reset Management Unit (RMU)

The RMU is responsible for handling reset of the EFM32TG11. A wide range of reset sources are available, including several power supply monitors, pin reset, software controlled reset, core lockup reset, and watchdog reset.

## 4.1.4 DC-DC Converter

Test conditions: L\_DCDC=4.7 µH (Murata LQH3NPN4R7MM0L), C\_DCDC=4.7 µF (Samsung CL10B475KQ8NQNC), V\_DCDC\_I=3.3 V, V\_DCDC\_O=1.8 V, I\_DCDC\_LOAD=50 mA, Heavy Drive configuration, F\_DCDC\_LN=7 MHz, unless otherwise indicated.

### Table 4.4. DC-DC Converter

| Parameter                                           | Symbol              | Test Condition                                                                                                                  | Min | Тур | Max                         | Unit |

|-----------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                 | V <sub>DCDC_I</sub> | Bypass mode, I <sub>DCDC_LOAD</sub> = 50<br>mA                                                                                  | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V output, $I_{DCDC\_LOAD}$ = 100 mA, or<br>Low power (LP) mode, 1.8 V output, $I_{DCDC\_LOAD}$ = 10 mA | 2.4 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V out-<br>put, I <sub>DCDC_LOAD</sub> = 200 mA                                                         | 2.6 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Output voltage programma-<br>ble range <sup>1</sup> | V <sub>DCDC_0</sub> |                                                                                                                                 | 1.8 | _   | V <sub>VREGVDD</sub>        | V    |

| Regulation DC accuracy                              | ACC <sub>DC</sub>   | Low Noise (LN) mode, 1.8 V tar-<br>get output                                                                                   | TBD | _   | TBD                         | V    |

| Regulation window <sup>4</sup>                      | WIN <sub>REG</sub>  | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 75 µA                | TBD | _   | TBD                         | V    |

|                                                     |                     | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 10 mA                | TBD | _   | TBD                         | V    |

| Steady-state output ripple                          | V <sub>R</sub>      |                                                                                                                                 | _   | 3   | —                           | mVpp |

| Output voltage under/over-<br>shoot                 | V <sub>OV</sub>     | CCM Mode (LNFORCECCM <sup>3</sup> = 1), Load changes between 0 mA and 100 mA                                                    | _   | 25  | TBD                         | mV   |

|                                                     |                     | DCM Mode (LNFORCECCM <sup>3</sup> = 0), Load changes between 0 mA and 10 mA                                                     | _   | 45  | TBD                         | mV   |

|                                                     |                     | Overshoot during LP to LN<br>CCM/DCM mode transitions com-<br>pared to DC level in LN mode                                      | _   | 200 | -                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>CCM (LNFORCECCM <sup>3</sup> = 1) mode<br>transitions compared to DC level<br>in LN mode      | _   | 40  | _                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>DCM (LNFORCECCM <sup>3</sup> = 0) mode<br>transitions compared to DC level<br>in LN mode      | _   | 100 | _                           | mV   |

| DC line regulation                                  | V <sub>REG</sub>    | Input changes between V <sub>VREGVDD_MAX</sub> and 2.4 V                                                                        | _   | 0.1 | -                           | %    |

| DC load regulation                                  | I <sub>REG</sub>    | Load changes between 0 mA and 100 mA in CCM mode                                                                                | —   | 0.1 | _                           | %    |

| Parameter                                       | Symbol                | Test Condition                                                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-----------------------|----------------------------------------------------------------|-----|-----|-----|------|

| Max load current                                | I <sub>LOAD_MAX</sub> | Low noise (LN) mode, Heavy Drive <sup>2</sup> , T $\leq$ 85 °C | _   | _   | 200 | mA   |

|                                                 |                       | Low noise (LN) mode, Heavy<br>Drive <sup>2</sup> , T > 85 °C   | _   | _   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Medium Drive <sup>2</sup>                 | _   | _   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Light Drive <sup>2</sup>                  | _   | _   | 50  | mA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0         | _   | _   | 75  | μA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3         | _   | _   | 10  | mA   |

| DCDC nominal output ca-<br>pacitor <sup>5</sup> | C <sub>DCDC</sub>     | 25% tolerance                                                  | 1   | 4.7 | 4.7 | μF   |

| DCDC nominal output induc-<br>tor               | L <sub>DCDC</sub>     | 20% tolerance                                                  | 4.7 | 4.7 | 4.7 | μH   |

| Resistance in Bypass mode                       | R <sub>BYP</sub>      |                                                                | _   | 1.2 | TBD | Ω    |

### Note:

1. Due to internal dropout, the DC-DC output will never be able to reach its input voltage, V<sub>VREGVDD</sub>.

- 2. Drive levels are defined by configuration of the PFETCNT and NFETCNT registers. Light Drive: PFETCNT=NFETCNT=3; Medium Drive: PFETCNT=NFETCNT=7; Heavy Drive: PFETCNT=15.

- 3. LPCMPBIASEMxx refers to either LPCMPBIASEM234H in the EMU\_DCDCMISCCTRL register or LPCMPBIASEM01 in the EMU\_DCDCLOEM01CFG register, depending on the energy mode.

4. LP mode controller is a hysteretic controller that maintains the output voltage within the specified limits.

5. Output voltage under/over-shoot and regulation are specified with C<sub>DCDC</sub> 4.7 μF. Different settings for DCDCLNCOMPCTRL must be used if C<sub>DCDC</sub> is lower than 4.7 μF. See Application Note AN0948 for details.

## 4.1.8 Brown Out Detector (BOD)

| Parameter              | Symbol                     | Test Condition               | Min | Тур | Max | Unit |

|------------------------|----------------------------|------------------------------|-----|-----|-----|------|

| DVDD BOD threshold     | V <sub>DVDDBOD</sub>       | DVDD rising                  | —   | _   | TBD | V    |

|                        |                            | DVDD falling (EM0/EM1)       | TBD | _   | _   | V    |

|                        |                            | DVDD falling (EM2/EM3)       | TBD | _   | —   | V    |

| DVDD BOD hysteresis    | V <sub>DVDDBOD_HYST</sub>  |                              | _   | 18  | _   | mV   |

| DVDD BOD response time | tDVDDBOD_DELAY             | Supply drops at 0.1V/µs rate | _   | 2.4 | _   | μs   |

| AVDD BOD threshold     | V <sub>AVDDBOD</sub>       | AVDD rising                  | _   |     | TBD | V    |

|                        |                            | AVDD falling (EM0/EM1)       | TBD | _   | _   | V    |

|                        |                            | AVDD falling (EM2/EM3)       | TBD | _   | _   | V    |

| AVDD BOD hysteresis    | VAVDDBOD_HYST              |                              | —   | 20  | _   | mV   |

| AVDD BOD response time | t <sub>AVDDBOD_DELAY</sub> | Supply drops at 0.1V/µs rate | —   | 2.4 |     | μs   |

| EM4 BOD threshold      | V <sub>EM4DBOD</sub>       | AVDD rising                  | —   | _   | TBD | V    |

|                        |                            | AVDD falling                 | TBD |     | _   | V    |

| EM4 BOD hysteresis     | V <sub>EM4BOD_HYST</sub>   |                              | _   | 25  | _   | mV   |

| EM4 BOD response time  | t <sub>EM4BOD_DELAY</sub>  | Supply drops at 0.1V/µs rate | —   | 300 |     | μs   |

## Table 4.10. Brown Out Detector (BOD)

| Parameter                              | Symbol                    | Test Condition                                                                      | Min | Тур | Max | Unit  |

|----------------------------------------|---------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Frequency accuracy                     | f <sub>HFRCO_ACC</sub>    | At production calibrated frequen-<br>cies, across supply voltage and<br>temperature | TBD | _   | TBD | %     |

| Start-up time                          | t <sub>HFRCO</sub>        | f <sub>HFRCO</sub> ≥ 19 MHz                                                         | _   | 300 | —   | ns    |

|                                        |                           | 4 < f <sub>HFRCO</sub> < 19 MHz                                                     | _   | 1   | —   | μs    |

|                                        |                           | f <sub>HFRCO</sub> ≤ 4 MHz                                                          | _   | 2.5 | _   | μs    |

| Current consumption on all             | I <sub>HFRCO</sub>        | f <sub>HFRCO</sub> = 48 MHz                                                         |     | 258 | TBD | μA    |

| supplies                               |                           | f <sub>HFRCO</sub> = 38 MHz                                                         | _   | 218 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 32 MHz                                                         |     | 182 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 26 MHz                                                         |     | 156 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 19 MHz                                                         |     | 130 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 16 MHz                                                         |     | 112 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 13 MHz                                                         |     | 101 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 7 MHz                                                          |     | 80  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 4 MHz                                                          |     | 29  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 2 MHz                                                          |     | 26  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 1 MHz                                                          |     | 24  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 40 MHz, DPLL enabled                                           |     | 393 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 32 MHz, DPLL enabled                                           |     | 313 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 16 MHz, DPLL enabled                                           |     | 180 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 4 MHz, DPLL enabled                                            |     | 46  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 1 MHz, DPLL enabled                                            |     | 33  | TBD | μA    |

| Coarse trim step size (% of period)    | SS <sub>HFRCO_COARS</sub> |                                                                                     |     | 0.8 | _   | %     |

| Fine trim step size (% of pe-<br>riod) | SS <sub>HFRCO_FINE</sub>  |                                                                                     |     | 0.1 | -   | %     |

| Period jitter                          | PJ <sub>HFRCO</sub>       |                                                                                     |     | 0.2 | _   | % RMS |

## Table 4.14. High-Frequency RC Oscillator (HFRCO)

| Parameter        | Symbol                  | Test Condition                        | Min | Тур | Мах | Unit |

|------------------|-------------------------|---------------------------------------|-----|-----|-----|------|

| Frequency limits | f <sub>HFRCO_BAND</sub> | FREQRANGE = 0, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 3, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 6, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 7, FINETUNIN-<br>GEN = 0  | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 8, FINETUNIN-<br>GEN = 0  | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 10, FINETUNIN-<br>GEN = 0 | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 11, FINETUNIN-<br>GEN = 0 | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 12, FINETUNIN-<br>GEN = 0 | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 13, FINETUNIN-<br>GEN = 0 | TBD | _   | TBD | MHz  |

### 4.1.9.5 Auxiliary High-Frequency RC Oscillator (AUXHFRCO)

| Parameter                              | Symbol                             | Test Condition                                                                      | Min | Тур | Мах | Unit  |

|----------------------------------------|------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Frequency accuracy                     | fauxhfrco_acc                      | At production calibrated frequen-<br>cies, across supply voltage and<br>temperature | TBD | _   | TBD | %     |

| Start-up time                          | t <sub>AUXHFRCO</sub>              | f <sub>AUXHFRCO</sub> ≥ 19 MHz                                                      | _   | 400 | _   | ns    |

|                                        |                                    | 4 < f <sub>AUXHFRCO</sub> < 19 MHz                                                  | _   | 1.4 | _   | μs    |

|                                        |                                    | f <sub>AUXHFRCO</sub> ≤ 4 MHz                                                       | _   | 2.5 | _   | μs    |

| Current consumption on all             | I <sub>AUXHFRCO</sub>              | f <sub>AUXHFRCO</sub> = 48 MHz                                                      | _   | 238 | TBD | μA    |

| supplies                               |                                    | f <sub>AUXHFRCO</sub> = 38 MHz                                                      | —   | 196 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 32 MHz                                                      | _   | 160 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 26 MHz                                                      | _   | 137 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 19 MHz                                                      | _   | 110 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 16 MHz                                                      | _   | 101 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 13 MHz                                                      | _   | 78  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 7 MHz                                                       | _   | 54  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 4 MHz                                                       | _   | 30  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 2 MHz                                                       | _   | 27  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 1 MHz                                                       | _   | 25  | TBD | μA    |

| Coarse trim step size (% of period)    | SS <sub>AUXHFR-</sub><br>CO_COARSE |                                                                                     |     | 0.8 | _   | %     |

| Fine trim step size (% of pe-<br>riod) | SS <sub>AUXHFR-</sub><br>CO_FINE   |                                                                                     |     | 0.1 | _   | %     |

| Period jitter                          | PJ <sub>AUXHFRCO</sub>             |                                                                                     |     | 0.2 | _   | % RMS |

## Table 4.15. Auxiliary High-Frequency RC Oscillator (AUXHFRCO)

## 4.1.9.6 Ultra-low Frequency RC Oscillator (ULFRCO)

### Table 4.16. Ultra-low Frequency RC Oscillator (ULFRCO)

| Parameter             | Symbol              | Test Condition | Min | Тур | Мах | Unit |

|-----------------------|---------------------|----------------|-----|-----|-----|------|

| Oscillation frequency | f <sub>ULFRCO</sub> |                | TBD | 1   | TBD | kHz  |

## 4.1.12 Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Мах | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | I <sub>VMON</sub>       | In EM0 or EM1, 1 supply monitored, T $\leq$ 85 °C                | _    | 6.3  | TBD | μA   |

|                                    |                         | In EM0 or EM1, 4 supplies monitored, T $\leq$ 85 °C              | —    | 12.5 | TBD | μA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshold       | —    | 62   |     | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | _    | 99   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold | —    | 99   | _   | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | —    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    | _   | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | _    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  |     | mV   |

|                                    |                         | Fine                                                             | _    | 20   | _   | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | _    | 460  | _   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  |      | 26   | _   | mV   |

## Table 4.19. Voltage Monitor (VMON)

| Parameter | Symbol                              | Test Condition                                              | Min | Тур | Max | Unit   |

|-----------|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|--------|

|           | the sum of the<br>e.<br>Gregisters. | etting in ACMPn_CTRL_PWRS<br>ne contributions from the ACMP | -   |     |     | ACMP + |

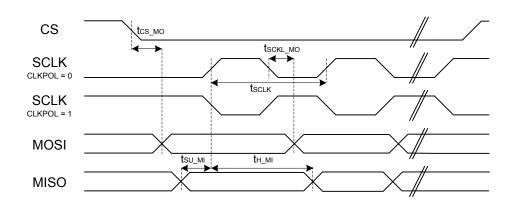

## 4.1.22 USART SPI

## **SPI Master Timing**

## Table 4.31. SPI Master Timing

| Parameter                      | Symbol               | Test Condition | Min                          | Тур | Мах  | Unit |

|--------------------------------|----------------------|----------------|------------------------------|-----|------|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>    |                | 2 *<br><sup>t</sup> HFPERCLK | —   | _    | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub>   |                | -19.8                        | _   | 18.9 | ns   |

| SCLK to MOSI <sup>1 3</sup>    | t <sub>SCLK_MO</sub> |                | -10                          | _   | 14.5 | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>su_мi</sub>   | IOVDD = 1.62 V | 75                           | _   | _    | ns   |

|                                |                      | IOVDD = 3.0 V  | 40                           | —   | _    | ns   |

| MISO hold time <sup>1 3</sup>  | t <sub>H_MI</sub>    |                | -10                          | _   | _    | ns   |

## Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

2. t<sub>HFPERCLK</sub> is one period of the selected HFPERCLK.

3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $V_{\text{DD}}$ ).

Figure 4.1. SPI Master Timing Diagram

| Pin Name              | Pin(s)    | Description                | Pin Name | Pin(s) | Description |

|-----------------------|-----------|----------------------------|----------|--------|-------------|

| PE15                  | 79        | GPIO                       | PA15     | 80     | GPIO        |

| Note:<br>1. GPIO with | 5V tolera | nce are indicated by (5V). |          |        | ·           |

| Pin Name | Pin(s) | Description                                                                                                                                                                                                 | Pin Name | Pin(s)   | Description           |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------------------|

| PB6      | 12     | GPIO                                                                                                                                                                                                        | PC4      | 13       | GPIO                  |

| PC5      | 14     | GPIO                                                                                                                                                                                                        | PB7      | 15       | GPIO                  |

| PB8      | 16     | GPIO                                                                                                                                                                                                        | PA12     | 17       | GPIO                  |

| PA13     | 18     | GPIO (5V)                                                                                                                                                                                                   | PA14     | 19       | GPIO                  |

| RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB11     | 21       | GPIO                  |

| PB12     | 22     | GPIO                                                                                                                                                                                                        | AVDD     | 23<br>27 | Analog power supply.  |

| PB13     | 24     | GPIO                                                                                                                                                                                                        | PB14     | 25       | GPIO                  |

| PD0      | 28     | GPIO (5V)                                                                                                                                                                                                   | PD1      | 29       | GPIO                  |

| PD2      | 30     | GPIO (5V)                                                                                                                                                                                                   | PD3      | 31       | GPIO                  |

| PD4      | 32     | GPIO                                                                                                                                                                                                        | PD5      | 33       | GPIO                  |

| PD6      | 34     | GPIO                                                                                                                                                                                                        | PD7      | 35       | GPIO                  |

| PD8      | 36     | GPIO                                                                                                                                                                                                        | PC6      | 37       | GPIO                  |

| PC7      | 38     | GPIO                                                                                                                                                                                                        | DVDD     | 39       | Digital power supply. |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    | PE4      | 41       | GPIO                  |

| PE5      | 42     | GPIO                                                                                                                                                                                                        | PE6      | 43       | GPIO                  |

| PE7      | 44     | GPIO                                                                                                                                                                                                        | PC12     | 45       | GPIO (5V)             |

| PC13     | 46     | GPIO (5V)                                                                                                                                                                                                   | PC14     | 47       | GPIO (5V)             |

| PC15     | 48     | GPIO (5V)                                                                                                                                                                                                   | PF0      | 49       | GPIO (5V)             |

| PF1      | 50     | GPIO (5V)                                                                                                                                                                                                   | PF2      | 51       | GPIO                  |

| PF3      | 52     | GPIO                                                                                                                                                                                                        | PF4      | 53       | GPIO                  |

| PF5      | 54     | GPIO                                                                                                                                                                                                        | PE8      | 56       | GPIO                  |

| PE9      | 57     | GPIO                                                                                                                                                                                                        | PE10     | 58       | GPIO                  |

| PE11     | 59     | GPIO                                                                                                                                                                                                        | PE12     | 60       | GPIO                  |

| PE13     | 61     | GPIO                                                                                                                                                                                                        | PE14     | 62       | GPIO                  |

| PE15     | 63     | GPIO                                                                                                                                                                                                        | PA15     | 64       | GPIO                  |

1. GPIO with 5V tolerance are indicated by (5V).

| GPIO Name | Pin Alternate Functionality / Description                  |                                                                  |                                                                          |                                                                |  |

|-----------|------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|--|

|           | Analog                                                     | Timers                                                           | Communication                                                            | Other                                                          |  |

| PC15      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #3 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI2 #1<br>TIM1_CC2 #0<br>WTIM0_CC0 #4 LE-<br>TIM0_OUT1 #5 | US0_CLK #3 US1_CLK<br>#3 US3_RTS #3 U0_RX<br>#3 LEU0_RX #5               | LES_CH15 PRS_CH1 #2                                            |  |

| PF0       | BUSDY BUSCX                                                | TIM0_CC0 #4<br>WTIM0_CC1 #4 LE-<br>TIM0_OUT0 #2                  | CAN0_RX #1 US1_CLK<br>#2 US2_TX #5 LEU0_TX<br>#3 I2C0_SDA #5             | DBG_SWCLKTCK<br>BOOT_TX                                        |  |

| PF1       | BUSCY BUSDX                                                | TIM0_CC1 #4<br>WTIM0_CC2 #4 LE-<br>TIM0_OUT1 #2                  | US1_CS #2 US2_RX #5<br>U0_TX #5 LEU0_RX #3<br>I2C0_SCL #5                | PRS_CH4 #2<br>DBG_SWDIOTMS<br>GPIO_EM4WU3<br>BOOT_RX           |  |

| PF2       | BUSDY BUSCX<br>LCD_SEG0                                    | TIM0_CC2 #4 TIM1_CC0<br>#5                                       | CAN0_TX #1 US1_TX #5<br>US2_CLK #5 U0_RX #5<br>LEU0_TX #4 I2C1_SCL<br>#4 | CMU_CLK0 #4 PRS_CH0<br>#3 ACMP1_O #0<br>DBG_TDO<br>GPIO_EM4WU4 |  |

| PF3       | BUSCY BUSDX<br>LCD_SEG1                                    | TIM0_CDTI0 #2<br>TIM1_CC1 #5                                     | US1_CTS #2                                                               | CMU_CLK1 #4 PRS_CH0<br>#1                                      |  |

| PF4       | BUSDY BUSCX<br>LCD_SEG2                                    | TIM0_CDTI1 #2<br>TIM1_CC2 #5                                     | US1_RTS #2                                                               | PRS_CH1 #1                                                     |  |

| PF5       | BUSCY BUSDX<br>LCD_SEG3                                    | TIM0_CDTI2 #2<br>TIM1_CC3 #6                                     | US2_CS #5                                                                | PRS_CH2 #1 DBG_TDI                                             |  |

| PE8       | BUSDY BUSCX<br>LCD_SEG4                                    |                                                                  |                                                                          | PRS_CH3 #1                                                     |  |

| PE9       | BUSCY BUSDX<br>LCD_SEG5                                    |                                                                  |                                                                          |                                                                |  |

| PE10      | BUSDY BUSCX<br>LCD_SEG6                                    | TIM1_CC0 #1<br>WTIM0_CDTI0 #0                                    | US0_TX #0                                                                | PRS_CH2 #2<br>GPIO_EM4WU9                                      |  |

| PE11      | BUSCY BUSDX<br>LCD_SEG7                                    | TIM1_CC1 #1<br>WTIM0_CDTI1 #0                                    | US0_RX #0                                                                | LES_ALTEX5 PRS_CH3<br>#2                                       |  |

| PE12      | BUSDY BUSCX<br>LCD_SEG8                                    | TIM1_CC2 #1<br>WTIM0_CDTI2 #0 LE-<br>TIM0_OUT0 #4                | US0_RX #3 US0_CLK #0<br>I2C0_SDA #6                                      | CMU_CLK1 #2<br>CMU_CLKI0 #6 LES_AL-<br>TEX6 PRS_CH1 #3         |  |

| PE13      | BUSCY BUSDX<br>LCD_SEG9                                    | TIM1_CC3 #1 LE-<br>TIM0_OUT1 #4                                  | US0_TX #3 US0_CS #0<br>I2C0_SCL #6                                       | LES_ALTEX7 PRS_CH2<br>#3 ACMP0_O #0<br>GPIO_EM4WU5             |  |

| PE14      | BUSDY BUSCX<br>LCD_SEG10                                   |                                                                  | US0_CTS #0 LEU0_TX<br>#2                                                 |                                                                |  |

| PE15      | BUSCY BUSDX<br>LCD_SEG11                                   |                                                                  | US0_RTS #0 LEU0_RX<br>#2                                                 |                                                                |  |

| PA15      | BUSAY BUSBX<br>LCD_SEG12                                   |                                                                  | US2_CLK #3                                                               |                                                                |  |

| Alternate     | LOCA                                  | ATION              |                                                                                                                                                                                      |  |  |

|---------------|---------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Functionality | 0 - 3                                 | 4 - 7              | Description                                                                                                                                                                          |  |  |

| CAN0_TX       | 0: PC1<br>1: PF2<br>2: PD1            |                    | CAN0 TX.                                                                                                                                                                             |  |  |

| CMU_CLK0      | 0: PA2<br>1: PC12<br>2: PD7           | 4: PF2<br>5: PA12  | Clock Management Unit, clock output number 0.                                                                                                                                        |  |  |

| CMU_CLK1      | 0: PA1<br>1: PD8<br>2: PE12           | 4: PF3<br>5: PB11  | Clock Management Unit, clock output number 1.                                                                                                                                        |  |  |

| CMU_CLK2      | 0: PA0<br>1: PA3<br>2: PD6            | 4: PA3             | Clock Management Unit, clock output number 2.                                                                                                                                        |  |  |

| CMU_CLKI0     | 0: PD4<br>1: PA3<br>2: PB8<br>3: PB13 | 6: PE12<br>7: PB11 | Clock Management Unit, clock input number 0.                                                                                                                                         |  |  |

| DBG_SWCLKTCK  | 0: PF0                                |                    | Debug-interface Serial Wire clock input and JTAG Test Clock.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull down.                            |  |  |

| DBG_SWDIOTMS  | 0: PF1                                |                    | Debug-interface Serial Wire data input / output and JTAG Test Mode Select.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull up.                |  |  |

| DBG_TDI       | 0: PF5                                |                    | Debug-interface JTAG Test Data In.<br>Note that this function becomes available after the first valid JTAG command is re-<br>ceived, and has a built-in pull up when JTAG is active. |  |  |

| DBG_TDO       | 0: PF2                                |                    | Debug-interface JTAG Test Data Out.<br>Note that this function becomes available after the first valid JTAG command is re-<br>ceived.                                                |  |  |

| GPIO_EM4WU0   | 0: PA0                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |

| GPIO_EM4WU1   | 0: PA6                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |

| GPIO_EM4WU2   | 0: PC9                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |

| GPIO_EM4WU3   | 0: PF1                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |

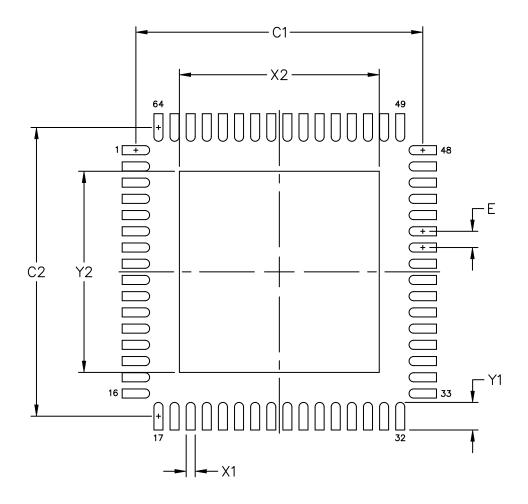

### Table 8.2. TQFP64 PCB Land Pattern Dimensions

| Dimension | Min      | Мах   |  |

|-----------|----------|-------|--|

| C1        | 11.30    | 11.40 |  |

| C2        | 11.30    | 11.40 |  |

| E         | 0.50 BSC |       |  |

| x         | 0.20     | 0.30  |  |

| Y         | 1.40     | 1.50  |  |

### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

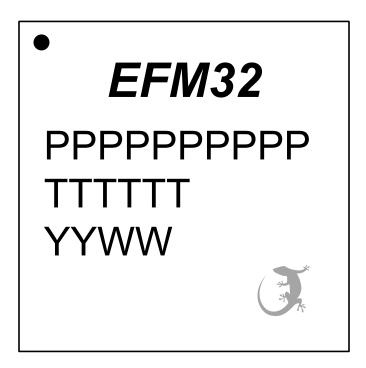

### 8.3 TQFP64 Package Marking

Figure 8.3. TQFP64 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

### 9.2 QFN64 PCB Land Pattern

Figure 9.2. QFN64 PCB Land Pattern Drawing

| Dimension | Min      | Тур | Мах   |  |  |

|-----------|----------|-----|-------|--|--|

| A         | 7.00 BSC |     |       |  |  |

| A1        | 3.50 BSC |     |       |  |  |

| В         | 7.00 BSC |     |       |  |  |

| B1        | 3.50 BSC |     |       |  |  |

| С         | 1.00     | _   | 1.20  |  |  |

| D         | 0.17     | —   | 0.27  |  |  |

| E         | 0.95     | —   | 1.05  |  |  |

| F         | 0.17     | _   | 0.23  |  |  |

| G         | 0.50 BSC |     |       |  |  |

| Н         | 0.05     | _   | 0.15  |  |  |

| J         | 0.09     | —   | 0.20  |  |  |

| К         | 0.50     | —   | 0.70  |  |  |

| L         | 0        | _   | 7     |  |  |

| М         | 12 REF   |     |       |  |  |

| Ν         | 0.09     | —   | 0.16  |  |  |

| Ρ         | 0.25 BSC |     |       |  |  |

| R         | 0.150    | —   | 0.250 |  |  |

| S         | 9.00 BSC |     |       |  |  |

| S1        | 4.50 BSC |     |       |  |  |

| V         | 9.00 BSC |     |       |  |  |

| V1        | 4.50 BSC |     |       |  |  |

| W         | 0.20 BSC |     |       |  |  |

| AA        | 1.00 BSC |     |       |  |  |

| Note:     |          |     |       |  |  |

## Table 10.1. TQFP48 Package Dimensions

Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## **Simplicity Studio**

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

Support and Community community.silabs.com

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com