Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 53                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b120f128iq64-a |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Feature List

The EFM32TG11 highlighted features are listed below.

# ARM Cortex-M0+ CPU platform

- High performance 32-bit processor @ up to 48 MHz

- Memory Protection Unit

- Wake-up Interrupt Controller

- Flexible Energy Management System

- 37 µA/MHz in Active Mode (EM0)

- 1.30 µA EM2 Deep Sleep current (8 kB RAM retention and RTCC running from LFRCO)

- Integrated DC-DC buck converter

- Backup Power Domain

- RTCC and retention registers in a separate power domain, available in all energy modes

- Operation from backup battery when main power absent/ insufficient

- Up to 128 kB flash program memory

- Up to 32 kB RAM data memory

- Communication Interfaces

- CAN Bus Controller

- Version 2.0A and 2.0B up to 1 Mbps

- 4 × Universal Synchronous/Asynchronous Receiver/ Transmitter

- UART/SPI/SmartCard (ISO 7816)/IrDA/I2S/LIN

- Triple buffered full/half-duplex operation with flow control

- Ultra high speed (24 MHz) operation on one instance

- 1 × Universal Asynchronous Receiver/ Transmitter

- 1 × Low Energy UART

- Autonomous operation with DMA in Deep Sleep Mode

- $2 \times I^2C$  Interface with SMBus support

- Address recognition in EM3 Stop Mode

## Up to 67 General Purpose I/O Pins

- Configurable push-pull, open-drain, pull-up/down, input filter, drive strength

- Configurable peripheral I/O locations

- · 5 V tolerance on select pins

- Asynchronous external interrupts

- Output state retention and wake-up from Shutoff Mode

- Up to 8 Channel DMA Controller

- Up to 8 Channel Peripheral Reflex System (PRS) for autonomous inter-peripheral signaling

- Hardware Cryptography

- AES 128/256-bit keys

- ECC B/K163, B/K233, P192, P224, P256

- SHA-1 and SHA-2 (SHA-224 and SHA-256)

- True Random Number Generator (TRNG)

- Hardware CRC engine

- Single-cycle computation with 8/16/32-bit data and 16-bit (programmable)/32-bit (fixed) polynomial

- Security Management Unit (SMU)

- Fine-grained access control for on-chip peripherals

- Integrated Low-energy LCD Controller with up to 8 × 32 segments

- Voltage boost, contrast and autonomous animation

- Patented low-energy LCD driver

- Ultra Low-Power Precision Analog Peripherals

- 12-bit 1 Msamples/s Analog to Digital Converter (ADC)

- On-chip temperature sensor

- 2 × 12-bit 500 ksamples/s Digital to Analog Converter (VDAC)

- Up to 2 × Analog Comparator (ACMP)

- Up to 4 × Operational Amplifier (OPAMP)

- Robust current-based capacitive sensing with up to 38 inputs and wake-on-touch (CSEN)

- Up to 62 GPIO pins are analog-capable. Flexible analog peripheral-to-pin routing via Analog Port (APORT)

- Supply Voltage Monitor

# **Table of Contents**

| 1. | Feature List                                                                                                                                                                                                                                                                        | . 2 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2. | Ordering Information                                                                                                                                                                                                                                                                | . 4 |

| 3. | System Overview                                                                                                                                                                                                                                                                     | 10  |

|    | 3.1 Introduction                                                                                                                                                                                                                                                                    | .10 |

|    | 3.2 Power                                                                                                                                                                                                                                                                           | .11 |

|    | 3.2.1 Energy Management Unit (EMU)                                                                                                                                                                                                                                                  |     |

|    | 3.2.2 DC-DC Converter                                                                                                                                                                                                                                                               |     |

|    | 3.2.3 EM2 and EM3 Power Domains                                                                                                                                                                                                                                                     |     |

|    | 3.3 General Purpose Input/Output (GPIO).                                                                                                                                                                                                                                            | .12 |

|    | 3.4 Clocking                                                                                                                                                                                                                                                                        |     |

|    | 3.4.1 Clock Management Unit (CMU)                                                                                                                                                                                                                                                   |     |

|    | 3.4.2 Internal and External Oscillators.                                                                                                                                                                                                                                            |     |

|    | 3.5 Counters/Timers and PWM                                                                                                                                                                                                                                                         |     |

|    | 3.5.1 Timer/Counter (TIMER)                                                                                                                                                                                                                                                         |     |

|    | 3.5.2 Wide Timer/Counter (WTIMER)                                                                                                                                                                                                                                                   |     |

|    | 3.5.3 Real Time Counter and Calendar (RTCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |     |

|    | 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)                                                                                                                                                                                                                                     |     |

|    | 3.5.6 Pulse Counter (PCNT)                                                                                                                                                                                                                                                          |     |

|    | 3.5.7 Watchdog Timer (WDOG).                                                                                                                                                                                                                                                        |     |

|    | 3.6 Communications and Other Digital Peripherals                                                                                                                                                                                                                                    | .13 |

|    | 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART).                                                                                                                                                                                                              |     |

|    | 3.6.2 Universal Asynchronous Receiver/Transmitter (UART)                                                                                                                                                                                                                            |     |

|    | 3.6.3 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)                                                                                                                                                                                                               | .13 |

|    | 3.6.4 Inter-Integrated Circuit Interface (I <sup>2</sup> C)                                                                                                                                                                                                                         |     |

|    | 3.6.5 Controller Area Network (CAN)                                                                                                                                                                                                                                                 |     |

|    | 3.6.6 Peripheral Reflex System (PRS)                                                                                                                                                                                                                                                |     |

|    | 3.6.7 Low Energy Sensor Interface (LESENSE)                                                                                                                                                                                                                                         | .14 |

|    | 3.7 Security Features.                                                                                                                                                                                                                                                              |     |

|    | 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)                                                                                                                                                                                                                               |     |

|    | 3.7.2 Crypto Accelerator (CRYPTO)                                                                                                                                                                                                                                                   |     |

|    | 3.7.3 True Random Number Generator (TRNG)                                                                                                                                                                                                                                           |     |

|    |                                                                                                                                                                                                                                                                                     |     |

|    | 3.8 Analog                                                                                                                                                                                                                                                                          |     |

|    | 3.8.1 Analog Port (APORT)                                                                                                                                                                                                                                                           |     |

|    | 3.8.3 Analog to Digital Converter (ADC)                                                                                                                                                                                                                                             |     |

|    | 3.8.4 Capacitive Sense (CSEN).                                                                                                                                                                                                                                                      |     |

|    | 3.8.5 Digital to Analog Converter (VDAC)                                                                                                                                                                                                                                            |     |

|    | 3.8.6 Operational Amplifiers                                                                                                                                                                                                                                                        |     |

|    | 3.8.7 Liquid Crystal Display Driver (LCD).                                                                                                                                                                                                                                          |     |

|    | 3.9 Reset Management Unit (RMU)                                                                                                                                                                                                                                                     | .15 |

## 3. System Overview

#### 3.1 Introduction

The Tiny Gecko Series 1 product family is well suited for any battery operated application as well as other systems requiring high performance and low energy consumption. This section gives a short introduction to the MCU system. The detailed functional description can be found in the Tiny Gecko Series 1 Reference Manual. Any behavior that does not conform to the specifications in this data sheet or the functional descriptions in the Tiny Gecko Series 1 Reference Manual are detailed in the EFM32TG11 Errata document.

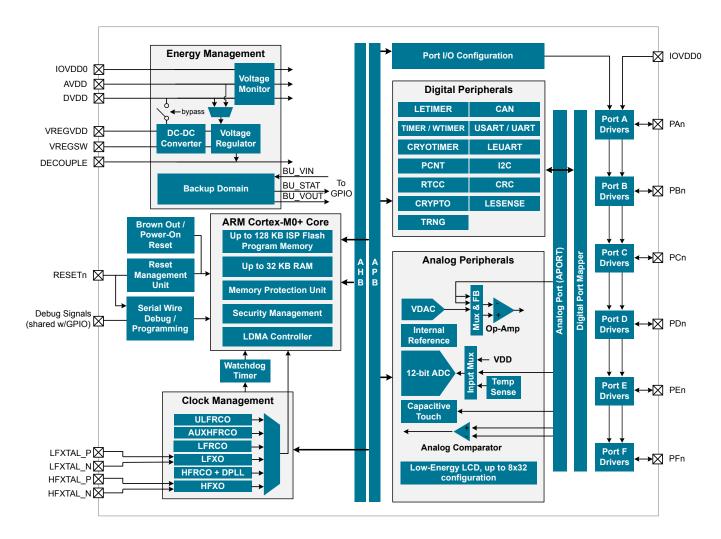

A block diagram of the Tiny Gecko Series 1 family is shown in Figure 3.1 Detailed EFM32TG11 Block Diagram on page 10. The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Detailed EFM32TG11 Block Diagram

#### 3.5.4 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

#### 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

#### 3.5.6 Pulse Counter (PCNT)

The Pulse Counter (PCNT) peripheral can be used for counting pulses on a single input or to decode quadrature encoded inputs. The clock for PCNT is selectable from either an external source on pin PCTNn\_S0IN or from an internal timing reference, selectable from among any of the internal oscillators, except the AUXHFRCO. The module may operate in energy mode EM0 Active, EM1 Sleep, EM2 Deep Sleep, and EM3 Stop.

#### 3.5.7 Watchdog Timer (WDOG)

The watchdog timer can act both as an independent watchdog or as a watchdog synchronous with the CPU clock. It has windowed monitoring capabilities, and can generate a reset or different interrupts depending on the failure mode of the system. The watchdog can also monitor autonomous systems driven by PRS.

#### 3.6 Communications and Other Digital Peripherals

#### 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous/Asynchronous Receiver/Transmitter is a flexible serial I/O module. It supports full duplex asynchronous UART communication with hardware flow control as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with devices supporting:

- ISO7816 SmartCards

- IrDA

- I<sup>2</sup>S

#### 3.6.2 Universal Asynchronous Receiver/Transmitter (UART)

The Universal Asynchronous Receiver/Transmitter is a subset of the USART module, supporting full duplex asynchronous UART communication with hardware flow control and RS-485.

#### 3.6.3 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup> provides two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud. The LEUART includes all necessary hardware to make asynchronous serial communication possible with a minimum of software intervention and energy consumption.

#### **3.6.4** Inter-Integrated Circuit Interface (I<sup>2</sup>C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C bus. It is capable of acting as both a master and a slave and supports multi-master buses. Standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also available, allowing implementation of an SMBus-compliant system. The interface provided to software by the I<sup>2</sup>C module allows precise timing control of the transmission process and highly automated transfers. Automatic recognition of slave addresses is provided in active and low energy modes.

#### 3.8.1 Analog Port (APORT)

The Analog Port (APORT) is an analog interconnect matrix allowing access to many analog modules on a flexible selection of pins. Each APORT bus consists of analog switches connected to a common wire. Since many clients can operate differentially, buses are grouped by X/Y pairs.

#### 3.8.2 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs are selected from among internal references and external pins. The tradeoff between response time and current consumption is configurable by software. Two 6-bit reference dividers allow for a wide range of internally-programmable reference sources. The ACMP can also be used to monitor the supply voltage. An interrupt can be generated when the supply falls below or rises above the programmable threshold.

#### 3.8.3 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to 1 Msps. The output sample resolution is configurable and additional resolution is possible using integrated hardware for averaging over multiple samples. The ADC includes integrated voltage references and an integrated temperature sensor. Inputs are selectable from a wide range of sources, including pins configurable as either single-ended or differential.

#### 3.8.4 Capacitive Sense (CSEN)

The CSEN module is a dedicated Capacitive Sensing block for implementing touch-sensitive user interface elements such a switches and sliders. The CSEN module uses a charge ramping measurement technique, which provides robust sensing even in adverse conditions including radiated noise and moisture. The module can be configured to take measurements on a single port pin or scan through multiple pins and store results to memory through DMA. Several channels can also be shorted together to measure the combined capacitance or implement wake-on-touch from very low energy modes. Hardware includes a digital accumulator and an averaging filter, as well as digital threshold comparators to reduce software overhead.

#### 3.8.5 Digital to Analog Converter (VDAC)

The Digital to Analog Converter (VDAC) can convert a digital value to an analog output voltage. The VDAC is a fully differential, 500 ksps, 12-bit converter. The opamps are used in conjunction with the VDAC, to provide output buffering. One opamp is used per singleended channel, or two opamps are used to provide differential outputs. The VDAC may be used for a number of different applications such as sensor interfaces or sound output. The VDAC can generate high-resolution analog signals while the MCU is operating at low frequencies and with low total power consumption. Using DMA and a timer, the VDAC can be used to generate waveforms without any CPU intervention. The VDAC is available in all energy modes down to and including EM3.

#### 3.8.6 Operational Amplifiers

The opamps are low power amplifiers with a high degree of flexibility targeting a wide variety of standard opamp application areas, and are available down to EM3. With flexible built-in programming for gain and interconnection they can be configured to support multiple common opamp functions. All pins are also available externally for filter configurations. Each opamp has a rail to rail input and a rail to rail output. They can be used in conjunction with the VDAC module or in stand-alone configurations. The opamps save energy, PCB space, and cost as compared with standalone opamps because they are integrated on-chip.

#### 3.8.7 Liquid Crystal Display Driver (LCD)

The LCD driver is capable of driving a segmented LCD display with up to 8x32 segments. A voltage boost function enables it to provide the LCD display with higher voltage than the supply voltage for the device. A patented charge redistribution driver can reduce the LCD module supply current by up to 40%. In addition, an animation feature can run custom animations on the LCD display without any CPU intervention. The LCD driver can also remain active even in Energy Mode 2 and provides a Frame Counter interrupt that can wake-up the device on a regular basis for updating data.

#### 3.9 Reset Management Unit (RMU)

The RMU is responsible for handling reset of the EFM32TG11. A wide range of reset sources are available, including several power supply monitors, pin reset, software controlled reset, core lockup reset, and watchdog reset.

| Parameter                      | Symbol                | Test Condition                                                        | Min                 | Тур              | Мах             | Unit      |

|--------------------------------|-----------------------|-----------------------------------------------------------------------|---------------------|------------------|-----------------|-----------|

| Note:                          |                       |                                                                       |                     |                  |                 |           |

|                                |                       | mode is calculated using $R_{BYP}$ _min+ILOAD * $R_{BYP}$ _max.       | from the DCDC spec  | cification table | e. Requiremer   | nts for   |

| 2. VREGVDD must be             | e tied to AVDD. Both  | VREGVDD and AVDD minimum                                              | voltages must be sa | atisfied for the | part to opera   | te.       |

|                                |                       | characteristic specs of the capa oss temperature and DC bias.         | citor used on DECOU | JPLE to ensu     | re its capacita | ance val- |

|                                | will be dependent on  | transitions occur at a rate of 10 r<br>the value of the DECOUPLE ou   |                     |                  |                 |           |

| 5. When the CSEN pe            | ripheral is used with | chopping enabled (CSEN_CTRI                                           | CHOPEN = ENAB       | LE), IOVDD n     | nust be equal   | to AVDE   |

| cation. T <sub>A</sub> (max) = |                       | due to device self-heating, which<br>x PowerDissipation). Refer to th |                     | •                | -               |           |

## 4.1.3 Thermal Characteristics

| Parameter                  | Symbol                          | Test Condition                    | Min | Тур  | Мах | Unit |

|----------------------------|---------------------------------|-----------------------------------|-----|------|-----|------|

| Thermal resistance, QFN32  | THETA <sub>JA_QFN32</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 25.7 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 23.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 21.3 | _   | °C/W |

| Thermal resistance, TQFP48 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 44.1 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP48</sub>         | 4-Layer PCB, Air velocity = 1 m/s |     | 43.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s |     | 42.3 | _   | °C/W |

| Thermal resistance, QFN64  | THETA <sub>JA_QFN64</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP64 | THE-<br>TA <sub>JA_TQFP64</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 37.3 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 35.6 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 33.8 | _   | °C/W |

| Thermal resistance, QFN80  | THETA <sub>JA_QFN80</sub>       | 4-Layer PCB, Air velocity = 0 m/s |     | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP80 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 49.3 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP80</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 44.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 42.6 | _   | °C/W |

## Table 4.3. Thermal Characteristics

## 4.1.9.3 Low-Frequency RC Oscillator (LFRCO)

| Symbol             | Test Condition                     | Min                                                                                                                                                                                                                                                                           | Тур                                                                                                                                                                                                                                                                                        | Мах                                                                                                                                                                                                                                                                                                                                                                     | Unit                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>LFRCO</sub> | ENVREF <sup>2</sup> = 1            | TBD                                                                                                                                                                                                                                                                           | 32.768                                                                                                                                                                                                                                                                                     | TBD                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | ENVREF <sup>2</sup> = 1, T > 85 °C | TBD                                                                                                                                                                                                                                                                           | 32.768                                                                                                                                                                                                                                                                                     | TBD                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | ENVREF <sup>2</sup> = 0            | TBD                                                                                                                                                                                                                                                                           | 32.768                                                                                                                                                                                                                                                                                     | TBD                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                                                                                                                                                                                                                                                                                                  |

| t <sub>LFRCO</sub> |                                    | _                                                                                                                                                                                                                                                                             | 500                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                         | μs                                                                                                                                                                                                                                                                                                                                                                                   |

| ILFRCO             | ENVREF = 1 in<br>CMU_LFRCOCTRL     | _                                                                                                                                                                                                                                                                             | 370                                                                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                       | nA                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | ENVREF = 0 in<br>CMU_LFRCOCTRL     | _                                                                                                                                                                                                                                                                             | 520                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                         | nA                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | f <sub>LFRCO</sub>                 | $\begin{tabular}{ c c c c } \hline f_{LFRCO} & ENVREF^2 = 1 \\ \hline ENVREF^2 = 1, \ T > 85 \ ^{\circ}C \\ \hline ENVREF^2 = 0 \\ \hline t_{LFRCO} & \hline \\ \hline l_{LFRCO} & ENVREF = 1 \ in \\ \hline CMU_LFRCOCTRL \\ \hline ENVREF = 0 \ in \\ \hline \end{tabular}$ | $\begin{tabular}{ c c c c } \hline f_{LFRCO} & ENVREF^2 = 1 & TBD \\ \hline ENVREF^2 = 1, T > 85 \ ^{\circ}C & TBD \\ \hline ENVREF^2 = 0 & TBD \\ \hline t_{LFRCO} & & \\ \hline l_{LFRCO} & ENVREF = 1 \ in \\ \hline CMU_LFRCOCTRL & \\ \hline ENVREF = 0 \ in & \\ \hline \end{array}$ | $ \begin{array}{c c} f_{LFRCO} & ENVREF^2 = 1 & TBD & 32.768 \\ \hline ENVREF^2 = 1, T > 85 \ ^{\circ}C & TBD & 32.768 \\ \hline ENVREF^2 = 0 & TBD & 32.768 \\ \hline ENVREF^2 = 0 & TBD & 32.768 \\ \hline t_{LFRCO} & \hline & & 500 \\ \hline l_{LFRCO} & ENVREF = 1 \ in \\ \hline CMU_LFRCOCTRL & & 370 \\ \hline ENVREF = 0 \ in & & 520 \\ \hline \end{array} $ | $ \begin{array}{c c} f_{LFRCO} & ENVREF^2 = 1 & TBD & 32.768 & TBD \\ \hline ENVREF^2 = 1, T > 85 \ ^{\circ}C & TBD & 32.768 & TBD \\ \hline ENVREF^2 = 0 & TBD & 32.768 & TBD \\ \hline ENVREF^2 = 0 & TBD & 32.768 & TBD \\ \hline t_{LFRCO} & & & 500 & \\ \hline t_{LFRCO} & ENVREF = 1 \ ^{\circ}n & & 370 & \\ \hline ENVREF = 0 \ ^{\circ}n & & 520 & \\ \hline \end{array} $ |

## Table 4.13. Low-Frequency RC Oscillator (LFRCO)

1. Block is supplied by AVDD if ANASW = 0, or DVDD if ANASW=1 in EMU\_PWRCTRL register.

2. In CMU\_LFRCOCTRL register.

## 4.1.13 Analog to Digital Converter (ADC)

Specified at 1 Msps, ADCCLK = 16 MHz, BIASPROG = 0, GPBIASACC = 0, unless otherwise indicated.

## Table 4.20. Analog to Digital Converter (ADC)

| Parameter                                                                                     | Symbol                             | Test Condition                                                           | Min                 | Тур | Мах                | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|---------------------|-----|--------------------|------|

| Resolution                                                                                    | VRESOLUTION                        |                                                                          | 6                   | —   | 12                 | Bits |

| Input voltage range <sup>5</sup>                                                              | V <sub>ADCIN</sub>                 | Single ended                                                             | _                   | —   | V <sub>FS</sub>    | V    |

|                                                                                               |                                    | Differential                                                             | -V <sub>FS</sub> /2 | _   | V <sub>FS</sub> /2 | V    |

| Input range of external refer-<br>ence voltage, single ended<br>and differential              | V <sub>ADCREFIN_P</sub>            |                                                                          | 1                   | _   | V <sub>AVDD</sub>  | V    |

| Power supply rejection <sup>2</sup>                                                           | PSRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | —                  | dB   |

| Analog input common mode rejection ratio                                                      | CMRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | -                  | dB   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | I <sub>ADC_CONTI-</sub><br>NOUS_LP | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>    | _                   | 270 | TBD                | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                          |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 1 <sup>3</sup>   | _                   | 125 | -                  | μA   |

|                                                                                               |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 1 <sup>3</sup> | _                   | 80  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | I <sub>ADC_NORMAL_LP</sub>         | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 45  | -                  | μA   |

| Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL                                  |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>     | _                   | 8   | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_STAND-<br>BY_LP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>  | _                   | 105 | -                  | μA   |

| Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 70  | _                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_CONTI-<br>NOUS_HP             | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>    | _                   | 325 | -                  | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                          |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 0 <sup>3</sup>   | _                   | 175 | -                  | μA   |

|                                                                                               |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 0 <sup>3</sup> | _                   | 125 | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_NORMAL_HP                     | 35 ksps / 16 MHz ADCCLK, BIA-SPROG = 0, GPBIASACC = 0 $^3$               | _                   | 85  | -                  | μA   |

| Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL                                  |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>     | _                   | 16  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_STAND-<br>BY_HP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>  | —                   | 160 | -                  | μA   |

| Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>   | _                   | 125 | -                  | μA   |

| Current from HFPERCLK                                                                         | IADC_CLK                           | HFPERCLK = 16 MHz                                                        | _                   | 166 | _                  | μΑ   |

| Parameter                   | Symbol                                         | Test Condition                                                                   | Min               | Тур             | Мах             | Unit      |

|-----------------------------|------------------------------------------------|----------------------------------------------------------------------------------|-------------------|-----------------|-----------------|-----------|

| Note:                       | l                                              |                                                                                  |                   |                 |                 |           |

| 1. Supply current the load. | specifications are for VD                      | AC circuitry operating with static outpo                                         | ut only and do n  | not include cur | rent required   | to drive  |

|                             | ode, the output is define<br>ngle-ended range. | d as the difference between two single                                           | e-ended outputs   | s. Absolute vol | ltage on each   | output is |

| 3. Entire range is          | monotonic and has no m                         | nissing codes.                                                                   |                   |                 |                 |           |

|                             | PERCLK is dependent<br>DAC module is enabled   | on HFPERCLK frequency. This currer<br>in the CMU.                                | nt contributes to | the total supp  | bly current use | ed when   |

|                             |                                                | pe from 10% to 90% of full scale. Offs<br>at 10% of full scale with the measured |                   | by comparing    | actual VDAC     | output at |

|                             |                                                | $\Delta V_{OUT}$ ), VDAC output at 90% of full set                               | aala              |                 |                 |           |

| Parameter                                    | Symbol             | Test Condition                                                                               | Min | Тур   | Мах | Unit |

|----------------------------------------------|--------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Slew rate <sup>5</sup>                       | SR                 | DRIVESTRENGTH = 3,<br>INCBW=1 <sup>3</sup>                                                   | _   | 4.7   | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 3,<br>INCBW=0                                                                | _   | 1.5   | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=1 <sup>3</sup>                                                   | _   | 1.27  | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=0                                                                | _   | 0.42  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.17  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=0                                                                | —   | 0.058 | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.044 | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=0                                                                | _   | 0.015 | _   | V/µs |

| Startup time <sup>6</sup>                    | T <sub>START</sub> | DRIVESTRENGTH = 2                                                                            | _   | _     | TBD | μs   |

| Input offset voltage                         | V <sub>OSI</sub>   | DRIVESTRENGTH = 2 or 3, T =<br>25 °C                                                         | TBD | _     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0, T = 25 °C                                                            | TBD | —     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 2 or 3,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

| DC power supply rejection ratio <sup>9</sup> | PSRR <sub>DC</sub> | Input referred                                                                               | —   | 70    | _   | dB   |

| DC common-mode rejection ratio <sup>9</sup>  | CMRR <sub>DC</sub> | Input referred                                                                               | _   | 70    | _   | dB   |

| Total harmonic distortion                    | THD <sub>OPA</sub> | DRIVESTRENGTH = 2, 3x Gain<br>connection, 1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V   | _   | 90    | _   | dB   |

|                                              |                    | DRIVESTRENGTH = 0, 3x Gain<br>connection, 0.1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V | _   | 90    | _   | dB   |

## 4.1.21.3 I2C Fast-mode Plus (Fm+)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min  | Тур | Мах  | Unit |

|--------------------------------------------------|---------------------|----------------|------|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0    | —   | 1000 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 0.5  | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.26 | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 50   | _   | _    | ns   |

| SDA hold time                                    | t <sub>HD_DAT</sub> |                | 100  | —   | —    | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.26 |     |      | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.26 |     | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.26 | —   | —    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 0.5  | _   | _    | μs   |

## Table 4.30. I2C Fast-mode Plus (Fm+)<sup>1</sup>

## Note:

1. For CLHR set to 0 or 1 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Fast-mode Plus, refer to the I2C chapter in the reference manual.

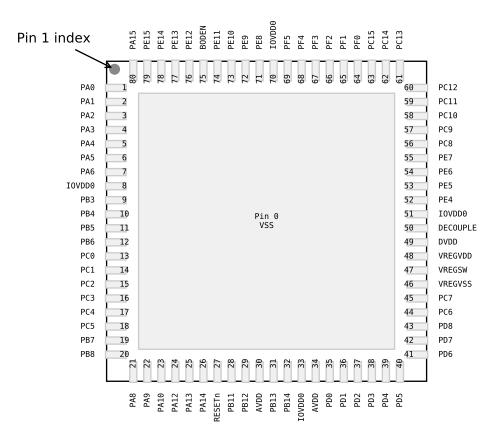

### Figure 5.2. EFM32TG11B5xx in QFN80 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.2. E | EFM32TG11B5xx | in QFN80 | <b>Device Pinout</b> |

|--------------|---------------|----------|----------------------|

|--------------|---------------|----------|----------------------|

| Pin Name | Pin(s)              | Description                | Pin Name | Pin(s) | Description |

|----------|---------------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0<br>46             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2                   | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4                   | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6                   | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>33<br>51<br>70 | Digital IO power supply 0. | PB3      | 9      | GPIO        |

| Pin Name              | Pin(s) | Description | Pin Name | Pin(s) | Description |  |  |  |

|-----------------------|--------|-------------|----------|--------|-------------|--|--|--|

| PE15                  | 79     | GPIO        | PA15     | 80     | GPIO        |  |  |  |

| Note:<br>1. GPIO with |        |             |          |        |             |  |  |  |

| Pin Name | Pin(s)   | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB4      | 10       | GPIO                          | PB5      | 11     | GPIO                                                                                                                                                                                                        |

| PB6      | 12       | GPIO                          | PC4      | 13     | GPIO                                                                                                                                                                                                        |

| PC5      | 14       | GPIO                          | PB7      | 15     | GPIO                                                                                                                                                                                                        |

| PB8      | 16       | GPIO                          | PA8      | 17     | GPIO                                                                                                                                                                                                        |

| PA12     | 18       | GPIO                          | PA13     | 19     | GPIO (5V)                                                                                                                                                                                                   |

| PA14     | 20       | GPIO                          | RESETn   | 21     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 22       | GPIO                          | PB12     | 23     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.          | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26       | GPIO                          | PD0      | 29     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 30       | GPIO                          | PD3      | 31     | GPIO                                                                                                                                                                                                        |

| PD4      | 32       | GPIO                          | PD5      | 33     | GPIO                                                                                                                                                                                                        |

| PD6      | 34       | GPIO                          | PD7      | 35     | GPIO                                                                                                                                                                                                        |

| PD8      | 36       | GPIO                          | PC7      | 37     | GPIO                                                                                                                                                                                                        |

| VREGSW   | 39       | DCDC regulator switching node | VREGVDD  | 40     | Voltage regulator VDD input                                                                                                                                                                                 |

| DVDD     | 41       | Digital power supply.         | DECOUPLE | 42     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PE4      | 43       | GPIO                          | PE5      | 44     | GPIO                                                                                                                                                                                                        |

| PE6      | 45       | GPIO                          | PE7      | 46     | GPIO                                                                                                                                                                                                        |

| PC12     | 47       | GPIO (5V)                     | PC13     | 48     | GPIO (5V)                                                                                                                                                                                                   |

| PF0      | 49       | GPIO (5V)                     | PF1      | 50     | GPIO (5V)                                                                                                                                                                                                   |

| PF2      | 51       | GPIO                          | PF3      | 52     | GPIO                                                                                                                                                                                                        |

| PF4      | 53       | GPIO                          | PF5      | 54     | GPIO                                                                                                                                                                                                        |

| PE8      | 56       | GPIO                          | PE9      | 57     | GPIO                                                                                                                                                                                                        |

| PE10     | 58       | GPIO                          | PE11     | 59     | GPIO                                                                                                                                                                                                        |

| PE12     | 60       | GPIO                          | PE13     | 61     | GPIO                                                                                                                                                                                                        |

| PE14     | 62       | GPIO                          | PE15     | 63     | GPIO                                                                                                                                                                                                        |

| PA15     | 64       | GPIO                          |          |        |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s) | Description           | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|-----------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB8      | 8      | GPIO                  | RESETn   | 9        | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 10     | GPIO                  | AVDD     | 11<br>15 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 12     | GPIO                  | PB14     | 13       | GPIO                                                                                                                                                                                                        |

| PD4      | 16     | GPIO                  | PD5      | 17       | GPIO                                                                                                                                                                                                        |

| PD6      | 18     | GPIO                  | PD7      | 19       | GPIO                                                                                                                                                                                                        |

| DVDD     | 20     | Digital power supply. | DECOUPLE | 21       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PC13     | 22     | GPIO (5V)             | PC14     | 23       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 24     | GPIO (5V)             | PF0      | 25       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 26     | GPIO (5V)             | PF2      | 27       | GPIO                                                                                                                                                                                                        |

| PE10     | 29     | GPIO                  | PE11     | 30       | GPIO                                                                                                                                                                                                        |

| PE12     | 31     | GPIO                  | PE13     | 32       | GPIO                                                                                                                                                                                                        |

| Note:    |        | ,                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Alternate               | LOCA    | TION  |                                                                  |

|-------------------------|---------|-------|------------------------------------------------------------------|

| Functionality           | 0 - 3   | 4 - 7 | Description                                                      |

| LCD_SEG9                | 0: PE13 |       | LCD segment line 9.                                              |

| LCD_SEG10               | 0: PE14 |       | LCD segment line 10.                                             |

| LCD_SEG11               | 0: PE15 |       | LCD segment line 11.                                             |

| LCD_SEG12               | 0: PA15 |       | LCD segment line 12.                                             |

| LCD_SEG13               | 0: PA0  |       | LCD segment line 13.                                             |

| LCD_SEG14               | 0: PA1  |       | LCD segment line 14.                                             |

| LCD_SEG15               | 0: PA2  |       | LCD segment line 15.                                             |

| LCD_SEG16               | 0: PA3  |       | LCD segment line 16.                                             |

| LCD_SEG17               | 0: PA4  |       | LCD segment line 17.                                             |

| LCD_SEG18               | 0: PA5  |       | LCD segment line 18.                                             |

| LCD_SEG19               | 0: PA6  |       | LCD segment line 19.                                             |

| LCD_SEG20 /<br>LCD_COM4 | 0: PB3  |       | LCD segment line 20. This pin may also be used as LCD COM line 4 |

| LCD_SEG21 /<br>LCD_COM5 | 0: PB4  |       | LCD segment line 21. This pin may also be used as LCD COM line 5 |

| Alternate                                | LOCA<br>0 - 3   | ATION<br>4 - 7 | Description                                                                     |

|------------------------------------------|-----------------|----------------|---------------------------------------------------------------------------------|

| Functionality<br>LCD_SEG22 /<br>LCD_COM6 | 0 - 3<br>0: PB5 | 4 - 7          | Description<br>LCD segment line 22. This pin may also be used as LCD COM line 6 |

| LCD_SEG23 /<br>LCD_COM7                  | 0: PB6          |                | LCD segment line 23. This pin may also be used as LCD COM line 7                |

| LCD_SEG24                                | 0: PC4          |                | LCD segment line 24.                                                            |

| LCD_SEG25                                | 0: PC5          |                | LCD segment line 25.                                                            |

| LCD_SEG26                                | 0: PA9          |                | LCD segment line 26.                                                            |

| LCD_SEG27                                | 0: PA10         |                | LCD segment line 27.                                                            |

| LCD_SEG28                                | 0: PB11         |                | LCD segment line 28.                                                            |

| LCD_SEG29                                | 0: PB12         |                | LCD segment line 29.                                                            |

| LCD_SEG30                                | 0: PD3          |                | LCD segment line 30.                                                            |

| LCD_SEG31                                | 0: PD4          |                | LCD segment line 31.                                                            |

| LCD_SEG32                                | 0: PC6          |                | LCD segment line 32.                                                            |

| LCD_SEG33                                | 0: PC7          |                | LCD segment line 33.                                                            |

| LCD_SEG34                                | 0: PC8          |                | LCD segment line 34.                                                            |

| Alternate     | LOC                                    | ATION                        |                                                                                                                    |

|---------------|----------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                  | 4 - 7                        | Description                                                                                                        |

| LETIM0_OUT1   | 0: PD7<br>1: PB12<br>2: PF1<br>3: PC5  | 4: PE13<br>5: PC15<br>6: PA9 | Low Energy Timer LETIM0, output channel 1.                                                                         |

| LEU0_RX       | 0: PD5<br>1: PB14<br>2: PE15<br>3: PF1 | 4: PA0<br>5: PC15            | LEUART0 Receive input.                                                                                             |

| LEU0_TX       | 0: PD4<br>1: PB13<br>2: PE14<br>3: PF0 | 4: PF2<br>5: PC14            | LEUART0 Transmit output. Also used as receive input in half duplex communication.                                  |

| LFXTAL_N      | 0: PB8                                 |                              | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional ex-<br>ternal clock input pin. |

| LFXTAL_P      | 0: PB7                                 |                              | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                         |

| OPA0_N        | 0: PC5                                 |                              | Operational Amplifier 0 external negative input.                                                                   |

| OPA0_P        | 0: PC4                                 |                              | Operational Amplifier 0 external positive input.                                                                   |

| OPA1_N        | 0: PD7                                 |                              | Operational Amplifier 1 external negative input.                                                                   |

| OPA1_P        | 0: PD6                                 |                              | Operational Amplifier 1 external positive input.                                                                   |

| OPA2_N        | 0: PD3                                 |                              | Operational Amplifier 2 external negative input.                                                                   |