Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Discontinued at Digi-Key                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                              |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-TQFP                                                                  |

| Supplier Device Package    | 48-TQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b140f64gq48-a |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2. Ordering Information

## Table 2.1. Ordering Information

|                         | Flash | RAM  | DC-DC<br>Con- |     |      |         |               |

|-------------------------|-------|------|---------------|-----|------|---------|---------------|

| Ordering Code           | (kB)  | (kB) | verter        | LCD | GPIO | Package | Temp Range    |

| EFM32TG11B520F128GM80-A | 128   | 32   | Yes           | Yes | 67   | QFN80   | -40 to +85°C  |

| EFM32TG11B520F128GQ80-A | 128   | 32   | Yes           | Yes | 63   | QFP80   | -40 to +85°C  |

| EFM32TG11B520F128IM80-A | 128   | 32   | Yes           | Yes | 67   | QFN80   | -40 to +125°C |

| EFM32TG11B520F128IQ80-A | 128   | 32   | Yes           | Yes | 63   | QFP80   | -40 to +125°C |

| EFM32TG11B540F64GM80-A  | 64    | 32   | Yes           | Yes | 67   | QFN80   | -40 to +85°C  |

| EFM32TG11B540F64GQ80-A  | 64    | 32   | Yes           | Yes | 63   | QFP80   | -40 to +85°C  |

| EFM32TG11B540F64IM80-A  | 64    | 32   | Yes           | Yes | 67   | QFN80   | -40 to +125°C |

| EFM32TG11B540F64IQ80-A  | 64    | 32   | Yes           | Yes | 63   | QFP80   | -40 to +125°C |

| EFM32TG11B520F128GM64-A | 128   | 32   | Yes           | Yes | 53   | QFN64   | -40 to +85°C  |

| EFM32TG11B520F128GQ64-A | 128   | 32   | Yes           | Yes | 50   | QFP64   | -40 to +85°C  |

| EFM32TG11B520F128IM64-A | 128   | 32   | Yes           | Yes | 53   | QFN64   | -40 to +125°C |

| EFM32TG11B520F128IQ64-A | 128   | 32   | Yes           | Yes | 50   | QFP64   | -40 to +125°C |

| EFM32TG11B540F64GM64-A  | 64    | 32   | Yes           | Yes | 53   | QFN64   | -40 to +85°C  |

| EFM32TG11B540F64GQ64-A  | 64    | 32   | Yes           | Yes | 50   | QFP64   | -40 to +85°C  |

| EFM32TG11B540F64IM64-A  | 64    | 32   | Yes           | Yes | 53   | QFN64   | -40 to +125°C |

| EFM32TG11B540F64IQ64-A  | 64    | 32   | Yes           | Yes | 50   | QFP64   | -40 to +125°C |

| EFM32TG11B520F128GQ48-A | 128   | 32   | Yes           | Yes | 34   | QFP48   | -40 to +85°C  |

| EFM32TG11B520F128IQ48-A | 128   | 32   | Yes           | Yes | 34   | QFP48   | -40 to +125°C |

| EFM32TG11B540F64GQ48-A  | 64    | 32   | Yes           | Yes | 34   | QFP48   | -40 to +85°C  |

| EFM32TG11B540F64IQ48-A  | 64    | 32   | Yes           | Yes | 34   | QFP48   | -40 to +125°C |

| EFM32TG11B520F128GM32-A | 128   | 32   | Yes           | Yes | 22   | QFN32   | -40 to +85°C  |

| EFM32TG11B520F128IM32-A | 128   | 32   | Yes           | Yes | 22   | QFN32   | -40 to +125°C |

| EFM32TG11B540F64GM32-A  | 64    | 32   | Yes           | Yes | 22   | QFN32   | -40 to +85°C  |

| EFM32TG11B540F64IM32-A  | 64    | 32   | Yes           | Yes | 22   | QFN32   | -40 to +125°C |

| EFM32TG11B320F128GM64-A | 128   | 32   | No            | Yes | 56   | QFN64   | -40 to +85°C  |

| EFM32TG11B320F128GQ64-A | 128   | 32   | No            | Yes | 53   | QFP64   | -40 to +85°C  |

| EFM32TG11B320F128IM64-A | 128   | 32   | No            | Yes | 56   | QFN64   | -40 to +125°C |

| EFM32TG11B320F128IQ64-A | 128   | 32   | No            | Yes | 53   | QFP64   | -40 to +125°C |

| EFM32TG11B340F64GM64-A  | 64    | 32   | No            | Yes | 56   | QFN64   | -40 to +85°C  |

| EFM32TG11B340F64GQ64-A  | 64    | 32   | No            | Yes | 53   | QFP64   | -40 to +85°C  |

| EFM32TG11B340F64IM64-A  | 64    | 32   | No            | Yes | 56   | QFN64   | -40 to +125°C |

| EFM32TG11B340F64IQ64-A  | 64    | 32   | No            | Yes | 53   | QFP64   | -40 to +125°C |

| Ordering Code           | Flash<br>(kB) | RAM<br>(kB) | DC-DC<br>Con-<br>verter | LCD | GPIO | Package | Temp Range    |

|-------------------------|---------------|-------------|-------------------------|-----|------|---------|---------------|

| EFM32TG11B320F128GQ48-A | 128           | 32          | No                      | Yes | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B320F128IQ48-A | 128           | 32          | No                      | Yes | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B340F64GQ48-A  | 64            | 32          | No                      | Yes | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B340F64IQ48-A  | 64            | 32          | No                      | Yes | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B120F128GM64-A | 128           | 32          | No                      | No  | 56   | QFN64   | -40 to +85°C  |

| EFM32TG11B120F128GQ64-A | 128           | 32          | No                      | No  | 53   | QFP64   | -40 to +85°C  |

| EFM32TG11B120F128IM64-A | 128           | 32          | No                      | No  | 56   | QFN64   | -40 to +125°C |

| EFM32TG11B120F128IQ64-A | 128           | 32          | No                      | No  | 53   | QFP64   | -40 to +125°C |

| EFM32TG11B140F64GM64-A  | 64            | 32          | No                      | No  | 56   | QFN64   | -40 to +85°C  |

| EFM32TG11B140F64GQ64-A  | 64            | 32          | No                      | No  | 53   | QFP64   | -40 to +85°C  |

| EFM32TG11B140F64IM64-A  | 64            | 32          | No                      | No  | 56   | QFN64   | -40 to +125°C |

| EFM32TG11B140F64IQ64-A  | 64            | 32          | No                      | No  | 53   | QFP64   | -40 to +125°C |

| EFM32TG11B120F128GQ48-A | 128           | 32          | No                      | No  | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B120F128IQ48-A | 128           | 32          | No                      | No  | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B140F64GQ48-A  | 64            | 32          | No                      | No  | 37   | QFP48   | -40 to +85°C  |

| EFM32TG11B140F64IQ48-A  | 64            | 32          | No                      | No  | 37   | QFP48   | -40 to +125°C |

| EFM32TG11B120F128GM32-A | 128           | 32          | No                      | No  | 24   | QFN32   | -40 to +85°C  |

| EFM32TG11B120F128IM32-A | 128           | 32          | No                      | No  | 24   | QFN32   | -40 to +125°C |

| EFM32TG11B140F64GM32-A  | 64            | 32          | No                      | No  | 24   | QFN32   | -40 to +85°C  |

| EFM32TG11B140F64IM32-A  | 64            | 32          | No                      | No  | 24   | QFN32   | -40 to +125°C |

## 3. System Overview

### 3.1 Introduction

The Tiny Gecko Series 1 product family is well suited for any battery operated application as well as other systems requiring high performance and low energy consumption. This section gives a short introduction to the MCU system. The detailed functional description can be found in the Tiny Gecko Series 1 Reference Manual. Any behavior that does not conform to the specifications in this data sheet or the functional descriptions in the Tiny Gecko Series 1 Reference Manual are detailed in the EFM32TG11 Errata document.

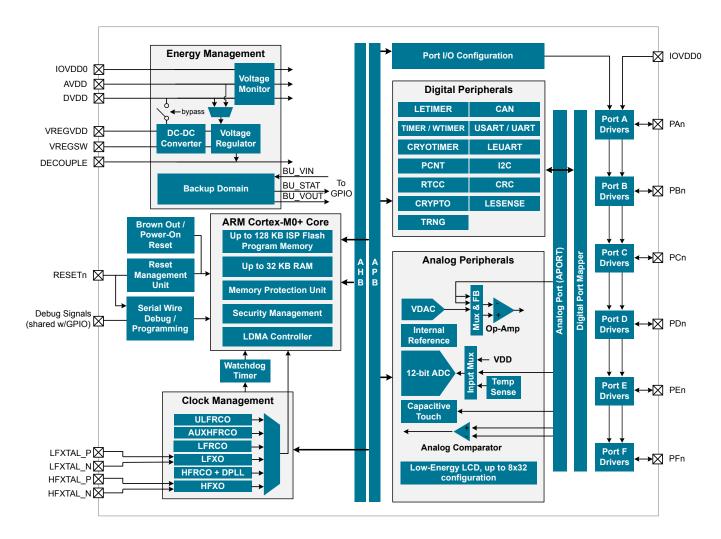

A block diagram of the Tiny Gecko Series 1 family is shown in Figure 3.1 Detailed EFM32TG11 Block Diagram on page 10. The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Detailed EFM32TG11 Block Diagram

#### 3.10 Core and Memory

### 3.10.1 Processor Core

The ARM Cortex-M processor includes a 32-bit RISC processor integrating the following features and tasks in the system:

- ARM Cortex-M0+ RISC processor

- Memory Protection Unit (MPU) supporting up to 8 memory segments

- Micro-Trace Buffer (MTB)

- Up to 128 kB flash program memory

- · Up to 32 kB RAM data memory

- · Configuration and event handling of all modules

- · 2-pin Serial-Wire debug interface

### 3.10.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block, whereas the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

### 3.10.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling so-phisticated operations to be implemented.

#### 3.10.4 Bootloader

All devices come pre-programmed with a UART bootloader. This bootloader resides in flash and can be erased if it is not needed. More information about the bootloader protocol and usage can be found in *AN0003: UART Bootloader*. Application notes can be found on the Silicon Labs website (www.silabs.com/32bit-appnotes) or within Simplicity Studio in the [**Documentation**] area.

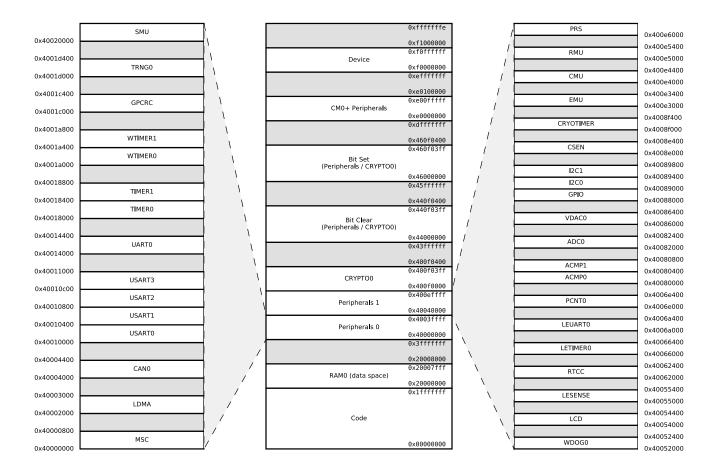

Figure 3.3. EFM32TG11 Memory Map — Peripherals

### 3.12 Configuration Summary

The features of the EFM32TG11 are a subset of the feature set described in the device reference manual. The table below describes device specific implementation of the features. Remaining modules support full configuration.

| Table 3.2. | Configuration | Summary |

|------------|---------------|---------|

|------------|---------------|---------|

| Module  | Configuration               | Pin Connections                 |

|---------|-----------------------------|---------------------------------|

| USART0  | IrDA, SmartCard             | US0_TX, US0_RX, US0_CLK, US0_CS |

| USART1  | I <sup>2</sup> S, SmartCard | US1_TX, US1_RX, US1_CLK, US1_CS |

| USART2  | IrDA, SmartCard, High-Speed | US2_TX, US2_RX, US2_CLK, US2_CS |

| USART3  | I <sup>2</sup> S, SmartCard | US3_TX, US3_RX, US3_CLK, US3_CS |

| TIMER0  | with DTI                    | TIM0_CC[2:0], TIM0_CDTI[2:0]    |

| TIMER1  | -                           | TIM1_CC[3:0]                    |

| WTIMER0 | with DTI                    | WTIM0_CC[2:0], WTIM0_CDTI[2:0]  |

| WTIMER1 | -                           | WTIM1_CC[3:0]                   |

| Parameter                      | Symbol                | Test Condition                                                        | Min                 | Тур              | Мах             | Unit      |

|--------------------------------|-----------------------|-----------------------------------------------------------------------|---------------------|------------------|-----------------|-----------|

| Note:                          |                       |                                                                       |                     |                  |                 |           |

|                                |                       | mode is calculated using $R_{BYP}$ _min+ILOAD * $R_{BYP}$ _max.       | from the DCDC spec  | cification table | e. Requiremer   | nts for   |

| 2. VREGVDD must be             | e tied to AVDD. Both  | VREGVDD and AVDD minimum                                              | voltages must be sa | atisfied for the | part to opera   | te.       |

|                                |                       | characteristic specs of the capa oss temperature and DC bias.         | citor used on DECOU | JPLE to ensu     | re its capacita | ance val- |

|                                | will be dependent on  | transitions occur at a rate of 10 r<br>the value of the DECOUPLE ou   |                     |                  |                 |           |

| 5. When the CSEN pe            | ripheral is used with | chopping enabled (CSEN_CTRI                                           | CHOPEN = ENAB       | LE), IOVDD n     | nust be equal   | to AVDE   |

| cation. T <sub>A</sub> (max) = |                       | due to device self-heating, which<br>x PowerDissipation). Refer to th |                     | •                | -               |           |

## 4.1.3 Thermal Characteristics

| Parameter                  | Symbol                    | Test Condition                    | Min | Тур  | Мах                                                   | Unit |

|----------------------------|---------------------------|-----------------------------------|-----|------|-------------------------------------------------------|------|

| Thermal resistance, QFN32  | THETA <sub>JA_QFN32</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 25.7 | _                                                     | °C/W |

| Package                    |                           | 4-Layer PCB, Air velocity = 1 m/s | _   | 23.2 | _                                                     | °C/W |

|                            |                           | 4-Layer PCB, Air velocity = 2 m/s | _   | 21.3 | _                                                     | °C/W |

| Thermal resistance, TQFP48 | THE-                      | 4-Layer PCB, Air velocity = 0 m/s | _   | 44.1 | _                                                     | °C/W |

| Package                    | TA <sub>JA_TQFP48</sub>   | 4-Layer PCB, Air velocity = 1 m/s |     | 43.5 | _                                                     | °C/W |

|                            |                           | 4-Layer PCB, Air velocity = 2 m/s |     | 42.3 | Max                                                   | °C/W |

| Thermal resistance, QFN64  | THETA <sub>JA_QFN64</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 20.9 | _                                                     | °C/W |

| Package                    |                           | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _                                                     | °C/W |

|                            |                           | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | 4 <u> </u>                                            | °C/W |

| Thermal resistance, TQFP64 |                           | 4-Layer PCB, Air velocity = 0 m/s | _   | 37.3 | _                                                     | °C/W |

| Package                    | TA <sub>JA_TQFP64</sub>   | 4-Layer PCB, Air velocity = 1 m/s | _   | 35.6 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | °C/W |

|                            |                           | 4-Layer PCB, Air velocity = 2 m/s | _   | 33.8 |                                                       | °C/W |

| Thermal resistance, QFN80  | THETA <sub>JA_QFN80</sub> | 4-Layer PCB, Air velocity = 0 m/s |     | 20.9 | _                                                     | °C/W |

| Package                    |                           | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 |                                                       | °C/W |

|                            |                           | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _                                                     | °C/W |

| Thermal resistance, TQFP80 | THE-                      | 4-Layer PCB, Air velocity = 0 m/s | _   | 49.3 | _                                                     | °C/W |

| Package                    | TA <sub>JA_TQFP80</sub>   | 4-Layer PCB, Air velocity = 1 m/s | _   | 44.5 | _                                                     | °C/W |

|                            |                           | 4-Layer PCB, Air velocity = 2 m/s | _   | 42.6 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | °C/W |

### Table 4.3. Thermal Characteristics

### 4.1.6.2 Current Consumption 3.3 V using DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = IOVDD = 3.3 V, DVDD = 1.8 V DC-DC output. T = 25 °C. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

| Parameter                                                    | Symbol      | Test Condition                                        | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------|-------------|-------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>mode with all peripherals dis- | IACTIVE_DCM | 48 MHz crystal, CPU running while loop from flash     | _   | 38   | -   | µA/MHz |

| abled, DCDC in Low Noise<br>DCM mode <sup>2</sup>            |             | 48 MHz HFRCO, CPU running while loop from flash       | _   | 37   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>Prime from flash         | _   | 45   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash | _   | 53   | _   | µA/MHz |

|                                                              |             | 32 MHz HFRCO, CPU running while loop from flash       | _   | 43   | _   | µA/MHz |

|                                                              |             | 26 MHz HFRCO, CPU running while loop from flash       |     | 47   | _   | µA/MHz |

|                                                              |             | 16 MHz HFRCO, CPU running while loop from flash       |     | 61   | _   | µA/MHz |

|                                                              |             | 1 MHz HFRCO, CPU running while loop from flash        |     | 587  | _   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis- | IACTIVE_CCM | 48 MHz crystal, CPU running while loop from flash     | _   | 49   | _   | µA/MHz |

| abled, DCDC in Low Noise<br>CCM mode <sup>1</sup>            |             | 48 MHz HFRCO, CPU running while loop from flash       |     | 48   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>Prime from flash         | _   | 55   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash |     | 63   | _   | µA/MHz |

|                                                              |             | 32 MHz HFRCO, CPU running while loop from flash       |     | 60   | _   | µA/MHz |

|                                                              |             | 26 MHz HFRCO, CPU running while loop from flash       |     | 68   | _   | µA/MHz |

|                                                              |             | 16 MHz HFRCO, CPU running while loop from flash       |     | 96   | _   | µA/MHz |

|                                                              |             | 1 MHz HFRCO, CPU running while loop from flash        |     | 1157 | _   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis- | IACTIVE_LPM | 32 MHz HFRCO, CPU running while loop from flash       | _   | 32   | _   | µA/MHz |

| abled, DCDC in LP mode <sup>3</sup>                          |             | 26 MHz HFRCO, CPU running while loop from flash       |     | 33   | _   | µA/MHz |

|                                                              |             | 16 MHz HFRCO, CPU running while loop from flash       |     | 36   | _   | µA/MHz |

|                                                              |             | 1 MHz HFRCO, CPU running while loop from flash        | _   | 156  | _   | µA/MHz |

| Parameter                                                                                                               | Symbol  | Test Condition                                                                                          | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled,<br>DCDC in LP mode <sup>3</sup> | IPD1_VS | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>4</sup> |     | 0.18 | _   | μA   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled,<br>DCDC in LP mode <sup>3</sup> | IPD2_VS | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>4</sup> |     | 0.18 |     | μA   |

Note:

1. DCDC Low Noise CCM Mode = Light Drive (PFETCNT=NFETCNT=3), F=6.4 MHz (RCOBAND=4), ANASW=DVDD.

2. DCDC Low Noise DCM Mode = Light Drive (PFETCNT=NFETCNT=3), F=3.0 MHz (RCOBAND=0), ANASW=DVDD.

3. DCDC Low Power Mode = Medium Drive (PFETCNT=NFETCNT=7), LPOSCDIV=1, LPCMPBIASEM234H=0, LPCLIMILIM-SEL=1, ANASW=DVDD.

4. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.3 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

5. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

| Parameter        | Symbol                  | Test Condition                        | Min | Тур | Мах | Unit |

|------------------|-------------------------|---------------------------------------|-----|-----|-----|------|

| Frequency limits | f <sub>HFRCO_BAND</sub> | FREQRANGE = 0, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 3, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 6, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 7, FINETUNIN-<br>GEN = 0  | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 8, FINETUNIN-<br>GEN = 0  | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 10, FINETUNIN-<br>GEN = 0 | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 11, FINETUNIN-<br>GEN = 0 | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 12, FINETUNIN-<br>GEN = 0 | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 13, FINETUNIN-<br>GEN = 0 | TBD | _   | TBD | MHz  |

### 4.1.10 Flash Memory Characteristics<sup>5</sup>

| Parameter                                   | Symbol               | Test Condition                                | Min   | Тур | Мах | Unit   |

|---------------------------------------------|----------------------|-----------------------------------------------|-------|-----|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                                               | 10000 | _   | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T ≤ 85 °C                                     | 10    | _   | _   | years  |

|                                             |                      | T ≤ 125 °C                                    | 10    |     | _   | years  |

| Word (32-bit) programming time              | tw_prog              | Burst write, 128 words, average time per word | 20    | 26  | 32  | μs     |

|                                             |                      | Single word                                   | 59    | 68  | 83  | μs     |

| Page erase time <sup>4</sup>                | t <sub>PERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Device erase time <sup>2 3</sup>            | t <sub>DERASE</sub>  | T ≤ 85 °C                                     | _     | 54  | 70  | ms     |

|                                             |                      | T ≤ 125 °C                                    | _     | 54  | 75  | ms     |

| Erase current <sup>6</sup>                  | I <sub>ERASE</sub>   | Page Erase                                    | _     | _   | 1.7 | mA     |

|                                             |                      | Mass or Device Erase                          | _     |     | 2.0 | mA     |

| Write current <sup>6</sup>                  | I <sub>WRITE</sub>   |                                               | —     |     | 3.5 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                                               | 1.62  | _   | 3.6 | V      |

### Table 4.17. Flash Memory Characteristics<sup>5</sup>

# Note:

- 1. Mass erase is issued by the CPU and erases all flash.

- 2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

- 3. From setting the DEVICEERASE bit in AAP\_CMD to 1 until the ERASEBUSY bit in AAP\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 4. From setting the ERASEPAGE bit in MSC\_WRITECMD to 1 until the BUSY bit in MSC\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 5. Flash data retention information is published in the Quarterly Quality and Reliability Report.

6. Measured at 25 °C.

### 4.1.12 Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Мах | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | I <sub>VMON</sub>       | In EM0 or EM1, 1 supply monitored, T $\leq$ 85 °C                | _    | 6.3  | TBD | μA   |

|                                    |                         | In EM0 or EM1, 4 supplies monitored, T $\leq$ 85 °C              | —    | 12.5 | TBD | μA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshold       | —    | 62   |     | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | —    | 62   |     | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | _    | 99   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold | _    | 99   | _   | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | —    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    | _   | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | _    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  |     | mV   |

|                                    |                         | Fine                                                             | —    | 20   | _   | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | —    | 460  | _   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  |      | 26   | _   | mV   |

### Table 4.19. Voltage Monitor (VMON)

### 4.1.16 Capacitive Sense (CSEN)

| Parameter                                                                           | Symbol              | Test Condition                                                                                                                                                   | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Single conversion time (1x                                                          | t <sub>CNV</sub>    | 12-bit SAR Conversions                                                                                                                                           | _   | 20.2 | _   | μs   |

| accumulation)                                                                       |                     | 16-bit SAR Conversions                                                                                                                                           | _   | 26.4 | _   | μs   |

|                                                                                     |                     | Delta Modulation Conversion (sin-<br>gle comparison)                                                                                                             | _   | 1.55 | _   | μs   |

| Maximum external capacitive load                                                    | C <sub>EXTMAX</sub> | CS0CG=7 (Gain = 1x), including routing parasitics                                                                                                                | _   | 68   |     | pF   |

|                                                                                     |                     | CS0CG=0 (Gain = 10x), including routing parasitics                                                                                                               | —   | 680  |     | pF   |

| Maximum external series impedance                                                   | R <sub>EXTMAX</sub> |                                                                                                                                                                  | _   | 1    | _   | kΩ   |

| Supply current, EM2 bonded<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-<br>MUPCNT=0 | ICSEN_BOND          | 12-bit SAR conversions, 20 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                       | _   | 326  | _   | nA   |

|                                                                                     |                     | Delta Modulation conversions, 20<br>ms conversion rate, CS0CG=7<br>(Gain = 1x), 10 channels bonded<br>(total capacitance of 330 pF) <sup>1</sup>                 | _   | 226  | _   | nA   |

|                                                                                     |                     | 12-bit SAR conversions, 200 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                      | _   | 33   | _   | nA   |

|                                                                                     |                     | Delta Modulation conversions,<br>200 ms conversion rate,<br>CS0CG=7 (Gain = 1x), 10 chan-<br>nels bonded (total capacitance of<br>330 pF) <sup>1</sup>           | _   | 25   | _   | nA   |

| Supply current, EM2 scan<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-               | ICSEN_EM2           | 12-bit SAR conversions, 20 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                             | —   | 690  | _   | nA   |

| MUPCNT=0                                                                            |                     | Delta Modulation conversions, 20<br>ms scan rate, 8 comparisons per<br>sample (DMCR = 1, DMR = 2),<br>CS0CG=0 (Gain = 10x), 8 sam-<br>ples per scan <sup>1</sup> | _   | 515  | _   | nA   |

|                                                                                     |                     | 12-bit SAR conversions, 200 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                            | —   | 79   | _   | nA   |

|                                                                                     |                     | Delta Modulation conversions,<br>200 ms scan rate, 8 comparisons<br>per sample (DMCR = 1, DMR =<br>2), CS0CG=0 (Gain = 10x), 8<br>samples per scan <sup>1</sup>  | _   | 57   |     | nA   |

### Table 4.23. Capacitive Sense (CSEN)

| Pin Name | Pin(s)   | Description                                                                                              | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|----------------------------------------------------------------------------------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13       | GPIO                                                                                                     | PC5      | 14     | GPIO                                                                                                                                                                                                        |

| PB7      | 15       | GPIO                                                                                                     | PB8      | 16     | GPIO                                                                                                                                                                                                        |

| PA8      | 17       | GPIO                                                                                                     | PA12     | 18     | GPIO                                                                                                                                                                                                        |

| PA14     | 19       | GPIO                                                                                                     | RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21       | GPIO                                                                                                     | PB12     | 22     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.                                                                                     | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26       | GPIO                                                                                                     | PD0      | 29     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 30       | GPIO                                                                                                     | PD3      | 31     | GPIO                                                                                                                                                                                                        |

| PD4      | 32       | GPIO                                                                                                     | PD5      | 33     | GPIO                                                                                                                                                                                                        |

| PD6      | 34       | GPIO                                                                                                     | PD7      | 35     | GPIO                                                                                                                                                                                                        |

| PD8      | 36       | GPIO                                                                                                     | PC7      | 37     | GPIO                                                                                                                                                                                                        |

| VREGVSS  | 38       | Voltage regulator VSS                                                                                    | VREGSW   | 39     | DCDC regulator switching node                                                                                                                                                                               |

| VREGVDD  | 40       | Voltage regulator VDD input                                                                              | DVDD     | 41     | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 42       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PE4      | 43     | GPIO                                                                                                                                                                                                        |

| PE5      | 44       | GPIO                                                                                                     | PE6      | 45     | GPIO                                                                                                                                                                                                        |

| PE7      | 46       | GPIO                                                                                                     | PC12     | 47     | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 48       | GPIO (5V)                                                                                                | PF0      | 49     | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50       | GPIO (5V)                                                                                                | PF2      | 51     | GPIO                                                                                                                                                                                                        |

| PF3      | 52       | GPIO                                                                                                     | PF4      | 53     | GPIO                                                                                                                                                                                                        |

| PF5      | 54       | GPIO                                                                                                     | PE8      | 57     | GPIO                                                                                                                                                                                                        |

| PE9      | 58       | GPIO                                                                                                     | PE10     | 59     | GPIO                                                                                                                                                                                                        |

| PE11     | 60       | GPIO                                                                                                     | PE12     | 61     | GPIO                                                                                                                                                                                                        |

| PE13     | 62       | GPIO                                                                                                     | PE14     | 63     | GPIO                                                                                                                                                                                                        |

| PE15     | 64       | GPIO                                                                                                     |          |        |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s)   | Description                                                                                                                                                                                                 | Pin Name | Pin(s) | Description                   |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-------------------------------|

| PB8      | 11       | GPIO                                                                                                                                                                                                        | PA8      | 12     | GPIO                          |

| PA12     | 13       | GPIO                                                                                                                                                                                                        | PA14     | 14     | GPIO                          |

| RESETn   | 15       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB11     | 16     | GPIO                          |

| AVDD     | 18<br>22 | Analog power supply.                                                                                                                                                                                        | PB13     | 19     | GPIO                          |

| PB14     | 20       | GPIO                                                                                                                                                                                                        | PD4      | 23     | GPIO                          |

| PD5      | 24       | GPIO                                                                                                                                                                                                        | PD6      | 25     | GPIO                          |

| PD7      | 26       | GPIO                                                                                                                                                                                                        | PD8      | 27     | GPIO                          |

| VREGVSS  | 28       | Voltage regulator VSS                                                                                                                                                                                       | VREGSW   | 29     | DCDC regulator switching node |

| VREGVDD  | 30       | Voltage regulator VDD input                                                                                                                                                                                 | DVDD     | 31     | Digital power supply.         |

| DECOUPLE | 32       | Decouple output for on-chip voltage<br>regulator. An external decoupling ca-<br>pacitor is required at this pin.                                                                                            | PE4      | 33     | GPIO                          |

| PE5      | 34       | GPIO                                                                                                                                                                                                        | PE6      | 35     | GPIO                          |

| PE7      | 36       | GPIO                                                                                                                                                                                                        | PF0      | 37     | GPIO (5V)                     |

| PF1      | 38       | GPIO (5V)                                                                                                                                                                                                   | PF2      | 39     | GPIO                          |

| PF3      | 40       | GPIO                                                                                                                                                                                                        | PF4      | 41     | GPIO                          |

| PF5      | 42       | GPIO                                                                                                                                                                                                        | PE10     | 45     | GPIO                          |

| PE11     | 46       | GPIO                                                                                                                                                                                                        | PE12     | 47     | GPIO                          |

| PE13     | 48       | GPIO                                                                                                                                                                                                        |          |        |                               |

1. GPIO with 5V tolerance are indicated by (5V).

### Figure 5.13. EFM32TG11B1xx in QFN32 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.13. EFM32TG11B1xx in QFN32 Devic | e Pinout |

|------------------------------------------|----------|

|------------------------------------------|----------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| IOVDD0   | 4<br>14<br>28 | Digital IO power supply 0. | PC0      | 5      | GPIO (5V)   |

| PC1      | 6             | GPIO (5V)                  | PB7      | 7      | GPIO        |

| GPIO Name |                                                            | Pin Alternate Functi                                                               | onality / Description                                                     |                                                      |

|-----------|------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|

|           | Analog                                                     | Timers                                                                             | Communication                                                             | Other                                                |

| PD5       | BUSADC0Y BUSADC0X<br>OPA2_OUT                              | WTIM0_CDTI1 #4<br>WTIM1_CC3 #1                                                     | US1_RTS #1 U0_CTS #5<br>LEU0_RX #0 I2C1_SCL<br>#3                         |                                                      |

| PD6       | BUSADC0Y BUSADC0X<br>ADC0_EXTP<br>VDAC0_EXT OPA1_P         | TIM1_CC0 #4<br>WTIM0_CDTI2 #4<br>WTIM1_CC0 #2 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US0_RTS #5 US1_RX #2<br>US2_CTS #5 US3_CTS<br>#2 U0_RTS #5 I2C0_SDA<br>#1 | CMU_CLK2 #2 LES_AL-<br>TEX0 PRS_CH5 #2<br>ACMP0_O #2 |

| PD7       | BUSADC0Y BUSADC0X<br>ADC0_EXTN OPA1_N                      | TIM1_CC1 #4<br>WTIM1_CC1 #2 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3                   | US1_TX #2 US3_CLK #1<br>U0_TX #6 I2C0_SCL #1                              | CMU_CLK0 #2 LES_AL-<br>TEX1 ACMP1_O #2               |

| PD8       | BU_VIN                                                     | WTIM1_CC2 #2                                                                       | US2_RTS #5                                                                | CMU_CLK1 #1                                          |

| PC6       | BUSACMP0Y BU-<br>SACMP0X OPA3_P<br>LCD_SEG32               | WTIM1_CC3 #2                                                                       | US0_RTS #2 US1_CTS<br>#3 I2C0_SDA #2                                      | LES_CH6                                              |

| PC7       | BUSACMP0Y BU-<br>SACMP0X OPA3_N<br>LCD_SEG33               | WTIM1_CC0 #3                                                                       | US0_CTS #2 US1_RTS<br>#3 I2C0_SCL #2                                      | LES_CH7                                              |

| PE4       | BUSDY BUSCX<br>LCD_COM0                                    | WTIM0_CC0 #0<br>WTIM1_CC1 #4                                                       | US0_CS #1 US1_CS #5<br>US3_CS #1 U0_RX #6<br>I2C0_SDA #7                  |                                                      |

| PE5       | BUSCY BUSDX<br>LCD_COM1                                    | WTIM0_CC1 #0<br>WTIM1_CC2 #4                                                       | US0_CLK #1 US1_CLK<br>#6 US3_CTS #1<br>I2C0_SCL #7                        |                                                      |

| PE6       | BUSDY BUSCX<br>LCD_COM2                                    | WTIM0_CC2 #0<br>WTIM1_CC3 #4                                                       | US0_RX #1 US3_TX #1                                                       | PRS_CH6 #2                                           |

| PE7       | BUSCY BUSDX<br>LCD_COM3                                    | WTIM1_CC0 #5                                                                       | US0_TX #1 US3_RX #1                                                       | PRS_CH7 #2                                           |

| PC8       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG34                         |                                                                                    | US0_CS #2                                                                 | LES_CH8 PRS_CH4 #0                                   |

| PC9       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG35                         |                                                                                    | US0_CLK #2                                                                | LES_CH9 PRS_CH5 #0<br>GPIO_EM4WU2                    |

| PC10      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_RX #2                                                                 | LES_CH10                                             |

| PC11      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_TX #2 I2C1_SDA #4                                                     | LES_CH11                                             |

| PC12      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0 BU-<br>SACMP1Y BUSACMP1X | TIM1_CC3 #0                                                                        | US0_RTS #3 US1_CTS<br>#4 US2_CTS #4 U0_RTS<br>#3                          | CMU_CLK0 #1<br>LES_CH12                              |

| PC13      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #1 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI0 #1<br>TIM1_CC0 #0 TIM1_CC2<br>#4 PCNT0_S0IN #0                          | US0_CTS #3 US1_RTS<br>#4 US2_RTS #4 U0_CTS<br>#3                          | LES_CH13                                             |

| PC14      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI1 #1<br>TIM1_CC1 #0 TIM1_CC3<br>#4 LETIM0_OUT0 #5<br>PCNT0_S1IN #0        | US0_CS #3 US1_CS #3<br>US2_RTS #3 US3_CS #2<br>U0_TX #3 LEU0_TX #5        | LES_CH14 PRS_CH0 #2                                  |

### Table 6.2. TQFP80 PCB Land Pattern Dimensions

| Dimension | Min      | Мах   |  |

|-----------|----------|-------|--|

| C1        | 13.30    | 13.40 |  |

| C2        | 13.30    | 13.40 |  |

| E         | 0.50 BSC |       |  |

| x         | 0.20     | 0.30  |  |

| Y         | 1.40     | 1.50  |  |

### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

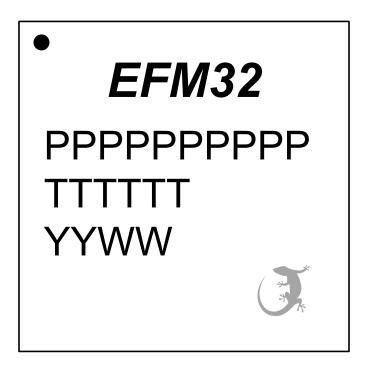

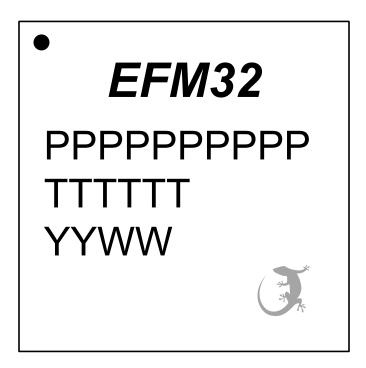

### 6.3 TQFP80 Package Marking

Figure 6.3. TQFP80 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

### Table 7.2. QFN80 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 8.90 |

| C2        | 8.90 |

| E         | 0.40 |

| X1        | 0.20 |

| Y1        | 0.85 |

| X2        | 7.30 |

| Y2        | 7.30 |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

6. The stencil thickness should be 0.125 mm (5 mils).

7. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

8. A 3x3 array of 1.45 mm square openings on a 2.00 mm pitch can be used for the center ground pad.

9. A No-Clean, Type-3 solder paste is recommended.

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### Table 8.2. TQFP64 PCB Land Pattern Dimensions

| Dimension | Min      | Мах   |  |

|-----------|----------|-------|--|

| C1        | 11.30    | 11.40 |  |

| C2        | 11.30    | 11.40 |  |

| E         | 0.50 BSC |       |  |

| x         | 0.20     | 0.30  |  |

| Y         | 1.40     | 1.50  |  |

### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 8.3 TQFP64 Package Marking

Figure 8.3. TQFP64 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

### **Simplicity Studio**

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

Support and Community community.silabs.com

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com