# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 37                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-TQFP                                                                   |

| Supplier Device Package    | 48-TQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b140f64gq48-ar |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Timers/Counters

- 2 × 16-bit Timer/Counter

- 3 or 4 Compare/Capture/PWM channels (4 + 4 on one timer instance)

- Dead-Time Insertion on one timer instance

- 2 × 32-bit Timer/Counter

- 32-bit Real Time Counter and Calendar (RTCC)

- 32-bit Ultra Low Energy CRYOTIMER for periodic wakeup from any Energy Mode

- 16-bit Low Energy Timer for waveform generation

- 16-bit Pulse Counter with asynchronous operation

- Watchdog Timer with dedicated RC oscillator

- Low Energy Sensor Interface (LESENSE)

- Autonomous sensor monitoring in Deep Sleep Mode

- Wide range of sensors supported, including LC sensors and capacitive buttons

- Up to 16 inputs

- Ultra efficient Power-on Reset and Brown-Out Detector

- Debug Interface

- 2-pin Serial Wire Debug interface

- 4-pin JTAG interface

- Micro Trace Buffer (MTB)

Pre-Programmed UART Bootloader

# Wide Operating Range

- 1.8 V to 3.8 V single power supply

- Integrated DC-DC, down to 1.8 V output with up to 200 mA load current for system

- Standard (-40  $^\circ C$  to 85  $^\circ C$   $T_A)$  and Extended (-40  $^\circ C$  to 125  $^\circ C$   $T_J)$  temperature grades available

- Packages

- QFN32 (5x5 mm)

- TQFP48 (7x7 mm)

- QFN64 (9x9 mm)

- TQFP64 (10x10 mm)

- QFN80 (9x9 mm)

- TQFP80 (12x12 mm)

# 3. System Overview

### 3.1 Introduction

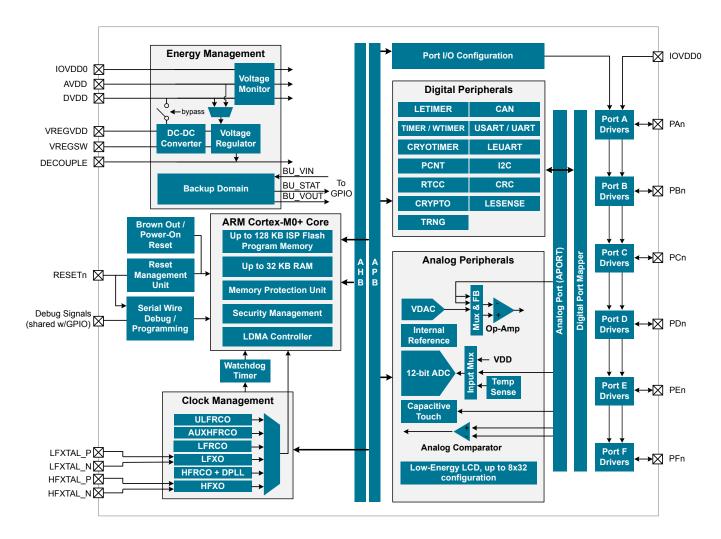

The Tiny Gecko Series 1 product family is well suited for any battery operated application as well as other systems requiring high performance and low energy consumption. This section gives a short introduction to the MCU system. The detailed functional description can be found in the Tiny Gecko Series 1 Reference Manual. Any behavior that does not conform to the specifications in this data sheet or the functional descriptions in the Tiny Gecko Series 1 Reference Manual are detailed in the EFM32TG11 Errata document.

A block diagram of the Tiny Gecko Series 1 family is shown in Figure 3.1 Detailed EFM32TG11 Block Diagram on page 10. The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Detailed EFM32TG11 Block Diagram

# 4.1.2.1 General Operating Conditions

| Parameter                                     | Symbol                 | Test Condition                                           | Min  | Тур | Мах                  | Unit |

|-----------------------------------------------|------------------------|----------------------------------------------------------|------|-----|----------------------|------|

| Operating ambient tempera-                    | T <sub>A</sub>         | -G temperature grade                                     | -40  | 25  | 85                   | °C   |

| ture range <sup>6</sup>                       |                        | -I temperature grade                                     | -40  | 25  | 125                  | °C   |

| AVDD supply voltage <sup>2</sup>              | V <sub>AVDD</sub>      |                                                          | 1.8  | 3.3 | 3.8                  | V    |

| VREGVDD operating supply                      | V <sub>VREGVDD</sub>   | DCDC in regulation                                       | 2.4  | 3.3 | 3.8                  | V    |

| voltage <sup>2 1</sup>                        |                        | DCDC in bypass, 50mA load                                | 1.8  | 3.3 | 3.8                  | V    |

|                                               |                        | DCDC not in use. DVDD external-<br>ly shorted to VREGVDD | 1.8  | 3.3 | 3.8                  | V    |

| VREGVDD current                               | I <sub>VREGVDD</sub>   | DCDC in bypass, T ≤ 85 °C                                | _    | _   | 200                  | mA   |

|                                               |                        | DCDC in bypass, T > 85 °C                                | _    | _   | 100                  | mA   |

| DVDD operating supply volt-<br>age            | V <sub>DVDD</sub>      |                                                          | 1.62 | _   | V <sub>VREGVDD</sub> | V    |

| IOVDD operating supply volt-<br>age           | VIOVDD                 | All IOVDD pins <sup>5</sup>                              | 1.62 | _   | V <sub>VREGVDD</sub> | V    |

| DECOUPLE output capaci-<br>tor <sup>3 4</sup> | C <sub>DECOUPLE</sub>  |                                                          | 0.75 | 1.0 | 2.75                 | μF   |

| HFCORECLK frequency                           | fcore                  | VSCALE2, MODE = WS1                                      | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE2, MODE = WS0                                      | _    | _   | 25                   | MHz  |

|                                               |                        | VSCALE0, MODE = WS1                                      | _    | _   | 20                   | MHz  |

|                                               |                        | VSCALE0, MODE = WS0                                      | _    | _   | 10                   | MHz  |

| HFCLK frequency                               | f <sub>HFCLK</sub>     | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFSRCCLK frequency                            | f <sub>HFSRCCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFBUSCLK frequency                            | f <sub>HFBUSCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  |      | _   | 20                   | MHz  |

| HFPERCLK frequency                            | f <sub>HFPERCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFPERBCLK frequency                           | f <sub>HFPERBCLK</sub> | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFPERCCLK frequency                           | fHFPERCCLK             | VSCALE2                                                  | _    | —   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

|                                               |                        |                                                          |      |     |                      |      |

# Table 4.2. General Operating Conditions

| Parameter                                                                              | Symbol               | Test Condition                                                                                          | Min | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption in<br>EM4H mode, with voltage                                      | I <sub>EM4H_VS</sub> | 128 byte RAM retention, RTCC running from LFXO                                                          | —   | 0.82 |     | μA   |

| scaling enabled                                                                        |                      | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO                                              | —   | 0.45 | _   | μA   |

|                                                                                        |                      | 128 byte RAM retention, no RTCC                                                                         | —   | 0.45 | TBD | μA   |

| Current consumption in EM4S mode                                                       | I <sub>EM4S</sub>    | No RAM retention, no RTCC                                                                               | —   | 0.07 | TBD | μA   |

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled | IPD1_VS              | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>1</sup> | _   | 0.18 | _   | μA   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled | IPD2_VS              | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>1</sup> | _   | 0.18 | _   | μA   |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.3 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

2. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

# 4.1.12 Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Мах | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | I <sub>VMON</sub>       | In EM0 or EM1, 1 supply monitored, T $\leq$ 85 °C                | _    | 6.3  | TBD | μA   |

|                                    |                         | In EM0 or EM1, 4 supplies monitored, T $\leq$ 85 °C              | —    | 12.5 | TBD | μA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshold       | —    | 62   |     | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | _    | 99   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold | —    | 99   | _   | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | —    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    | _   | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | _    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  |     | mV   |

|                                    |                         | Fine                                                             | _    | 20   | _   | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | _    | 460  | _   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  |      | 26   | _   | mV   |

# Table 4.19. Voltage Monitor (VMON)

| Parameter                                               | Symbol                   | Test Condition                                                                                         | Min | Тур  | Мах | Unit |

|---------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| ratio (1 kHz sine wave),                                | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal 1.25V reference                                                       | _   | 60.4 | _   | dB   |

| Noise band limited to 250<br>kHz                        |                          | 500 ksps, single-ended, internal<br>2.5V reference                                                     | —   | 61.6 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 64.0 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 63.3 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 64.4 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 65.8 |     | dB   |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference                                                       | _   | 65.3 |     | dB   |

| Noise band limited to 22 kHz                            |                          | 500 ksps, single-ended, internal<br>2.5V reference                                                     | _   | 66.7 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 68.5 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 67.8 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 69.0 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 70.0 |     | dB   |

| Total harmonic distortion                               | THD                      |                                                                                                        |     | 70.2 |     | dB   |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                                                                        | TBD | _    | TBD | LSB  |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                                                                        | TBD | _    | TBD | LSB  |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T = 25 °C                                                                                              | TBD | _    | TBD | mV   |

|                                                         |                          | Across operating temperature range                                                                     | TBD | _    | TBD | mV   |

| Gain error <sup>5</sup>                                 | V <sub>GAIN</sub>        | T = 25 °C, Low-noise internal ref-<br>erence (REFSEL = 1V25LN or<br>2V5LN)                             | TBD | _    | TBD | %    |

|                                                         |                          | Across operating temperature<br>range, Low-noise internal refer-<br>ence (REFSEL = 1V25LN or<br>2V5LN) | TBD | _    | TBD | %    |

| External load capactiance,<br>OUTSCALE=0                | C <sub>LOAD</sub>        |                                                                                                        | —   | _    | 75  | pF   |

| Parameter                                                               | Symbol         | Test Condition                                                                                     | Min | Тур  | Max | Unit   |

|-------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Supply current, continuous<br>conversions, WARMUP-<br>MODE=KEEPCSENWARM | ICSEN_ACTIVE   | SAR or Delta Modulation conver-<br>sions of 33 pF capacitor,<br>CS0CG=0 (Gain = 10x), always<br>on | _   | 90.5 | _   | μA     |

| HFPERCLK supply current                                                 | ICSEN_HFPERCLK | Current contribution from<br>HFPERCLK when clock to CSEN<br>block is enabled.                      | _   | 2.25 | _   | µA/MHz |

# Note:

Current is specified with a total external capacitance of 33 pF per channel. Average current is dependent on how long the module is actively sampling channels within the scan period, and scales with the number of samples acquired. Supply current for a specific application can be estimated by multiplying the current per sample by the total number of samples per period (total\_current = single\_sample\_current \* (number\_of\_channels \* accumulation)).

# 4.1.21.3 I2C Fast-mode Plus (Fm+)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min  | Тур | Мах  | Unit |

|--------------------------------------------------|---------------------|----------------|------|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0    | —   | 1000 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 0.5  | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.26 | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 50   | _   | _    | ns   |

| SDA hold time                                    | t <sub>HD_DAT</sub> |                | 100  | —   | —    | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.26 |     |      | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.26 |     | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.26 | —   | —    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 0.5  | _   | _    | μs   |

# Table 4.30. I2C Fast-mode Plus (Fm+)<sup>1</sup>

## Note:

1. For CLHR set to 0 or 1 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Fast-mode Plus, refer to the I2C chapter in the reference manual.

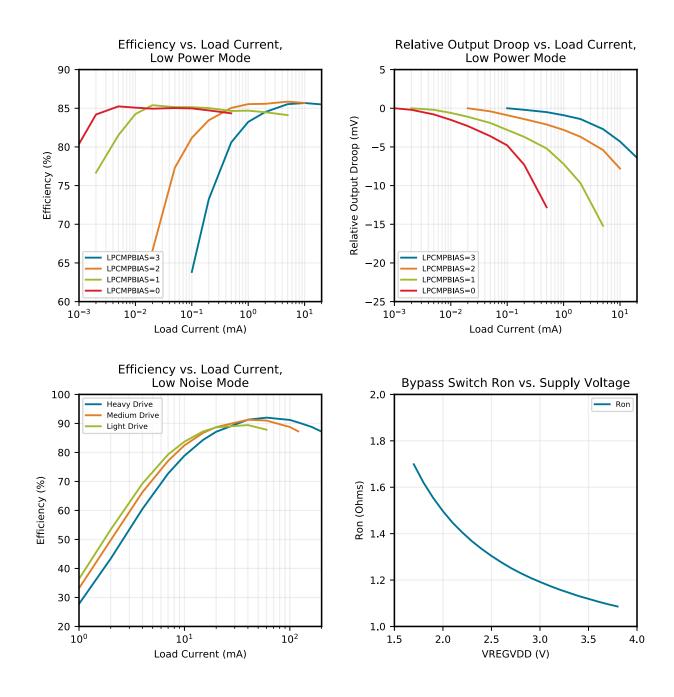

#### 4.2.2 DC-DC Converter

Default test conditions: CCM mode, LDCDC = 4.7 µH, CDCDC = 4.7 µF, VDCDC\_I = 3.3 V, VDCDC\_O = 1.8 V, FDCDC\_LN = 7 MHz

Figure 4.8. DC-DC Converter Typical Performance Characteristics

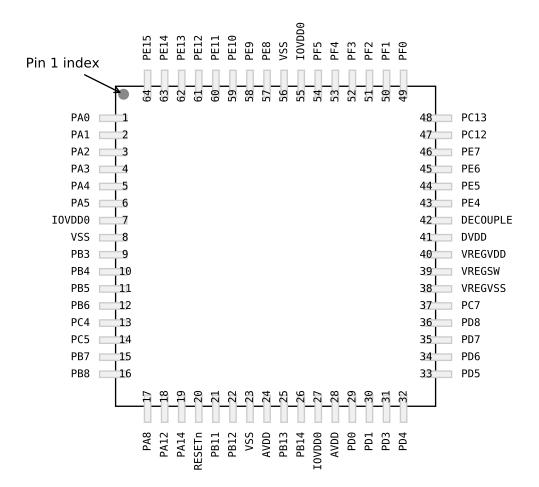

#### Figure 5.3. EFM32TG11B5xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.3. EFM32TG11B5xx in Q | FP64 Device Pinout |

|-------------------------------|--------------------|

|-------------------------------|--------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>27<br>55 | Digital IO power supply 0. | VSS      | 8<br>23<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

| Pin Name | Pin(s)   | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB4      | 10       | GPIO                          | PB5      | 11     | GPIO                                                                                                                                                                                                        |

| PB6      | 12       | GPIO                          | PC4      | 13     | GPIO                                                                                                                                                                                                        |

| PC5      | 14       | GPIO                          | PB7      | 15     | GPIO                                                                                                                                                                                                        |

| PB8      | 16       | GPIO                          | PA8      | 17     | GPIO                                                                                                                                                                                                        |

| PA12     | 18       | GPIO                          | PA13     | 19     | GPIO (5V)                                                                                                                                                                                                   |

| PA14     | 20       | GPIO                          | RESETn   | 21     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 22       | GPIO                          | PB12     | 23     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.          | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26       | GPIO                          | PD0      | 29     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 30       | GPIO                          | PD3      | 31     | GPIO                                                                                                                                                                                                        |

| PD4      | 32       | GPIO                          | PD5      | 33     | GPIO                                                                                                                                                                                                        |

| PD6      | 34       | GPIO                          | PD7      | 35     | GPIO                                                                                                                                                                                                        |

| PD8      | 36       | GPIO                          | PC7      | 37     | GPIO                                                                                                                                                                                                        |

| VREGSW   | 39       | DCDC regulator switching node | VREGVDD  | 40     | Voltage regulator VDD input                                                                                                                                                                                 |

| DVDD     | 41       | Digital power supply.         | DECOUPLE | 42     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PE4      | 43       | GPIO                          | PE5      | 44     | GPIO                                                                                                                                                                                                        |

| PE6      | 45       | GPIO                          | PE7      | 46     | GPIO                                                                                                                                                                                                        |

| PC12     | 47       | GPIO (5V)                     | PC13     | 48     | GPIO (5V)                                                                                                                                                                                                   |

| PF0      | 49       | GPIO (5V)                     | PF1      | 50     | GPIO (5V)                                                                                                                                                                                                   |

| PF2      | 51       | GPIO                          | PF3      | 52     | GPIO                                                                                                                                                                                                        |

| PF4      | 53       | GPIO                          | PF5      | 54     | GPIO                                                                                                                                                                                                        |

| PE8      | 56       | GPIO                          | PE9      | 57     | GPIO                                                                                                                                                                                                        |

| PE10     | 58       | GPIO                          | PE11     | 59     | GPIO                                                                                                                                                                                                        |

| PE12     | 60       | GPIO                          | PE13     | 61     | GPIO                                                                                                                                                                                                        |

| PE14     | 62       | GPIO                          | PE15     | 63     | GPIO                                                                                                                                                                                                        |

| PA15     | 64       | GPIO                          |          |        |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

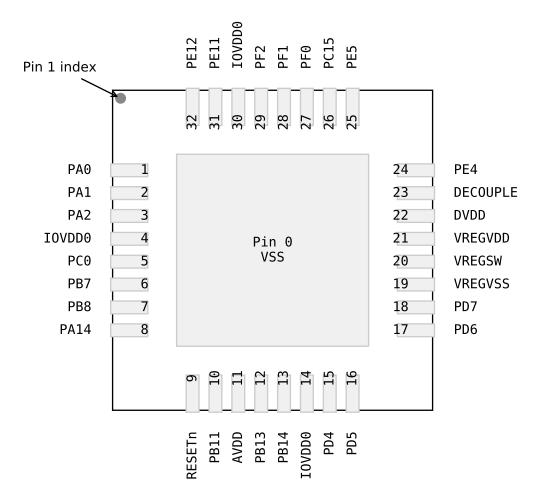

## Figure 5.12. EFM32TG11B5xx in QFN32 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.12. EFM32TG11B5xx in QFN32 Device Pinout |

|--------------------------------------------------|

|--------------------------------------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0<br>19       | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| IOVDD0   | 4<br>14<br>30 | Digital IO power supply 0. | PC0      | 5      | GPIO (5V)   |

| PB7      | 6             | GPIO                       | PB8      | 7      | GPIO        |

## 5.14 GPIO Functionality Table

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of each GPIO pin, followed by the functionality available on that pin. Refer to 5.15 Alternate Functionality Overview for a list of GPIO locations available for each function.

| GPIO Name | Pin Alternate Functionality / Description                  |                                              |                                                                                     |                                                            |  |  |  |  |  |

|-----------|------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

|           | Analog                                                     | Timers                                       | Communication                                                                       | Other                                                      |  |  |  |  |  |

| PA0       | BUSBY BUSAX<br>LCD_SEG13                                   | TIM0_CC0 #0 TIM0_CC1<br>#7 PCNT0_S0IN #4     | US1_RX #5 US3_TX #0<br>LEU0_RX #4 I2C0_SDA<br>#0                                    | CMU_CLK2 #0 PRS_CH0<br>#0 PRS_CH3 #3<br>GPIO_EM4WU0        |  |  |  |  |  |

| PA1       | BUSAY BUSBX<br>LCD_SEG14                                   | TIM0_CC0 #7 TIM0_CC1<br>#0 PCNT0_S1IN #4     | US3_RX #0 I2C0_SCL #0                                                               | CMU_CLK1 #0 PRS_CH1<br>#0                                  |  |  |  |  |  |

| PA2       | BUSBY BUSAX<br>LCD_SEG15                                   | TIM0_CC2 #0                                  | US1_RX #6 US3_CLK #0                                                                | CMU_CLK0 #0                                                |  |  |  |  |  |

| PA3       | BUSAY BUSBX<br>LCD_SEG16                                   | TIM0_CDTI0 #0                                | US3_CS #0 U0_TX #2                                                                  | CMU_CLK2 #1<br>CMU_CLK2 #4<br>CMU_CLKI0 #1 LES_AL-<br>TEX2 |  |  |  |  |  |

| PA4       | BUSBY BUSAX<br>LCD_SEG17                                   | TIM0_CDTI1 #0                                | US3_CTS #0 U0_RX #2                                                                 | LES_ALTEX3                                                 |  |  |  |  |  |

| PA5       | BUSAY BUSBX<br>LCD_SEG18                                   | TIM0_CDTI2 #0                                | US3_RTS #0 U0_CTS #2                                                                | LES_ALTEX4 ACMP1_O<br>#7                                   |  |  |  |  |  |

| PA6       | BUSBY BUSAX<br>LCD_SEG19                                   | WTIM0_CC0 #1                                 | U0_RTS #2                                                                           | PRS_CH6 #0 ACMP0_O<br>#4 GPIO_EM4WU1                       |  |  |  |  |  |

| PB3       | BUSAY BUSBX<br>LCD_SEG20 /<br>LCD_COM4                     | TIM1_CC3 #2<br>WTIM0_CC0 #6                  | US2_TX #1 US3_TX #2                                                                 | ACMP0_O #7                                                 |  |  |  |  |  |

| PB4       | BUSBY BUSAX<br>LCD_SEG21 /<br>LCD_COM5                     | WTIM0_CC1 #6                                 | US2_RX #1                                                                           |                                                            |  |  |  |  |  |

| PB5       | BUSAY BUSBX<br>LCD_SEG22 /<br>LCD_COM6                     | WTIM0_CC2 #6<br>PCNT0_S0IN #6                | US0_RTS #4 US2_CLK<br>#1                                                            |                                                            |  |  |  |  |  |

| PB6       | BUSBY BUSAX<br>LCD_SEG23 /<br>LCD_COM7                     | TIM0_CC0 #3<br>PCNT0_S1IN #6                 | US0_CTS #4 US2_CS #1                                                                |                                                            |  |  |  |  |  |

| PC0       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #0 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC1 #3<br>PCNT0_S0IN #2                 | CAN0_RX #0 US0_TX #5<br>US1_TX #0 US1_CS #4<br>US2_RTS #0 US3_CS #3<br>I2C0_SDA #4  | LES_CH0 PRS_CH2 #0                                         |  |  |  |  |  |

| PC1       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #1 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC2 #3<br>WTIM0_CC0 #7<br>PCNT0_S1IN #2 | CAN0_TX #0 US0_RX #5<br>US1_TX #4 US1_RX #0<br>US2_CTS #0 US3_RTS<br>#1 I2C0_SCL #4 | LES_CH1 PRS_CH3 #0                                         |  |  |  |  |  |

| PC2       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #2 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI0 #3<br>WTIM0_CC1 #7                | US1_RX #4 US2_TX #0                                                                 | LES_CH2                                                    |  |  |  |  |  |

| PC3       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #3 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI1 #3<br>WTIM0_CC2 #7                | US1_CLK #4 US2_RX #0                                                                | LES_CH3                                                    |  |  |  |  |  |

## Table 5.14. GPIO Functionality Table

| Alternate     | LOCA                                   | ATION                       |                                                  |  |  |  |  |  |  |  |

|---------------|----------------------------------------|-----------------------------|--------------------------------------------------|--|--|--|--|--|--|--|

| Functionality | 0 - 3                                  | 4 - 7                       | Description                                      |  |  |  |  |  |  |  |

| OPA3_N        | 0: PC7                                 |                             | Operational Amplifier 3 external negative input. |  |  |  |  |  |  |  |

| OPA3_OUT      | 0: PD1                                 |                             | Operational Amplifier 3 output.                  |  |  |  |  |  |  |  |

| OPA3_P        | 0: PC6                                 |                             | Operational Amplifier 3 external positive input. |  |  |  |  |  |  |  |

| PCNT0_S0IN    | 0: PC13<br>2: PC0<br>3: PD6            | 4: PA0<br>6: PB5<br>7: PB12 | Pulse Counter PCNT0 input number 0.              |  |  |  |  |  |  |  |

| PCNT0_S1IN    | 0: PC14<br>2: PC1<br>3: PD7            | 4: PA1<br>6: PB6<br>7: PB11 | Pulse Counter PCNT0 input number 1.              |  |  |  |  |  |  |  |

| PRS_CH0       | 0: PA0<br>1: PF3<br>2: PC14<br>3: PF2  |                             | Peripheral Reflex System PRS, channel 0.         |  |  |  |  |  |  |  |

| PRS_CH1       | 0: PA1<br>1: PF4<br>2: PC15<br>3: PE12 |                             | Peripheral Reflex System PRS, channel 1.         |  |  |  |  |  |  |  |

| PRS_CH2       | 0: PC0<br>1: PF5<br>2: PE10<br>3: PE13 |                             | Peripheral Reflex System PRS, channel 2.         |  |  |  |  |  |  |  |

| PRS_CH3       | 0: PC1<br>1: PE8<br>2: PE11<br>3: PA0  |                             | Peripheral Reflex System PRS, channel 3.         |  |  |  |  |  |  |  |

| PRS_CH4       | 0: PC8<br>2: PF1                       |                             | Peripheral Reflex System PRS, channel 4.         |  |  |  |  |  |  |  |

| PRS_CH5       | 0: PC9<br>2: PD6                       |                             | Peripheral Reflex System PRS, channel 5.         |  |  |  |  |  |  |  |

| PRS_CH6       | 0: PA6<br>1: PB14<br>2: PE6            |                             | Peripheral Reflex System PRS, channel 6.         |  |  |  |  |  |  |  |

| PRS_CH7       | 0: PB13<br>2: PE7                      |                             | Peripheral Reflex System PRS, channel 7.         |  |  |  |  |  |  |  |

| Alternate                      | LOCA                                     | ATION                       |                                                                    |

|--------------------------------|------------------------------------------|-----------------------------|--------------------------------------------------------------------|

| Functionality                  | 0 - 3                                    | 4 - 7                       | Description                                                        |

| VDAC0_OUT0 /<br>OPA0_OUT       | 0: PB11                                  |                             | Digital to Analog Converter DAC0 output channel number 0.          |

| VDAC0_OUT0ALT<br>/ OPA0_OUTALT | 0: PC0<br>1: PC1<br>2: PC2<br>3: PC3     | 4: PD0                      | Digital to Analog Converter DAC0 alternative output for channel 0. |

| VDAC0_OUT1 /<br>OPA1_OUT       | 0: PB12                                  |                             | Digital to Analog Converter DAC0 output channel number 1.          |

| VDAC0_OUT1ALT<br>/ OPA1_OUTALT | 0: PC12<br>1: PC13<br>2: PC14<br>3: PC15 | 4: PD1                      | Digital to Analog Converter DAC0 alternative output for channel 1. |

| WTIM0_CC0                      | 0: PE4<br>1: PA6                         | 4: PC15<br>6: PB3<br>7: PC1 | Wide timer 0 Capture Compare input / output channel 0.             |

| WTIM0_CC1                      | 0: PE5                                   | 4: PF0<br>6: PB4<br>7: PC2  | Wide timer 0 Capture Compare input / output channel 1.             |

| WTIM0_CC2                      | 0: PE6                                   | 4: PF1<br>6: PB5<br>7: PC3  | Wide timer 0 Capture Compare input / output channel 2.             |

| WTIM0_CDTI0                    | 0: PE10<br>2: PA12                       | 4: PD4                      | Wide timer 0 Complimentary Dead Time Insertion channel 0.          |

| WTIM0_CDTI1                    | 0: PE11<br>2: PA13                       | 4: PD5                      | Wide timer 0 Complimentary Dead Time Insertion channel 1.          |

| WTIM0_CDTI2                    | 0: PE12<br>2: PA14                       | 4: PD6                      | Wide timer 0 Complimentary Dead Time Insertion channel 2.          |

| WTIM1_CC0                      | 0: PB13<br>1: PD2<br>2: PD6<br>3: PC7    | 5: PE7                      | Wide timer 1 Capture Compare input / output channel 0.             |

| WTIM1_CC1                      | 0: PB14<br>1: PD3<br>2: PD7              | 4: PE4                      | Wide timer 1 Capture Compare input / output channel 1.             |

| WTIM1_CC2                      | 0: PD0<br>1: PD4<br>2: PD8               | 4: PE5                      | Wide timer 1 Capture Compare input / output channel 2.             |

| Port           | Bus             | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СН9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

|----------------|-----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| <b>APORT0X</b> | <b>BUSADC0X</b> |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PD7 | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 |

| <b>APORT0Y</b> | <b>BUSADC0Y</b> |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PD7 | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 |

| APORT1X        | BUSAX           |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT1Y        | BUSAY           |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2X        | BUSBX           |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY           |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3X        | BUSCX           |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| APORT3Y        | BUSCY           |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4X        | BUSDX           |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY           |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

# Table 5.18. ADC0 Bus and Pin Mapping

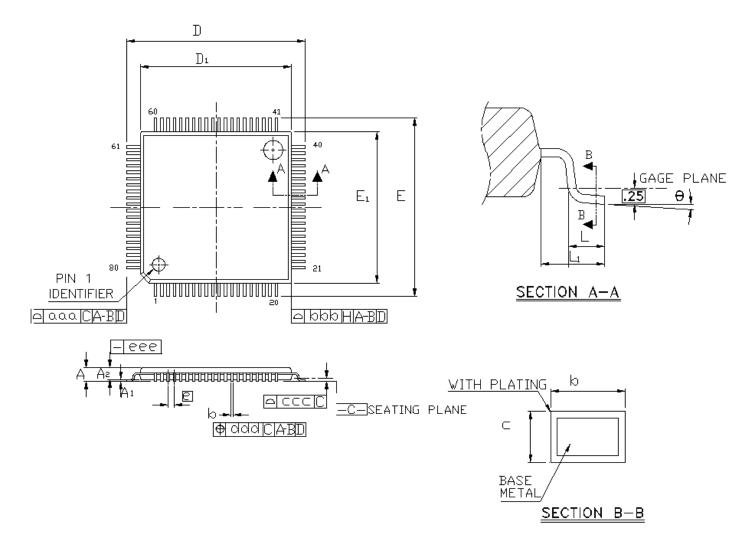

# 6. TQFP80 Package Specifications

## 6.1 TQFP80 Package Dimensions

Figure 6.1. TQFP80 Package Drawing

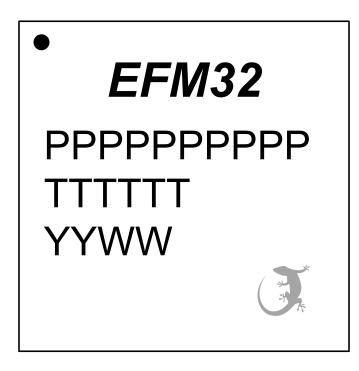

Figure 7.3. QFN80 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

#### Table 9.2. QFN64 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 8.90 |

| C2        | 8.90 |

| E         | 0.50 |

| X1        | 0.30 |

| Y1        | 0.85 |

| X2        | 7.30 |

| Y2        | 7.30 |

## Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

6. The stencil thickness should be 0.125 mm (5 mils).

7. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

8. A 3x3 array of 1.45 mm square openings on a 2.00 mm pitch can be used for the center ground pad.

9. A No-Clean, Type-3 solder paste is recommended.

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 12. Revision History

#### **Revision 0.5**

February, 2018

- 4.1 Electrical Characteristics updated with latest characterization data and production test limits.

- Added 4.1.3 Thermal Characteristics.

- Added 4.2 Typical Performance Curves section.

- Corrected OPA / VDAC output connections in Figure 5.14 APORT Connection Diagram on page 119.

#### **Revision 0.1**

May 1st, 2017

Initial release.