Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-WFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-QFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b140f64im32-ar |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

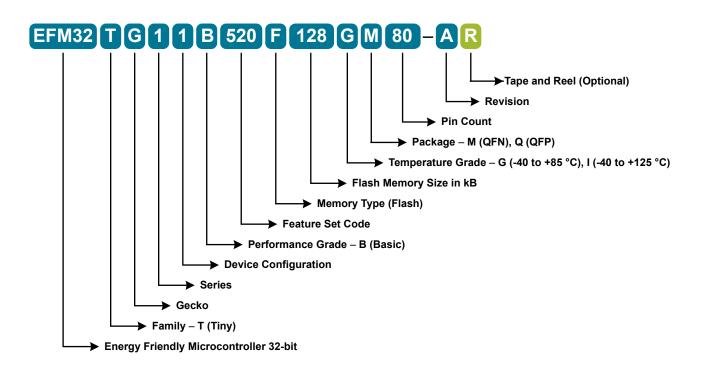

Figure 2.1. Ordering Code Key

#### 3.6.5 Controller Area Network (CAN)

The CAN peripheral provides support for communication at up to 1 Mbps over CAN protocol version 2.0 part A and B. It includes 32 message objects with independent identifier masks and retains message RAM in EM2. Automatic retransmittion may be disabled in order to support Time Triggered CAN applications.

#### 3.6.6 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality such as simple logic operations (AND, OR, NOT) can be applied by the PRS to the signals. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

### 3.6.7 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface LESENSE<sup>TM</sup> is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators, ADC, and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable finite state machine which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

#### 3.7 Security Features

#### 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)

The GPCRC module implements a Cyclic Redundancy Check (CRC) function. It supports both 32-bit and 16-bit polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3), while the 16-bit polynomial can be programmed to any value, depending on the needs of the application.

#### 3.7.2 Crypto Accelerator (CRYPTO)

The Crypto Accelerator is a fast and energy-efficient autonomous hardware encryption and decryption accelerator. Tiny Gecko Series 1 devices support AES encryption and decryption with 128- or 256-bit keys, ECC over both GF(P) and GF(2<sup>m</sup>), and SHA-1 and SHA-2 (SHA-224 and SHA-256).

Supported block cipher modes of operation for AES include: ECB, CTR, CBC, PCBC, CFB, OFB, GCM, CBC-MAC, GMAC and CCM.

Supported ECC NIST recommended curves include P-192, P-224, P-256, K-163, K-233, B-163 and B-233.

The CRYPTO module allows fast processing of GCM (AES), ECC and SHA with little CPU intervention. CRYPTO also provides trigger signals for DMA read and write operations.

#### 3.7.3 True Random Number Generator (TRNG)

The TRNG module is a non-deterministic random number generator based on a full hardware solution. The TRNG is validated with NIST800-22 and AIS-31 test suites as well as being suitable for FIPS 140-2 certification (for the purposes of cryptographic key generation).

#### 3.7.4 Security Management Unit (SMU)

The Security Management Unit (SMU) allows software to set up fine-grained security for peripheral access, which is not possible in the Memory Protection Unit (MPU). Peripherals may be secured by hardware on an individual basis, such that only priveleged accesses to the peripheral's register interface will be allowed. When an access fault occurs, the SMU reports the specific peripheral involved and can optionally generate an interrupt.

#### 3.8 Analog

| Parameter                      | Symbol                | Test Condition                                                        | Min                 | Тур              | Мах             | Unit      |

|--------------------------------|-----------------------|-----------------------------------------------------------------------|---------------------|------------------|-----------------|-----------|

| Note:                          |                       |                                                                       |                     |                  |                 |           |

|                                |                       | mode is calculated using $R_{BYP}$ _min+ILOAD * $R_{BYP}$ _max.       | from the DCDC spec  | cification table | e. Requiremer   | nts for   |

| 2. VREGVDD must be             | e tied to AVDD. Both  | VREGVDD and AVDD minimum                                              | voltages must be sa | atisfied for the | part to opera   | te.       |

|                                |                       | characteristic specs of the capa<br>oss temperature and DC bias.      | citor used on DECOU | JPLE to ensu     | re its capacita | ance val- |

|                                | will be dependent on  | transitions occur at a rate of 10 r<br>the value of the DECOUPLE ou   |                     |                  |                 |           |

| 5. When the CSEN pe            | ripheral is used with | chopping enabled (CSEN_CTRI                                           | CHOPEN = ENAB       | LE), IOVDD n     | nust be equal   | to AVDE   |

| cation. T <sub>A</sub> (max) = |                       | due to device self-heating, which<br>x PowerDissipation). Refer to th |                     | •                | -               |           |

# 4.1.3 Thermal Characteristics

| Parameter                  | Symbol                          | Test Condition                    | Min | Тур  | Мах | Unit |

|----------------------------|---------------------------------|-----------------------------------|-----|------|-----|------|

| Thermal resistance, QFN32  | THETA <sub>JA_QFN32</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 25.7 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 23.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 21.3 | _   | °C/W |

| Thermal resistance, TQFP48 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 44.1 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP48</sub>         | 4-Layer PCB, Air velocity = 1 m/s |     | 43.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s |     | 42.3 | _   | °C/W |

| Thermal resistance, QFN64  | THETA <sub>JA_QFN64</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP64 | THE-<br>TA <sub>JA_TQFP64</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 37.3 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 35.6 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 33.8 | _   | °C/W |

| Thermal resistance, QFN80  | THETA <sub>JA_QFN80</sub>       | 4-Layer PCB, Air velocity = 0 m/s |     | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP80 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 49.3 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP80</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 44.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 42.6 | _   | °C/W |

### Table 4.3. Thermal Characteristics

# 4.1.8 Brown Out Detector (BOD)

| Parameter              | Symbol                     | Test Condition               | Min | Тур | Max | Unit |

|------------------------|----------------------------|------------------------------|-----|-----|-----|------|

| DVDD BOD threshold     | V <sub>DVDDBOD</sub>       | DVDD rising                  | _   | _   | TBD | V    |

|                        |                            | DVDD falling (EM0/EM1)       | TBD | _   | _   | V    |

|                        |                            | DVDD falling (EM2/EM3)       | TBD | _   | —   | V    |

| DVDD BOD hysteresis    | V <sub>DVDDBOD_HYST</sub>  |                              | _   | 18  | _   | mV   |

| DVDD BOD response time | tDVDDBOD_DELAY             | Supply drops at 0.1V/µs rate | —   | 2.4 | _   | μs   |

| AVDD BOD threshold     | V <sub>AVDDBOD</sub>       | AVDD rising                  | _   |     | TBD | V    |

|                        |                            | AVDD falling (EM0/EM1)       | TBD | _   | _   | V    |

|                        |                            | AVDD falling (EM2/EM3)       | TBD | _   | _   | V    |

| AVDD BOD hysteresis    | VAVDDBOD_HYST              |                              | —   | 20  | _   | mV   |

| AVDD BOD response time | t <sub>AVDDBOD_DELAY</sub> | Supply drops at 0.1V/µs rate | —   | 2.4 |     | μs   |

| EM4 BOD threshold      | V <sub>EM4DBOD</sub>       | AVDD rising                  | —   | _   | TBD | V    |

|                        |                            | AVDD falling                 | TBD |     | _   | V    |

| EM4 BOD hysteresis     | V <sub>EM4BOD_HYST</sub>   |                              | _   | 25  | _   | mV   |

| EM4 BOD response time  | t <sub>EM4BOD_DELAY</sub>  | Supply drops at 0.1V/µs rate | —   | 300 |     | μs   |

## Table 4.10. Brown Out Detector (BOD)

# 4.1.11 General-Purpose I/O (GPIO)

| Parameter                                                                | Symbol                 | Test Condition                                        | Min       | Тур | Max       | Unit |

|--------------------------------------------------------------------------|------------------------|-------------------------------------------------------|-----------|-----|-----------|------|

| Input low voltage                                                        | V <sub>IL</sub>        | GPIO pins                                             | _         | _   | IOVDD*0.3 | V    |

| Input high voltage                                                       | V <sub>IH</sub>        | GPIO pins                                             | IOVDD*0.7 | —   | —         | V    |

| Output high voltage relative                                             | V <sub>OH</sub>        | Sourcing 3 mA, IOVDD $\ge$ 3 V,                       | IOVDD*0.8 | _   | _         | V    |

| to IOVDD                                                                 |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sourcing 1.2 mA, IOVDD $\ge$ 1.62 V,                  | IOVDD*0.6 | _   | -         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sourcing 20 mA, IOVDD $\ge$ 3 V,                      | IOVDD*0.8 | _   | _         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

|                                                                          |                        | Sourcing 8 mA, IOVDD ≥ 1.62 V,                        | IOVDD*0.6 | _   | _         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

| Output low voltage relative to                                           | V <sub>OL</sub>        | Sinking 3 mA, IOVDD ≥ 3 V,                            |           | _   | IOVDD*0.2 | V    |

| IOVDD                                                                    |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sinking 1.2 mA, IOVDD $\ge$ 1.62 V,                   | —         | —   | IOVDD*0.4 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sinking 20 mA, IOVDD $\ge$ 3 V,                       | —         | —   | IOVDD*0.2 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

|                                                                          |                        | Sinking 8 mA, IOVDD ≥ 1.62 V,                         | _         | _   | IOVDD*0.4 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

| Input leakage current                                                    | I <sub>IOLEAK</sub>    | All GPIO except LFXO pins, GPIO<br>≤ IOVDD, T ≤ 85 °C | —         | 0.1 | TBD       | nA   |

|                                                                          |                        | LFXO Pins, GPIO ≤ IOVDD, T ≤<br>85 °C                 | —         | 0.1 | TBD       | nA   |

|                                                                          |                        | All GPIO except LFXO pins, GPIO<br>≤ IOVDD, T > 85 °C | —         | —   | TBD       | nA   |

|                                                                          |                        | LFXO Pins, GPIO ≤ IOVDD, T ><br>85 °C                 | —         | —   | TBD       | nA   |

| Input leakage current on<br>5VTOL pads above IOVDD                       | I <sub>5VTOLLEAK</sub> | IOVDD < GPIO ≤ IOVDD + 2 V                            | _         | 3.3 | TBD       | μA   |

| I/O pin pull-up/pull-down re-<br>sistor                                  | R <sub>PUD</sub>       |                                                       | TBD       | 40  | TBD       | kΩ   |

| Pulse width of pulses re-<br>moved by the glitch suppres-<br>sion filter | t <sub>IOGLITCH</sub>  |                                                       | TBD       | 25  | TBD       | ns   |

## Table 4.18. General-Purpose I/O (GPIO)

### 4.1.13 Analog to Digital Converter (ADC)

Specified at 1 Msps, ADCCLK = 16 MHz, BIASPROG = 0, GPBIASACC = 0, unless otherwise indicated.

## Table 4.20. Analog to Digital Converter (ADC)

| Parameter                                                                                                                        | Symbol                             | Test Condition                                                           | Min                 | Тур | Мах                | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|---------------------|-----|--------------------|------|

| Resolution                                                                                                                       | VRESOLUTION                        |                                                                          | 6                   | —   | 12                 | Bits |

| Input voltage range <sup>5</sup>                                                                                                 | V <sub>ADCIN</sub>                 | Single ended                                                             | _                   | —   | V <sub>FS</sub>    | V    |

|                                                                                                                                  |                                    | Differential                                                             | -V <sub>FS</sub> /2 | _   | V <sub>FS</sub> /2 | V    |

| Input range of external refer-<br>ence voltage, single ended<br>and differential                                                 | V <sub>ADCREFIN_P</sub>            |                                                                          | 1                   | _   | V <sub>AVDD</sub>  | V    |

| Power supply rejection <sup>2</sup>                                                                                              | PSRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | —                  | dB   |

| Analog input common mode rejection ratio                                                                                         | CMRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | -                  | dB   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                 | I <sub>ADC_CONTI-</sub><br>NOUS_LP | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>    | _                   | 270 | TBD                | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                                                             |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 1 <sup>3</sup>   | _                   | 125 | -                  | μA   |

|                                                                                                                                  |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 1 <sup>3</sup> | _                   | 80  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.<br>Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL | I <sub>ADC_NORMAL_LP</sub>         | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 45  | -                  | μA   |

|                                                                                                                                  |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>     | _                   | 8   | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                 | IADC_STAND-<br>BY_LP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>  | _                   | 105 | -                  | μA   |

| Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC                                    |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 70  | _                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                 | I <sub>ADC_CONTI-</sub><br>NOUS_HP | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>    | _                   | 325 | -                  | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                                                             |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 0 <sup>3</sup>   | _                   | 175 | -                  | μA   |

|                                                                                                                                  |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 0 <sup>3</sup> | _                   | 125 | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                 | IADC_NORMAL_HP                     | 35 ksps / 16 MHz ADCCLK, BIA-SPROG = 0, GPBIASACC = 0 $^3$               | _                   | 85  | -                  | μA   |

| Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL                                                                     |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>     | _                   | 16  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                 | IADC_STAND-<br>BY_HP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>  | —                   | 160 | -                  | μA   |

| Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC                                    |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>   | _                   | 125 | -                  | μA   |

| Current from HFPERCLK                                                                                                            | IADC_CLK                           | HFPERCLK = 16 MHz                                                        | _                   | 166 | _                  | μΑ   |

| Parameter | Symbol                              | Test Condition                                              | Min | Тур | Max | Unit   |

|-----------|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|--------|

|           | the sum of the<br>e.<br>Gregisters. | etting in ACMPn_CTRL_PWRS<br>ne contributions from the ACMP | -   |     |     | ACMP + |

### 4.1.16 Capacitive Sense (CSEN)

| Parameter                                                                           | Symbol                                                                                                                                    | Test Condition                                                                                                                                                   | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Single conversion time (1x                                                          | t <sub>CNV</sub>                                                                                                                          | 12-bit SAR Conversions                                                                                                                                           | _   | 20.2 | —   | μs   |

| accumulation)                                                                       |                                                                                                                                           | 16-bit SAR Conversions                                                                                                                                           | _   | 26.4 | _   | μs   |

|                                                                                     |                                                                                                                                           | Delta Modulation Conversion (sin-<br>gle comparison)                                                                                                             | _   | 1.55 | _   | μs   |

| Maximum external capacitive load                                                    | C <sub>EXTMAX</sub>                                                                                                                       | CS0CG=7 (Gain = 1x), including routing parasitics                                                                                                                | _   | 68   |     | pF   |

|                                                                                     |                                                                                                                                           | CS0CG=0 (Gain = 10x), including routing parasitics                                                                                                               | —   | 680  | _   | pF   |

| Maximum external series impedance                                                   | R <sub>EXTMAX</sub>                                                                                                                       |                                                                                                                                                                  | —   | 1    | _   | kΩ   |

| Supply current, EM2 bonded<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-<br>MUPCNT=0 | ICSEN_BOND                                                                                                                                | 12-bit SAR conversions, 20 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                       | _   | 326  | _   | nA   |

|                                                                                     | ms conversion rate,<br>(Gain = 1x), 10 char<br>(total capacitance o<br>12-bit SAR conversi<br>conversion rate, CS<br>= 1x), 10 channels b | Delta Modulation conversions, 20<br>ms conversion rate, CS0CG=7<br>(Gain = 1x), 10 channels bonded<br>(total capacitance of 330 pF) <sup>1</sup>                 | _   | 226  | _   | nA   |

|                                                                                     |                                                                                                                                           | 12-bit SAR conversions, 200 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                      | _   | 33   | _   | nA   |

|                                                                                     |                                                                                                                                           | Delta Modulation conversions,<br>200 ms conversion rate,<br>CS0CG=7 (Gain = 1x), 10 chan-<br>nels bonded (total capacitance of<br>330 pF) <sup>1</sup>           | _   | 25   | _   | nA   |

| Supply current, EM2 scan<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-               | I <sub>CSEN_EM2</sub>                                                                                                                     | 12-bit SAR conversions, 20 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                             | —   | 690  | _   | nA   |

| MUPCNT=0                                                                            |                                                                                                                                           | Delta Modulation conversions, 20<br>ms scan rate, 8 comparisons per<br>sample (DMCR = 1, DMR = 2),<br>CS0CG=0 (Gain = 10x), 8 sam-<br>ples per scan <sup>1</sup> | _   | 515  | _   | nA   |

|                                                                                     |                                                                                                                                           | 12-bit SAR conversions, 200 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                            | _   | 79   | _   | nA   |

|                                                                                     |                                                                                                                                           | Delta Modulation conversions,<br>200 ms scan rate, 8 comparisons<br>per sample (DMCR = 1, DMR =<br>2), CS0CG=0 (Gain = 10x), 8<br>samples per scan <sup>1</sup>  | _   | 57   |     | nA   |

## Table 4.23. Capacitive Sense (CSEN)

| Parameter                                    | Symbol             | Test Condition                                                                               | Min | Тур   | Мах | Unit |

|----------------------------------------------|--------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Slew rate <sup>5</sup>                       | SR                 | DRIVESTRENGTH = 3,<br>INCBW=1 <sup>3</sup>                                                   | _   | 4.7   | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 3,<br>INCBW=0                                                                | _   | 1.5   | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=1 <sup>3</sup>                                                   | _   | 1.27  | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=0                                                                | _   | 0.42  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.17  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=0                                                                | —   | 0.058 | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.044 | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=0                                                                | _   | 0.015 | _   | V/µs |

| Startup time <sup>6</sup>                    | T <sub>START</sub> | DRIVESTRENGTH = 2                                                                            | _   | _     | TBD | μs   |

| Input offset voltage                         | V <sub>OSI</sub>   | DRIVESTRENGTH = 2 or 3, T =<br>25 °C                                                         | TBD | _     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0, T = 25 °C                                                            | TBD | —     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 2 or 3,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

| DC power supply rejection ratio <sup>9</sup> | PSRR <sub>DC</sub> | Input referred                                                                               | —   | 70    | _   | dB   |

| DC common-mode rejection ratio <sup>9</sup>  | CMRR <sub>DC</sub> | Input referred                                                                               | _   | 70    | _   | dB   |

| Total harmonic distortion                    | THD <sub>OPA</sub> | DRIVESTRENGTH = 2, 3x Gain<br>connection, 1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V   | _   | 90    | _   | dB   |

|                                              |                    | DRIVESTRENGTH = 0, 3x Gain<br>connection, 0.1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V | _   | 90    | _   | dB   |

| 3.                         | uration is: INCBW = 1, HCMDIS = 1, F                                                                                                                           | RESINSEL = V                                                                                                                                                                                                                                                                                                                                                                                                                 | √SS, V <sub>INPUT</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | = 0.5 V, V <sub>OUTI</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.                         | uration is: INCBW = 1, HCMDIS = 1, F                                                                                                                           | RESINSEL = \                                                                                                                                                                                                                                                                                                                                                                                                                 | VSS, V <sub>INPUT</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | = 0.5 V, V <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| xceeded, an isc            |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PUI - 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            | plation resistor is required for stability.                                                                                                                    | See AN0038                                                                                                                                                                                                                                                                                                                                                                                                                   | for more infor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | dwidth is increased. This is allowed or                                                                                                                        | nly when the n                                                                                                                                                                                                                                                                                                                                                                                                               | on-inverting c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | lose-loop gair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | n is ≥ 3,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| network. The ir            | nternal resistor feedback network has                                                                                                                          | total resistance                                                                                                                                                                                                                                                                                                                                                                                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <sub>PA</sub> -0.2V, 10%-9 | 90% rising/falling range.                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ed. In sample-a            | and-off mode, RC network after OPAM                                                                                                                            | IP will contrib                                                                                                                                                                                                                                                                                                                                                                                                              | ute extra dela                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | y. Settling err                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | or < 1m\                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| •                          | •                                                                                                                                                              | x Gain connec                                                                                                                                                                                                                                                                                                                                                                                                                | tion, UGF is t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | he gain-band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Unit gain buffer           | configuration is: INCBW = 0, HCMDI                                                                                                                             | S = 0, RESIN                                                                                                                                                                                                                                                                                                                                                                                                                 | SEL = DISABI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LE. V <sub>INPUT</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.5 V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                            |                                                                                                                                                                | 4V to V <sub>OPA</sub> -1∖                                                                                                                                                                                                                                                                                                                                                                                                   | /, input offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | will change. F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 'SRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | network. The in<br>en the OPAMP<br><sub>OPA</sub> -0.2V, 10%-9<br>led. In sample-a<br>GF is the gain-b<br>1/3 attenuation<br>Unit gain buffer<br>ut common mod | or is excluded. When the OPAMP is connected with a<br>network. The internal resistor feedback network has<br>en the OPAMP drives 1.5 V between output and grou<br>opA-0.2V, 10%-90% rising/falling range.<br>led. In sample-and-off mode, RC network after OPAM<br>GF is the gain-bandwidth product of the OPAMP. In 32<br>I 1/3 attenuation of the feedback network.<br>Unit gain buffer configuration is: INCBW = 0, HCMDI | or is excluded. When the OPAMP is connected with closed-loop ga<br>network. The internal resistor feedback network has total resistant<br>en the OPAMP drives 1.5 V between output and ground.<br><sub>OPA</sub> -0.2V, 10%-90% rising/falling range.<br>led. In sample-and-off mode, RC network after OPAMP will contribu-<br>SF is the gain-bandwidth product of the OPAMP. In 3x Gain connect<br>1/3 attenuation of the feedback network.<br>Unit gain buffer configuration is: INCBW = 0, HCMDIS = 0, RESIN<br>ut common mode transitions the region from V <sub>OPA</sub> -1.4V to V <sub>OPA</sub> -1. | or is excluded. When the OPAMP is connected with closed-loop gain > 1, there were network. The internal resistor feedback network has total resistance of 143.5 kC en the OPAMP drives 1.5 V between output and ground.<br><sub>OPA</sub> -0.2V, 10%-90% rising/falling range.<br>led. In sample-and-off mode, RC network after OPAMP will contribute extra dela<br>GF is the gain-bandwidth product of the OPAMP. In 3x Gain connection, UGF is the 1/3 attenuation of the feedback network.<br>Unit gain buffer configuration is: INCBW = 0, HCMDIS = 0, RESINSEL = DISAB<br>ut common mode transitions the region from V <sub>OPA</sub> -1.4V to V <sub>OPA</sub> -1V, input offset | or is excluded. When the OPAMP is connected with closed-loop gain > 1, there will be extra c<br>network. The internal resistor feedback network has total resistance of 143.5 kOhm, which wi<br>en the OPAMP drives 1.5 V between output and ground.<br><sub>OPA</sub> -0.2V, 10%-90% rising/falling range.<br>led. In sample-and-off mode, RC network after OPAMP will contribute extra delay. Settling err<br>GF is the gain-bandwidth product of the OPAMP. In 3x Gain connection, UGF is the gain-band<br>1/3 attenuation of the feedback network.<br>Unit gain buffer configuration is: INCBW = 0, HCMDIS = 0, RESINSEL = DISABLE. V <sub>INPUT</sub> =<br>ut common mode transitions the region from V <sub>OPA</sub> -1.4V to V <sub>OPA</sub> -1V, input offset will change. F |

### Table 4.25. LCD Driver

| Parameter                                        | Symbol                   | Test Condition                                 | Min | Тур  | Мах                                           | Unit |

|--------------------------------------------------|--------------------------|------------------------------------------------|-----|------|-----------------------------------------------|------|

| Frame rate                                       | f <sub>LCDFR</sub>       |                                                | TBD | —    | TBD                                           | Hz   |

| LCD supply range <sup>2</sup>                    | V <sub>LCDIN</sub>       |                                                | 1.8 | _    | 3.8                                           | V    |

| LCD output voltage range VL                      | V <sub>LCD</sub>         | Current source mode, No external LCD capacitor | 2.0 | _    | V <sub>LCDIN</sub> -0.4                       | V    |

|                                                  |                          | Step-down mode with external LCD capacitor     | 2.0 |      | V <sub>LCDIN</sub>                            | V    |

|                                                  |                          | Charge pump mode with external LCD capacitor   | 2.0 | _    | Min of 3.8<br>and 1.9 *<br>V <sub>LCDIN</sub> | V    |

| Contrast control step size                       | STEP <sub>CONTRAST</sub> | Current source mode                            | _   | 64   | _                                             | mV   |

|                                                  |                          | Charge pump or Step-down mode                  | _   | 43   | —                                             | mV   |

| Contrast control step accura-<br>cy <sup>1</sup> | ACC <sub>CONTRAST</sub>  |                                                | —   | +/-4 | —                                             | %    |

### Note:

1. Step size accuracy is measured relative to the typical step size, and typ value represents one standard deviation.

2.  $V_{LCDIN}$  is selectable between the AVDD or DVDD supply pins, depending on EMU\_PWRCTRL\_ANASW.

# 4.1.22 USART SPI

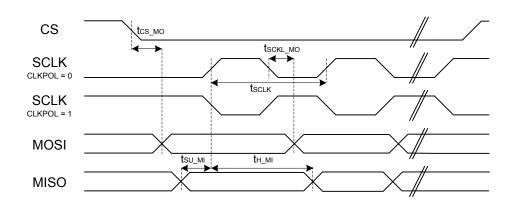

# **SPI Master Timing**

# Table 4.31. SPI Master Timing

| Parameter                      | Symbol               | Test Condition | Min                          | Тур | Мах  | Unit |

|--------------------------------|----------------------|----------------|------------------------------|-----|------|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>    |                | 2 *<br><sup>t</sup> HFPERCLK | —   | _    | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub>   |                | -19.8                        | _   | 18.9 | ns   |

| SCLK to MOSI <sup>1 3</sup>    | t <sub>SCLK_MO</sub> |                | -10                          | _   | 14.5 | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>su_мi</sub>   | IOVDD = 1.62 V | 75                           | _   | _    | ns   |

|                                |                      | IOVDD = 3.0 V  | 40                           | —   | _    | ns   |

| MISO hold time <sup>1 3</sup>  | t <sub>H_MI</sub>    |                | -10                          | _   | _    | ns   |

## Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

2. t<sub>HFPERCLK</sub> is one period of the selected HFPERCLK.

3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $V_{\text{DD}}$ ).

Figure 4.1. SPI Master Timing Diagram

| Pin Name | Pin(s)              | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|---------------------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | 9<br>24<br>51<br>70 | Ground                        | PB3      | 10     | GPIO                                                                                                                                                                                                        |

| PB4      | 11                  | GPIO                          | PB5      | 12     | GPIO                                                                                                                                                                                                        |

| PB6      | 13                  | GPIO                          | PC1      | 14     | GPIO (5V)                                                                                                                                                                                                   |

| PC2      | 15                  | GPIO (5V)                     | PC3      | 16     | GPIO (5V)                                                                                                                                                                                                   |

| PC4      | 17                  | GPIO                          | PC5      | 18     | GPIO                                                                                                                                                                                                        |

| PB7      | 19                  | GPIO                          | PB8      | 20     | GPIO                                                                                                                                                                                                        |

| PA8      | 21                  | GPIO                          | PA9      | 22     | GPIO                                                                                                                                                                                                        |

| PA10     | 23                  | GPIO                          | PA12     | 25     | GPIO                                                                                                                                                                                                        |

| PA14     | 26                  | GPIO                          | RESETn   | 27     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 28                  | GPIO                          | PB12     | 29     | GPIO                                                                                                                                                                                                        |

| AVDD     | 30<br>34            | Analog power supply.          | PB13     | 31     | GPIO                                                                                                                                                                                                        |

| PB14     | 32                  | GPIO                          | PD0      | 35     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 36                  | GPIO                          | PD3      | 37     | GPIO                                                                                                                                                                                                        |