#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Discontinued at Digi-Key                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                              |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-TQFP                                                                  |

| Supplier Device Package    | 48-TQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b140f64iq48-a |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 5.9 EFM32TG11B5xx in QFP48 Device Pinout  | 90 |

|-----|-------------------------------------------|----|

|     | 5.10 EFM32TG11B3xx in QFP48 Device Pinout | 92 |

|     | 5.11 EFM32TG11B1xx in QFP48 Device Pinout | 94 |

|     | 5.12 EFM32TG11B5xx in QFN32 Device Pinout | 96 |

|     | 5.13 EFM32TG11B1xx in QFN32 Device Pinout | 98 |

|     | 5.14 GPIO Functionality Table             | 00 |

|     | 5.15 Alternate Functionality Overview     | 04 |

|     | 5.16 Analog Port (APORT) Client Maps      | 19 |

| 6.  | TQFP80 Package Specifications             | 29 |

|     | 6.1 TQFP80 Package Dimensions             | 29 |

|     | 6.2 TQFP80 PCB Land Pattern               | 31 |

|     | 6.3 TQFP80 Package Marking                | 32 |

| 7.  | QFN80 Package Specifications.             | 33 |

|     | 7.1 QFN80 Package Dimensions              | 33 |

|     | 7.2 QFN80 PCB Land Pattern                | 35 |

|     | 7.3 QFN80 Package Marking                 | 37 |

| 8.  | TQFP64 Package Specifications             | 38 |

|     | 8.1 TQFP64 Package Dimensions             | 38 |

|     | 8.2 TQFP64 PCB Land Pattern               | 40 |

|     | 8.3 TQFP64 Package Marking                | 41 |

| 9.  | QFN64 Package Specifications.             | 42 |

|     | 9.1 QFN64 Package Dimensions              | 42 |

|     | 9.2 QFN64 PCB Land Pattern                | 44 |

|     | 9.3 QFN64 Package Marking                 | 46 |

| 10. | TQFP48 Package Specifications             | 47 |

|     | 10.1 TQFP48 Package Dimensions            | 47 |

|     | 10.2 TQFP48 PCB Land Pattern              | 49 |

|     | 10.3 TQFP48 Package Marking               | 50 |

| 11. | QFN32 Package Specifications              | 51 |

|     | 11.1 QFN32 Package Dimensions             | 51 |

|     | 11.2 QFN32 PCB Land Pattern               | 53 |

|     | 11.3 QFN32 Package Marking                | 55 |

| 12. | Revision History.                         | 56 |

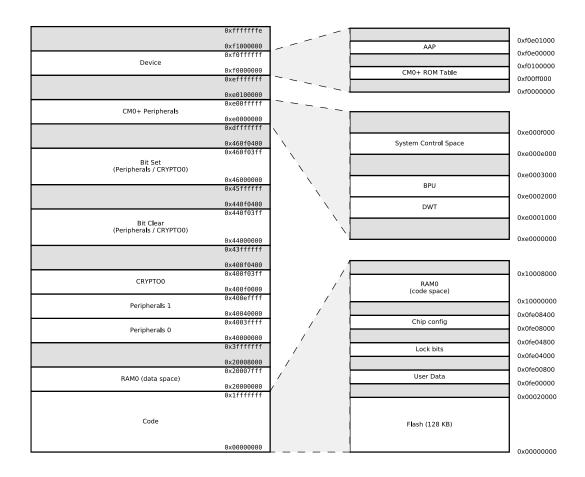

### 3.11 Memory Map

The EFM32TG11 memory map is shown in the figures below. RAM and flash sizes are for the largest memory configuration.

Figure 3.2. EFM32TG11 Memory Map — Core Peripherals and Code Space

| Parameter                      | Symbol                | Test Condition                                                        | Min                 | Тур              | Мах             | Unit      |

|--------------------------------|-----------------------|-----------------------------------------------------------------------|---------------------|------------------|-----------------|-----------|

| Note:                          |                       |                                                                       |                     |                  |                 |           |

|                                |                       | mode is calculated using $R_{BYP}$ _min+ILOAD * $R_{BYP}$ _max.       | from the DCDC spec  | cification table | e. Requiremer   | nts for   |

| 2. VREGVDD must be             | e tied to AVDD. Both  | VREGVDD and AVDD minimum                                              | voltages must be sa | atisfied for the | part to opera   | te.       |

|                                |                       | characteristic specs of the capa oss temperature and DC bias.         | citor used on DECOU | JPLE to ensu     | re its capacita | ance val- |

|                                | will be dependent on  | transitions occur at a rate of 10 r<br>the value of the DECOUPLE ou   |                     |                  |                 |           |

| 5. When the CSEN pe            | ripheral is used with | chopping enabled (CSEN_CTRI                                           | CHOPEN = ENAB       | LE), IOVDD n     | nust be equal   | to AVDE   |

| cation. T <sub>A</sub> (max) = |                       | due to device self-heating, which<br>x PowerDissipation). Refer to th |                     | •                | -               |           |

## 4.1.3 Thermal Characteristics

| Parameter                  | Symbol                          | Test Condition                    | Min | Тур  | Мах | Unit |

|----------------------------|---------------------------------|-----------------------------------|-----|------|-----|------|

| Thermal resistance, QFN32  | THETA <sub>JA_QFN32</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 25.7 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 23.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 21.3 | _   | °C/W |

| Thermal resistance, TQFP48 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 44.1 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP48</sub>         | 4-Layer PCB, Air velocity = 1 m/s |     | 43.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s |     | 42.3 | _   | °C/W |

| Thermal resistance, QFN64  | THETA <sub>JA_QFN64</sub>       | 4-Layer PCB, Air velocity = 0 m/s | _   | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP64 | THE-<br>TA <sub>JA_TQFP64</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 37.3 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 35.6 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 33.8 | _   | °C/W |

| Thermal resistance, QFN80  | THETA <sub>JA_QFN80</sub>       | 4-Layer PCB, Air velocity = 0 m/s |     | 20.9 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 18.2 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 16.4 | _   | °C/W |

| Thermal resistance, TQFP80 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 49.3 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP80</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 44.5 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 42.6 | _   | °C/W |

## Table 4.3. Thermal Characteristics

| Parameter                                   | Symbol                 | Test Condition                                             | Min | Тур      | Мах | Unit |

|---------------------------------------------|------------------------|------------------------------------------------------------|-----|----------|-----|------|

| Hysteresis (V <sub>CM</sub> = 1.25 V,       | V <sub>ACMPHYST</sub>  | HYSTSEL <sup>5</sup> = HYST0                               | TBD | 0        | TBD | mV   |

| $BIASPROG^4 = 0x10, FULL-$<br>$BIAS^4 = 1)$ |                        | HYSTSEL <sup>5</sup> = HYST1                               | TBD | 18       | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST2                               | TBD | 33       | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST3                               | TBD | 46       | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST4                               | TBD | 57       | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST5                               | TBD | 68       | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST6                               | TBD | 79       | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST7                               | TBD | 90       | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST8                               | TBD | 0        | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST9                               | TBD | -18      | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST10                              | TBD | -33      | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST11                              | TBD | -45      | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST12                              | TBD | -57      | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST13                              | TBD | -67      | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST14                              | TBD | -78      | TBD | mV   |

|                                             |                        | HYSTSEL <sup>5</sup> = HYST15                              | TBD | -88      | TBD | mV   |

| Comparator delay <sup>3</sup>               | t <sub>ACMPDELAY</sub> | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                        | _   | 30       | _   | μs   |

|                                             |                        | $BIASPROG^4 = 0x10, FULLBIAS^4 = 0$                        | _   | 3.7      | _   | μs   |

|                                             |                        | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1 |     | 360      | _   | ns   |

|                                             |                        | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1 | _   | 35       | _   | ns   |

| Offset voltage                              | VACMPOFFSET            | BIASPROG <sup>4</sup> =0x10, FULLBIAS <sup>4</sup><br>= 1  | TBD | _        | TBD | mV   |

| Reference voltage                           | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | TBD | 1.25     | TBD | V    |

|                                             |                        | Internal 2.5 V reference                                   | TBD | 2.5      | TBD | V    |

| Capacitive sense internal re-<br>sistance   | R <sub>CSRES</sub>     | CSRESSEL <sup>6</sup> = 0                                  | —   | infinite | _   | kΩ   |

|                                             |                        | CSRESSEL <sup>6</sup> = 1                                  | —   | 15       | _   | kΩ   |

|                                             |                        | CSRESSEL <sup>6</sup> = 2                                  |     | 27       | _   | kΩ   |

|                                             |                        | CSRESSEL <sup>6</sup> = 3                                  | —   | 39       |     | kΩ   |

|                                             |                        | CSRESSEL <sup>6</sup> = 4                                  |     | 51       |     | kΩ   |

|                                             |                        | CSRESSEL <sup>6</sup> = 5                                  | _   | 100      | _   | kΩ   |

|                                             |                        | CSRESSEL <sup>6</sup> = 6                                  |     | 162      | _   | kΩ   |

|                                             |                        | CSRESSEL <sup>6</sup> = 7                                  |     | 235      | _   | kΩ   |

| Parameter                   | Symbol                                         | Test Condition                                                                   | Min               | Тур             | Мах             | Unit      |

|-----------------------------|------------------------------------------------|----------------------------------------------------------------------------------|-------------------|-----------------|-----------------|-----------|

| Note:                       | l                                              |                                                                                  |                   |                 |                 |           |

| 1. Supply current the load. | specifications are for VD                      | AC circuitry operating with static outpo                                         | ut only and do n  | not include cur | rent required   | to drive  |

|                             | ode, the output is define<br>ngle-ended range. | d as the difference between two single                                           | e-ended outputs   | s. Absolute vol | ltage on each   | output is |

| 3. Entire range is          | monotonic and has no m                         | nissing codes.                                                                   |                   |                 |                 |           |

|                             | PERCLK is dependent<br>DAC module is enabled   | on HFPERCLK frequency. This currer<br>in the CMU.                                | nt contributes to | the total supp  | bly current use | ed when   |

|                             |                                                | pe from 10% to 90% of full scale. Offs<br>at 10% of full scale with the measured |                   | by comparing    | actual VDAC     | output at |

|                             |                                                | $\Delta V_{OUT}$ ), VDAC output at 90% of full set                               | aala              |                 |                 |           |

## 4.1.17 Operational Amplifier (OPAMP)

Unless otherwise indicated, specified conditions are: Non-inverting input configuration, VDD = 3.3 V, DRIVESTRENGTH = 2, MAIN-OUTEN = 1,  $C_{LOAD}$  = 75 pF with OUTSCALE = 0, or  $C_{LOAD}$  = 37.5 pF with OUTSCALE = 1. Unit gain buffer and 3X-gain connection as specified in table footnotes<sup>8 1</sup>.

| Parameter                     | Symbol            | Test Condition                                                                                                                                                                | Min              | Тур  | Мах                   | Unit |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----------------------|------|

| Supply voltage (from AVDD)    | V <sub>OPA</sub>  | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | 2                | _    | 3.8                   | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | 1.62             |      | 3.8                   | V    |

| Input voltage                 | V <sub>IN</sub>   | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | $V_{VSS}$        | _    | V <sub>OPA</sub>      | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | V <sub>VSS</sub> | _    | V <sub>OPA</sub> -1.2 | V    |

| Input impedance               | R <sub>IN</sub>   |                                                                                                                                                                               | 100              | _    | _                     | MΩ   |

| Output voltage                | V <sub>OUT</sub>  |                                                                                                                                                                               | V <sub>VSS</sub> |      | V <sub>OPA</sub>      | V    |

| Load capacitance <sup>2</sup> | C <sub>LOAD</sub> | OUTSCALE = 0                                                                                                                                                                  | _                |      | 75                    | pF   |

|                               |                   | OUTSCALE = 1                                                                                                                                                                  | _                | _    | 37.5                  | pF   |

| Output impedance              | R <sub>OUT</sub>  | DRIVESTRENGTH = 2 or 3, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -8 mA <<br>I <sub>OUT</sub> < 8 mA, Buffer connection,<br>Full supply range         | _                | 0.25 | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -400 µA $<$<br>I <sub>OUT</sub> $<$ 400 µA, Buffer connection,<br>Full supply range | _                | 0.6  | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 2 or 3, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -2 mA $<$<br>I <sub>OUT</sub> $<$ 2 mA, Buffer connection,<br>Full supply range     | _                | 0.4  | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -100 µA $<$<br>I <sub>OUT</sub> $<$ 100 µA, Buffer connection,<br>Full supply range | _                | 1    | _                     | Ω    |

| Internal closed-loop gain     | G <sub>CL</sub>   | Buffer connection                                                                                                                                                             | TBD              | 1    | TBD                   | -    |

|                               |                   | 3x Gain connection                                                                                                                                                            | TBD              | 2.99 | TBD                   | -    |

|                               |                   | 16x Gain connection                                                                                                                                                           | TBD              | 15.7 | TBD                   | -    |

| Active current <sup>4</sup>   | I <sub>OPA</sub>  | DRIVESTRENGTH = 3, OUT-<br>SCALE = 0                                                                                                                                          | _                | 580  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 2, OUT-<br>SCALE = 0                                                                                                                                          | _                | 176  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 1, OUT-<br>SCALE = 0                                                                                                                                          | _                | 13   | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 0, OUT-<br>SCALE = 0                                                                                                                                          | _                | 4.7  | -                     | μA   |

### Table 4.24. Operational Amplifier (OPAMP)

### 4.1.19 Pulse Counter (PCNT)

### Table 4.26. Pulse Counter (PCNT)

| Parameter       | Symbol          | Test Condition                                | Min | Тур | Max | Unit |

|-----------------|-----------------|-----------------------------------------------|-----|-----|-----|------|

| Input frequency | F <sub>IN</sub> | Asynchronous Single and Quad-<br>rature Modes | —   | —   | 20  | MHz  |

|                 |                 | Sampled Modes with Debounce filter set to 0.  |     |     | 8   | kHz  |

### 4.1.20 Analog Port (APORT)

### Table 4.27. Analog Port (APORT)

| Parameter                     | Symbol | Test Condition       | Min | Тур | Max | Unit |

|-------------------------------|--------|----------------------|-----|-----|-----|------|

| Supply current <sup>2 1</sup> | IAPORT | Operation in EM0/EM1 | —   | 7   | —   | μA   |

|                               |        | Operation in EM2/EM3 |     | 915 |     | nA   |

#### Note:

1. Specified current is for continuous APORT operation. In applications where the APORT is not requested continuously (e.g. periodic ACMP requests from LESENSE in EM2), the average current requirements can be estimated by mutiplying the duty cycle of the requests by the specified continuous current number.

2. Supply current increase that occurs when an analog peripheral requests access to APORT. This current is not included in reported module currents. Additional peripherals requesting access to APORT do not incur further current.

## 4.1.21 I2C

# 4.1.21.1 I2C Standard-mode (Sm)<sup>1</sup>

| Table 4.28. | I2C Standard-mode | (Sm) <sup>1</sup> |

|-------------|-------------------|-------------------|

|-------------|-------------------|-------------------|

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | —   | 100  | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 4.7 | —   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 4   | _   |      | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 250 |     |      | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD_DAT</sub> |                | 100 |     | 3450 | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 4.7 | _   | _    | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 4   |     | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 4   |     |      | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 4.7 | —   | —    | μs   |

## Note:

1. For CLHR set to 0 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Standard-mode, refer to the I2C chapter in the reference manual.

3. The maximum SDA hold time (t<sub>HD DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

| Pin Name              | Pin(s)    | Description                | Pin Name | Pin(s) | Description |

|-----------------------|-----------|----------------------------|----------|--------|-------------|

| PE15                  | 79        | GPIO                       | PA15     | 80     | GPIO        |

| Note:<br>1. GPIO with | 5V tolera | nce are indicated by (5V). |          |        | ·           |

| Pin Name | Pin(s)   | Description                                                                                              | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|----------------------------------------------------------------------------------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13       | GPIO                                                                                                     | PC5      | 14     | GPIO                                                                                                                                                                                                        |

| PB7      | 15       | GPIO                                                                                                     | PB8      | 16     | GPIO                                                                                                                                                                                                        |

| PA8      | 17       | GPIO                                                                                                     | PA12     | 18     | GPIO                                                                                                                                                                                                        |

| PA14     | 19       | GPIO                                                                                                     | RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21       | GPIO                                                                                                     | PB12     | 22     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.                                                                                     | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26       | GPIO                                                                                                     | PD0      | 29     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 30       | GPIO                                                                                                     | PD3      | 31     | GPIO                                                                                                                                                                                                        |

| PD4      | 32       | GPIO                                                                                                     | PD5      | 33     | GPIO                                                                                                                                                                                                        |

| PD6      | 34       | GPIO                                                                                                     | PD7      | 35     | GPIO                                                                                                                                                                                                        |

| PD8      | 36       | GPIO                                                                                                     | PC7      | 37     | GPIO                                                                                                                                                                                                        |

| VREGVSS  | 38       | Voltage regulator VSS                                                                                    | VREGSW   | 39     | DCDC regulator switching node                                                                                                                                                                               |

| VREGVDD  | 40       | Voltage regulator VDD input                                                                              | DVDD     | 41     | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 42       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PE4      | 43     | GPIO                                                                                                                                                                                                        |

| PE5      | 44       | GPIO                                                                                                     | PE6      | 45     | GPIO                                                                                                                                                                                                        |

| PE7      | 46       | GPIO                                                                                                     | PC12     | 47     | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 48       | GPIO (5V)                                                                                                | PF0      | 49     | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50       | GPIO (5V)                                                                                                | PF2      | 51     | GPIO                                                                                                                                                                                                        |

| PF3      | 52       | GPIO                                                                                                     | PF4      | 53     | GPIO                                                                                                                                                                                                        |

| PF5      | 54       | GPIO                                                                                                     | PE8      | 57     | GPIO                                                                                                                                                                                                        |

| PE9      | 58       | GPIO                                                                                                     | PE10     | 59     | GPIO                                                                                                                                                                                                        |

| PE11     | 60       | GPIO                                                                                                     | PE12     | 61     | GPIO                                                                                                                                                                                                        |

| PE13     | 62       | GPIO                                                                                                     | PE14     | 63     | GPIO                                                                                                                                                                                                        |

| PE15     | 64       | GPIO                                                                                                     |          |        |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s)   | Description                                                                                                                                                                                                 | Pin Name | Pin(s) | Description                   |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-------------------------------|

| PB8      | 11       | GPIO                                                                                                                                                                                                        | PA8      | 12     | GPIO                          |

| PA12     | 13       | GPIO                                                                                                                                                                                                        | PA14     | 14     | GPIO                          |

| RESETn   | 15       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB11     | 16     | GPIO                          |

| AVDD     | 18<br>22 | Analog power supply.                                                                                                                                                                                        | PB13     | 19     | GPIO                          |

| PB14     | 20       | GPIO                                                                                                                                                                                                        | PD4      | 23     | GPIO                          |

| PD5      | 24       | GPIO                                                                                                                                                                                                        | PD6      | 25     | GPIO                          |

| PD7      | 26       | GPIO                                                                                                                                                                                                        | PD8      | 27     | GPIO                          |

| VREGVSS  | 28       | Voltage regulator VSS                                                                                                                                                                                       | VREGSW   | 29     | DCDC regulator switching node |

| VREGVDD  | 30       | Voltage regulator VDD input                                                                                                                                                                                 | DVDD     | 31     | Digital power supply.         |

| DECOUPLE | 32       | Decouple output for on-chip voltage<br>regulator. An external decoupling ca-<br>pacitor is required at this pin.                                                                                            | PE4      | 33     | GPIO                          |

| PE5      | 34       | GPIO                                                                                                                                                                                                        | PE6      | 35     | GPIO                          |

| PE7      | 36       | GPIO                                                                                                                                                                                                        | PF0      | 37     | GPIO (5V)                     |

| PF1      | 38       | GPIO (5V)                                                                                                                                                                                                   | PF2      | 39     | GPIO                          |

| PF3      | 40       | GPIO                                                                                                                                                                                                        | PF4      | 41     | GPIO                          |

| PF5      | 42       | GPIO                                                                                                                                                                                                        | PE10     | 45     | GPIO                          |

| PE11     | 46       | GPIO                                                                                                                                                                                                        | PE12     | 47     | GPIO                          |

| PE13     | 48       | GPIO                                                                                                                                                                                                        |          |        |                               |

1. GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s) | Description           | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|-----------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB8      | 8      | GPIO                  | RESETn   | 9        | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 10     | GPIO                  | AVDD     | 11<br>15 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 12     | GPIO                  | PB14     | 13       | GPIO                                                                                                                                                                                                        |

| PD4      | 16     | GPIO                  | PD5      | 17       | GPIO                                                                                                                                                                                                        |

| PD6      | 18     | GPIO                  | PD7      | 19       | GPIO                                                                                                                                                                                                        |

| DVDD     | 20     | Digital power supply. | DECOUPLE | 21       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PC13     | 22     | GPIO (5V)             | PC14     | 23       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 24     | GPIO (5V)             | PF0      | 25       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 26     | GPIO (5V)             | PF2      | 27       | GPIO                                                                                                                                                                                                        |

| PE10     | 29     | GPIO                  | PE11     | 30       | GPIO                                                                                                                                                                                                        |

| PE12     | 31     | GPIO                  | PE13     | 32       | GPIO                                                                                                                                                                                                        |

| Note:    |        | ,                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

#### 5.15 Alternate Functionality Overview

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings and the associated GPIO pin. Refer to 5.14 GPIO Functionality Table for a list of functions available on each GPIO pin.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     | LOC               | ATION   |                                                                          |

|---------------|-------------------|---------|--------------------------------------------------------------------------|

| Functionality | 0 - 3             | 4 - 7   | Description                                                              |

|               | 0: PE13           | 4: PA6  |                                                                          |

| ACMP0_O       | 2: PD6<br>3: PB11 | 7: PB3  | Analog comparator ACMP0, digital output.                                 |

|               | 0: PF2            | 4: PA14 |                                                                          |

| ACMP1_O       | 2: PD7<br>3: PA12 | 7: PA5  | Analog comparator ACMP1, digital output.                                 |

|               | 0: PD7            |         |                                                                          |

| ADC0_EXTN     |                   |         | Analog to digital converter ADC0 external reference input negative pin.  |

|               | 0: PD6            |         |                                                                          |

| ADC0_EXTP     |                   |         | Analog to digital converter ADC0 external reference input positive pin.  |

|               | 0: PF1            |         |                                                                          |

| BOOT_RX       |                   |         | Bootloader RX.                                                           |

|               | 0: PF0            |         |                                                                          |

| BOOT_TX       |                   |         | Bootloader TX.                                                           |

|               | 0: PA8            |         |                                                                          |

| BU_STAT       |                   |         | Backup Power Domain status, whether or not the system is in backup mode. |

|               | 0: PD8            |         |                                                                          |

| BU_VIN        |                   |         | Battery input for Backup Power Domain.                                   |

|               | 0: PA12           |         |                                                                          |

| BU_VOUT       |                   |         | Power output for Backup Power Domain.                                    |

|               | 0: PC0<br>1: PF0  |         |                                                                          |

| CAN0_RX       | 2: PD0            |         | CAN0 RX.                                                                 |

#### Table 5.15. Alternate Functionality Overview

| Alternate     | LOC                         | ATION                                 |                                                                                                                                                                                                                                |

|---------------|-----------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                       | 4 - 7                                 | Description                                                                                                                                                                                                                    |

| GPIO_EM4WU4   | 0: PF2                      |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU5   | 0: PE13                     |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU6   | 0: PC4                      |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU7   | 0: PB11                     |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU9   | 0: PE10                     |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| HFXTAL_N      | 0: PB14                     |                                       | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                                                                           |

| HFXTAL_P      | 0: PB13                     |                                       | High Frequency Crystal positive pin.                                                                                                                                                                                           |

| I2C0_SCL      | 0: PA1<br>1: PD7<br>2: PC7  | 4: PC1<br>5: PF1<br>6: PE13<br>7: PE5 | I2C0 Serial Clock Line input / output.                                                                                                                                                                                         |

| I2C0_SDA      | 0: PA0<br>1: PD6<br>2: PC6  | 4: PC0<br>5: PF0<br>6: PE12<br>7: PE4 | I2C0 Serial Data input / output.                                                                                                                                                                                               |

| I2C1_SCL      | 0: PC5<br>1: PB12<br>3: PD5 | 4: PF2                                | I2C1 Serial Clock Line input / output.                                                                                                                                                                                         |

| I2C1_SDA      | 0: PC4<br>1: PB11<br>3: PD4 | 4: PC11                               | I2C1 Serial Data input / output.                                                                                                                                                                                               |

|               | 0: PA14                     |                                       | LCD external supply bypass in step down or charge pump mode. If using the LCD in step-down or charge pump mode, a 1 uF (minimum) capacitor between this pin and VSS is required.                                               |

| LCD_BEXT      |                             |                                       | To reduce supply ripple, a larger capcitor of approximately 1000 times the total LCD segment capacitance may be used.<br>If using the LCD with the internal supply source, this pin may be left unconnected or used as a GPIO. |

| Alternate     | LOCA    | TION  |                                    |

|---------------|---------|-------|------------------------------------|

| Functionality | 0 - 3   | 4 - 7 | Description                        |

| LCD_SEG35     | 0: PC9  |       | LCD segment line 35.               |

| LES_ALTEX0    | 0: PD6  |       | LESENSE alternate excite output 0. |

| LES_ALTEX1    | 0: PD7  |       | LESENSE alternate excite output 1. |

| LES_ALTEX2    | 0: PA3  |       | LESENSE alternate excite output 2. |

| LES_ALTEX3    | 0: PA4  |       | LESENSE alternate excite output 3. |

| LES_ALTEX4    | 0: PA5  |       | LESENSE alternate excite output 4. |

| LES_ALTEX5    | 0: PE11 |       | LESENSE alternate excite output 5. |

| LES_ALTEX6    | 0: PE12 |       | LESENSE alternate excite output 6. |

| LES_ALTEX7    | 0: PE13 |       | LESENSE alternate excite output 7. |

| LES_CH0       | 0: PC0  |       | LESENSE channel 0.                 |

| LES_CH1       | 0: PC1  |       | LESENSE channel 1.                 |

| LES_CH2       | 0: PC2  |       | LESENSE channel 2.                 |

| LES_CH3       | 0: PC3  |       | LESENSE channel 3.                 |

| Alternate     | LOC                        | ATION  |                                                        |  |  |  |  |  |  |

|---------------|----------------------------|--------|--------------------------------------------------------|--|--|--|--|--|--|

| Functionality | 0 - 3                      | 4 - 7  | Description                                            |  |  |  |  |  |  |

| WTIM1_CC3     | 0: PD1<br>1: PD5<br>2: PC6 | 4: PE6 | Wide timer 1 Capture Compare input / output channel 3. |  |  |  |  |  |  |

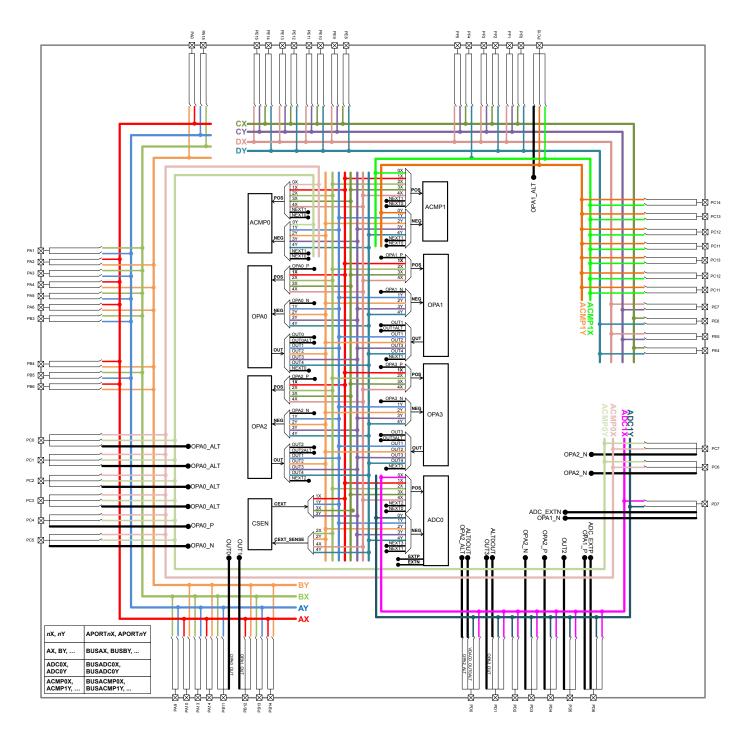

### 5.16 Analog Port (APORT) Client Maps

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. Figure 5.14 APORT Connection Diagram on page 119 shows the APORT routing for this device family (note that available features may vary by part number). A complete description of APORT functionality can be found in the Reference Manual.

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin

| Port           | Bus       | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СН9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | СНО |

|----------------|-----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| <b>APORT0X</b> | BUSACMP0X |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PCO |

| <b>APORT0Y</b> | BUSACMP0Y |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PCO |

| APORT1X        | BUSAX     |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT1Y        | BUSAY     |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2X        | BUSBX     |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY     |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3X        | BUSCX     |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| <b>APORT3Y</b> | BUSCY     |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4X        | BUSDX     |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY     |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

PF7 is available on port APORT2X as CH23, the register field enumeration to connect to PF7 would be APORT2XCH23. The shared bus used by this connection is indicated in the Bus column.

## Table 5.16. ACMP0 Bus and Pin Mapping

### Table 8.2. TQFP64 PCB Land Pattern Dimensions

| Dimension | Min      | Мах   |  |  |  |  |  |  |

|-----------|----------|-------|--|--|--|--|--|--|

| C1        | 11.30    | 11.40 |  |  |  |  |  |  |

| C2        | 11.30    | 11.40 |  |  |  |  |  |  |

| E         | 0.50 BSC |       |  |  |  |  |  |  |

| x         | 0.20     | 0.30  |  |  |  |  |  |  |

| Y         | 1.40     | 1.50  |  |  |  |  |  |  |

### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 8.3 TQFP64 Package Marking

Figure 8.3. TQFP64 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

Figure 11.3. QFN32 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.