Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT          |

| Number of I/O              | 37                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b320f128gq48-ar |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Parameter                                       | Symbol                | Test Condition                                                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-----------------------|----------------------------------------------------------------|-----|-----|-----|------|

| Max load current                                | I <sub>LOAD_MAX</sub> | Low noise (LN) mode, Heavy Drive <sup>2</sup> , T $\leq$ 85 °C | _   | _   | 200 | mA   |

|                                                 |                       | Low noise (LN) mode, Heavy<br>Drive <sup>2</sup> , T > 85 °C   | _   | _   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Medium Drive <sup>2</sup>                 | _   | _   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Light Drive <sup>2</sup>                  | _   | _   | 50  | mA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0         | _   | _   | 75  | μA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3         | _   | _   | 10  | mA   |

| DCDC nominal output ca-<br>pacitor <sup>5</sup> | C <sub>DCDC</sub>     | 25% tolerance                                                  | 1   | 4.7 | 4.7 | μF   |

| DCDC nominal output induc-<br>tor               | L <sub>DCDC</sub>     | 20% tolerance                                                  | 4.7 | 4.7 | 4.7 | μH   |

| Resistance in Bypass mode                       | R <sub>BYP</sub>      |                                                                | _   | 1.2 | TBD | Ω    |

#### Note:

1. Due to internal dropout, the DC-DC output will never be able to reach its input voltage, V<sub>VREGVDD</sub>.

- 2. Drive levels are defined by configuration of the PFETCNT and NFETCNT registers. Light Drive: PFETCNT=NFETCNT=3; Medium Drive: PFETCNT=NFETCNT=7; Heavy Drive: PFETCNT=15.

- 3. LPCMPBIASEMxx refers to either LPCMPBIASEM234H in the EMU\_DCDCMISCCTRL register or LPCMPBIASEM01 in the EMU\_DCDCLOEM01CFG register, depending on the energy mode.

4. LP mode controller is a hysteretic controller that maintains the output voltage within the specified limits.

5. Output voltage under/over-shoot and regulation are specified with C<sub>DCDC</sub> 4.7 μF. Different settings for DCDCLNCOMPCTRL must be used if C<sub>DCDC</sub> is lower than 4.7 μF. See Application Note AN0948 for details.

| Parameter                                                                                                          | Symbol                  | Test Condition                                                       | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-                                                          | IACTIVE_CCM_VS          | 19 MHz HFRCO, CPU running while loop from flash                      | _   | 81   | _   | µA/MHz |

| abled and voltage scaling<br>enabled, DCDC in Low<br>Noise CCM mode <sup>1</sup>                                   |                         | 1 MHz HFRCO, CPU running while loop from flash                       | —   | 1147 |     | µA/MHz |

| Current consumption in EM0 mode with all peripherals dis-                                                          | IACTIVE_LPM_VS          | 19 MHz HFRCO, CPU running while loop from flash                      | _   | 30   | _   | µA/MHz |

| abled and voltage scaling enabled, DCDC in LP mode <sup>3</sup>                                                    |                         | 1 MHz HFRCO, CPU running while loop from flash                       | _   | 144  | _   | µA/MHz |

| Current consumption in EM1                                                                                         | I <sub>EM1_DCM</sub>    | 48 MHz crystal                                                       | _   | 31   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled, DCDC in Low Noise                                                         |                         | 48 MHz HFRCO                                                         | _   | 30   | _   | µA/MHz |

| DCM mode <sup>2</sup>                                                                                              |                         | 32 MHz HFRCO                                                         | _   | 36   | _   | µA/MHz |

|                                                                                                                    |                         | 26 MHz HFRCO                                                         | _   | 41   | _   | µA/MHz |

|                                                                                                                    |                         | 16 MHz HFRCO                                                         |     | 54   | _   | µA/MHz |

|                                                                                                                    |                         | 1 MHz HFRCO                                                          |     | 581  | _   | µA/MHz |

| Current consumption in EM1                                                                                         | I <sub>EM1_LPM</sub>    | 32 MHz HFRCO                                                         |     | 25   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled, DCDC in Low Power                                                         |                         | 26 MHz HFRCO                                                         | _   | 26   | _   | µA/MHz |

| mode <sup>3</sup>                                                                                                  |                         | 16 MHz HFRCO                                                         | _   | 29   | _   | µA/MHz |

|                                                                                                                    |                         | 1 MHz HFRCO                                                          | _   | 153  | _   | µA/MHz |

| Current consumption in EM1                                                                                         | Iem1_dcm_vs             | 19 MHz HFRCO                                                         | _   | 46   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled, DCDC in Low<br>Noise DCM mode <sup>2</sup> |                         | 1 MHz HFRCO                                                          | _   | 573  | _   | µA/MHz |

| Current consumption in EM1                                                                                         | I <sub>EM1_LPM_VS</sub> | 19 MHz HFRCO                                                         | _   | 25   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled. DCDC in LP mode <sup>3</sup>               |                         | 1 MHz HFRCO                                                          | _   | 140  | _   | µA/MHz |

| Current consumption in EM2<br>mode, with voltage scaling                                                           | I <sub>EM2_VS</sub>     | Full 32 kB RAM retention and<br>RTCC running from LFXO               | _   | 1.26 | _   | μΑ     |

| enabled, DCDC in LP mode <sup>3</sup>                                                                              |                         | Full 32 kB RAM retention and<br>RTCC running from LFRCO              | _   | 1.54 | _   | μΑ     |

|                                                                                                                    |                         | 8 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>5</sup> | —   | 1.30 | _   | μA     |

| Current consumption in EM3 mode, with voltage scaling enabled                                                      | IEM3_VS                 | Full 32 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO   | _   | 0.93 |     | μA     |

| Current consumption in<br>EM4H mode, with voltage                                                                  | I <sub>EM4H_VS</sub>    | 128 byte RAM retention, RTCC running from LFXO                       | _   | 0.78 | _   | μΑ     |

| scaling enabled                                                                                                    |                         | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO           | _   | 0.50 |     | μΑ     |

|                                                                                                                    |                         | 128 byte RAM retention, no RTCC                                      | _   | 0.50 | _   | μA     |

| Current consumption in EM4S mode                                                                                   | I <sub>EM4S</sub>       | No RAM retention, no RTCC                                            |     | 0.06 |     | μΑ     |

## 4.1.10 Flash Memory Characteristics<sup>5</sup>

| Parameter                                   | Symbol               | Test Condition                                | Min   | Тур | Мах | Unit   |

|---------------------------------------------|----------------------|-----------------------------------------------|-------|-----|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                                               | 10000 | _   | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T ≤ 85 °C                                     | 10    | _   | _   | years  |

|                                             |                      | T ≤ 125 °C                                    | 10    |     | _   | years  |

| Word (32-bit) programming time              | tw_prog              | Burst write, 128 words, average time per word | 20    | 26  | 32  | μs     |

|                                             |                      | Single word                                   | 59    | 68  | 83  | μs     |

| Page erase time <sup>4</sup>                | t <sub>PERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Device erase time <sup>2 3</sup>            | t <sub>DERASE</sub>  | T ≤ 85 °C                                     | _     | 54  | 70  | ms     |

|                                             |                      | T ≤ 125 °C                                    | _     | 54  | 75  | ms     |

| Erase current <sup>6</sup>                  | I <sub>ERASE</sub>   | Page Erase                                    | _     | _   | 1.7 | mA     |

|                                             |                      | Mass or Device Erase                          | _     |     | 2.0 | mA     |

| Write current <sup>6</sup>                  | I <sub>WRITE</sub>   |                                               | —     |     | 3.5 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                                               | 1.62  | _   | 3.6 | V      |

### Table 4.17. Flash Memory Characteristics<sup>5</sup>

# Note:

- 1. Mass erase is issued by the CPU and erases all flash.

- 2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

- 3. From setting the DEVICEERASE bit in AAP\_CMD to 1 until the ERASEBUSY bit in AAP\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 4. From setting the ERASEPAGE bit in MSC\_WRITECMD to 1 until the BUSY bit in MSC\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 5. Flash data retention information is published in the Quarterly Quality and Reliability Report.

6. Measured at 25 °C.

### 4.1.13 Analog to Digital Converter (ADC)

Specified at 1 Msps, ADCCLK = 16 MHz, BIASPROG = 0, GPBIASACC = 0, unless otherwise indicated.

## Table 4.20. Analog to Digital Converter (ADC)

| Parameter                                                                                     | Symbol                             | Test Condition                                                           | Min                 | Тур | Мах                | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|---------------------|-----|--------------------|------|

| Resolution                                                                                    | VRESOLUTION                        |                                                                          | 6                   | —   | 12                 | Bits |

| Input voltage range <sup>5</sup>                                                              | V <sub>ADCIN</sub>                 | Single ended                                                             | _                   | —   | V <sub>FS</sub>    | V    |

|                                                                                               |                                    | Differential                                                             | -V <sub>FS</sub> /2 | _   | V <sub>FS</sub> /2 | V    |

| Input range of external refer-<br>ence voltage, single ended<br>and differential              | V <sub>ADCREFIN_P</sub>            |                                                                          | 1                   | _   | V <sub>AVDD</sub>  | V    |

| Power supply rejection <sup>2</sup>                                                           | PSRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | -                  | dB   |

| Analog input common mode rejection ratio                                                      | CMRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | -                  | dB   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | I <sub>ADC_CONTI-</sub><br>NOUS_LP | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>    | _                   | 270 | TBD                | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                          |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 1 <sup>3</sup>   | _                   | 125 | -                  | μA   |

|                                                                                               |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 1 <sup>3</sup> | _                   | 80  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | I <sub>ADC_NORMAL_LP</sub>         | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 45  | -                  | μA   |

| Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL                                  |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>     | _                   | 8   | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_STAND-<br>BY_LP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>  | _                   | 105 | -                  | μA   |

| Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 70  | _                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_CONTI-<br>NOUS_HP             | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>    | _                   | 325 | -                  | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                          |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 0 <sup>3</sup>   | _                   | 175 | -                  | μA   |

|                                                                                               |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 0 <sup>3</sup> | _                   | 125 | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_NORMAL_HP                     | 35 ksps / 16 MHz ADCCLK, BIA-SPROG = 0, GPBIASACC = 0 $^3$               | _                   | 85  | -                  | μA   |

| Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL                                  |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>     | _                   | 16  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                              | IADC_STAND-<br>BY_HP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>  | —                   | 160 | -                  | μA   |

| Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>   | _                   | 125 | -                  | μA   |

| Current from HFPERCLK                                                                         | IADC_CLK                           | HFPERCLK = 16 MHz                                                        | _                   | 166 | _                  | μΑ   |

### 4.1.17 Operational Amplifier (OPAMP)

Unless otherwise indicated, specified conditions are: Non-inverting input configuration, VDD = 3.3 V, DRIVESTRENGTH = 2, MAIN-OUTEN = 1,  $C_{LOAD}$  = 75 pF with OUTSCALE = 0, or  $C_{LOAD}$  = 37.5 pF with OUTSCALE = 1. Unit gain buffer and 3X-gain connection as specified in table footnotes<sup>8 1</sup>.

| Parameter                     | Symbol            | Test Condition                                                                                                                                                                | Min              | Тур  | Мах                   | Unit |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----------------------|------|

| Supply voltage (from AVDD)    | V <sub>OPA</sub>  | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | 2                | _    | 3.8                   | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | 1.62             |      | 3.8                   | V    |

| Input voltage                 | V <sub>IN</sub>   | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | $V_{VSS}$        | _    | V <sub>OPA</sub>      | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | V <sub>VSS</sub> | _    | V <sub>OPA</sub> -1.2 | V    |

| Input impedance               | R <sub>IN</sub>   |                                                                                                                                                                               | 100              | _    | _                     | MΩ   |

| Output voltage                | V <sub>OUT</sub>  |                                                                                                                                                                               | V <sub>VSS</sub> |      | V <sub>OPA</sub>      | V    |

| Load capacitance <sup>2</sup> | C <sub>LOAD</sub> | OUTSCALE = 0                                                                                                                                                                  | _                |      | 75                    | pF   |

|                               |                   | OUTSCALE = 1                                                                                                                                                                  | _                | _    | 37.5                  | pF   |

| Output impedance              | R <sub>OUT</sub>  | DRIVESTRENGTH = 2 or 3, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -8 mA <<br>I <sub>OUT</sub> < 8 mA, Buffer connection,<br>Full supply range         | _                | 0.25 | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -400 µA $<$<br>I <sub>OUT</sub> $<$ 400 µA, Buffer connection,<br>Full supply range | _                | 0.6  | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 2 or 3, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -2 mA $<$<br>I <sub>OUT</sub> $<$ 2 mA, Buffer connection,<br>Full supply range     | _                | 0.4  | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -100 µA $<$<br>I <sub>OUT</sub> $<$ 100 µA, Buffer connection,<br>Full supply range | _                | 1    | _                     | Ω    |

| Internal closed-loop gain     | G <sub>CL</sub>   | Buffer connection                                                                                                                                                             | TBD              | 1    | TBD                   | -    |

|                               |                   | 3x Gain connection                                                                                                                                                            | TBD              | 2.99 | TBD                   | -    |

|                               |                   | 16x Gain connection                                                                                                                                                           | TBD              | 15.7 | TBD                   | -    |

| Active current <sup>4</sup>   | I <sub>OPA</sub>  | DRIVESTRENGTH = 3, OUT-<br>SCALE = 0                                                                                                                                          | _                | 580  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 2, OUT-<br>SCALE = 0                                                                                                                                          | _                | 176  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 1, OUT-<br>SCALE = 0                                                                                                                                          | _                | 13   | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 0, OUT-<br>SCALE = 0                                                                                                                                          | _                | 4.7  | -                     | μA   |

#### Table 4.24. Operational Amplifier (OPAMP)

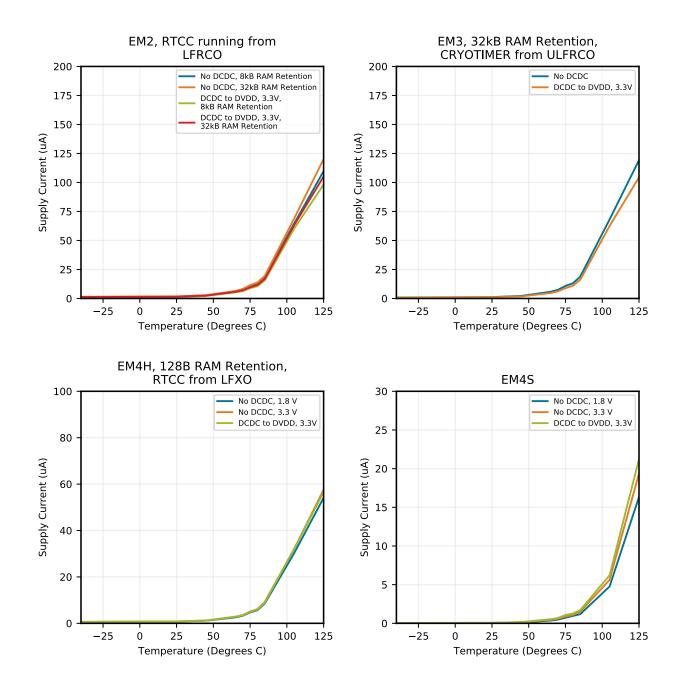

Figure 4.5. EM2, EM3, EM4H and EM4S Typical Supply Current vs. Temperature

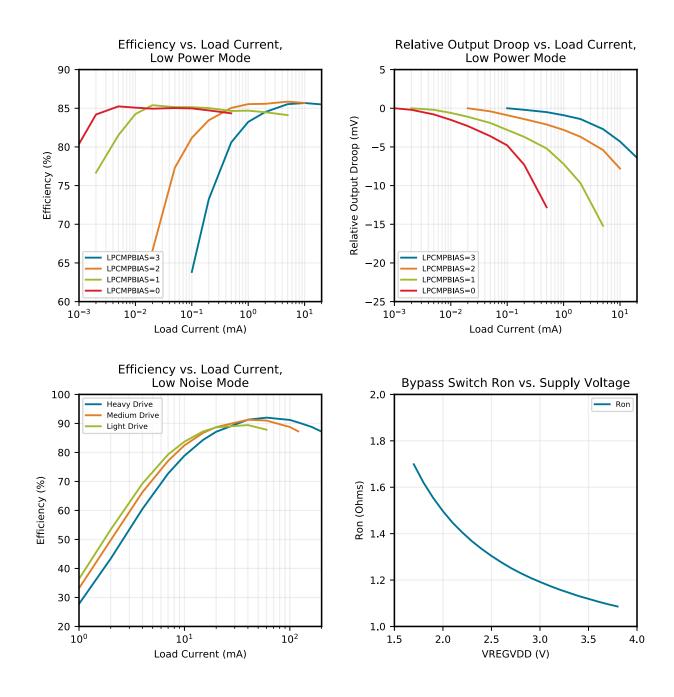

#### 4.2.2 DC-DC Converter

Default test conditions: CCM mode, LDCDC = 4.7 µH, CDCDC = 4.7 µF, VDCDC\_I = 3.3 V, VDCDC\_O = 1.8 V, FDCDC\_LN = 7 MHz

Figure 4.8. DC-DC Converter Typical Performance Characteristics

#### Figure 5.7. EFM32TG11B3xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>26<br>55 | Digital IO power supply 0. | PB3      | 9      | GPIO        |

| PB4      | 10            | GPIO                       | PB5      | 11     | GPIO        |

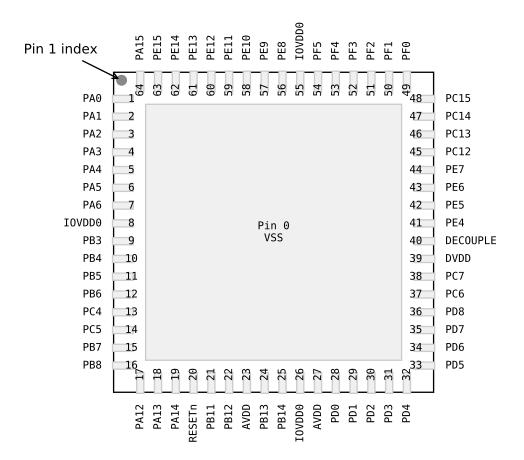

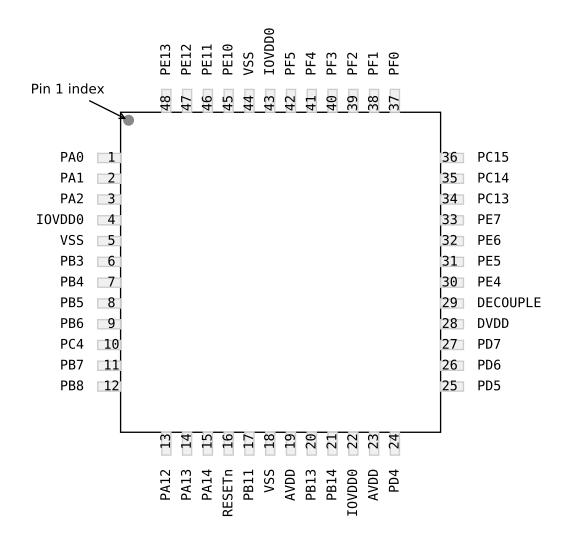

#### Figure 5.10. EFM32TG11B3xx in QFP48 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.10. | EFM32TG11B3xx in | <b>QFP48 Device Pinout</b> |

|-------------|------------------|----------------------------|

|-------------|------------------|----------------------------|

| Pin Name | Pin(s)        | Description | Pin Name | Pin(s)        | Description                |

|----------|---------------|-------------|----------|---------------|----------------------------|

| PA0      | 1             | GPIO        | PA1      | 2             | GPIO                       |

| PA2      | 3             | GPIO        | IOVDD0   | 4<br>22<br>43 | Digital IO power supply 0. |

| VSS      | 5<br>18<br>44 | Ground      | PB3      | 6             | GPIO                       |

| PB4      | 7             | GPIO        | PB5      | 8             | GPIO                       |

| PB6      | 9             | GPIO        | PC4      | 10            | GPIO                       |

| Pin Name                                                  | Pin(s) | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |  |

|-----------------------------------------------------------|--------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PA14                                                      | 8      | GPIO                          | RESETn   | 9      | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |  |

| PB11                                                      | 10     | GPIO                          | AVDD     | 11     | Analog power supply.                                                                                                                                                                                        |  |

| PB13                                                      | 12     | GPIO                          | PB14     | 13     | GPIO                                                                                                                                                                                                        |  |

| PD4                                                       | 15     | GPIO                          | PD5      | 16     | GPIO                                                                                                                                                                                                        |  |

| PD6                                                       | 17     | GPIO                          | PD7      | 18     | GPIO                                                                                                                                                                                                        |  |

| VREGSW                                                    | 20     | DCDC regulator switching node | VREGVDD  | 21     | Voltage regulator VDD input                                                                                                                                                                                 |  |

| DVDD                                                      | 22     | Digital power supply.         | DECOUPLE | 23     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |  |

| PE4                                                       | 24     | GPIO                          | PE5      | 25     | GPIO                                                                                                                                                                                                        |  |

| PC15                                                      | 26     | GPIO (5V)                     | PF0      | 27     | GPIO (5V)                                                                                                                                                                                                   |  |

| PF1                                                       | 28     | GPIO (5V)                     | PF2      | 29     | GPIO                                                                                                                                                                                                        |  |

| PE11                                                      | 31     | GPIO                          | PE12     | 32     | GPIO                                                                                                                                                                                                        |  |

| Note:<br>1. GPIO with 5V tolerance are indicated by (5V). |        |                               |          |        |                                                                                                                                                                                                             |  |

| GPIO Name |                                                            | Pin Alternate Functi                                                               | onality / Description                                                     |                                                      |

|-----------|------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|

|           | Analog                                                     | Timers                                                                             | Communication                                                             | Other                                                |

| PD5       | BUSADC0Y BUSADC0X<br>OPA2_OUT                              | WTIM0_CDTI1 #4<br>WTIM1_CC3 #1                                                     | US1_RTS #1 U0_CTS #5<br>LEU0_RX #0 I2C1_SCL<br>#3                         |                                                      |

| PD6       | BUSADC0Y BUSADC0X<br>ADC0_EXTP<br>VDAC0_EXT OPA1_P         | TIM1_CC0 #4<br>WTIM0_CDTI2 #4<br>WTIM1_CC0 #2 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US0_RTS #5 US1_RX #2<br>US2_CTS #5 US3_CTS<br>#2 U0_RTS #5 I2C0_SDA<br>#1 | CMU_CLK2 #2 LES_AL-<br>TEX0 PRS_CH5 #2<br>ACMP0_O #2 |

| PD7       | BUSADC0Y BUSADC0X<br>ADC0_EXTN OPA1_N                      | TIM1_CC1 #4<br>WTIM1_CC1 #2 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3                   | US1_TX #2 US3_CLK #1<br>U0_TX #6 I2C0_SCL #1                              | CMU_CLK0 #2 LES_AL-<br>TEX1 ACMP1_O #2               |

| PD8       | BU_VIN                                                     | WTIM1_CC2 #2                                                                       | US2_RTS #5                                                                | CMU_CLK1 #1                                          |

| PC6       | BUSACMP0Y BU-<br>SACMP0X OPA3_P<br>LCD_SEG32               | WTIM1_CC3 #2                                                                       | US0_RTS #2 US1_CTS<br>#3 I2C0_SDA #2                                      | LES_CH6                                              |

| PC7       | BUSACMP0Y BU-<br>SACMP0X OPA3_N<br>LCD_SEG33               | WTIM1_CC0 #3                                                                       | US0_CTS #2 US1_RTS<br>#3 I2C0_SCL #2                                      | LES_CH7                                              |

| PE4       | BUSDY BUSCX<br>LCD_COM0                                    | WTIM0_CC0 #0<br>WTIM1_CC1 #4                                                       | US0_CS #1 US1_CS #5<br>US3_CS #1 U0_RX #6<br>I2C0_SDA #7                  |                                                      |

| PE5       | BUSCY BUSDX<br>LCD_COM1                                    | WTIM0_CC1 #0<br>WTIM1_CC2 #4                                                       | US0_CLK #1 US1_CLK<br>#6 US3_CTS #1<br>I2C0_SCL #7                        |                                                      |

| PE6       | BUSDY BUSCX<br>LCD_COM2                                    | WTIM0_CC2 #0<br>WTIM1_CC3 #4                                                       | US0_RX #1 US3_TX #1                                                       | PRS_CH6 #2                                           |

| PE7       | BUSCY BUSDX<br>LCD_COM3                                    | WTIM1_CC0 #5                                                                       | US0_TX #1 US3_RX #1                                                       | PRS_CH7 #2                                           |

| PC8       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG34                         |                                                                                    | US0_CS #2                                                                 | LES_CH8 PRS_CH4 #0                                   |

| PC9       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG35                         |                                                                                    | US0_CLK #2                                                                | LES_CH9 PRS_CH5 #0<br>GPIO_EM4WU2                    |

| PC10      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_RX #2                                                                 | LES_CH10                                             |

| PC11      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_TX #2 I2C1_SDA #4                                                     | LES_CH11                                             |

| PC12      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0 BU-<br>SACMP1Y BUSACMP1X | TIM1_CC3 #0                                                                        | US0_RTS #3 US1_CTS<br>#4 US2_CTS #4 U0_RTS<br>#3                          | CMU_CLK0 #1<br>LES_CH12                              |

| PC13      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #1 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI0 #1<br>TIM1_CC0 #0 TIM1_CC2<br>#4 PCNT0_S0IN #0                          | US0_CTS #3 US1_RTS<br>#4 US2_RTS #4 U0_CTS<br>#3                          | LES_CH13                                             |

| PC14      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI1 #1<br>TIM1_CC1 #0 TIM1_CC3<br>#4 LETIM0_OUT0 #5<br>PCNT0_S1IN #0        | US0_CS #3 US1_CS #3<br>US2_RTS #3 US3_CS #2<br>U0_TX #3 LEU0_TX #5        | LES_CH14 PRS_CH0 #2                                  |

| GPIO Name | Pin Alternate Functionality / Description                  |                                                                  |                                                              |                                                        |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|

|           | Analog                                                     | Timers                                                           | Communication                                                | Other                                                  |  |  |  |  |  |  |  |

| PC15      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #3 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI2 #1<br>TIM1_CC2 #0<br>WTIM0_CC0 #4 LE-<br>TIM0_OUT1 #5 | US0_CLK #3 US1_CLK<br>#3 US3_RTS #3 U0_RX<br>#3 LEU0_RX #5   | LES_CH15 PRS_CH1 #2                                    |  |  |  |  |  |  |  |

| PF0       | BUSDY BUSCX                                                | TIM0_CC0 #4<br>WTIM0_CC1 #4 LE-<br>TIM0_OUT0 #2                  | CAN0_RX #1 US1_CLK<br>#2 US2_TX #5 LEU0_TX<br>#3 I2C0_SDA #5 | DBG_SWCLKTCK<br>BOOT_TX                                |  |  |  |  |  |  |  |

| PF1       | BUSCY BUSDX                                                | TIM0_CC1 #4<br>WTIM0_CC2 #4 LE-<br>TIM0_OUT1 #2                  | US1_CS #2 US2_RX #5<br>U0_TX #5 LEU0_RX #3<br>I2C0_SCL #5    | PRS_CH4 #2<br>DBG_SWDIOTMS<br>GPIO_EM4WU3<br>BOOT_RX   |  |  |  |  |  |  |  |

| PF2       | BUSDY BUSCX<br>LCD_SEG0                                    |                                                                  |                                                              |                                                        |  |  |  |  |  |  |  |

| PF3       | BUSCY BUSDX<br>LCD_SEG1                                    | TIM0_CDTI0 #2<br>TIM1_CC1 #5                                     | US1_CTS #2                                                   | CMU_CLK1 #4 PRS_CH0<br>#1                              |  |  |  |  |  |  |  |

| PF4       | BUSDY BUSCX<br>LCD_SEG2                                    | TIM0_CDTI1 #2<br>TIM1_CC2 #5                                     | US1_RTS #2                                                   | PRS_CH1 #1                                             |  |  |  |  |  |  |  |

| PF5       | BUSCY BUSDX<br>LCD_SEG3                                    | TIM0_CDTI2 #2<br>TIM1_CC3 #6                                     | US2_CS #5                                                    | PRS_CH2 #1 DBG_TDI                                     |  |  |  |  |  |  |  |

| PE8       | BUSDY BUSCX<br>LCD_SEG4                                    |                                                                  |                                                              |                                                        |  |  |  |  |  |  |  |

| PE9       | BUSCY BUSDX<br>LCD_SEG5                                    |                                                                  |                                                              |                                                        |  |  |  |  |  |  |  |

| PE10      | BUSDY BUSCX<br>LCD_SEG6                                    | TIM1_CC0 #1<br>WTIM0_CDTI0 #0                                    | US0_TX #0                                                    | PRS_CH2 #2<br>GPIO_EM4WU9                              |  |  |  |  |  |  |  |

| PE11      | BUSCY BUSDX<br>LCD_SEG7                                    | TIM1_CC1 #1<br>WTIM0_CDTI1 #0                                    | US0_RX #0                                                    | LES_ALTEX5 PRS_CH3<br>#2                               |  |  |  |  |  |  |  |

| PE12      | BUSDY BUSCX<br>LCD_SEG8                                    |                                                                  |                                                              | CMU_CLK1 #2<br>CMU_CLKI0 #6 LES_AL-<br>TEX6 PRS_CH1 #3 |  |  |  |  |  |  |  |

| PE13      | BUSCY BUSDX<br>LCD_SEG9                                    | TIM1_CC3 #1 LE-<br>TIM0_OUT1 #4                                  | US0_TX #3 US0_CS #0<br>I2C0_SCL #6                           | LES_ALTEX7 PRS_CH2<br>#3 ACMP0_O #0<br>GPIO_EM4WU5     |  |  |  |  |  |  |  |

| PE14      | BUSDY BUSCX<br>LCD_SEG10                                   |                                                                  | US0_CTS #0 LEU0_TX<br>#2                                     |                                                        |  |  |  |  |  |  |  |

| PE15      | BUSCY BUSDX<br>LCD_SEG11                                   |                                                                  | US0_RTS #0 LEU0_RX<br>#2                                     |                                                        |  |  |  |  |  |  |  |

| PA15      | BUSAY BUSBX<br>LCD_SEG12                                   |                                                                  | US2_CLK #3                                                   |                                                        |  |  |  |  |  |  |  |

| Alternate     | LOC                                   | ATION                        |                                            |

|---------------|---------------------------------------|------------------------------|--------------------------------------------|

| Functionality | 0 - 3                                 | 4 - 7                        | Description                                |

| LES_CH4       | 0: PC4                                |                              | LESENSE channel 4.                         |

| LES_CH5       | 0: PC5                                |                              | LESENSE channel 5.                         |

| LES_CH6       | 0: PC6                                |                              | LESENSE channel 6.                         |

| LES_CH7       | 0: PC7                                |                              | LESENSE channel 7.                         |

| LES_CH8       | 0: PC8                                |                              | LESENSE channel 8.                         |

| LES_CH9       | 0: PC9                                |                              | LESENSE channel 9.                         |

| LES_CH10      | 0: PC10                               |                              | LESENSE channel 10.                        |

| LES_CH11      | 0: PC11                               |                              | LESENSE channel 11.                        |

| LES_CH12      | 0: PC12                               |                              | LESENSE channel 12.                        |

| LES_CH13      | 0: PC13                               |                              | LESENSE channel 13.                        |

| LES_CH14      | 0: PC14                               |                              | LESENSE channel 14.                        |

| LES_CH15      | 0: PC15                               |                              | LESENSE channel 15.                        |

| LETIM0_OUT0   | 0: PD6<br>1: PB11<br>2: PF0<br>3: PC4 | 4: PE12<br>5: PC14<br>6: PA8 | Low Energy Timer LETIM0, output channel 0. |

| Alternate     | LOC                        | ATION  |                                                        |

|---------------|----------------------------|--------|--------------------------------------------------------|

| Functionality | 0 - 3                      | 4 - 7  | Description                                            |

| WTIM1_CC3     | 0: PD1<br>1: PD5<br>2: PC6 | 4: PE6 | Wide timer 1 Capture Compare input / output channel 3. |

### EFM32TG11 Family Data Sheet Pin Definitions

| Port    | Bus                   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | СНО |

|---------|-----------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| VD      | VDAC0_OUT1 / OPA1_OUT |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y | BUSAY                 |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y | BUSBY                 |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3Y | BUSCY                 |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y | BUSDY                 |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

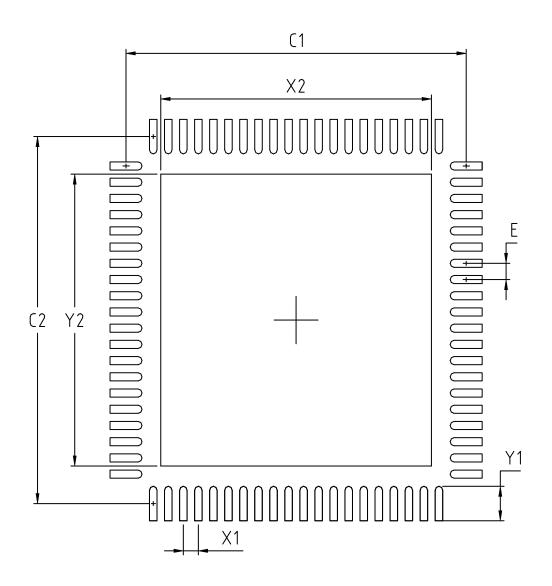

#### 7.2 QFN80 PCB Land Pattern

Figure 7.2. QFN80 PCB Land Pattern Drawing

#### Table 7.2. QFN80 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 8.90 |

| C2        | 8.90 |

| E         | 0.40 |

| X1        | 0.20 |

| Y1        | 0.85 |

| X2        | 7.30 |

| Y2        | 7.30 |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

6. The stencil thickness should be 0.125 mm (5 mils).

7. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

8. A 3x3 array of 1.45 mm square openings on a 2.00 mm pitch can be used for the center ground pad.

9. A No-Clean, Type-3 solder paste is recommended.

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

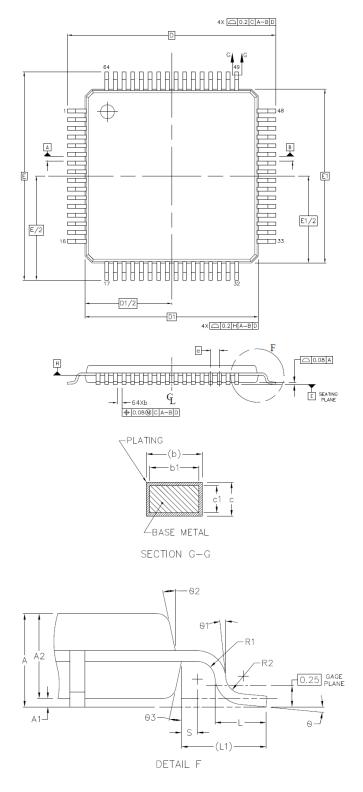

# 8. TQFP64 Package Specifications

#### 8.1 TQFP64 Package Dimensions

Figure 8.1. TQFP64 Package Drawing

| Dimension | Min       | Тур      | Мах  |  |  |  |  |  |  |  |  |  |

|-----------|-----------|----------|------|--|--|--|--|--|--|--|--|--|

| A         | 0.70      | 0.75     | 0.80 |  |  |  |  |  |  |  |  |  |

| A1        | 0.00      | —        | 0.05 |  |  |  |  |  |  |  |  |  |

| b         | 0.20      | 0.30     |      |  |  |  |  |  |  |  |  |  |

| A3        | 0.203 REF |          |      |  |  |  |  |  |  |  |  |  |

| D         |           | 9.00 BSC |      |  |  |  |  |  |  |  |  |  |

| е         | 0.50 BSC  |          |      |  |  |  |  |  |  |  |  |  |

| E         | 9.00 BSC  |          |      |  |  |  |  |  |  |  |  |  |

| D2        | 7.10      | 7.20     | 7.30 |  |  |  |  |  |  |  |  |  |

| E2        | 7.10      | 7.20     | 7.30 |  |  |  |  |  |  |  |  |  |

| L         | 0.40      | 0.45     | 0.50 |  |  |  |  |  |  |  |  |  |

| L1        | 0.00 — 0. |          |      |  |  |  |  |  |  |  |  |  |

| ааа       |           | 0.10     |      |  |  |  |  |  |  |  |  |  |

| bbb       |           | 0.10     |      |  |  |  |  |  |  |  |  |  |

| CCC       |           | 0.10     |      |  |  |  |  |  |  |  |  |  |

| ddd       |           | 0.05     |      |  |  |  |  |  |  |  |  |  |

| eee       | 0.08      |          |      |  |  |  |  |  |  |  |  |  |

| Note:     |           |          |      |  |  |  |  |  |  |  |  |  |

#### Table 9.1. QFN64 Package Dimensions

Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Figure 11.3. QFN32 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.