Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Discontinued at Digi-Key                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT        |

| Number of I/O              | 56                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                              |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b340f64gm64-a |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

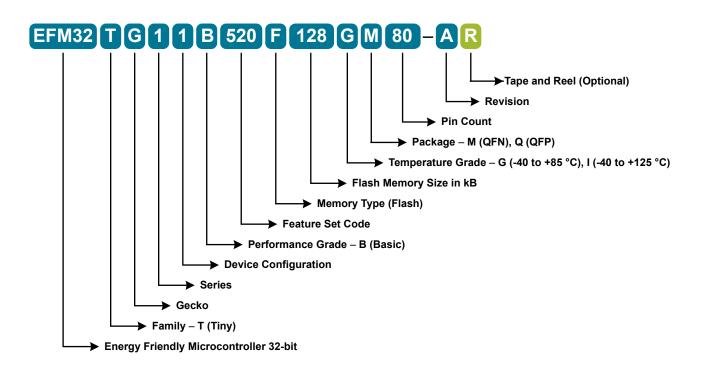

Figure 2.1. Ordering Code Key

# 3. System Overview

## 3.1 Introduction

The Tiny Gecko Series 1 product family is well suited for any battery operated application as well as other systems requiring high performance and low energy consumption. This section gives a short introduction to the MCU system. The detailed functional description can be found in the Tiny Gecko Series 1 Reference Manual. Any behavior that does not conform to the specifications in this data sheet or the functional descriptions in the Tiny Gecko Series 1 Reference Manual are detailed in the EFM32TG11 Errata document.

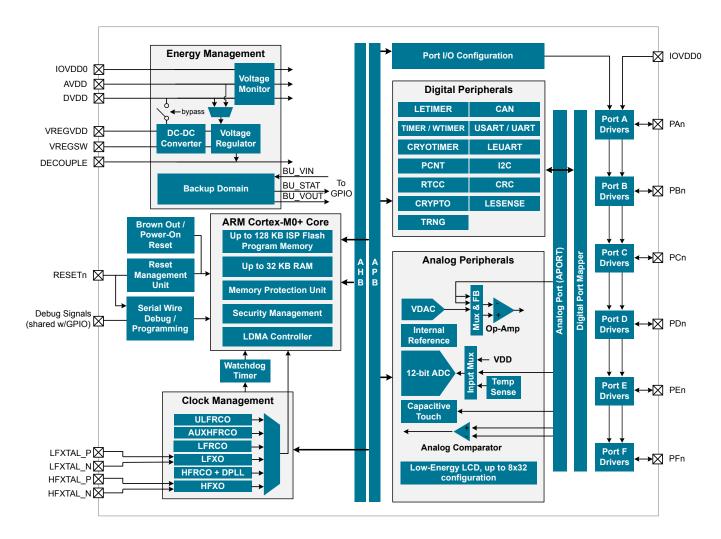

A block diagram of the Tiny Gecko Series 1 family is shown in Figure 3.1 Detailed EFM32TG11 Block Diagram on page 10. The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Detailed EFM32TG11 Block Diagram

### 3.6.5 Controller Area Network (CAN)

The CAN peripheral provides support for communication at up to 1 Mbps over CAN protocol version 2.0 part A and B. It includes 32 message objects with independent identifier masks and retains message RAM in EM2. Automatic retransmittion may be disabled in order to support Time Triggered CAN applications.

#### 3.6.6 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality such as simple logic operations (AND, OR, NOT) can be applied by the PRS to the signals. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

## 3.6.7 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface LESENSE<sup>TM</sup> is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators, ADC, and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable finite state machine which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

#### 3.7 Security Features

### 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)

The GPCRC module implements a Cyclic Redundancy Check (CRC) function. It supports both 32-bit and 16-bit polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3), while the 16-bit polynomial can be programmed to any value, depending on the needs of the application.

### 3.7.2 Crypto Accelerator (CRYPTO)

The Crypto Accelerator is a fast and energy-efficient autonomous hardware encryption and decryption accelerator. Tiny Gecko Series 1 devices support AES encryption and decryption with 128- or 256-bit keys, ECC over both GF(P) and GF(2<sup>m</sup>), and SHA-1 and SHA-2 (SHA-224 and SHA-256).

Supported block cipher modes of operation for AES include: ECB, CTR, CBC, PCBC, CFB, OFB, GCM, CBC-MAC, GMAC and CCM.

Supported ECC NIST recommended curves include P-192, P-224, P-256, K-163, K-233, B-163 and B-233.

The CRYPTO module allows fast processing of GCM (AES), ECC and SHA with little CPU intervention. CRYPTO also provides trigger signals for DMA read and write operations.

#### 3.7.3 True Random Number Generator (TRNG)

The TRNG module is a non-deterministic random number generator based on a full hardware solution. The TRNG is validated with NIST800-22 and AIS-31 test suites as well as being suitable for FIPS 140-2 certification (for the purposes of cryptographic key generation).

#### 3.7.4 Security Management Unit (SMU)

The Security Management Unit (SMU) allows software to set up fine-grained security for peripheral access, which is not possible in the Memory Protection Unit (MPU). Peripherals may be secured by hardware on an individual basis, such that only priveleged accesses to the peripheral's register interface will be allowed. When an access fault occurs, the SMU reports the specific peripheral involved and can optionally generate an interrupt.

#### 3.8 Analog

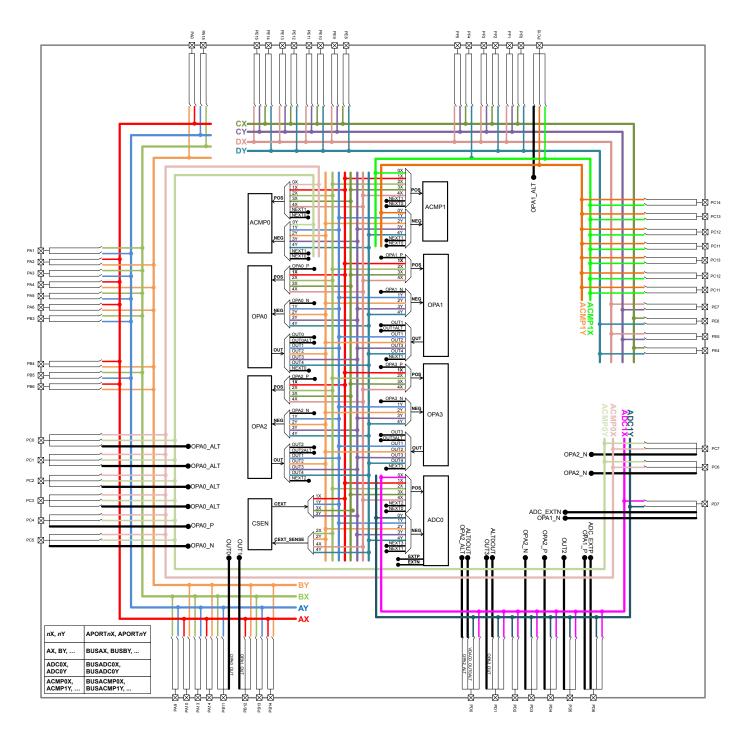

## 3.8.1 Analog Port (APORT)

The Analog Port (APORT) is an analog interconnect matrix allowing access to many analog modules on a flexible selection of pins. Each APORT bus consists of analog switches connected to a common wire. Since many clients can operate differentially, buses are grouped by X/Y pairs.

## 3.8.2 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs are selected from among internal references and external pins. The tradeoff between response time and current consumption is configurable by software. Two 6-bit reference dividers allow for a wide range of internally-programmable reference sources. The ACMP can also be used to monitor the supply voltage. An interrupt can be generated when the supply falls below or rises above the programmable threshold.

### 3.8.3 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to 1 Msps. The output sample resolution is configurable and additional resolution is possible using integrated hardware for averaging over multiple samples. The ADC includes integrated voltage references and an integrated temperature sensor. Inputs are selectable from a wide range of sources, including pins configurable as either single-ended or differential.

### 3.8.4 Capacitive Sense (CSEN)

The CSEN module is a dedicated Capacitive Sensing block for implementing touch-sensitive user interface elements such a switches and sliders. The CSEN module uses a charge ramping measurement technique, which provides robust sensing even in adverse conditions including radiated noise and moisture. The module can be configured to take measurements on a single port pin or scan through multiple pins and store results to memory through DMA. Several channels can also be shorted together to measure the combined capacitance or implement wake-on-touch from very low energy modes. Hardware includes a digital accumulator and an averaging filter, as well as digital threshold comparators to reduce software overhead.

### 3.8.5 Digital to Analog Converter (VDAC)

The Digital to Analog Converter (VDAC) can convert a digital value to an analog output voltage. The VDAC is a fully differential, 500 ksps, 12-bit converter. The opamps are used in conjunction with the VDAC, to provide output buffering. One opamp is used per singleended channel, or two opamps are used to provide differential outputs. The VDAC may be used for a number of different applications such as sensor interfaces or sound output. The VDAC can generate high-resolution analog signals while the MCU is operating at low frequencies and with low total power consumption. Using DMA and a timer, the VDAC can be used to generate waveforms without any CPU intervention. The VDAC is available in all energy modes down to and including EM3.

## 3.8.6 Operational Amplifiers

The opamps are low power amplifiers with a high degree of flexibility targeting a wide variety of standard opamp application areas, and are available down to EM3. With flexible built-in programming for gain and interconnection they can be configured to support multiple common opamp functions. All pins are also available externally for filter configurations. Each opamp has a rail to rail input and a rail to rail output. They can be used in conjunction with the VDAC module or in stand-alone configurations. The opamps save energy, PCB space, and cost as compared with standalone opamps because they are integrated on-chip.

## 3.8.7 Liquid Crystal Display Driver (LCD)

The LCD driver is capable of driving a segmented LCD display with up to 8x32 segments. A voltage boost function enables it to provide the LCD display with higher voltage than the supply voltage for the device. A patented charge redistribution driver can reduce the LCD module supply current by up to 40%. In addition, an animation feature can run custom animations on the LCD display without any CPU intervention. The LCD driver can also remain active even in Energy Mode 2 and provides a Frame Counter interrupt that can wake-up the device on a regular basis for updating data.

#### 3.9 Reset Management Unit (RMU)

The RMU is responsible for handling reset of the EFM32TG11. A wide range of reset sources are available, including several power supply monitors, pin reset, software controlled reset, core lockup reset, and watchdog reset.

# 4.1.2.1 General Operating Conditions

| Parameter                                     | Symbol                 | Test Condition                                           | Min  | Тур | Мах                  | Unit |

|-----------------------------------------------|------------------------|----------------------------------------------------------|------|-----|----------------------|------|

| Operating ambient tempera-                    | T <sub>A</sub>         | -G temperature grade                                     | -40  | 25  | 85                   | °C   |

| ture range <sup>6</sup>                       |                        | -I temperature grade                                     | -40  | 25  | 125                  | °C   |

| AVDD supply voltage <sup>2</sup>              | V <sub>AVDD</sub>      |                                                          | 1.8  | 3.3 | 3.8                  | V    |

| VREGVDD operating supply                      | Vvregvdd               | DCDC in regulation                                       | 2.4  | 3.3 | 3.8                  | V    |

| voltage <sup>2 1</sup>                        |                        | DCDC in bypass, 50mA load                                | 1.8  | 3.3 | 3.8                  | V    |

|                                               |                        | DCDC not in use. DVDD external-<br>ly shorted to VREGVDD | 1.8  | 3.3 | 3.8                  | V    |

| VREGVDD current                               | I <sub>VREGVDD</sub>   | DCDC in bypass, T ≤ 85 °C                                | _    | _   | 200                  | mA   |

|                                               |                        | DCDC in bypass, T > 85 °C                                | _    | _   | 100                  | mA   |

| DVDD operating supply volt-<br>age            | V <sub>DVDD</sub>      |                                                          | 1.62 | _   | V <sub>VREGVDD</sub> | V    |

| IOVDD operating supply volt-<br>age           | VIOVDD                 | All IOVDD pins <sup>5</sup>                              | 1.62 | _   | V <sub>VREGVDD</sub> | V    |

| DECOUPLE output capaci-<br>tor <sup>3 4</sup> | C <sub>DECOUPLE</sub>  |                                                          | 0.75 | 1.0 | 2.75                 | μF   |

| HFCORECLK frequency                           | fcore                  | VSCALE2, MODE = WS1                                      | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE2, MODE = WS0                                      | _    | _   | 25                   | MHz  |

|                                               |                        | VSCALE0, MODE = WS1                                      | _    | _   | 20                   | MHz  |

|                                               |                        | VSCALE0, MODE = WS0                                      | _    | _   | 10                   | MHz  |

| HFCLK frequency                               | f <sub>HFCLK</sub>     | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFSRCCLK frequency                            | f <sub>HFSRCCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFBUSCLK frequency                            | f <sub>HFBUSCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  |      | _   | 20                   | MHz  |

| HFPERCLK frequency                            | f <sub>HFPERCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFPERBCLK frequency                           | f <sub>HFPERBCLK</sub> | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFPERCCLK frequency                           | fHFPERCCLK             | VSCALE2                                                  | _    | —   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

|                                               |                        |                                                          |      |     |                      |      |

# Table 4.2. General Operating Conditions

## 4.1.6.3 Current Consumption 1.8 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 1.8 V. T = 25 °C. DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

## Table 4.8. Current Consumption 1.8 V without DC-DC Converter

| Parameter                                                              | Symbol                 | Test Condition                                                       | Min | Тур  | Max | Unit   |

|------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-              | I <sub>ACTIVE</sub>    | 48 MHz crystal, CPU running while loop from flash                    | _   | 45   | _   | µA/MHz |

| abled                                                                  |                        | 48 MHz HFRCO, CPU running while loop from flash                      | _   | 44   | _   | µA/MHz |

|                                                                        |                        | 48 MHz HFRCO, CPU running<br>Prime from flash                        | _   | 57   | _   | µA/MHz |

|                                                                        |                        | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash                | _   | 71   |     | µA/MHz |

|                                                                        |                        | 32 MHz HFRCO, CPU running while loop from flash                      | _   | 45   | _   | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO, CPU running while loop from flash                      | _   | 46   | _   | µA/MHz |

|                                                                        |                        | 16 MHz HFRCO, CPU running while loop from flash                      | _   | 49   | _   | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO, CPU running while loop from flash                       | —   | 158  | —   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis-           | I <sub>ACTIVE_VS</sub> | 19 MHz HFRCO, CPU running while loop from flash                      | _   | 41   | —   | µA/MHz |

| abled and voltage scaling enabled                                      |                        | 1 MHz HFRCO, CPU running while loop from flash                       | —   | 142  | _   | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1</sub>       | 48 MHz crystal                                                       | —   | 34   | _   | µA/MHz |

| mode with all peripherals disabled                                     |                        | 48 MHz HFRCO                                                         | _   | 33   | _   | µA/MHz |

|                                                                        |                        | 32 MHz HFRCO                                                         | _   | 34   | _   | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO                                                         | _   | 35   |     | µA/MHz |

|                                                                        |                        | 16 MHz HFRCO                                                         | _   | 39   |     | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO                                                          | _   | 147  |     | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1_VS</sub>    | 19 MHz HFRCO                                                         | _   | 32   |     | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled |                        | 1 MHz HFRCO                                                          | —   | 133  | —   | µA/MHz |

| Current consumption in EM2 mode, with voltage scaling                  | I <sub>EM2_VS</sub>    | Full 32 kB RAM retention and<br>RTCC running from LFXO               | _   | 1.39 | _   | μΑ     |

| enabled                                                                |                        | Full 32 kB RAM retention and<br>RTCC running from LFRCO              | _   | 1.63 | _   | μΑ     |

|                                                                        |                        | 8 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup> | _   | 1.37 | _   | μΑ     |

| Current consumption in EM3<br>mode, with voltage scaling<br>enabled    | I <sub>EM3_VS</sub>    | Full 32 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO   | _   | 1.10 | _   | μA     |

| Parameter                                                                              | Symbol               | Test Condition                                                                                          | Min | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption in EM4H mode, with voltage                                         | I <sub>EM4H_VS</sub> | 128 byte RAM retention, RTCC running from LFXO                                                          | —   | 0.75 | _   | μA   |

| scaling enabled                                                                        |                      | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO                                              | —   | 0.37 | _   | μA   |

|                                                                                        |                      | 128 byte RAM retention, no RTCC                                                                         | _   | 0.37 | _   | μA   |

| Current consumption in EM4S mode                                                       | I <sub>EM4S</sub>    | No RAM retention, no RTCC                                                                               | —   | 0.05 | _   | μA   |

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled | I <sub>PD1_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>1</sup> | _   | 0.18 | _   | μA   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled | I <sub>PD2_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>1</sup> | _   | 0.18 | _   | μA   |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.3 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

2. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

| Parameter                  | Symbol            | Test Condition                       | Min | Тур | Мах | Unit |

|----------------------------|-------------------|--------------------------------------|-----|-----|-----|------|

| Output fall time, From 70% | t <sub>IOOF</sub> | C <sub>L</sub> = 50 pF,              | —   | 1.8 | —   | ns   |

| to 30% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              |     | 4.5 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Output rise time, From 30% | t <sub>IOOR</sub> | C <sub>L</sub> = 50 pF,              |     | 2.2 |     | ns   |

| to 70% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE = 0x6 <sup>1</sup>          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              | _   | 7.4 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Note:                      | 1                 | 1                                    | 1   | 1   | 1   | 1    |

# 4.1.12 Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Мах | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | I <sub>VMON</sub>       | In EM0 or EM1, 1 supply monitored, T $\leq$ 85 °C                | _    | 6.3  | TBD | μA   |

|                                    |                         | In EM0 or EM1, 4 supplies monitored, T $\leq$ 85 °C              | —    | 12.5 | TBD | μA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshold       | —    | 62   |     | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | _    | 99   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold | —    | 99   | _   | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | —    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    | _   | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | _    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  |     | mV   |

|                                    |                         | Fine                                                             | _    | 20   | _   | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | _    | 460  | _   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  |      | 26   | _   | mV   |

# Table 4.19. Voltage Monitor (VMON)

| Parameter                                         | Symbol                | Test Condition                                             | Min | Тур   | Max | Unit   |

|---------------------------------------------------|-----------------------|------------------------------------------------------------|-----|-------|-----|--------|

| ADC clock frequency                               | f <sub>ADCCLK</sub>   |                                                            | _   | _     | 16  | MHz    |

| Throughput rate                                   | <b>f</b> ADCRATE      |                                                            | _   | _     | 1   | Msps   |

| Conversion time <sup>1</sup>                      | t <sub>ADCCONV</sub>  | 6 bit                                                      | _   | 7     | _   | cycles |

|                                                   |                       | 8 bit                                                      | _   | 9     | _   | cycles |

|                                                   |                       | 12 bit                                                     | —   | 13    | _   | cycles |

| Startup time of reference generator and ADC core  | t <sub>ADCSTART</sub> | WARMUPMODE <sup>4</sup> = NORMAL                           | —   | —     | 5   | μs     |

| generator and ADC core                            |                       | WARMUPMODE <sup>4</sup> = KEEPIN-<br>STANDBY               | _   |       | 2   | μs     |

|                                                   |                       | WARMUPMODE <sup>4</sup> = KEEPINSLO-<br>WACC               | _   |       | 1   | μs     |

| SNDR at 1Msps and f <sub>IN</sub> =<br>10kHz      | SNDR <sub>ADC</sub>   | Internal reference <sup>7</sup> , differential measurement | TBD | 67    | _   | dB     |

|                                                   |                       | External reference <sup>6</sup> , differential measurement | _   | 68    | _   | dB     |

| Spurious-free dynamic range (SFDR)                | SFDR <sub>ADC</sub>   | 1 MSamples/s, 10 kHz full-scale sine wave                  | _   | 75    | _   | dB     |

| Differential non-linearity (DNL)                  | DNL <sub>ADC</sub>    | 12 bit resolution, No missing co-<br>des                   | TBD |       | TBD | LSB    |

| Integral non-linearity (INL),<br>End point method | INL <sub>ADC</sub>    | 12 bit resolution                                          | TBD |       | TBD | LSB    |

| Offset error                                      | VADCOFFSETERR         |                                                            | TBD | 0     | TBD | LSB    |

| Gain error in ADC                                 | VADCGAIN              | Using internal reference                                   | _   | -0.2  | TBD | %      |

|                                                   |                       | Using external reference                                   | _   | -1    | _   | %      |

| Temperature sensor slope                          | V <sub>TS_SLOPE</sub> |                                                            | _   | -1.84 | _   | mV/°C  |

Note:

1. Derived from ADCCLK.

2. PSRR is referenced to AVDD when ANASW=0 and to DVDD when ANASW=1 in EMU\_PWRCTRL.

3. In ADCn\_BIASPROG register.

4. In ADCn CNTL register.

5. The absolute voltage allowed at any ADC input is dictated by the power rail supplied to on-chip circuitry, and may be lower than the effective full scale voltage. All ADC inputs are limited to the ADC supply (AVDD or DVDD depending on EMU PWRCTRL ANASW). Any ADC input routed through the APORT will further be limited by the IOVDD supply to the pin.

6. External reference is 1.25 V applied externally to ADCnEXTREFP, with the selection CONF in the SINGLECTRL\_REF or SCANCTRL\_REF register field and VREFP in the SINGLECTRLX\_VREFSEL or SCANCTRLX\_VREFSEL field. The differential input range with this configuration is ± 1.25 V.

7. Internal reference option used corresponds to selection 2V5 in the SINGLECTRL\_REF or SCANCTRL\_REF register field. The differential input range with this configuration is ± 1.25 V. Typical value is characterized using full-scale sine wave input. Minimum value is production-tested using sine wave input at 1.5 dB lower than full scale.

# 4.1.21 I2C

# 4.1.21.1 I2C Standard-mode (Sm)<sup>1</sup>

| Table 4.28. | I2C Standard-mode | (Sm) <sup>1</sup> |

|-------------|-------------------|-------------------|

|-------------|-------------------|-------------------|

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | —   | 100  | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 4.7 | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 4   | _   |      | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 250 |     |      | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD_DAT</sub> |                | 100 |     | 3450 | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 4.7 | _   | _    | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 4   |     | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 4   |     |      | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 4.7 | —   | —    | μs   |

# Note:

1. For CLHR set to 0 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Standard-mode, refer to the I2C chapter in the reference manual.

3. The maximum SDA hold time (t<sub>HD DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

# 4.1.21.3 I2C Fast-mode Plus (Fm+)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min  | Тур | Мах  | Unit |

|--------------------------------------------------|---------------------|----------------|------|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0    | —   | 1000 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 0.5  | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.26 | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 50   | _   | _    | ns   |

| SDA hold time                                    | t <sub>HD_DAT</sub> |                | 100  | —   | —    | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.26 |     |      | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.26 |     | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.26 | —   | —    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 0.5  | _   | _    | μs   |

# Table 4.30. I2C Fast-mode Plus (Fm+)<sup>1</sup>

## Note:

1. For CLHR set to 0 or 1 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Fast-mode Plus, refer to the I2C chapter in the reference manual.

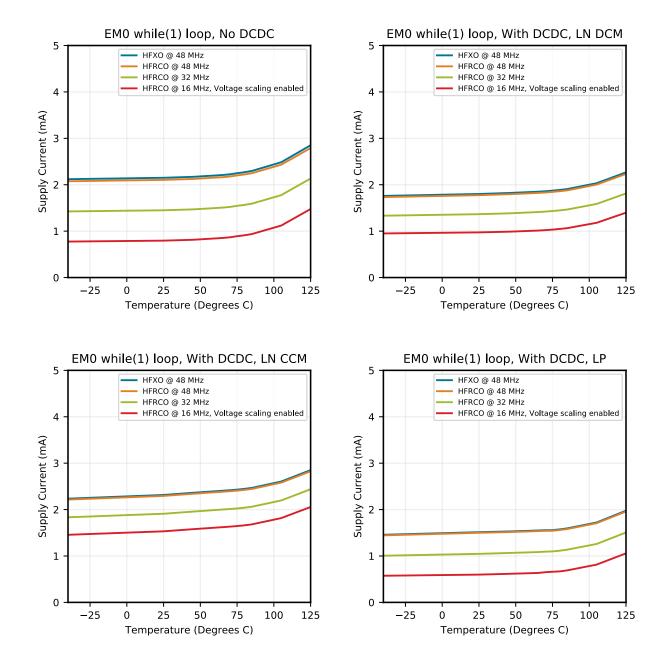

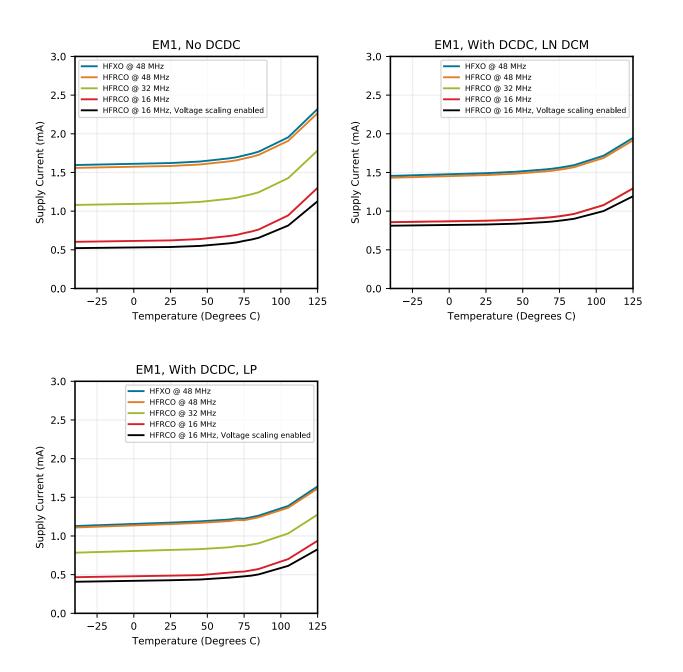

Figure 4.3. EM0 Active Mode Typical Supply Current vs. Temperature

Figure 4.4. EM1 Sleep Mode Typical Supply Current vs. Temperature

Typical supply current for EM2, EM3 and EM4H using standard software libraries from Silicon Laboratories.

| Pin Name              | Pin(s)    | Description                | Pin Name | Pin(s) | Description |

|-----------------------|-----------|----------------------------|----------|--------|-------------|

| PE15                  | 79        | GPIO                       | PA15     | 80     | GPIO        |

| Note:<br>1. GPIO with | 5V tolera | nce are indicated by (5V). |          |        | ·           |

| GPIO Name |                                                            | Pin Alternate Functi                                                               | onality / Description                                                     |                                                      |

|-----------|------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|

|           | Analog                                                     | Timers                                                                             | Communication                                                             | Other                                                |

| PD5       | BUSADC0Y BUSADC0X<br>OPA2_OUT                              | WTIM0_CDTI1 #4<br>WTIM1_CC3 #1                                                     | US1_RTS #1 U0_CTS #5<br>LEU0_RX #0 I2C1_SCL<br>#3                         |                                                      |

| PD6       | BUSADC0Y BUSADC0X<br>ADC0_EXTP<br>VDAC0_EXT OPA1_P         | TIM1_CC0 #4<br>WTIM0_CDTI2 #4<br>WTIM1_CC0 #2 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US0_RTS #5 US1_RX #2<br>US2_CTS #5 US3_CTS<br>#2 U0_RTS #5 I2C0_SDA<br>#1 | CMU_CLK2 #2 LES_AL-<br>TEX0 PRS_CH5 #2<br>ACMP0_O #2 |

| PD7       | BUSADC0Y BUSADC0X<br>ADC0_EXTN OPA1_N                      | TIM1_CC1 #4<br>WTIM1_CC1 #2 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3                   | US1_TX #2 US3_CLK #1<br>U0_TX #6 I2C0_SCL #1                              | CMU_CLK0 #2 LES_AL-<br>TEX1 ACMP1_O #2               |

| PD8       | BU_VIN                                                     | WTIM1_CC2 #2                                                                       | US2_RTS #5                                                                | CMU_CLK1 #1                                          |

| PC6       | BUSACMP0Y BU-<br>SACMP0X OPA3_P<br>LCD_SEG32               | WTIM1_CC3 #2                                                                       | US0_RTS #2 US1_CTS<br>#3 I2C0_SDA #2                                      | LES_CH6                                              |

| PC7       | BUSACMP0Y BU-<br>SACMP0X OPA3_N<br>LCD_SEG33               | WTIM1_CC0 #3                                                                       | US0_CTS #2 US1_RTS<br>#3 I2C0_SCL #2                                      | LES_CH7                                              |

| PE4       | BUSDY BUSCX<br>LCD_COM0                                    | WTIM0_CC0 #0<br>WTIM1_CC1 #4                                                       | US0_CS #1 US1_CS #5<br>US3_CS #1 U0_RX #6<br>I2C0_SDA #7                  |                                                      |

| PE5       | BUSCY BUSDX<br>LCD_COM1                                    | WTIM0_CC1 #0<br>WTIM1_CC2 #4                                                       | US0_CLK #1 US1_CLK<br>#6 US3_CTS #1<br>I2C0_SCL #7                        |                                                      |

| PE6       | BUSDY BUSCX<br>LCD_COM2                                    | WTIM0_CC2 #0<br>WTIM1_CC3 #4                                                       | US0_RX #1 US3_TX #1                                                       | PRS_CH6 #2                                           |

| PE7       | BUSCY BUSDX<br>LCD_COM3                                    | WTIM1_CC0 #5                                                                       | US0_TX #1 US3_RX #1                                                       | PRS_CH7 #2                                           |

| PC8       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG34                         |                                                                                    | US0_CS #2                                                                 | LES_CH8 PRS_CH4 #0                                   |

| PC9       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG35                         |                                                                                    | US0_CLK #2                                                                | LES_CH9 PRS_CH5 #0<br>GPIO_EM4WU2                    |

| PC10      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_RX #2                                                                 | LES_CH10                                             |

| PC11      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_TX #2 I2C1_SDA #4                                                     | LES_CH11                                             |

| PC12      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0 BU-<br>SACMP1Y BUSACMP1X | TIM1_CC3 #0                                                                        | US0_RTS #3 US1_CTS<br>#4 US2_CTS #4 U0_RTS<br>#3                          | CMU_CLK0 #1<br>LES_CH12                              |

| PC13      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #1 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI0 #1<br>TIM1_CC0 #0 TIM1_CC2<br>#4 PCNT0_S0IN #0                          | US0_CTS #3 US1_RTS<br>#4 US2_RTS #4 U0_CTS<br>#3                          | LES_CH13                                             |

| PC14      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI1 #1<br>TIM1_CC1 #0 TIM1_CC3<br>#4 LETIM0_OUT0 #5<br>PCNT0_S1IN #0        | US0_CS #3 US1_CS #3<br>US2_RTS #3 US3_CS #2<br>U0_TX #3 LEU0_TX #5        | LES_CH14 PRS_CH0 #2                                  |

| Alternate     | LOCATION                    |                                       |                                                                                                                                                                                                                                |

|---------------|-----------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                       | 4 - 7                                 | Description                                                                                                                                                                                                                    |

| GPIO_EM4WU4   | 0: PF2                      |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU5   | 0: PE13                     |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU6   | 0: PC4                      |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU7   | 0: PB11                     |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| GPIO_EM4WU9   | 0: PE10                     |                                       | Pin can be used to wake the system up from EM4                                                                                                                                                                                 |

| HFXTAL_N      | 0: PB14                     |                                       | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                                                                           |

| HFXTAL_P      | 0: PB13                     |                                       | High Frequency Crystal positive pin.                                                                                                                                                                                           |

| I2C0_SCL      | 0: PA1<br>1: PD7<br>2: PC7  | 4: PC1<br>5: PF1<br>6: PE13<br>7: PE5 | I2C0 Serial Clock Line input / output.                                                                                                                                                                                         |

| I2C0_SDA      | 0: PA0<br>1: PD6<br>2: PC6  | 4: PC0<br>5: PF0<br>6: PE12<br>7: PE4 | I2C0 Serial Data input / output.                                                                                                                                                                                               |

| I2C1_SCL      | 0: PC5<br>1: PB12<br>3: PD5 | 4: PF2                                | I2C1 Serial Clock Line input / output.                                                                                                                                                                                         |

| I2C1_SDA      | 0: PC4<br>1: PB11<br>3: PD4 | 4: PC11                               | I2C1 Serial Data input / output.                                                                                                                                                                                               |

|               | 0: PA14                     |                                       | LCD external supply bypass in step down or charge pump mode. If using the LCD in step-down or charge pump mode, a 1 uF (minimum) capacitor between this pin and VSS is required.                                               |

| LCD_BEXT      |                             |                                       | To reduce supply ripple, a larger capcitor of approximately 1000 times the total LCD segment capacitance may be used.<br>If using the LCD with the internal supply source, this pin may be left unconnected or used as a GPIO. |

| Alternate     | LOCATION                              |                              |                                            |

|---------------|---------------------------------------|------------------------------|--------------------------------------------|

| Functionality | 0 - 3                                 | 4 - 7                        | Description                                |

| LES_CH4       | 0: PC4                                |                              | LESENSE channel 4.                         |

| LES_CH5       | 0: PC5                                |                              | LESENSE channel 5.                         |

| LES_CH6       | 0: PC6                                |                              | LESENSE channel 6.                         |

| LES_CH7       | 0: PC7                                |                              | LESENSE channel 7.                         |

| LES_CH8       | 0: PC8                                |                              | LESENSE channel 8.                         |

| LES_CH9       | 0: PC9                                |                              | LESENSE channel 9.                         |

| LES_CH10      | 0: PC10                               |                              | LESENSE channel 10.                        |

| LES_CH11      | 0: PC11                               |                              | LESENSE channel 11.                        |

| LES_CH12      | 0: PC12                               |                              | LESENSE channel 12.                        |

| LES_CH13      | 0: PC13                               |                              | LESENSE channel 13.                        |

| LES_CH14      | 0: PC14                               |                              | LESENSE channel 14.                        |

| LES_CH15      | 0: PC15                               |                              | LESENSE channel 15.                        |

| LETIM0_OUT0   | 0: PD6<br>1: PB11<br>2: PF0<br>3: PC4 | 4: PE12<br>5: PC14<br>6: PA8 | Low Energy Timer LETIM0, output channel 0. |

## 5.16 Analog Port (APORT) Client Maps

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. Figure 5.14 APORT Connection Diagram on page 119 shows the APORT routing for this device family (note that available features may vary by part number). A complete description of APORT functionality can be found in the Reference Manual.

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin

Figure 9.3. QFN64 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.