#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Discontinued at Digi-Key                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 53                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b340f64im64-ar |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.10 Core and Memory

### 3.10.1 Processor Core

The ARM Cortex-M processor includes a 32-bit RISC processor integrating the following features and tasks in the system:

- ARM Cortex-M0+ RISC processor

- Memory Protection Unit (MPU) supporting up to 8 memory segments

- Micro-Trace Buffer (MTB)

- Up to 128 kB flash program memory

- · Up to 32 kB RAM data memory

- · Configuration and event handling of all modules

- · 2-pin Serial-Wire debug interface

### 3.10.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block, whereas the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

### 3.10.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling so-phisticated operations to be implemented.

#### 3.10.4 Bootloader

All devices come pre-programmed with a UART bootloader. This bootloader resides in flash and can be erased if it is not needed. More information about the bootloader protocol and usage can be found in *AN0003: UART Bootloader*. Application notes can be found on the Silicon Labs website (www.silabs.com/32bit-appnotes) or within Simplicity Studio in the [**Documentation**] area.

# 4.1.2.1 General Operating Conditions

| Parameter                                     | Symbol                 | Test Condition                                           | Min  | Тур | Мах                  | Unit |

|-----------------------------------------------|------------------------|----------------------------------------------------------|------|-----|----------------------|------|

| Operating ambient tempera-                    | T <sub>A</sub>         | -G temperature grade                                     | -40  | 25  | 85                   | °C   |

| ture range <sup>6</sup>                       |                        | -I temperature grade                                     | -40  | 25  | 125                  | °C   |

| AVDD supply voltage <sup>2</sup>              | V <sub>AVDD</sub>      |                                                          | 1.8  | 3.3 | 3.8                  | V    |

| VREGVDD operating supply                      | V <sub>VREGVDD</sub>   | DCDC in regulation                                       | 2.4  | 3.3 | 3.8                  | V    |

| voltage <sup>2 1</sup>                        |                        | DCDC in bypass, 50mA load                                | 1.8  | 3.3 | 3.8                  | V    |

|                                               |                        | DCDC not in use. DVDD external-<br>ly shorted to VREGVDD | 1.8  | 3.3 | 3.8                  | V    |

| VREGVDD current                               | I <sub>VREGVDD</sub>   | DCDC in bypass, T ≤ 85 °C                                | _    | _   | 200                  | mA   |

|                                               |                        | DCDC in bypass, T > 85 °C                                | _    | _   | 100                  | mA   |

| DVDD operating supply volt-<br>age            | V <sub>DVDD</sub>      |                                                          | 1.62 | _   | V <sub>VREGVDD</sub> | V    |

| IOVDD operating supply volt-<br>age           | VIOVDD                 | All IOVDD pins <sup>5</sup>                              | 1.62 | _   | V <sub>VREGVDD</sub> | V    |

| DECOUPLE output capaci-<br>tor <sup>3 4</sup> | C <sub>DECOUPLE</sub>  |                                                          | 0.75 | 1.0 | 2.75                 | μF   |

| HFCORECLK frequency                           | f <sub>CORE</sub>      | VSCALE2, MODE = WS1                                      | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE2, MODE = WS0                                      | _    | _   | 25                   | MHz  |

|                                               |                        | VSCALE0, MODE = WS1                                      | _    | _   | 20                   | MHz  |

|                                               |                        | VSCALE0, MODE = WS0                                      | _    | _   | 10                   | MHz  |

| HFCLK frequency                               | f <sub>HFCLK</sub>     | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFSRCCLK frequency                            | f <sub>HFSRCCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFBUSCLK frequency                            | f <sub>HFBUSCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  |      | _   | 20                   | MHz  |

| HFPERCLK frequency                            | f <sub>HFPERCLK</sub>  | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFPERBCLK frequency                           | f <sub>HFPERBCLK</sub> | VSCALE2                                                  | _    | _   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

| HFPERCCLK frequency                           | fHFPERCCLK             | VSCALE2                                                  | _    | —   | 48                   | MHz  |

|                                               |                        | VSCALE0                                                  | _    | _   | 20                   | MHz  |

|                                               |                        |                                                          |      |     |                      |      |

# Table 4.2. General Operating Conditions

### 4.1.5 Backup Supply Domain

| Parameter                                                   | Symbol               | Test Condition                                  | Min | Тур  | Max | Unit |

|-------------------------------------------------------------|----------------------|-------------------------------------------------|-----|------|-----|------|

| Backup supply voltage range                                 | V <sub>BU_VIN</sub>  |                                                 | TBD | —    | 3.8 | V    |

| PWRRES resistor                                             | R <sub>PWRRES</sub>  | EMU_BUCTRL_PWRRES =<br>RES0                     | TBD | 3900 | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES1                     | TBD | 1800 | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES2                     | TBD | 1330 | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES3                     | TBD | 815  | TBD | Ω    |

| Output impedance between<br>BU_VIN and BU_VOUT <sup>2</sup> | R <sub>BU_VOUT</sub> | EMU_BUCTRL_VOUTRES =<br>STRONG                  | TBD | 110  | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_VOUTRES =<br>MED                     | TBD | 775  | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_VOUTRES =<br>WEAK                    | TBD | 6500 | TBD | Ω    |

| Supply current                                              | I <sub>BU_VIN</sub>  | BU_VIN not powering backup do-<br>main          | _   | 10   | TBD | nA   |

|                                                             |                      | BU_VIN powering backup do-<br>main <sup>1</sup> |     | 450  | TBD | nA   |

### Table 4.5. Backup Supply Domain

# Note:

1. Additional current required by backup circuitry when backup is active. Includes supply current of backup switches and backup regulator. Does not include supply current required for backed-up circuitry.

2. BU\_VOUT and BU\_STAT signals are not available in all package configurations. Check the device pinout for availability.

### 4.1.6.2 Current Consumption 3.3 V using DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = IOVDD = 3.3 V, DVDD = 1.8 V DC-DC output. T = 25 °C. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

| Parameter                                                    | Symbol                  | Test Condition                                        | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------|-------------------------|-------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>mode with all peripherals dis- | IACTIVE_DCM             | 48 MHz crystal, CPU running while loop from flash     | _   | 38   | -   | µA/MHz |

| abled, DCDC in Low Noise<br>DCM mode <sup>2</sup>            |                         | 48 MHz HFRCO, CPU running while loop from flash       | _   | 37   | _   | µA/MHz |

|                                                              |                         | 48 MHz HFRCO, CPU running<br>Prime from flash         | _   | 45   | _   | µA/MHz |

|                                                              |                         | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash | _   | 53   | _   | µA/MHz |

|                                                              |                         | 32 MHz HFRCO, CPU running while loop from flash       | _   | 43   | _   | µA/MHz |

|                                                              |                         | 26 MHz HFRCO, CPU running while loop from flash       |     | 47   | _   | µA/MHz |

|                                                              |                         | 16 MHz HFRCO, CPU running while loop from flash       |     | 61   | _   | µA/MHz |

|                                                              |                         | 1 MHz HFRCO, CPU running while loop from flash        |     | 587  | _   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis- | I <sub>ACTIVE_CCM</sub> | 48 MHz crystal, CPU running while loop from flash     | _   | 49   | _   | µA/MHz |

| abled, DCDC in Low Noise<br>CCM mode <sup>1</sup>            |                         | 48 MHz HFRCO, CPU running while loop from flash       |     | 48   | _   | µA/MHz |

|                                                              |                         | 48 MHz HFRCO, CPU running<br>Prime from flash         | _   | 55   | _   | µA/MHz |

|                                                              |                         | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash |     | 63   | _   | µA/MHz |

|                                                              |                         | 32 MHz HFRCO, CPU running while loop from flash       |     | 60   | _   | µA/MHz |

|                                                              |                         | 26 MHz HFRCO, CPU running while loop from flash       |     | 68   | _   | µA/MHz |

|                                                              |                         | 16 MHz HFRCO, CPU running while loop from flash       |     | 96   | _   | µA/MHz |

|                                                              |                         | 1 MHz HFRCO, CPU running while loop from flash        |     | 1157 | _   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis- | I <sub>ACTIVE_LPM</sub> | 32 MHz HFRCO, CPU running while loop from flash       | _   | 32   | _   | µA/MHz |

| abled, DCDC in LP mode <sup>3</sup>                          |                         | 26 MHz HFRCO, CPU running while loop from flash       |     | 33   | _   | µA/MHz |

|                                                              |                         | 16 MHz HFRCO, CPU running while loop from flash       |     | 36   | _   | µA/MHz |

|                                                              |                         | 1 MHz HFRCO, CPU running while loop from flash        | _   | 156  | _   | µA/MHz |

| Parameter                              | Symbol                    | Test Condition                                                                      | Min | Тур | Max | Unit  |

|----------------------------------------|---------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Frequency accuracy                     | f <sub>HFRCO_ACC</sub>    | At production calibrated frequen-<br>cies, across supply voltage and<br>temperature | TBD | _   | TBD | %     |

| Start-up time                          | t <sub>HFRCO</sub>        | f <sub>HFRCO</sub> ≥ 19 MHz                                                         | _   | 300 | —   | ns    |

|                                        |                           | 4 < f <sub>HFRCO</sub> < 19 MHz                                                     | _   | 1   | —   | μs    |

|                                        |                           | f <sub>HFRCO</sub> ≤ 4 MHz                                                          | _   | 2.5 | _   | μs    |

| Current consumption on all             | I <sub>HFRCO</sub>        | f <sub>HFRCO</sub> = 48 MHz                                                         |     | 258 | TBD | μA    |

| supplies                               |                           | f <sub>HFRCO</sub> = 38 MHz                                                         | _   | 218 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 32 MHz                                                         |     | 182 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 26 MHz                                                         |     | 156 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 19 MHz                                                         |     | 130 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 16 MHz                                                         |     | 112 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 13 MHz                                                         |     | 101 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 7 MHz                                                          |     | 80  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 4 MHz                                                          |     | 29  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 2 MHz                                                          |     | 26  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 1 MHz                                                          |     | 24  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 40 MHz, DPLL enabled                                           |     | 393 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 32 MHz, DPLL enabled                                           |     | 313 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 16 MHz, DPLL enabled                                           |     | 180 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 4 MHz, DPLL enabled                                            |     | 46  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 1 MHz, DPLL enabled                                            |     | 33  | TBD | μA    |

| Coarse trim step size (% of period)    | SS <sub>HFRCO_COARS</sub> |                                                                                     |     | 0.8 | _   | %     |

| Fine trim step size (% of pe-<br>riod) | SS <sub>HFRCO_FINE</sub>  |                                                                                     |     | 0.1 | -   | %     |

| Period jitter                          | PJ <sub>HFRCO</sub>       |                                                                                     |     | 0.2 | _   | % RMS |

# Table 4.14. High-Frequency RC Oscillator (HFRCO)

# 4.1.21.2 I2C Fast-mode (Fm)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Мах | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|-----|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | _   | 400 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 1.3 | —   | _   | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.6 | —   | _   | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 100 | _   | _   | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD_DAT</sub> |                | 100 | —   | 900 | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.6 | _   | _   | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.6 |     |     | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.6 | _   |     | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 1.3 | _   | —   | μs   |

# Table 4.29. I2C Fast-mode (Fm)<sup>1</sup>

Note:

1. For CLHR set to 1 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Fast-mode, refer to the I2C chapter in the reference manual.

3. The maximum SDA hold time (t<sub>HD,DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

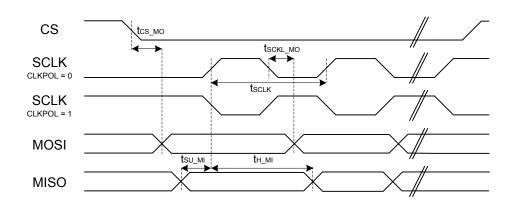

# 4.1.22 USART SPI

# **SPI Master Timing**

# Table 4.31. SPI Master Timing

| Parameter                      | Symbol               | Test Condition | Min                          | Тур | Мах  | Unit |

|--------------------------------|----------------------|----------------|------------------------------|-----|------|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>    |                | 2 *<br><sup>t</sup> HFPERCLK | —   | _    | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub>   |                | -19.8                        | _   | 18.9 | ns   |

| SCLK to MOSI <sup>1 3</sup>    | t <sub>SCLK_MO</sub> |                | -10                          | _   | 14.5 | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>su_мi</sub>   | IOVDD = 1.62 V | 75                           | _   | _    | ns   |

|                                |                      | IOVDD = 3.0 V  | 40                           | —   | _    | ns   |

| MISO hold time <sup>1 3</sup>  | t <sub>H_MI</sub>    |                | -10                          | _   | _    | ns   |

# Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

2. t<sub>HFPERCLK</sub> is one period of the selected HFPERCLK.

3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $V_{\text{DD}}$ ).

Figure 4.1. SPI Master Timing Diagram

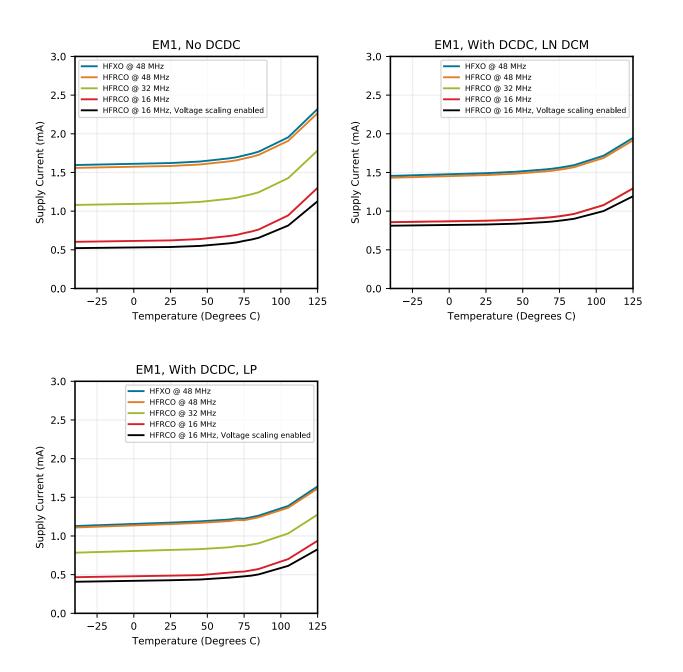

Figure 4.4. EM1 Sleep Mode Typical Supply Current vs. Temperature

Typical supply current for EM2, EM3 and EM4H using standard software libraries from Silicon Laboratories.

| Pin Name | Pin(s) | Description                                                                                              | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|----------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                                                                                                     | PC5      | 14       | GPIO                                                                                                                                                                                                        |

| PB7      | 15     | GPIO                                                                                                     | PB8      | 16       | GPIO                                                                                                                                                                                                        |

| PA8      | 17     | GPIO                                                                                                     | PA9      | 18       | GPIO                                                                                                                                                                                                        |

| PA10     | 19     | GPIO                                                                                                     | RESETn   | 20       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21     | GPIO                                                                                                     | AVDD     | 23<br>27 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 24     | GPIO                                                                                                     | PB14     | 25       | GPIO                                                                                                                                                                                                        |

| PD0      | 28     | GPIO (5V)                                                                                                | PD1      | 29       | GPIO                                                                                                                                                                                                        |

| PD2      | 30     | GPIO (5V)                                                                                                | PD3      | 31       | GPIO                                                                                                                                                                                                        |

| PD4      | 32     | GPIO                                                                                                     | PD5      | 33       | GPIO                                                                                                                                                                                                        |

| PD6      | 34     | GPIO                                                                                                     | PD7      | 35       | GPIO                                                                                                                                                                                                        |

| PD8      | 36     | GPIO                                                                                                     | PC6      | 37       | GPIO                                                                                                                                                                                                        |

| PC7      | 38     | GPIO                                                                                                     | DVDD     | 39       | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PC8      | 41       | GPIO                                                                                                                                                                                                        |

| PC9      | 42     | GPIO                                                                                                     | PC10     | 43       | GPIO (5V)                                                                                                                                                                                                   |

| PC11     | 44     | GPIO (5V)                                                                                                | PC12     | 45       | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 46     | GPIO (5V)                                                                                                | PC14     | 47       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 48     | GPIO (5V)                                                                                                | PF0      | 49       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50     | GPIO (5V)                                                                                                | PF2      | 51       | GPIO                                                                                                                                                                                                        |

| PF3      | 52     | GPIO                                                                                                     | PF4      | 53       | GPIO                                                                                                                                                                                                        |

| PF5      | 54     | GPIO                                                                                                     | PE8      | 57       | GPIO                                                                                                                                                                                                        |

| PE9      | 58     | GPIO                                                                                                     | PE10     | 59       | GPIO                                                                                                                                                                                                        |

| PE11     | 60     | GPIO                                                                                                     | PE12     | 61       | GPIO                                                                                                                                                                                                        |

| PE13     | 62     | GPIO                                                                                                     | PE14     | 63       | GPIO                                                                                                                                                                                                        |

| PE15     | 64     | GPIO                                                                                                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s)   | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB4      | 10       | GPIO                          | PB5      | 11     | GPIO                                                                                                                                                                                                        |

| PB6      | 12       | GPIO                          | PC4      | 13     | GPIO                                                                                                                                                                                                        |

| PC5      | 14       | GPIO                          | PB7      | 15     | GPIO                                                                                                                                                                                                        |

| PB8      | 16       | GPIO                          | PA8      | 17     | GPIO                                                                                                                                                                                                        |

| PA12     | 18       | GPIO                          | PA13     | 19     | GPIO (5V)                                                                                                                                                                                                   |

| PA14     | 20       | GPIO                          | RESETn   | 21     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 22       | GPIO                          | PB12     | 23     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.          | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26       | GPIO                          | PD0      | 29     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 30       | GPIO                          | PD3      | 31     | GPIO                                                                                                                                                                                                        |

| PD4      | 32       | GPIO                          | PD5      | 33     | GPIO                                                                                                                                                                                                        |

| PD6      | 34       | GPIO                          | PD7      | 35     | GPIO                                                                                                                                                                                                        |

| PD8      | 36       | GPIO                          | PC7      | 37     | GPIO                                                                                                                                                                                                        |

| VREGSW   | 39       | DCDC regulator switching node | VREGVDD  | 40     | Voltage regulator VDD input                                                                                                                                                                                 |

| DVDD     | 41       | Digital power supply.         | DECOUPLE | 42     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PE4      | 43       | GPIO                          | PE5      | 44     | GPIO                                                                                                                                                                                                        |

| PE6      | 45       | GPIO                          | PE7      | 46     | GPIO                                                                                                                                                                                                        |

| PC12     | 47       | GPIO (5V)                     | PC13     | 48     | GPIO (5V)                                                                                                                                                                                                   |

| PF0      | 49       | GPIO (5V)                     | PF1      | 50     | GPIO (5V)                                                                                                                                                                                                   |

| PF2      | 51       | GPIO                          | PF3      | 52     | GPIO                                                                                                                                                                                                        |

| PF4      | 53       | GPIO                          | PF5      | 54     | GPIO                                                                                                                                                                                                        |

| PE8      | 56       | GPIO                          | PE9      | 57     | GPIO                                                                                                                                                                                                        |

| PE10     | 58       | GPIO                          | PE11     | 59     | GPIO                                                                                                                                                                                                        |

| PE12     | 60       | GPIO                          | PE13     | 61     | GPIO                                                                                                                                                                                                        |

| PE14     | 62       | GPIO                          | PE15     | 63     | GPIO                                                                                                                                                                                                        |

| PA15     | 64       | GPIO                          |          |        |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

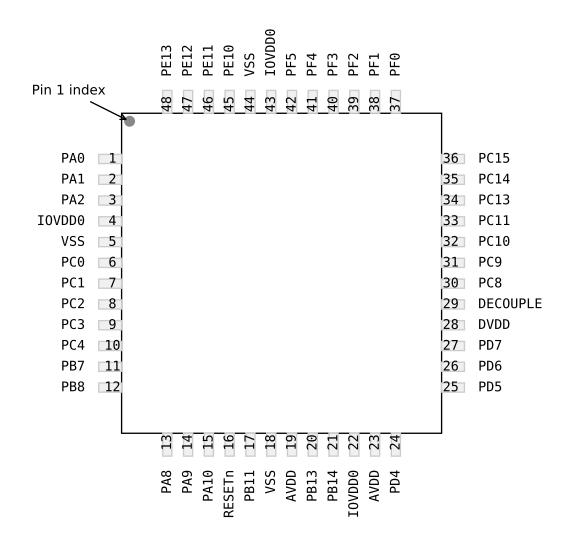

### Figure 5.11. EFM32TG11B1xx in QFP48 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.11. E | EFM32TG11B1xx in | QFP48 | Device Pinout |

|---------------|------------------|-------|---------------|

|---------------|------------------|-------|---------------|

| Pin Name | Pin(s)        | Description | Pin Name | Pin(s)        | Description                |

|----------|---------------|-------------|----------|---------------|----------------------------|

| PA0      | 1             | GPIO        | PA1      | 2             | GPIO                       |

| PA2      | 3             | GPIO        | IOVDD0   | 4<br>22<br>43 | Digital IO power supply 0. |

| VSS      | 5<br>18<br>44 | Ground      | PC0      | 6             | GPIO (5V)                  |

| PC1      | 7             | GPIO (5V)   | PC2      | 8             | GPIO (5V)                  |

| PC3      | 9             | GPIO (5V)   | PC4      | 10            | GPIO                       |

| Alternate     | LOC                                    | OCATION                      |                                                                                                                    |  |  |  |  |  |  |  |

|---------------|----------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Functionality | 0 - 3                                  | 4 - 7                        | Description                                                                                                        |  |  |  |  |  |  |  |

| LETIM0_OUT1   | 0: PD7<br>1: PB12<br>2: PF1<br>3: PC5  | 4: PE13<br>5: PC15<br>6: PA9 | Low Energy Timer LETIM0, output channel 1.                                                                         |  |  |  |  |  |  |  |

| LEU0_RX       | 0: PD5<br>1: PB14<br>2: PE15<br>3: PF1 | 4: PA0<br>5: PC15            | LEUART0 Receive input.                                                                                             |  |  |  |  |  |  |  |

| LEU0_TX       | 0: PD4<br>1: PB13<br>2: PE14<br>3: PF0 | 4: PF2<br>5: PC14            | LEUART0 Transmit output. Also used as receive input in half duplex communication.                                  |  |  |  |  |  |  |  |

| LFXTAL_N      | 0: PB8                                 |                              | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional ex-<br>ternal clock input pin. |  |  |  |  |  |  |  |

| LFXTAL_P      | 0: PB7                                 |                              | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                         |  |  |  |  |  |  |  |

| OPA0_N        | 0: PC5                                 |                              | Operational Amplifier 0 external negative input.                                                                   |  |  |  |  |  |  |  |

| OPA0_P        | 0: PC4                                 |                              | Operational Amplifier 0 external positive input.                                                                   |  |  |  |  |  |  |  |

| OPA1_N        | 0: PD7                                 |                              | Operational Amplifier 1 external negative input.                                                                   |  |  |  |  |  |  |  |

| OPA1_P        | 0: PD6                                 |                              | Operational Amplifier 1 external positive input.                                                                   |  |  |  |  |  |  |  |

| OPA2_N        | 0: PD3                                 |                              | Operational Amplifier 2 external negative input.                                                                   |  |  |  |  |  |  |  |

| OPA2_OUT      | 0: PD5                                 |                              | Operational Amplifier 2 output.                                                                                    |  |  |  |  |  |  |  |

| OPA2_OUTALT   | 0: PD0                                 |                              | Operational Amplifier 2 alternative output.                                                                        |  |  |  |  |  |  |  |

| OPA2_P        | 0: PD4                                 |                              | Operational Amplifier 2 external positive input.                                                                   |  |  |  |  |  |  |  |

| Alternate                      | LOCA                                     | ATION                       |                                                                    |

|--------------------------------|------------------------------------------|-----------------------------|--------------------------------------------------------------------|

| Functionality                  | 0 - 3                                    | 4 - 7                       | Description                                                        |

| VDAC0_OUT0 /<br>OPA0_OUT       | 0: PB11                                  |                             | Digital to Analog Converter DAC0 output channel number 0.          |

| VDAC0_OUT0ALT<br>/ OPA0_OUTALT | 0: PC0<br>1: PC1<br>2: PC2<br>3: PC3     | 4: PD0                      | Digital to Analog Converter DAC0 alternative output for channel 0. |

| VDAC0_OUT1 /<br>OPA1_OUT       | 0: PB12                                  |                             | Digital to Analog Converter DAC0 output channel number 1.          |

| VDAC0_OUT1ALT<br>/ OPA1_OUTALT | 0: PC12<br>1: PC13<br>2: PC14<br>3: PC15 | 4: PD1                      | Digital to Analog Converter DAC0 alternative output for channel 1. |

| WTIM0_CC0                      | 0: PE4<br>1: PA6                         | 4: PC15<br>6: PB3<br>7: PC1 | Wide timer 0 Capture Compare input / output channel 0.             |

| WTIM0_CC1                      | 0: PE5                                   | 4: PF0<br>6: PB4<br>7: PC2  | Wide timer 0 Capture Compare input / output channel 1.             |

| WTIM0_CC2                      | 0: PE6                                   | 4: PF1<br>6: PB5<br>7: PC3  | Wide timer 0 Capture Compare input / output channel 2.             |

| WTIM0_CDTI0                    | 0: PE10<br>2: PA12                       | 4: PD4                      | Wide timer 0 Complimentary Dead Time Insertion channel 0.          |

| WTIM0_CDTI1                    | 0: PE11<br>2: PA13                       | 4: PD5                      | Wide timer 0 Complimentary Dead Time Insertion channel 1.          |

| WTIM0_CDTI2                    | 0: PE12<br>2: PA14                       | 4: PD6                      | Wide timer 0 Complimentary Dead Time Insertion channel 2.          |

| WTIM1_CC0                      | 0: PB13<br>1: PD2<br>2: PD6<br>3: PC7    | 5: PE7                      | Wide timer 1 Capture Compare input / output channel 0.             |

| WTIM1_CC1                      | 0: PB14<br>1: PD3<br>2: PD7              | 4: PE4                      | Wide timer 1 Capture Compare input / output channel 1.             |

| WTIM1_CC2                      | 0: PD0<br>1: PD4<br>2: PD8               | 4: PE5                      | Wide timer 1 Capture Compare input / output channel 2.             |

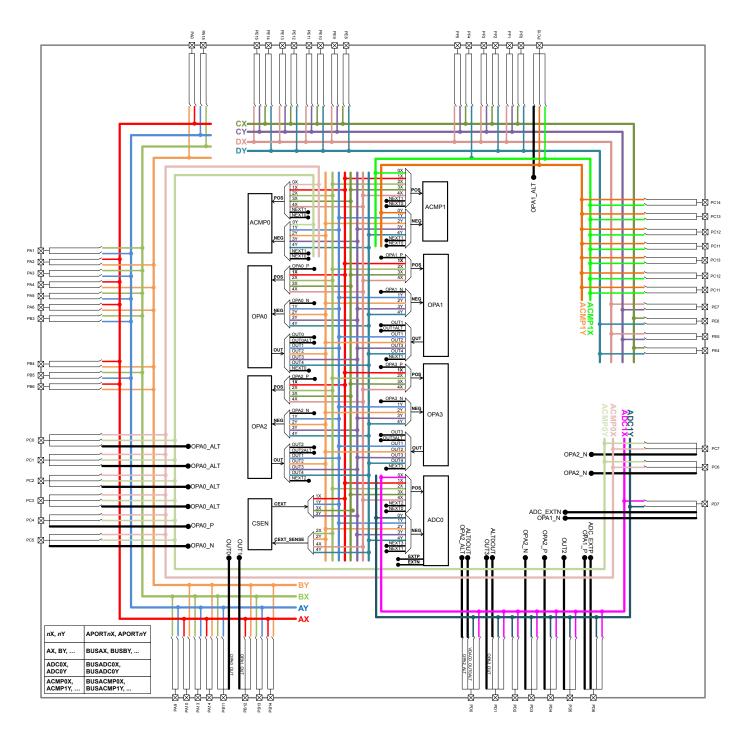

### 5.16 Analog Port (APORT) Client Maps

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. Figure 5.14 APORT Connection Diagram on page 119 shows the APORT routing for this device family (note that available features may vary by part number). A complete description of APORT functionality can be found in the Reference Manual.

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin

| Port           | Bus       | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СН9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | СНО |

|----------------|-----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| <b>APORT0X</b> | BUSACMP0X |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PCO |

| <b>APORT0Y</b> | BUSACMP0Y |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PCO |

| APORT1X        | BUSAX     |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT1Y        | BUSAY     |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2X        | BUSBX     |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY     |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3X        | BUSCX     |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| APORT3Y        | BUSCY     |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4X        | BUSDX     |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY     |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

PF7 is available on port APORT2X as CH23, the register field enumeration to connect to PF7 would be APORT2XCH23. The shared bus used by this connection is indicated in the Bus column.

# Table 5.16. ACMP0 Bus and Pin Mapping

| Dimension | Min       | Тур       | Мах  |  |  |  |  |  |  |  |  |

|-----------|-----------|-----------|------|--|--|--|--|--|--|--|--|

| A         | _         | _         | 1.20 |  |  |  |  |  |  |  |  |

| A1        | 0.05      | —         | 0.15 |  |  |  |  |  |  |  |  |

| A2        | 0.95      | 1.00      | 1.05 |  |  |  |  |  |  |  |  |

| b         | 0.17      | 0.20      | 0.27 |  |  |  |  |  |  |  |  |

| с         | 0.09      | —         | 0.20 |  |  |  |  |  |  |  |  |

| D         |           | 14.00 BSC |      |  |  |  |  |  |  |  |  |

| D1        |           | 12.00 BSC |      |  |  |  |  |  |  |  |  |

| е         | 0.50 BSC  |           |      |  |  |  |  |  |  |  |  |

| E         | 14.00 BSC |           |      |  |  |  |  |  |  |  |  |

| E1        |           | 12.00 BSC |      |  |  |  |  |  |  |  |  |

| L         | 0.45      | 0.60      | 0.75 |  |  |  |  |  |  |  |  |

| L1        |           | 1.00 REF  |      |  |  |  |  |  |  |  |  |

| θ         | 0 3.5 7   |           |      |  |  |  |  |  |  |  |  |

| ааа       |           | 0.20      |      |  |  |  |  |  |  |  |  |

| bbb       |           | 0.20      |      |  |  |  |  |  |  |  |  |

| ссс       |           | 0.08      |      |  |  |  |  |  |  |  |  |

| ddd       |           | 0.08      |      |  |  |  |  |  |  |  |  |

| eee       | 0.05      |           |      |  |  |  |  |  |  |  |  |

| Note:     |           |           |      |  |  |  |  |  |  |  |  |

### Table 6.1. TQFP80 Package Dimensions

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This package outline conforms to JEDEC MS-026, variant ADD.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

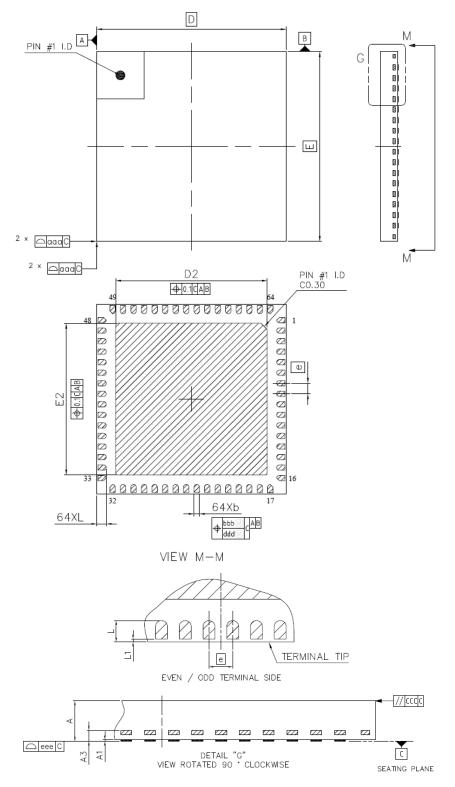

# 9. QFN64 Package Specifications

### 9.1 QFN64 Package Dimensions

Figure 9.1. QFN64 Package Drawing

### Table 9.2. QFN64 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 8.90 |

| C2        | 8.90 |

| E         | 0.50 |

| X1        | 0.30 |

| Y1        | 0.85 |

| X2        | 7.30 |

| Y2        | 7.30 |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

6. The stencil thickness should be 0.125 mm (5 mils).

7. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

8. A 3x3 array of 1.45 mm square openings on a 2.00 mm pitch can be used for the center ground pad.

9. A No-Clean, Type-3 solder paste is recommended.

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Figure 9.3. QFN64 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

Figure 11.3. QFN32 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.