Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XF

| Product Status             | Discontinued at Digi-Key                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT          |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

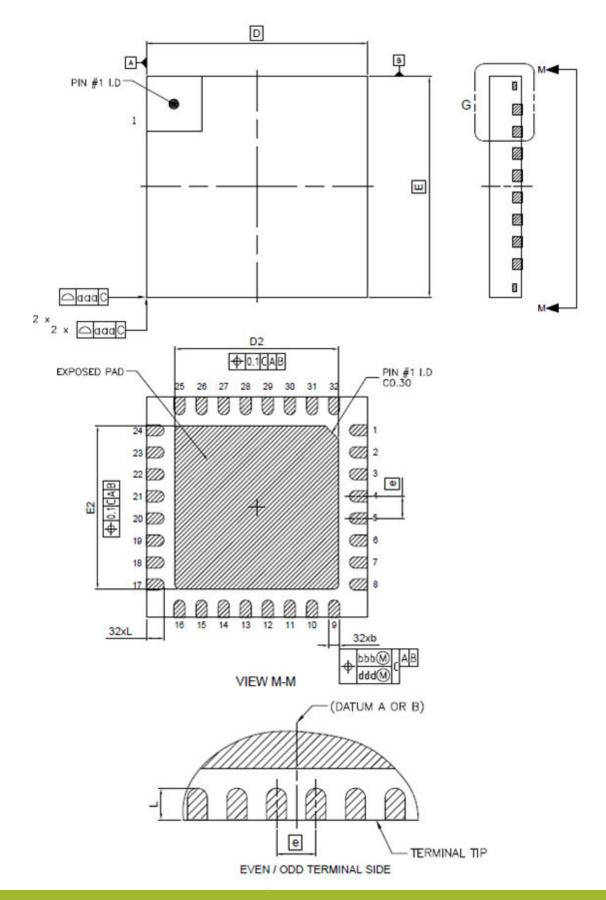

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b520f128gm64-ar |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3 General Purpose Input/Output (GPIO)

EFM32TG11 has up to 67 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

#### 3.4 Clocking

### 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32TG11. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

#### 3.4.2 Internal and External Oscillators

The EFM32TG11 supports two crystal oscillators and fully integrates four RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 4 to 48 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range. When crystal accuracy is not required, it can be operated in free-running mode at a number of factory-calibrated frequencies. A digital phase-locked loop (DPLL) feature allows the HFRCO to achieve higher accuracy and stability by referencing other available clock sources such as LFXO and HFXO.

- An integrated auxilliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC with a wide frequency range.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

#### 3.5 Counters/Timers and PWM

#### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

#### 3.5.2 Wide Timer/Counter (WTIMER)

WTIMER peripherals function just as TIMER peripherals, but are 32 bits wide. They keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each WTIMER is a 32-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the WTIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit WTIMER\_0 only.

#### 3.5.3 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes down to EM4H.

### 3.6.5 Controller Area Network (CAN)

The CAN peripheral provides support for communication at up to 1 Mbps over CAN protocol version 2.0 part A and B. It includes 32 message objects with independent identifier masks and retains message RAM in EM2. Automatic retransmittion may be disabled in order to support Time Triggered CAN applications.

#### 3.6.6 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality such as simple logic operations (AND, OR, NOT) can be applied by the PRS to the signals. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

### 3.6.7 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface LESENSE<sup>TM</sup> is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators, ADC, and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable finite state machine which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

#### 3.7 Security Features

### 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)

The GPCRC module implements a Cyclic Redundancy Check (CRC) function. It supports both 32-bit and 16-bit polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3), while the 16-bit polynomial can be programmed to any value, depending on the needs of the application.

### 3.7.2 Crypto Accelerator (CRYPTO)

The Crypto Accelerator is a fast and energy-efficient autonomous hardware encryption and decryption accelerator. Tiny Gecko Series 1 devices support AES encryption and decryption with 128- or 256-bit keys, ECC over both GF(P) and GF(2<sup>m</sup>), and SHA-1 and SHA-2 (SHA-224 and SHA-256).

Supported block cipher modes of operation for AES include: ECB, CTR, CBC, PCBC, CFB, OFB, GCM, CBC-MAC, GMAC and CCM.

Supported ECC NIST recommended curves include P-192, P-224, P-256, K-163, K-233, B-163 and B-233.

The CRYPTO module allows fast processing of GCM (AES), ECC and SHA with little CPU intervention. CRYPTO also provides trigger signals for DMA read and write operations.

#### 3.7.3 True Random Number Generator (TRNG)

The TRNG module is a non-deterministic random number generator based on a full hardware solution. The TRNG is validated with NIST800-22 and AIS-31 test suites as well as being suitable for FIPS 140-2 certification (for the purposes of cryptographic key generation).

#### 3.7.4 Security Management Unit (SMU)

The Security Management Unit (SMU) allows software to set up fine-grained security for peripheral access, which is not possible in the Memory Protection Unit (MPU). Peripherals may be secured by hardware on an individual basis, such that only priveleged accesses to the peripheral's register interface will be allowed. When an access fault occurs, the SMU reports the specific peripheral involved and can optionally generate an interrupt.

#### 3.8 Analog

## 4.1.6.3 Current Consumption 1.8 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 1.8 V. T = 25 °C. DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

# Table 4.8. Current Consumption 1.8 V without DC-DC Converter

| Parameter                                                                                            | Symbol                 | Test Condition                                                       | Min | Тур  | Max | Unit   |

|------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-                                            | I <sub>ACTIVE</sub>    | 48 MHz crystal, CPU running while loop from flash                    | _   | 45   | _   | µA/MHz |

| abled                                                                                                |                        | 48 MHz HFRCO, CPU running while loop from flash                      | _   | 44   | _   | µA/MHz |

|                                                                                                      |                        | 48 MHz HFRCO, CPU running<br>Prime from flash                        | _   | 57   | _   | µA/MHz |

|                                                                                                      |                        | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash                | _   | 71   |     | µA/MHz |

|                                                                                                      |                        | 32 MHz HFRCO, CPU running while loop from flash                      | _   | 45   | _   | µA/MHz |

|                                                                                                      |                        | 26 MHz HFRCO, CPU running while loop from flash                      | _   | 46   | _   | µA/MHz |

|                                                                                                      |                        | 16 MHz HFRCO, CPU running while loop from flash                      | _   | 49   | _   | µA/MHz |

|                                                                                                      |                        | 1 MHz HFRCO, CPU running while loop from flash                       | —   | 158  | —   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis-<br>abled and voltage scaling<br>enabled | I <sub>ACTIVE_VS</sub> | 19 MHz HFRCO, CPU running while loop from flash                      | _   | 41   | —   | µA/MHz |

|                                                                                                      |                        | 1 MHz HFRCO, CPU running while loop from flash                       | —   | 142  | _   | µA/MHz |

| Current consumption in EM1                                                                           | I <sub>EM1</sub>       | 48 MHz crystal                                                       | —   | 34   | _   | µA/MHz |

| mode with all peripherals disabled                                                                   |                        | 48 MHz HFRCO                                                         | _   | 33   | _   | µA/MHz |

|                                                                                                      |                        | 32 MHz HFRCO                                                         | _   | 34   | _   | µA/MHz |

|                                                                                                      |                        | 26 MHz HFRCO                                                         | _   | 35   |     | µA/MHz |

|                                                                                                      |                        | 16 MHz HFRCO                                                         | _   | 39   |     | µA/MHz |

|                                                                                                      |                        | 1 MHz HFRCO                                                          | _   | 147  |     | µA/MHz |

| Current consumption in EM1                                                                           | I <sub>EM1_VS</sub>    | 19 MHz HFRCO                                                         | _   | 32   |     | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled                               |                        | 1 MHz HFRCO                                                          | —   | 133  | —   | µA/MHz |

| Current consumption in EM2 mode, with voltage scaling                                                | I <sub>EM2_VS</sub>    | Full 32 kB RAM retention and<br>RTCC running from LFXO               | _   | 1.39 | _   | μΑ     |

| enabled                                                                                              |                        | Full 32 kB RAM retention and<br>RTCC running from LFRCO              | _   | 1.63 | _   | μΑ     |

|                                                                                                      |                        | 8 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup> | _   | 1.37 | _   | μΑ     |

| Current consumption in EM3<br>mode, with voltage scaling<br>enabled                                  | I <sub>EM3_VS</sub>    | Full 32 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO   | _   | 1.10 | _   | μA     |

# 4.1.10 Flash Memory Characteristics<sup>5</sup>

| Parameter                                   | Symbol               | Test Condition                                | Min   | Тур | Мах | Unit   |

|---------------------------------------------|----------------------|-----------------------------------------------|-------|-----|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                                               | 10000 | _   | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T ≤ 85 °C                                     | 10    | _   | _   | years  |

|                                             |                      | T ≤ 125 °C                                    | 10    |     | _   | years  |

| Word (32-bit) programming time              | tw_prog              | Burst write, 128 words, average time per word | 20    | 26  | 32  | μs     |

|                                             |                      | Single word                                   | 59    | 68  | 83  | μs     |

| Page erase time <sup>4</sup>                | t <sub>PERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                                               | 20    | 27  | 35  | ms     |

| Device erase time <sup>2 3</sup>            | t <sub>DERASE</sub>  | T ≤ 85 °C                                     | _     | 54  | 70  | ms     |

|                                             |                      | T ≤ 125 °C                                    | _     | 54  | 75  | ms     |

| Erase current <sup>6</sup>                  | I <sub>ERASE</sub>   | Page Erase                                    | _     | _   | 1.7 | mA     |

|                                             |                      | Mass or Device Erase                          | _     |     | 2.0 | mA     |

| Write current <sup>6</sup>                  | I <sub>WRITE</sub>   |                                               | —     |     | 3.5 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                                               | 1.62  | _   | 3.6 | V      |

# Table 4.17. Flash Memory Characteristics<sup>5</sup>

# Note:

- 1. Mass erase is issued by the CPU and erases all flash.

- 2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

- 3. From setting the DEVICEERASE bit in AAP\_CMD to 1 until the ERASEBUSY bit in AAP\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 4. From setting the ERASEPAGE bit in MSC\_WRITECMD to 1 until the BUSY bit in MSC\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 5. Flash data retention information is published in the Quarterly Quality and Reliability Report.

6. Measured at 25 °C.

| Parameter                  | Symbol            | Test Condition                       | Min | Тур | Мах | Unit |

|----------------------------|-------------------|--------------------------------------|-----|-----|-----|------|

| Output fall time, From 70% | t <sub>IOOF</sub> | C <sub>L</sub> = 50 pF,              | —   | 1.8 | —   | ns   |

| to 30% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              |     | 4.5 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Output rise time, From 30% | t <sub>IOOR</sub> | C <sub>L</sub> = 50 pF,              |     | 2.2 |     | ns   |

| to 70% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE = 0x6 <sup>1</sup>          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              | _   | 7.4 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Note:                      | 1                 | 1                                    | 1   | 1   | 1   | 1    |

# 4.1.16 Capacitive Sense (CSEN)

| Parameter                                                                           | Symbol                | Test Condition                                                                                                                                                   | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Single conversion time (1x                                                          | t <sub>CNV</sub>      | 12-bit SAR Conversions                                                                                                                                           | _   | 20.2 | —   | μs   |

| accumulation)                                                                       |                       | 16-bit SAR Conversions                                                                                                                                           | _   | 26.4 | _   | μs   |

|                                                                                     |                       | Delta Modulation Conversion (sin-<br>gle comparison)                                                                                                             | _   | 1.55 | _   | μs   |

| Maximum external capacitive load                                                    | C <sub>EXTMAX</sub>   | CS0CG=7 (Gain = 1x), including routing parasitics                                                                                                                | _   | 68   |     | pF   |

|                                                                                     |                       | CS0CG=0 (Gain = 10x), including routing parasitics                                                                                                               | —   | 680  | _   | pF   |

| Maximum external series impedance                                                   | R <sub>EXTMAX</sub>   |                                                                                                                                                                  | —   | 1    | _   | kΩ   |

| Supply current, EM2 bonded<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-<br>MUPCNT=0 | ICSEN_BOND            | 12-bit SAR conversions, 20 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                       | _   | 326  | _   | nA   |

|                                                                                     |                       | Delta Modulation conversions, 20<br>ms conversion rate, CS0CG=7<br>(Gain = 1x), 10 channels bonded<br>(total capacitance of 330 pF) <sup>1</sup>                 | _   | 226  | _   | nA   |

|                                                                                     |                       | 12-bit SAR conversions, 200 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                      | _   | 33   | _   | nA   |

|                                                                                     |                       | Delta Modulation conversions,<br>200 ms conversion rate,<br>CS0CG=7 (Gain = 1x), 10 chan-<br>nels bonded (total capacitance of<br>330 pF) <sup>1</sup>           | _   | 25   | _   | nA   |

| Supply current, EM2 scan<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-               | I <sub>CSEN_EM2</sub> | 12-bit SAR conversions, 20 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                             | —   | 690  | _   | nA   |

| MUPCNT=0                                                                            |                       | Delta Modulation conversions, 20<br>ms scan rate, 8 comparisons per<br>sample (DMCR = 1, DMR = 2),<br>CS0CG=0 (Gain = 10x), 8 sam-<br>ples per scan <sup>1</sup> | _   | 515  | _   | nA   |

|                                                                                     |                       | 12-bit SAR conversions, 200 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                            | _   | 79   | _   | nA   |

|                                                                                     |                       | Delta Modulation conversions,<br>200 ms scan rate, 8 comparisons<br>per sample (DMCR = 1, DMR =<br>2), CS0CG=0 (Gain = 10x), 8<br>samples per scan <sup>1</sup>  | _   | 57   |     | nA   |

# Table 4.23. Capacitive Sense (CSEN)

| Parameter                                                               | Symbol         | Test Condition                                                                                     | Min | Тур  | Max | Unit   |

|-------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Supply current, continuous<br>conversions, WARMUP-<br>MODE=KEEPCSENWARM | ICSEN_ACTIVE   | SAR or Delta Modulation conver-<br>sions of 33 pF capacitor,<br>CS0CG=0 (Gain = 10x), always<br>on | _   | 90.5 | _   | μA     |

| HFPERCLK supply current                                                 | ICSEN_HFPERCLK | Current contribution from<br>HFPERCLK when clock to CSEN<br>block is enabled.                      | _   | 2.25 | _   | µA/MHz |

# Note:

Current is specified with a total external capacitance of 33 pF per channel. Average current is dependent on how long the module is actively sampling channels within the scan period, and scales with the number of samples acquired. Supply current for a specific application can be estimated by multiplying the current per sample by the total number of samples per period (total\_current = single\_sample\_current \* (number\_of\_channels \* accumulation)).

| Parameter                                    | Symbol             | Test Condition                                                                               | Min | Тур   | Мах | Unit |

|----------------------------------------------|--------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Slew rate <sup>5</sup>                       | SR                 | DRIVESTRENGTH = 3,<br>INCBW=1 <sup>3</sup>                                                   | _   | 4.7   | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 3,<br>INCBW=0                                                                | _   | 1.5   | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=1 <sup>3</sup>                                                   | _   | 1.27  | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=0                                                                | _   | 0.42  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.17  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=0                                                                | —   | 0.058 | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.044 | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=0                                                                | _   | 0.015 | _   | V/µs |

| Startup time <sup>6</sup>                    | T <sub>START</sub> | DRIVESTRENGTH = 2                                                                            | _   | _     | TBD | μs   |

| Input offset voltage                         | V <sub>OSI</sub>   | DRIVESTRENGTH = 2 or 3, T =<br>25 °C                                                         | TBD | _     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0, T = 25 °C                                                            | TBD | —     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 2 or 3,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

| DC power supply rejection ratio <sup>9</sup> | PSRR <sub>DC</sub> | Input referred                                                                               | —   | 70    | _   | dB   |

| DC common-mode rejection ratio <sup>9</sup>  | CMRR <sub>DC</sub> | Input referred                                                                               | _   | 70    | _   | dB   |

| Total harmonic distortion                    | THD <sub>OPA</sub> | DRIVESTRENGTH = 2, 3x Gain<br>connection, 1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V   | _   | 90    | _   | dB   |

|                                              |                    | DRIVESTRENGTH = 0, 3x Gain<br>connection, 0.1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V | _   | 90    | _   | dB   |

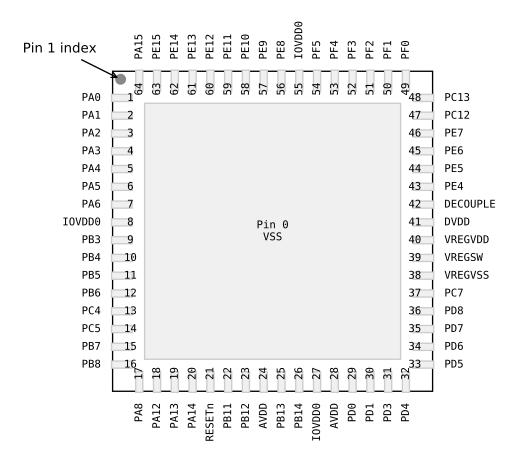

### Figure 5.6. EFM32TG11B5xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0<br>38       | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>27<br>55 | Digital IO power supply 0. | PB3      | 9      | GPIO        |

| Pin Name | Pin(s) | Description           | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|-----------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB7      | 11     | GPIO                  | PB8      | 12       | GPIO                                                                                                                                                                                                        |

| PA8      | 13     | GPIO                  | PA9      | 14       | GPIO                                                                                                                                                                                                        |

| PA10     | 15     | GPIO                  | RESETn   | 16       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 17     | GPIO                  | AVDD     | 19<br>23 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 20     | GPIO                  | PB14     | 21       | GPIO                                                                                                                                                                                                        |

| PD4      | 24     | GPIO                  | PD5      | 25       | GPIO                                                                                                                                                                                                        |

| PD6      | 26     | GPIO                  | PD7      | 27       | GPIO                                                                                                                                                                                                        |

| DVDD     | 28     | Digital power supply. | DECOUPLE | 29       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PC8      | 30     | GPIO                  | PC9      | 31       | GPIO                                                                                                                                                                                                        |

| PC10     | 32     | GPIO (5V)             | PC11     | 33       | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 34     | GPIO (5V)             | PC14     | 35       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 36     | GPIO (5V)             | PF0      | 37       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 38     | GPIO (5V)             | PF2      | 39       | GPIO                                                                                                                                                                                                        |

| PF3      | 40     | GPIO                  | PF4      | 41       | GPIO                                                                                                                                                                                                        |

| PF5      | 42     | GPIO                  | PE10     | 45       | GPIO                                                                                                                                                                                                        |

| PE11     | 46     | GPIO                  | PE12     | 47       | GPIO                                                                                                                                                                                                        |

| PE13     | 48     | GPIO                  |          |          |                                                                                                                                                                                                             |

| Note:    | •      | ·                     |          |          | ·                                                                                                                                                                                                           |

1. GPIO with 5V tolerance are indicated by (5V).

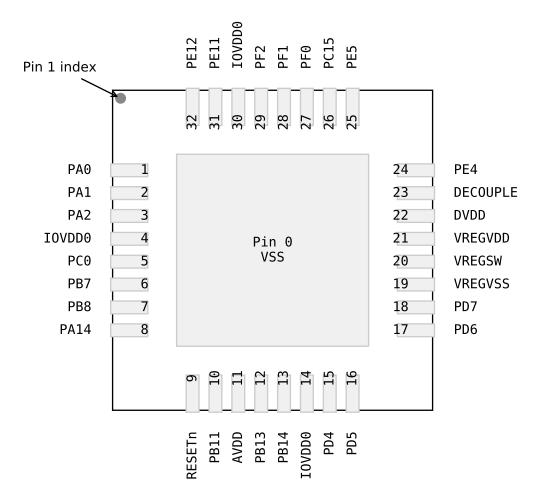

## Figure 5.12. EFM32TG11B5xx in QFN32 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.12. EFM32TG11B5xx in QFN32 Device Pinout |

|--------------------------------------------------|

|--------------------------------------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0<br>19       | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| IOVDD0   | 4<br>14<br>30 | Digital IO power supply 0. | PC0      | 5      | GPIO (5V)   |

| PB7      | 6             | GPIO                       | PB8      | 7      | GPIO        |

| Alternate     | LOCA                                  | ATION              |                                                                                                                                                                                      |  |  |  |  |  |  |

|---------------|---------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Functionality | 0 - 3                                 | 4 - 7              | Description                                                                                                                                                                          |  |  |  |  |  |  |

| CAN0_TX       | 0: PC1<br>1: PF2<br>2: PD1            |                    | CAN0 TX.                                                                                                                                                                             |  |  |  |  |  |  |

| CMU_CLK0      | 0: PA2<br>1: PC12<br>2: PD7           | 4: PF2<br>5: PA12  | Clock Management Unit, clock output number 0.                                                                                                                                        |  |  |  |  |  |  |

| CMU_CLK1      | 0: PA1<br>1: PD8<br>2: PE12           | 4: PF3<br>5: PB11  | Clock Management Unit, clock output number 1.                                                                                                                                        |  |  |  |  |  |  |

| CMU_CLK2      | 0: PA0<br>1: PA3<br>2: PD6            | 4: PA3             | Clock Management Unit, clock output number 2.                                                                                                                                        |  |  |  |  |  |  |

| CMU_CLKI0     | 0: PD4<br>1: PA3<br>2: PB8<br>3: PB13 | 6: PE12<br>7: PB11 | Clock Management Unit, clock input number 0.                                                                                                                                         |  |  |  |  |  |  |

| DBG_SWCLKTCK  | 0: PF0                                |                    | Debug-interface Serial Wire clock input and JTAG Test Clock.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull down.                            |  |  |  |  |  |  |

| DBG_SWDIOTMS  | 0: PF1                                |                    | Debug-interface Serial Wire data input / output and JTAG Test Mode Select.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull up.                |  |  |  |  |  |  |

| DBG_TDI       | 0: PF5                                |                    | Debug-interface JTAG Test Data In.<br>Note that this function becomes available after the first valid JTAG command is re-<br>ceived, and has a built-in pull up when JTAG is active. |  |  |  |  |  |  |

| DBG_TDO       | 0: PF2                                |                    | Debug-interface JTAG Test Data Out.<br>Note that this function becomes available after the first valid JTAG command is re-<br>ceived.                                                |  |  |  |  |  |  |

| GPIO_EM4WU0   | 0: PA0                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| GPIO_EM4WU1   | 0: PA6                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| GPIO_EM4WU2   | 0: PC9                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| GPIO_EM4WU3   | 0: PF1                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| Alternate     | LOCA                                   | ATION                       |                                                  |  |  |  |  |  |  |  |  |

|---------------|----------------------------------------|-----------------------------|--------------------------------------------------|--|--|--|--|--|--|--|--|

| Functionality | 0 - 3                                  | 4 - 7                       | Description                                      |  |  |  |  |  |  |  |  |

| OPA3_N        | 0: PC7                                 |                             | Operational Amplifier 3 external negative input. |  |  |  |  |  |  |  |  |

| OPA3_OUT      | 0: PD1                                 |                             | Operational Amplifier 3 output.                  |  |  |  |  |  |  |  |  |

| OPA3_P        | 0: PC6                                 |                             | Operational Amplifier 3 external positive input. |  |  |  |  |  |  |  |  |

| PCNT0_S0IN    | 0: PC13<br>2: PC0<br>3: PD6            | 4: PA0<br>6: PB5<br>7: PB12 | Pulse Counter PCNT0 input number 0.              |  |  |  |  |  |  |  |  |

| PCNT0_S1IN    | 0: PC14<br>2: PC1<br>3: PD7            | 4: PA1<br>6: PB6<br>7: PB11 | Pulse Counter PCNT0 input number 1.              |  |  |  |  |  |  |  |  |

| PRS_CH0       | 0: PA0<br>1: PF3<br>2: PC14<br>3: PF2  |                             | Peripheral Reflex System PRS, channel 0.         |  |  |  |  |  |  |  |  |

| PRS_CH1       | 0: PA1<br>1: PF4<br>2: PC15<br>3: PE12 |                             | Peripheral Reflex System PRS, channel 1.         |  |  |  |  |  |  |  |  |

| PRS_CH2       | 0: PC0<br>1: PF5<br>2: PE10<br>3: PE13 |                             | Peripheral Reflex System PRS, channel 2.         |  |  |  |  |  |  |  |  |

| PRS_CH3       | 0: PC1<br>1: PE8<br>2: PE11<br>3: PA0  |                             | Peripheral Reflex System PRS, channel 3.         |  |  |  |  |  |  |  |  |

| PRS_CH4       | 0: PC8<br>2: PF1                       |                             | Peripheral Reflex System PRS, channel 4.         |  |  |  |  |  |  |  |  |

| PRS_CH5       | 0: PC9<br>2: PD6                       |                             | Peripheral Reflex System PRS, channel 5.         |  |  |  |  |  |  |  |  |

| PRS_CH6       | 0: PA6<br>1: PB14<br>2: PE6            |                             | Peripheral Reflex System PRS, channel 6.         |  |  |  |  |  |  |  |  |

| PRS_CH7       | 0: PB13<br>2: PE7                      |                             | Peripheral Reflex System PRS, channel 7.         |  |  |  |  |  |  |  |  |

# EFM32TG11 Family Data Sheet Pin Definitions

| Port           | Bus      | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

|----------------|----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| OP             | OPA3_OUT |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y        | BUSAY    |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY    |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| <b>APORT3Y</b> | BUSCY    |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY    |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| OP             | OPA3_P   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1X        | BUSAX    |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PAO |

| APORT2X        | BUSBX    |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | 6A9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| <b>APORT3X</b> | BUSCX    |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| APORT4X        | BUSDX    |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| VD             | AC       | 0_0  | UT0  | / 0  | PA0  | _οι  | JT   |      |      |      |      |      | 1    |      |      | 1    |      |      |      |      | 1    | 1    |      |     |     |     | 1   |     |     |     |     |     |     |

| APORT1Y        | BUSAY    |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | 6A9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY    |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| <b>APORT3Y</b> | BUSCY    |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY    |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

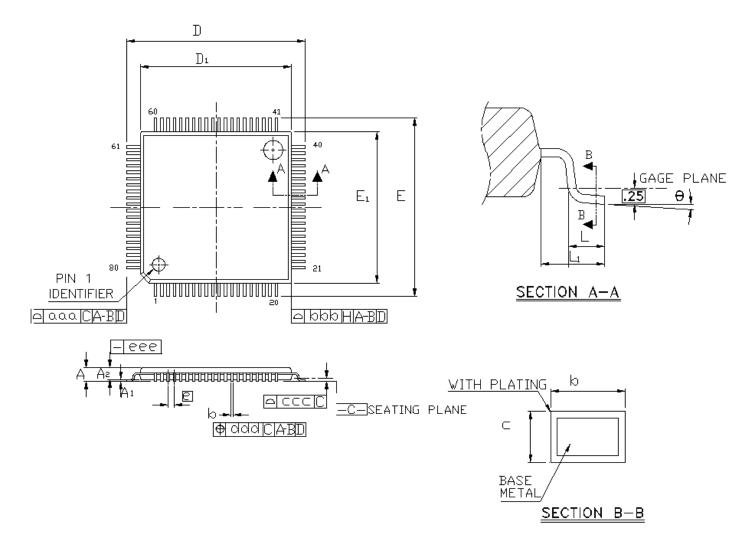

# 6. TQFP80 Package Specifications

# 6.1 TQFP80 Package Dimensions

Figure 6.1. TQFP80 Package Drawing

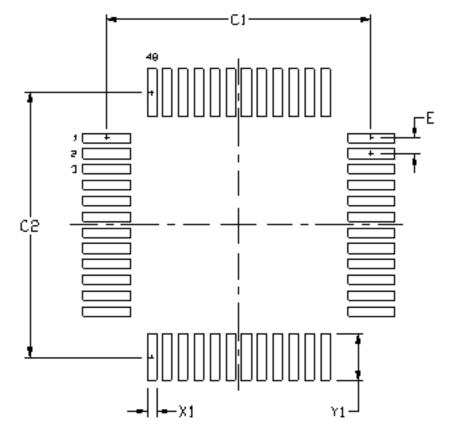

### Table 6.2. TQFP80 PCB Land Pattern Dimensions

| Dimension | Min   | Мах   |  |  |  |  |

|-----------|-------|-------|--|--|--|--|

| C1        | 13.30 | 13.40 |  |  |  |  |

| C2        | 13.30 | 13.40 |  |  |  |  |

| E         | 0.50  | BSC   |  |  |  |  |

| x         | 0.20  | 0.30  |  |  |  |  |

| Y         | 1.40  | 1.50  |  |  |  |  |

# Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

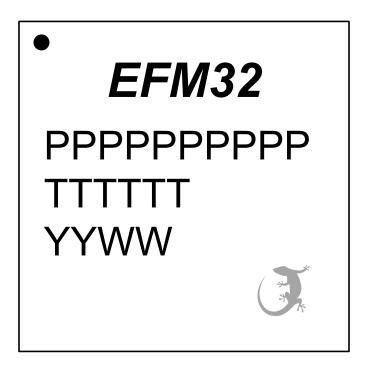

### 6.3 TQFP80 Package Marking

Figure 6.3. TQFP80 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

### Table 7.2. QFN80 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 8.90 |

| C2        | 8.90 |

| E         | 0.40 |

| X1        | 0.20 |

| Y1        | 0.85 |

| X2        | 7.30 |

| Y2        | 7.30 |

# Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

6. The stencil thickness should be 0.125 mm (5 mils).

7. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

8. A 3x3 array of 1.45 mm square openings on a 2.00 mm pitch can be used for the center ground pad.

9. A No-Clean, Type-3 solder paste is recommended.

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

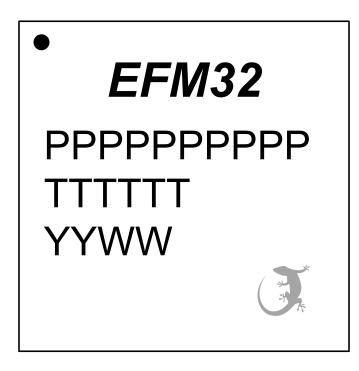

Figure 7.3. QFN80 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

### 10.2 TQFP48 PCB Land Pattern

Figure 10.2. TQFP48 PCB Land Pattern Drawing

Table 10.2.

TQFP48 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 8.50 |

| C2        | 8.50 |

| E         | 0.50 |

| x         | 0.30 |

| Y         | 1.60 |

#### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60  $\mu$ m minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

# 11. QFN32 Package Specifications

## 11.1 QFN32 Package Dimensions