Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                   |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT          |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b520f128gq64-ar |

#### 1. Feature List

The EFM32TG11 highlighted features are listed below.

- ARM Cortex-M0+ CPU platform

- · High performance 32-bit processor @ up to 48 MHz

- · Memory Protection Unit

- Wake-up Interrupt Controller

- Flexible Energy Management System

- 37 µA/MHz in Active Mode (EM0)

- 1.30 µA EM2 Deep Sleep current (8 kB RAM retention and RTCC running from LFRCO)

- Integrated DC-DC buck converter

- Backup Power Domain

- RTCC and retention registers in a separate power domain, available in all energy modes

- Operation from backup battery when main power absent/ insufficient

- Up to 128 kB flash program memory

- Up to 32 kB RAM data memory

- · Communication Interfaces

- · CAN Bus Controller

- Version 2.0A and 2.0B up to 1 Mbps

- 4 × Universal Synchronous/Asynchronous Receiver/ Transmitter

- UART/SPI/SmartCard (ISO 7816)/IrDA/I2S/LIN

- · Triple buffered full/half-duplex operation with flow control

- Ultra high speed (24 MHz) operation on one instance

- 1 × Universal Asynchronous Receiver/ Transmitter

- 1 × Low Energy UART

- · Autonomous operation with DMA in Deep Sleep Mode

- 2 × I<sup>2</sup>C Interface with SMBus support

- · Address recognition in EM3 Stop Mode

## Up to 67 General Purpose I/O Pins

- Configurable push-pull, open-drain, pull-up/down, input filter, drive strength

- · Configurable peripheral I/O locations

- · 5 V tolerance on select pins

- Asynchronous external interrupts

- · Output state retention and wake-up from Shutoff Mode

- Up to 8 Channel DMA Controller

- Up to 8 Channel Peripheral Reflex System (PRS) for autonomous inter-peripheral signaling

- · Hardware Cryptography

- AES 128/256-bit keys

- ECC B/K163, B/K233, P192, P224, P256

- SHA-1 and SHA-2 (SHA-224 and SHA-256)

- True Random Number Generator (TRNG)

- · Hardware CRC engine

- Single-cycle computation with 8/16/32-bit data and 16-bit (programmable)/32-bit (fixed) polynomial

- Security Management Unit (SMU)

- · Fine-grained access control for on-chip peripherals

- Integrated Low-energy LCD Controller with up to 8 × 32 segments

- Voltage boost, contrast and autonomous animation

- · Patented low-energy LCD driver

- Ultra Low-Power Precision Analog Peripherals

- 12-bit 1 Msamples/s Analog to Digital Converter (ADC)

- · On-chip temperature sensor

- 2 × 12-bit 500 ksamples/s Digital to Analog Converter (VDAC)

- Up to 2 × Analog Comparator (ACMP)

- Up to 4 × Operational Amplifier (OPAMP)

- Robust current-based capacitive sensing with up to 38 inputs and wake-on-touch (CSEN)

- Up to 62 GPIO pins are analog-capable. Flexible analog peripheral-to-pin routing via Analog Port (APORT)

- Supply Voltage Monitor

# **Table of Contents**

| 1. | Feature List                                                          | . 2  |

|----|-----------------------------------------------------------------------|------|

| 2. | Ordering Information                                                  | . 4  |

| 3. | System Overview                                                       | . 10 |

|    | 3.1 Introduction                                                      | .10  |

|    | 3.2 Power                                                             | .11  |

|    | 3.2.1 Energy Management Unit (EMU)                                    |      |

|    | 3.2.2 DC-DC Converter                                                 |      |

|    | 3.2.3 EM2 and EM3 Power Domains                                       |      |

|    | 3.3 General Purpose Input/Output (GPIO)                               |      |

|    | 3.4 Clocking                                                          |      |

|    | 3.4.1 Clock Management Unit (CMU)                                     |      |

|    | 3.5 Counters/Timers and PWM                                           |      |

|    | 3.5.1 Timer/Counter (TIMER)                                           |      |

|    | 3.5.2 Wide Timer/Counter (WTIMER)                                     | .12  |

|    | 3.5.3 Real Time Counter and Calendar (RTCC)                           |      |

|    | 3.5.4 Low Energy Timer (LETIMER)                                      |      |

|    | 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)                       |      |

|    | 3.5.7 Watchdog Timer (WDOG)                                           |      |

|    | 3.6 Communications and Other Digital Peripherals                      |      |

|    | 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART) |      |

|    | 3.6.2 Universal Asynchronous Receiver/Transmitter (UART)              |      |

|    | 3.6.3 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART) |      |

|    | 3.6.4 Inter-Integrated Circuit Interface (I <sup>2</sup> C)           |      |

|    | 3.6.5 Controller Area Network (CAN)                                   |      |

|    | 3.6.7 Low Energy Sensor Interface (LESENSE)                           |      |

|    | 3.7 Security Features                                                 |      |

|    | 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)                 |      |

|    | 3.7.2 Crypto Accelerator (CRYPTO)                                     | .14  |

|    | 3.7.3 True Random Number Generator (TRNG)                             |      |

|    | 3.7.4 Security Management Unit (SMU)                                  |      |

|    | 3.8 Analog                                                            |      |

|    | 3.8.1 Analog Port (APORT)                                             |      |

|    | 3.8.3 Analog to Digital Converter (ADC)                               |      |

|    | 3.8.4 Capacitive Sense (CSEN)                                         |      |

|    | 3.8.5 Digital to Analog Converter (VDAC)                              |      |

|    | 3.8.6 Operational Amplifiers                                          |      |

|    | 3.8.7 Liquid Crystal Display Driver (LCD)                             |      |

|    | 3.9 Reset Management Unit (RMU)                                       | .15  |

# 4.1.7 Wake Up Times

Table 4.9. Wake Up Times

| Parameter                                  | Symbol               | Test Condition                                               | Min | Тур  | Max | Unit          |

|--------------------------------------------|----------------------|--------------------------------------------------------------|-----|------|-----|---------------|

| Wake up time from EM1                      | t <sub>EM1_WU</sub>  |                                                              | _   | 3    | _   | AHB<br>Clocks |

| Wake up from EM2                           | t <sub>EM2_WU</sub>  | Code execution from flash                                    | _   | 10.1 | _   | μs            |

|                                            |                      | Code execution from RAM                                      | _   | 3.1  | _   | μs            |

| Wake up from EM3                           | t <sub>EM3_WU</sub>  | Code execution from flash                                    | _   | 10.1 | _   | μs            |

|                                            |                      | Code execution from RAM                                      | _   | 3.1  | _   | μs            |

| Wake up from EM4H <sup>1</sup>             | t <sub>EM4H_WU</sub> | Executing from flash                                         | _   | 88   | _   | μs            |

| Wake up from EM4S <sup>1</sup>             | t <sub>EM4S_WU</sub> | Executing from flash                                         | _   | 282  | _   | μs            |

| Time from release of reset                 | t <sub>RESET</sub>   | Soft Pin Reset released                                      | _   | 50   | _   | μs            |

| source to first instruction ex-<br>ecution |                      | Any other reset released                                     | _   | 352  | _   | μs            |

| Power mode scaling time                    | t <sub>SCALE</sub>   | VSCALE0 to VSCALE2, HFCLK = 19 MHz <sup>4</sup> <sup>2</sup> | _   | 31.8 | _   | μs            |

|                                            |                      | VSCALE2 to VSCALE0, HFCLK = 19 MHz <sup>3</sup>              | _   | 4.3  | _   | μs            |

- 1. Time from wake up request until first instruction is executed. Wakeup results in device reset.

- 2. VSCALE0 to VSCALE2 voltage change transitions occur at a rate of 10 mV/ $\mu$ s for approximately 20  $\mu$ s. During this transition, peak currents will be dependent on the value of the DECOUPLE output capacitor, from 35 mA (with a 1  $\mu$ F capacitor) to 70 mA (with a 2.7  $\mu$ F capacitor).

- 3. Scaling down from VSCALE2 to VSCALE0 requires approximately 2.8  $\mu$ s + 29 HFCLKs.

- 4. Scaling up from VSCALE0 to VSCALE2 requires approximately 30.3  $\mu$ s + 28 HFCLKs.

| Parameter                  | Symbol            | Test Condition                       | Min | Тур | Max | Unit |

|----------------------------|-------------------|--------------------------------------|-----|-----|-----|------|

| Output fall time, From 70% | t <sub>IOOF</sub> | C <sub>L</sub> = 50 pF,              | _   | 1.8 | _   | ns   |

| to 30% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              | _   | 4.5 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Output rise time, From 30% | t <sub>IOOR</sub> | C <sub>L</sub> = 50 pF,              | _   | 2.2 | _   | ns   |

| to 70% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE = 0x6 <sup>1</sup>          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              | _   | 7.4 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

# Note:

1. In GPIO\_Pn\_CTRL register.

# 4.1.12 Voltage Monitor (VMON)

Table 4.19. Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Max | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | I <sub>VMON</sub>       | In EM0 or EM1, 1 supply monitored, T ≤ 85 °C                     | _    | 6.3  | TBD | μA   |

|                                    |                         | In EM0 or EM1, 4 supplies monitored, T ≤ 85 °C                   | _    | 12.5 | TBD | μA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | _    | 99   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold |      | 99   | _   | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | _    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    | _   | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | _    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  | _   | mV   |

|                                    |                         | Fine                                                             | _    | 20   | _   | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | _    | 460  | _   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  |      | 26   | _   | mV   |

| Parameter                                                        | Symbol                   | Test Condition                                                                                | Min | Тур  | Max | Unit   |

|------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Supply current, continuous conversions, WARMUP-MODE=KEEPCSENWARM | I <sub>CSEN_ACTIVE</sub> | SAR or Delta Modulation conversions of 33 pF capacitor,<br>CS0CG=0 (Gain = 10x), always<br>on | _   | 90.5 | _   | μА     |

| HFPERCLK supply current                                          | ICSEN_HFPERCLK           | Current contribution from HFPERCLK when clock to CSEN block is enabled.                       | _   | 2.25 | _   | µA/MHz |

<sup>1.</sup> Current is specified with a total external capacitance of 33 pF per channel. Average current is dependent on how long the module is actively sampling channels within the scan period, and scales with the number of samples acquired. Supply current for a specific application can be estimated by multiplying the current per sample by the total number of samples per period (total\_current = single\_sample\_current \* (number\_of\_channels \* accumulation)).

## 4.1.19 Pulse Counter (PCNT)

# Table 4.26. Pulse Counter (PCNT)

| Parameter       | Symbol          | Test Condition                               | Min | Тур | Max | Unit |

|-----------------|-----------------|----------------------------------------------|-----|-----|-----|------|

| Input frequency | F <sub>IN</sub> | Asynchronous Single and Quadrature Modes     | _   | _   | 20  | MHz  |

|                 |                 | Sampled Modes with Debounce filter set to 0. | _   | _   | 8   | kHz  |

## 4.1.20 Analog Port (APORT)

#### Table 4.27. Analog Port (APORT)

| Parameter                   | Symbol             | Test Condition       | Min | Тур | Max | Unit |

|-----------------------------|--------------------|----------------------|-----|-----|-----|------|

| Supply current <sup>2</sup> | I <sub>APORT</sub> | Operation in EM0/EM1 | _   | 7   | _   | μΑ   |

|                             |                    | Operation in EM2/EM3 | _   | 915 | _   | nA   |

- 1. Specified current is for continuous APORT operation. In applications where the APORT is not requested continuously (e.g. periodic ACMP requests from LESENSE in EM2), the average current requirements can be estimated by mutiplying the duty cycle of the requests by the specified continuous current number.

- 2. Supply current increase that occurs when an analog peripheral requests access to APORT. This current is not included in reported module currents. Additional peripherals requesting access to APORT do not incur further current.

## 4.1.21 I2C

# 4.1.21.1 I2C Standard-mode (Sm)<sup>1</sup>

Table 4.28. I2C Standard-mode (Sm)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | _   | 100  | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 4.7 | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 4   | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 250 | _   | _    | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD_DAT</sub> |                | 100 | _   | 3450 | ns   |

| Repeated START condition set-up time             | tsu_sta             |                | 4.7 | _   | _    | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 4   | _   | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 4   | _   | _    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 4.7 | _   | _    | μs   |

- 1. For CLHR set to 0 in the I2Cn\_CTRL register.

- 2. For the minimum HFPERCLK frequency required in Standard-mode, refer to the I2C chapter in the reference manual.

- 3. The maximum SDA hold time ( $t_{HD\ DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ).

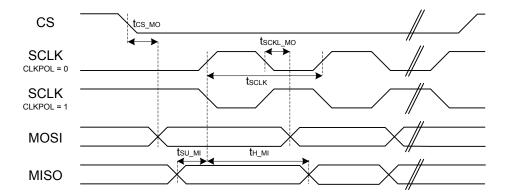

## 4.1.22 USART SPI

## **SPI Master Timing**

Table 4.31. SPI Master Timing

| Parameter                      | Symbol               | Test Condition | Min                          | Тур | Max  | Unit |

|--------------------------------|----------------------|----------------|------------------------------|-----|------|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>    |                | 2 *<br>t <sub>HFPERCLK</sub> | _   | _    | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub>   |                | -19.8                        | _   | 18.9 | ns   |

| SCLK to MOSI <sup>1 3</sup>    | t <sub>SCLK_MO</sub> |                | -10                          | _   | 14.5 | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>SU_MI</sub>   | IOVDD = 1.62 V | 75                           | _   | _    | ns   |

|                                |                      | IOVDD = 3.0 V  | 40                           | _   | _    | ns   |

| MISO hold time <sup>1 3</sup>  | t <sub>H_MI</sub>    |                | -10                          | _   | _    | ns   |

- 1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

- $2.\,t_{HFPERCLK}$  is one period of the selected HFPERCLK.

- 3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ ).

Figure 4.1. SPI Master Timing Diagram

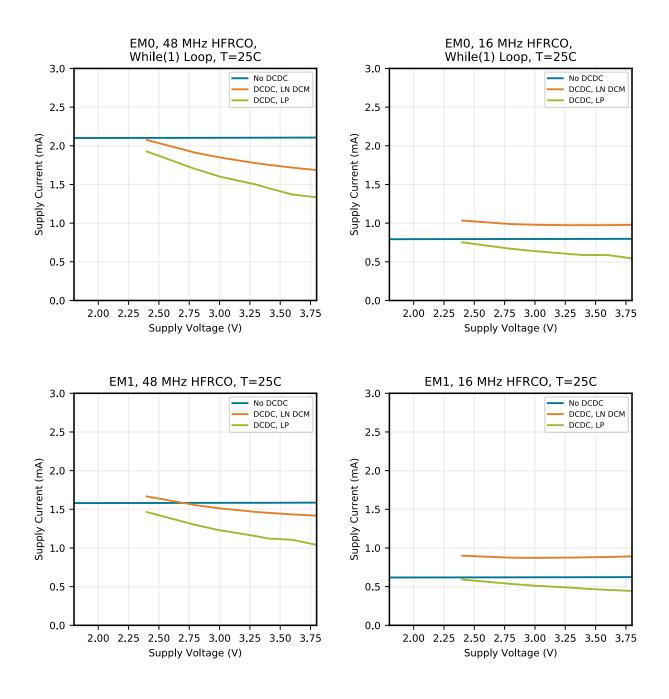

Figure 4.6. EM0 and EM1 Mode Typical Supply Current vs. Supply

Typical supply current for EM2, EM3 and EM4H using standard software libraries from Silicon Laboratories.

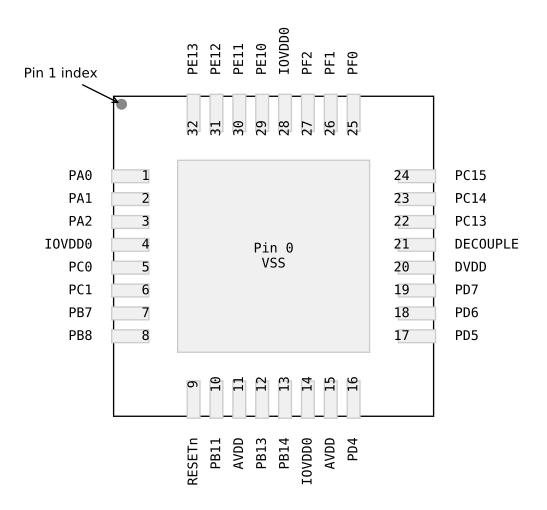

#### 5.13 EFM32TG11B1xx in QFN32 Device Pinout

Figure 5.13. EFM32TG11B1xx in QFN32 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

Table 5.13. EFM32TG11B1xx in QFN32 Device Pinout

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| IOVDD0   | 4<br>14<br>28 | Digital IO power supply 0. | PC0      | 5      | GPIO (5V)   |

| PC1      | 6             | GPIO (5V)                  | PB7      | 7      | GPIO        |

# 5.14 GPIO Functionality Table

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of each GPIO pin, followed by the functionality available on that pin. Refer to 5.15 Alternate Functionality Overview for a list of GPIO locations available for each function.

Table 5.14. GPIO Functionality Table

| GPIO Name |                                                            | Pin Alternate Functi                         | onality / Description                                                               |                                                            |

|-----------|------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|

|           | Analog                                                     | Timers                                       | Communication                                                                       | Other                                                      |

| PA0       | BUSBY BUSAX<br>LCD_SEG13                                   | TIM0_CC0 #0 TIM0_CC1<br>#7 PCNT0_S0IN #4     | US1_RX #5 US3_TX #0<br>LEU0_RX #4 I2C0_SDA<br>#0                                    | CMU_CLK2 #0 PRS_CH0<br>#0 PRS_CH3 #3<br>GPIO_EM4WU0        |

| PA1       | BUSAY BUSBX<br>LCD_SEG14                                   | TIM0_CC0 #7 TIM0_CC1<br>#0 PCNT0_S1IN #4     | US3_RX #0 I2C0_SCL #0                                                               | CMU_CLK1 #0 PRS_CH1<br>#0                                  |

| PA2       | BUSBY BUSAX<br>LCD_SEG15                                   | TIM0_CC2 #0                                  | US1_RX #6 US3_CLK #0                                                                | CMU_CLK0 #0                                                |

| PA3       | BUSAY BUSBX<br>LCD_SEG16                                   | TIM0_CDTI0 #0                                | US3_CS #0 U0_TX #2                                                                  | CMU_CLK2 #1<br>CMU_CLK2 #4<br>CMU_CLKI0 #1 LES_AL-<br>TEX2 |

| PA4       | BUSBY BUSAX<br>LCD_SEG17                                   | TIM0_CDTI1 #0                                | US3_CTS #0 U0_RX #2                                                                 | LES_ALTEX3                                                 |

| PA5       | BUSAY BUSBX<br>LCD_SEG18                                   | TIM0_CDTI2 #0                                | US3_RTS #0 U0_CTS #2                                                                | LES_ALTEX4 ACMP1_O<br>#7                                   |

| PA6       | BUSBY BUSAX<br>LCD_SEG19                                   | WTIM0_CC0 #1                                 | U0_RTS #2                                                                           | PRS_CH6 #0 ACMP0_O<br>#4 GPIO_EM4WU1                       |

| PB3       | BUSAY BUSBX<br>LCD_SEG20 /<br>LCD_COM4                     | TIM1_CC3 #2<br>WTIM0_CC0 #6                  | US2_TX #1 US3_TX #2                                                                 | ACMP0_O #7                                                 |

| PB4       | BUSBY BUSAX<br>LCD_SEG21 /<br>LCD_COM5                     | WTIM0_CC1 #6                                 | US2_RX #1                                                                           |                                                            |

| PB5       | BUSAY BUSBX<br>LCD_SEG22 /<br>LCD_COM6                     | WTIM0_CC2 #6<br>PCNT0_S0IN #6                | US0_RTS #4 US2_CLK<br>#1                                                            |                                                            |

| PB6       | BUSBY BUSAX<br>LCD_SEG23 /<br>LCD_COM7                     | TIM0_CC0 #3<br>PCNT0_S1IN #6                 | US0_CTS #4 US2_CS #1                                                                |                                                            |

| PC0       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #0 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC1 #3<br>PCNT0_S0IN #2                 | CAN0_RX #0 US0_TX #5<br>US1_TX #0 US1_CS #4<br>US2_RTS #0 US3_CS #3<br>I2C0_SDA #4  | LES_CH0 PRS_CH2 #0                                         |

| PC1       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #1 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC2 #3<br>WTIM0_CC0 #7<br>PCNT0_S1IN #2 | CAN0_TX #0 US0_RX #5<br>US1_TX #4 US1_RX #0<br>US2_CTS #0 US3_RTS<br>#1 I2C0_SCL #4 | LES_CH1 PRS_CH3 #0                                         |

| PC2       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #2 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI0 #3<br>WTIM0_CC1 #7                | US1_RX #4 US2_TX #0                                                                 | LES_CH2                                                    |

| PC3       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #3 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI1 #3<br>WTIM0_CC2 #7                | US1_CLK #4 US2_RX #0                                                                | LES_CH3                                                    |

| Port    | Bus      | CH31 | СН30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СНЭ | СН8 | CH7 | СН6 | CH5 | CH4 | СНЗ | CH2 | CH1 | СНО |

|---------|----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|         | OPA3_OUT |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y | BUSAY    |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y | BUSBY    |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3Y | BUSCY    |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | 6∃d |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y | BUSDY    |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

|         | A3_      | Р.   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1X | BUSAX    |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT2X | BUSBX    |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT3X | BUSCX    |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| APORT4X | BUSDX    |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| VD      | ACC      | )_Ol | JT0  | / OI | PA0  | _0L  | JΤ   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y | BUSAY    |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y | BUSBY    |      | PB14 |      | PB12 |      |      |      |      |      | 9Bd  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3Y | BUSCY    |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y | BUSDY    |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

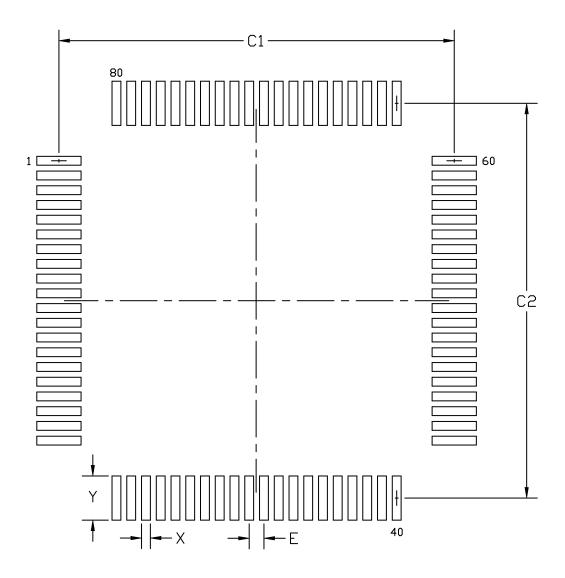

# 6.2 TQFP80 PCB Land Pattern

Figure 6.2. TQFP80 PCB Land Pattern Drawing

Table 6.2. TQFP80 PCB Land Pattern Dimensions

| Dimension | Min   | Max   |  |  |  |  |  |

|-----------|-------|-------|--|--|--|--|--|

| C1        | 13.30 | 13.40 |  |  |  |  |  |

| C2        | 13.30 | 13.40 |  |  |  |  |  |

| Е         | 0.50  | BSC   |  |  |  |  |  |

| Х         | 0.20  | 0.30  |  |  |  |  |  |

| Υ         | 1.40  | 1.50  |  |  |  |  |  |

#### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 6.3 TQFP80 Package Marking

Figure 6.3. TQFP80 Package Marking

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

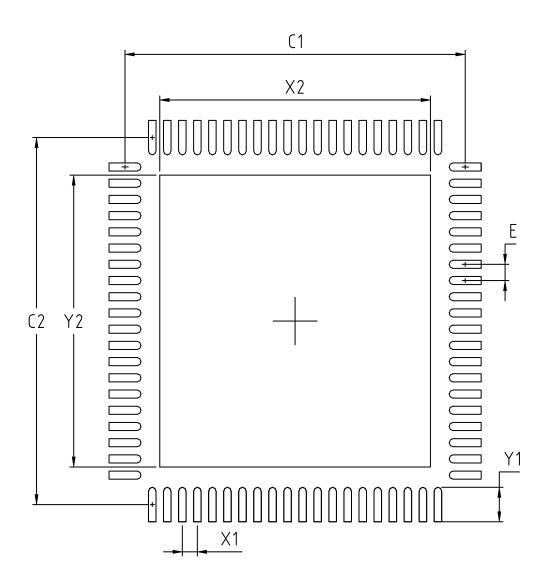

## 7.2 QFN80 PCB Land Pattern

Figure 7.2. QFN80 PCB Land Pattern Drawing

## 7.3 QFN80 Package Marking

Figure 7.3. QFN80 Package Marking

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

# 8. TQFP64 Package Specifications

# 8.1 TQFP64 Package Dimensions

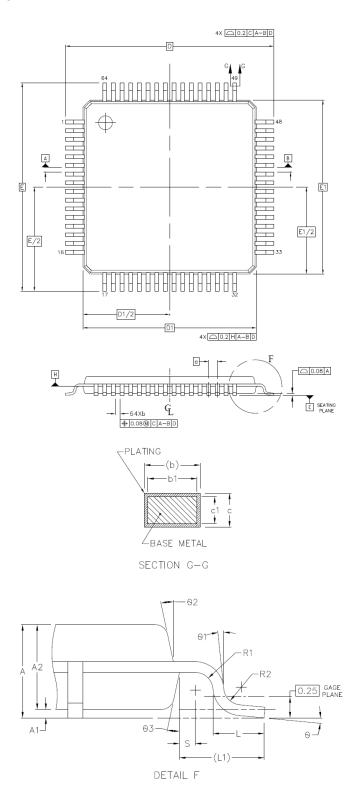

Figure 8.1. TQFP64 Package Drawing

## 10.3 TQFP48 Package Marking

Figure 10.3. TQFP48 Package Marking

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

## 11.3 QFN32 Package Marking

Figure 11.3. QFN32 Package Marking

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.