Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Discontinued at Digi-Key                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT          |

| Number of I/O              | 63                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b520f128gq80-ar |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Timers/Counters

- 2 × 16-bit Timer/Counter

- 3 or 4 Compare/Capture/PWM channels (4 + 4 on one timer instance)

- Dead-Time Insertion on one timer instance

- 2 × 32-bit Timer/Counter

- 32-bit Real Time Counter and Calendar (RTCC)

- 32-bit Ultra Low Energy CRYOTIMER for periodic wakeup from any Energy Mode

- 16-bit Low Energy Timer for waveform generation

- 16-bit Pulse Counter with asynchronous operation

- Watchdog Timer with dedicated RC oscillator

- Low Energy Sensor Interface (LESENSE)

- Autonomous sensor monitoring in Deep Sleep Mode

- Wide range of sensors supported, including LC sensors and capacitive buttons

- Up to 16 inputs

- Ultra efficient Power-on Reset and Brown-Out Detector

- Debug Interface

- 2-pin Serial Wire Debug interface

- 4-pin JTAG interface

- Micro Trace Buffer (MTB)

Pre-Programmed UART Bootloader

# Wide Operating Range

- 1.8 V to 3.8 V single power supply

- Integrated DC-DC, down to 1.8 V output with up to 200 mA load current for system

- Standard (-40  $^\circ C$  to 85  $^\circ C$   $T_A)$  and Extended (-40  $^\circ C$  to 125  $^\circ C$   $T_J)$  temperature grades available

- Packages

- QFN32 (5x5 mm)

- TQFP48 (7x7 mm)

- QFN64 (9x9 mm)

- TQFP64 (10x10 mm)

- QFN80 (9x9 mm)

- TQFP80 (12x12 mm)

#### 3.2 Power

The EFM32TG11 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. An optional integrated DC-DC buck regulator can be utilized to further reduce the current consumption. The DC-DC regulator requires one external inductor and one external capacitor.

The EFM32TG11 device family includes support for internal supply voltage scaling, as well as two different power domain groups for peripherals. These enhancements allow for further supply current reductions and lower overall power consumption.

AVDD and VREGVDD need to be 1.8 V or higher for the MCU to operate across all conditions; however the rest of the system will operate down to 1.62 V, including the digital supply and I/O. This means that the device is fully compatible with 1.8 V components. Running from a sufficiently high supply, the device can use the DC-DC to regulate voltage not only for itself, but also for other PCB components, supplying up to a total of 200 mA.

#### 3.2.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to turn off the power to unused RAM blocks, and it contains control registers for the DC-DC regulator and the Voltage Monitor (VMON). The VMON is used to monitor multiple supply voltages. It has multiple channels which can be programmed individually by the user to determine if a sensed supply has fallen below a chosen threshold.

#### 3.2.2 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents and provides up to 90% efficiency in energy modes EM0, EM1, EM2 and EM3, and can supply up to 200 mA to the device and surrounding PCB components. Protection features include programmable current limiting, short-circuit protection, and dead-time protection. The DC-DC converter may also enter bypass mode when the input voltage is too low for efficient operation. In bypass mode, the DC-DC input supply is internally connected directly to its output through a low resistance switch. Bypass mode also supports in-rush current limiting to prevent input supply voltage droops due to excessive output current transients.

#### 3.2.3 EM2 and EM3 Power Domains

The EFM32TG11 has three independent peripheral power domains for use in EM2 and EM3. Two of these domains are dynamic and can be shut down to save energy. Peripherals associated with the two dynamic power domains are listed in Table 3.1 EM2 and EM3 Peripheral Power Subdomains on page 11. If all of the peripherals in a peripheral power domain are unused, the power domain for that group will be powered off in EM2 and EM3, reducing the overall current consumption of the device. Other EM2, EM3, and EM4-capable peripherals and functions not listed in the table below reside on the primary power domain, which is always on in EM2 and EM3.

| Peripheral Power Domain 1 | Peripheral Power Domain 2 |

|---------------------------|---------------------------|

| ACMP0                     | ACMP1                     |

| PCNT0                     | CSEN                      |

| ADC0                      | VDAC0                     |

| LETIMER0                  | LEUART0                   |

| LESENSE                   | 12C0                      |

| APORT                     | 12C1                      |

| -                         | IDAC                      |

| -                         | LCD                       |

#### Table 3.1. EM2 and EM3 Peripheral Power Subdomains

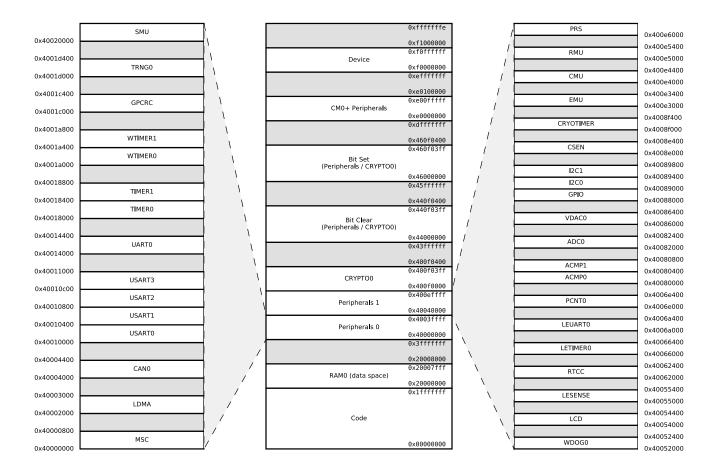

Figure 3.3. EFM32TG11 Memory Map — Peripherals

#### 3.12 Configuration Summary

The features of the EFM32TG11 are a subset of the feature set described in the device reference manual. The table below describes device specific implementation of the features. Remaining modules support full configuration.

| Table 3.2. | Configuration | Summary |

|------------|---------------|---------|

|------------|---------------|---------|

| Module  | Configuration               | Pin Connections                 |

|---------|-----------------------------|---------------------------------|

| USART0  | IrDA, SmartCard             | US0_TX, US0_RX, US0_CLK, US0_CS |

| USART1  | I <sup>2</sup> S, SmartCard | US1_TX, US1_RX, US1_CLK, US1_CS |

| USART2  | IrDA, SmartCard, High-Speed | US2_TX, US2_RX, US2_CLK, US2_CS |

| USART3  | I <sup>2</sup> S, SmartCard | US3_TX, US3_RX, US3_CLK, US3_CS |

| TIMER0  | with DTI                    | TIM0_CC[2:0], TIM0_CDTI[2:0]    |

| TIMER1  | -                           | TIM1_CC[3:0]                    |

| WTIMER0 | with DTI                    | WTIM0_CC[2:0], WTIM0_CDTI[2:0]  |

| WTIMER1 | -                           | WTIM1_CC[3:0]                   |

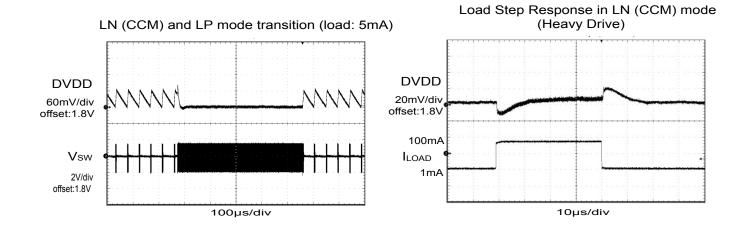

## 4.1.4 DC-DC Converter

Test conditions: L\_DCDC=4.7 µH (Murata LQH3NPN4R7MM0L), C\_DCDC=4.7 µF (Samsung CL10B475KQ8NQNC), V\_DCDC\_I=3.3 V, V\_DCDC\_O=1.8 V, I\_DCDC\_LOAD=50 mA, Heavy Drive configuration, F\_DCDC\_LN=7 MHz, unless otherwise indicated.

### Table 4.4. DC-DC Converter

| Parameter                                           | Symbol              | Test Condition                                                                                                                  | Min | Тур | Max                         | Unit |

|-----------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                 | V <sub>DCDC_I</sub> | Bypass mode, I <sub>DCDC_LOAD</sub> = 50<br>mA                                                                                  | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V output, $I_{DCDC\_LOAD}$ = 100 mA, or<br>Low power (LP) mode, 1.8 V output, $I_{DCDC\_LOAD}$ = 10 mA | 2.4 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V out-<br>put, I <sub>DCDC_LOAD</sub> = 200 mA                                                         | 2.6 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Output voltage programma-<br>ble range <sup>1</sup> | V <sub>DCDC_0</sub> |                                                                                                                                 | 1.8 | _   | V <sub>VREGVDD</sub>        | V    |

| Regulation DC accuracy                              | ACC <sub>DC</sub>   | Low Noise (LN) mode, 1.8 V tar-<br>get output                                                                                   | TBD | _   | TBD                         | V    |

| Regulation window <sup>4</sup>                      | WIN <sub>REG</sub>  | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 75 µA                | TBD | _   | TBD                         | V    |

|                                                     |                     | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 10 mA                | TBD | _   | TBD                         | V    |

| Steady-state output ripple                          | V <sub>R</sub>      |                                                                                                                                 | _   | 3   | —                           | mVpp |

| Output voltage under/over-<br>shoot                 | V <sub>OV</sub>     | CCM Mode (LNFORCECCM <sup>3</sup> = 1), Load changes between 0 mA and 100 mA                                                    | _   | 25  | TBD                         | mV   |

|                                                     |                     | DCM Mode (LNFORCECCM <sup>3</sup> = 0), Load changes between 0 mA and 10 mA                                                     | _   | 45  | TBD                         | mV   |

|                                                     |                     | Overshoot during LP to LN<br>CCM/DCM mode transitions com-<br>pared to DC level in LN mode                                      | _   | 200 | -                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>CCM (LNFORCECCM <sup>3</sup> = 1) mode<br>transitions compared to DC level<br>in LN mode      | _   | 40  | _                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>DCM (LNFORCECCM <sup>3</sup> = 0) mode<br>transitions compared to DC level<br>in LN mode      | _   | 100 | _                           | mV   |

| DC line regulation                                  | V <sub>REG</sub>    | Input changes between V <sub>VREGVDD_MAX</sub> and 2.4 V                                                                        | _   | 0.1 | -                           | %    |

| DC load regulation                                  | I <sub>REG</sub>    | Load changes between 0 mA and 100 mA in CCM mode                                                                                | —   | 0.1 | _                           | %    |

#### 4.1.6 Current Consumption

## 4.1.6.1 Current Consumption 3.3 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 3.3 V. T = 25 °C. DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

## Table 4.6. Current Consumption 3.3 V without DC-DC Converter

| Parameter                                                              | Symbol                 | Test Condition                                                       | Min | Тур  | Max | Unit   |

|------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-              | I <sub>ACTIVE</sub>    | 48 MHz crystal, CPU running while loop from flash                    | _   | 45   | _   | µA/MHz |

| abled                                                                  |                        | 48 MHz HFRCO, CPU running while loop from flash                      |     | 44   | TBD | µA/MHz |

|                                                                        |                        | 48 MHz HFRCO, CPU running<br>Prime from flash                        |     | 57   |     | µA/MHz |

|                                                                        |                        | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash                |     | 71   | _   | µA/MHz |

|                                                                        |                        | 32 MHz HFRCO, CPU running while loop from flash                      |     | 45   | _   | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO, CPU running while loop from flash                      |     | 46   | TBD | µA/MHz |

|                                                                        |                        | 16 MHz HFRCO, CPU running while loop from flash                      |     | 50   |     | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO, CPU running while loop from flash                       | —   | 161  | TBD | µA/MHz |

| Current consumption in EM0 mode with all peripherals dis-              | I <sub>ACTIVE_VS</sub> | 19 MHz HFRCO, CPU running while loop from flash                      | —   | 41   | _   | µA/MHz |

| abled and voltage scaling enabled                                      |                        | 1 MHz HFRCO, CPU running while loop from flash                       | _   | 145  | _   | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1</sub>       | 48 MHz crystal                                                       | —   | 34   | _   | µA/MHz |

| mode with all peripherals disabled                                     |                        | 48 MHz HFRCO                                                         | —   | 33   | TBD | µA/MHz |

|                                                                        |                        | 32 MHz HFRCO                                                         | —   | 34   |     | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO                                                         | —   | 35   | TBD | µA/MHz |

|                                                                        |                        | 16 MHz HFRCO                                                         | —   | 39   | _   | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO                                                          | —   | 150  | TBD | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1_VS</sub>    | 19 MHz HFRCO                                                         | —   | 32   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled |                        | 1 MHz HFRCO                                                          | _   | 136  |     | µA/MHz |

| Current consumption in EM2<br>mode, with voltage scaling               | I <sub>EM2_VS</sub>    | Full 32 kB RAM retention and RTCC running from LFXO                  |     | 1.48 | _   | μA     |

| enabled                                                                |                        | Full 32 kB RAM retention and<br>RTCC running from LFRCO              | _   | 1.86 |     | μΑ     |

|                                                                        |                        | 8 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup> |     | 1.59 | TBD | μΑ     |

| Current consumption in EM3<br>mode, with voltage scaling<br>enabled    | I <sub>EM3_VS</sub>    | Full 32 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO   |     | 1.23 | TBD | μA     |

| Parameter                                                                              | Symbol               | Test Condition                                                                                          | Min | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption in<br>EM4H mode, with voltage                                      | I <sub>EM4H_VS</sub> | 128 byte RAM retention, RTCC running from LFXO                                                          | —   | 0.82 |     | μA   |

| scaling enabled                                                                        |                      | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO                                              | —   | 0.45 | _   | μA   |

|                                                                                        |                      | 128 byte RAM retention, no RTCC                                                                         | —   | 0.45 | TBD | μA   |

| Current consumption in EM4S mode                                                       | I <sub>EM4S</sub>    | No RAM retention, no RTCC                                                                               | —   | 0.07 | TBD | μA   |

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled | IPD1_VS              | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>1</sup> | _   | 0.18 | _   | μA   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled | IPD2_VS              | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>1</sup> | _   | 0.18 | _   | μA   |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.3 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

2. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

| Parameter        | Symbol                  | Test Condition                        | Min | Тур | Мах | Unit |

|------------------|-------------------------|---------------------------------------|-----|-----|-----|------|

| Frequency limits | f <sub>HFRCO_BAND</sub> | FREQRANGE = 0, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 3, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 6, FINETUNIN-<br>GEN = 0  | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 7, FINETUNIN-<br>GEN = 0  | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 8, FINETUNIN-<br>GEN = 0  | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 10, FINETUNIN-<br>GEN = 0 | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 11, FINETUNIN-<br>GEN = 0 | TBD |     | TBD | MHz  |

|                  |                         | FREQRANGE = 12, FINETUNIN-<br>GEN = 0 | TBD | _   | TBD | MHz  |

|                  |                         | FREQRANGE = 13, FINETUNIN-<br>GEN = 0 | TBD | _   | TBD | MHz  |

# 4.1.14 Analog Comparator (ACMP)

| Parameter                                                           | Symbol              | Test Condition                                               | Min | Тур | Мах                         | Unit |

|---------------------------------------------------------------------|---------------------|--------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                                 | V <sub>ACMPIN</sub> | ACMPVDD =<br>ACMPn_CTRL_PWRSEL <sup>1</sup>                  | _   | _   | V <sub>ACMPVDD</sub>        | V    |

| Supply voltage                                                      | VACMPVDD            | $BIASPROG^4 \le 0x10 \text{ or } FULL-BIAS^4 = 0$            | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                                     |                     | $0x10 < BIASPROG^4 \le 0x20$ and FULLBIAS <sup>4</sup> = 1   | 2.1 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Active current not including                                        | I <sub>ACMP</sub>   | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                          | —   | 50  | —                           | nA   |

| voltage reference <sup>2</sup>                                      |                     | $BIASPROG^{4} = 0x10, FULLBIAS^{4} = 0$                      |     | 306 | _                           | nA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1   |     | 6.5 | —                           | μA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1   | _   | 74  | TBD                         | μA   |

| Current consumption of inter-<br>nal voltage reference <sup>2</sup> | IACMPREF            | VLP selected as input using 2.5 V<br>Reference / 4 (0.625 V) | _   | 50  | _                           | nA   |

|                                                                     |                     | VLP selected as input using VDD                              | _   | 20  | _                           | nA   |

|                                                                     |                     | VBDIV selected as input using 1.25 V reference / 1           | _   | 4.1 | _                           | μA   |

|                                                                     |                     | VADIV selected as input using VDD/1                          |     | 2.4 | -                           | μA   |

# Table 4.21. Analog Comparator (ACMP)

# 4.1.15 Digital to Analog Converter (VDAC)

DRIVESTRENGTH = 2 unless otherwise specified. Primary VDAC output.

| Table 4.22. | Digital to | Analog | Converter | (VDAC) |

|-------------|------------|--------|-----------|--------|

|-------------|------------|--------|-----------|--------|

| Parameter                                                               | Symbol                  | Test Condition                                                                                                                                                                    | Min                | Тур  | Max               | Unit   |

|-------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------------------|--------|

| Output voltage                                                          | V <sub>DACOUT</sub>     | Single-Ended                                                                                                                                                                      | 0                  | _    | V <sub>VREF</sub> | V      |

|                                                                         |                         | Differential <sup>2</sup>                                                                                                                                                         | -V <sub>VREF</sub> | _    | V <sub>VREF</sub> | V      |

| Current consumption includ-<br>ing references (2 channels) <sup>1</sup> | IDAC                    | 500 ksps, 12-bit, DRIVES-<br>TRENGTH = 2, REFSEL = 4                                                                                                                              |                    | 396  | _                 | μA     |

|                                                                         |                         | 44.1 ksps, 12-bit, DRIVES-<br>TRENGTH = 1, REFSEL = 4                                                                                                                             | —                  | 72   | -                 | μA     |

|                                                                         |                         | 200 Hz refresh rate, 12-bit Sam-<br>ple-Off mode in EM2, DRIVES-<br>TRENGTH = 2, BGRREQTIME =<br>1, EM2REFENTIME = 9, REFSEL<br>= 4, SETTLETIME = 0x0A, WAR-<br>MUPTIME = 0x02    |                    | 2    | _                 | μΑ     |

| Current from HFPERCLK <sup>4</sup>                                      | IDAC_CLK                |                                                                                                                                                                                   | _                  | 5.8  | —                 | µA/MHz |

| Sample rate                                                             | SR <sub>DAC</sub>       |                                                                                                                                                                                   | _                  | _    | 500               | ksps   |

| DAC clock frequency                                                     | f <sub>DAC</sub>        |                                                                                                                                                                                   | _                  | _    | 1                 | MHz    |

| Conversion time                                                         | t <sub>DACCONV</sub>    | f <sub>DAC</sub> = 1MHz                                                                                                                                                           | 2                  | _    | _                 | μs     |

| Settling time                                                           | t <sub>DACSETTLE</sub>  | 50% fs step settling to 5 LSB                                                                                                                                                     | _                  | 2.5  | —                 | μs     |

| Startup time                                                            | t <sub>DACSTARTUP</sub> | Enable to 90% fs output, settling to 10 LSB                                                                                                                                       | _                  | _    | 12                | μs     |

| Output impedance                                                        | R <sub>OUT</sub>        | DRIVESTRENGTH = 2, 0.4 V $\leq$<br>V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -8 mA $<$<br>I <sub>OUT</sub> $<$ 8 mA, Full supply range                                    | _                  | 2    | _                 | Ω      |

|                                                                         |                         | DRIVESTRENGTH = 0 or 1, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -400 µA $<$<br>I <sub>OUT</sub> $<$ 400 µA, Full supply range                           | _                  | 2    | _                 | Ω      |

|                                                                         |                         | $\label{eq:DRIVESTRENGTH} \begin{array}{l} DRIVESTRENGTH = 2, \ 0.1 \ V \leq \\ V_{OUT} \leq V_{OPA} - 0.1 \ V, \ -2 \ mA < \\ I_{OUT} < 2 \ mA, \ Full supply range \end{array}$ | _                  | 2    | _                 | Ω      |

|                                                                         |                         | DRIVESTRENGTH = 0 or 1, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -100 µA $<$<br>I <sub>OUT</sub> $<$ 100 µA, Full supply range                           |                    | 2    | -                 | Ω      |

| Power supply rejection ratio <sup>6</sup>                               | PSRR                    | Vout = 50% fs. DC                                                                                                                                                                 | _                  | 65.5 | _                 | dB     |

| Parameter                                                               | Symbol         | Test Condition                                                                                     | Min | Тур  | Max | Unit   |

|-------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Supply current, continuous<br>conversions, WARMUP-<br>MODE=KEEPCSENWARM | ICSEN_ACTIVE   | SAR or Delta Modulation conver-<br>sions of 33 pF capacitor,<br>CS0CG=0 (Gain = 10x), always<br>on | _   | 90.5 | _   | μA     |

| HFPERCLK supply current                                                 | ICSEN_HFPERCLK | Current contribution from<br>HFPERCLK when clock to CSEN<br>block is enabled.                      | _   | 2.25 | _   | µA/MHz |

# Note:

Current is specified with a total external capacitance of 33 pF per channel. Average current is dependent on how long the module is actively sampling channels within the scan period, and scales with the number of samples acquired. Supply current for a specific application can be estimated by multiplying the current per sample by the total number of samples per period (total\_current = single\_sample\_current \* (number\_of\_channels \* accumulation)).

# 4.1.21.2 I2C Fast-mode (Fm)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Мах | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|-----|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | _   | 400 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 1.3 | —   | _   | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.6 | —   | _   | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 100 | _   | _   | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD_DAT</sub> |                | 100 | —   | 900 | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.6 | _   | _   | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.6 |     |     | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.6 | _   |     | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 1.3 | _   | —   | μs   |

# Table 4.29. I2C Fast-mode (Fm)<sup>1</sup>

Note:

1. For CLHR set to 1 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Fast-mode, refer to the I2C chapter in the reference manual.

3. The maximum SDA hold time (t<sub>HD,DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

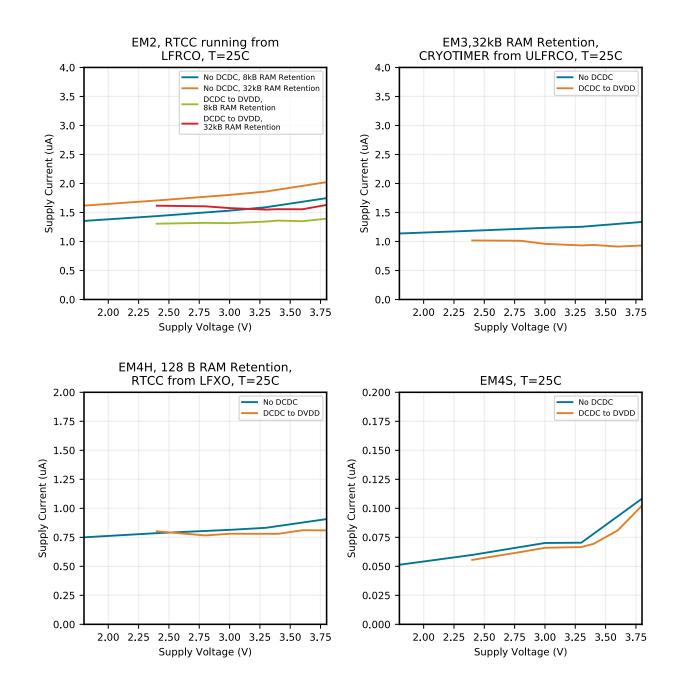

Figure 4.7. EM2, EM3, EM4H and EM4S Typical Supply Current vs. Supply

Figure 4.9. DC-DC Converter Transition Waveforms

| Pin Name | Pin(s) | Description                                                                                              | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|----------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                                                                                                     | PC5      | 14       | GPIO                                                                                                                                                                                                        |

| PB7      | 15     | GPIO                                                                                                     | PB8      | 16       | GPIO                                                                                                                                                                                                        |

| PA8      | 17     | GPIO                                                                                                     | PA9      | 18       | GPIO                                                                                                                                                                                                        |

| PA10     | 19     | GPIO                                                                                                     | RESETn   | 20       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21     | GPIO                                                                                                     | AVDD     | 23<br>27 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 24     | GPIO                                                                                                     | PB14     | 25       | GPIO                                                                                                                                                                                                        |

| PD0      | 28     | GPIO (5V)                                                                                                | PD1      | 29       | GPIO                                                                                                                                                                                                        |

| PD2      | 30     | GPIO (5V)                                                                                                | PD3      | 31       | GPIO                                                                                                                                                                                                        |

| PD4      | 32     | GPIO                                                                                                     | PD5      | 33       | GPIO                                                                                                                                                                                                        |

| PD6      | 34     | GPIO                                                                                                     | PD7      | 35       | GPIO                                                                                                                                                                                                        |

| PD8      | 36     | GPIO                                                                                                     | PC6      | 37       | GPIO                                                                                                                                                                                                        |

| PC7      | 38     | GPIO                                                                                                     | DVDD     | 39       | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PC8      | 41       | GPIO                                                                                                                                                                                                        |

| PC9      | 42     | GPIO                                                                                                     | PC10     | 43       | GPIO (5V)                                                                                                                                                                                                   |

| PC11     | 44     | GPIO (5V)                                                                                                | PC12     | 45       | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 46     | GPIO (5V)                                                                                                | PC14     | 47       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 48     | GPIO (5V)                                                                                                | PF0      | 49       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50     | GPIO (5V)                                                                                                | PF2      | 51       | GPIO                                                                                                                                                                                                        |

| PF3      | 52     | GPIO                                                                                                     | PF4      | 53       | GPIO                                                                                                                                                                                                        |

| PF5      | 54     | GPIO                                                                                                     | PE8      | 57       | GPIO                                                                                                                                                                                                        |

| PE9      | 58     | GPIO                                                                                                     | PE10     | 59       | GPIO                                                                                                                                                                                                        |

| PE11     | 60     | GPIO                                                                                                     | PE12     | 61       | GPIO                                                                                                                                                                                                        |

| PE13     | 62     | GPIO                                                                                                     | PE14     | 63       | GPIO                                                                                                                                                                                                        |

| PE15     | 64     | GPIO                                                                                                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

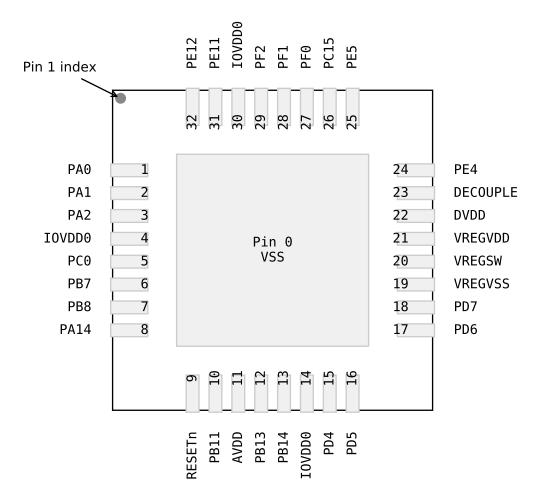

## Figure 5.12. EFM32TG11B5xx in QFN32 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.12. EFM32TG11B5xx in QFN32 Device Pinout |

|--------------------------------------------------|

|--------------------------------------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0<br>19       | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| IOVDD0   | 4<br>14<br>30 | Digital IO power supply 0. | PC0      | 5      | GPIO (5V)   |

| PB7      | 6             | GPIO                       | PB8      | 7      | GPIO        |

## Figure 5.13. EFM32TG11B1xx in QFN32 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.13. EFM32TG11B1xx in QFN32 Devic | e Pinout |

|------------------------------------------|----------|

|------------------------------------------|----------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| IOVDD0   | 4<br>14<br>28 | Digital IO power supply 0. | PC0      | 5      | GPIO (5V)   |

| PC1      | 6             | GPIO (5V)                  | PB7      | 7      | GPIO        |

| Pin Name | Pin(s) | Description           | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|-----------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB8      | 8      | GPIO                  | RESETn   | 9        | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 10     | GPIO                  | AVDD     | 11<br>15 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 12     | GPIO                  | PB14     | 13       | GPIO                                                                                                                                                                                                        |

| PD4      | 16     | GPIO                  | PD5      | 17       | GPIO                                                                                                                                                                                                        |

| PD6      | 18     | GPIO                  | PD7      | 19       | GPIO                                                                                                                                                                                                        |

| DVDD     | 20     | Digital power supply. | DECOUPLE | 21       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PC13     | 22     | GPIO (5V)             | PC14     | 23       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 24     | GPIO (5V)             | PF0      | 25       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 26     | GPIO (5V)             | PF2      | 27       | GPIO                                                                                                                                                                                                        |

| PE10     | 29     | GPIO                  | PE11     | 30       | GPIO                                                                                                                                                                                                        |

| PE12     | 31     | GPIO                  | PE13     | 32       | GPIO                                                                                                                                                                                                        |

| Note:    |        | ,                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Alternate     | LOC                                     | CATION                      |                                                                                                                                                            |  |  |  |  |  |  |

|---------------|-----------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Functionality | 0 - 3                                   | 4 - 7                       | Description                                                                                                                                                |  |  |  |  |  |  |

| U0_TX         | 2: PA3<br>3: PC14                       | 4: PC4<br>5: PF1<br>6: PD7  | UART0 Transmit output. Also used as receive input in half duplex communication.                                                                            |  |  |  |  |  |  |

| US0_CLK       | 0: PE12<br>1: PE5<br>2: PC9<br>3: PC15  | 4: PB13<br>5: PA12          | USART0 clock input / output.                                                                                                                               |  |  |  |  |  |  |

| US0_CS        | 0: PE13<br>1: PE4<br>2: PC8<br>3: PC14  | 4: PB14<br>5: PA13          | USART0 chip select input / output.                                                                                                                         |  |  |  |  |  |  |

| US0_CTS       | 0: PE14<br>2: PC7<br>3: PC13            | 4: PB6<br>5: PB11           | USART0 Clear To Send hardware flow control input.                                                                                                          |  |  |  |  |  |  |

| US0_RTS       | 0: PE15<br>2: PC6<br>3: PC12            | 4: PB5<br>5: PD6            | USART0 Request To Send hardware flow control output.                                                                                                       |  |  |  |  |  |  |

| US0_RX        | 0: PE11<br>1: PE6<br>2: PC10<br>3: PE12 | 4: PB8<br>5: PC1            | USART0 Asynchronous Receive.<br>USART0 Synchronous mode Master Input / Slave Output (MISO).                                                                |  |  |  |  |  |  |

| US0_TX        | 0: PE10<br>1: PE7<br>2: PC11<br>3: PE13 | 4: PB7<br>5: PC0            | USART0 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART0 Synchronous mode Master Output / Slave Input (MOSI). |  |  |  |  |  |  |

| US1_CLK       | 0: PB7<br>1: PD2<br>2: PF0<br>3: PC15   | 4: PC3<br>5: PB11<br>6: PE5 | USART1 clock input / output.                                                                                                                               |  |  |  |  |  |  |

| US1_CS        | 0: PB8<br>1: PD3<br>2: PF1<br>3: PC14   | 4: PC0<br>5: PE4            | USART1 chip select input / output.                                                                                                                         |  |  |  |  |  |  |

| US1_CTS       | 1: PD4<br>2: PF3<br>3: PC6              | 4: PC12<br>5: PB13          | USART1 Clear To Send hardware flow control input.                                                                                                          |  |  |  |  |  |  |

| US1_RTS       | 1: PD5<br>2: PF4<br>3: PC7              | 4: PC13<br>5: PB14          | USART1 Request To Send hardware flow control output.                                                                                                       |  |  |  |  |  |  |

| US1_RX        | 0: PC1<br>1: PD1<br>2: PD6              | 4: PC2<br>5: PA0<br>6: PA2  | USART1 Asynchronous Receive.<br>USART1 Synchronous mode Master Input / Slave Output (MISO).                                                                |  |  |  |  |  |  |

| US1_TX        | 0: PC0<br>1: PD0<br>2: PD7              | 4: PC1<br>5: PF2<br>6: PA14 | USART1 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART1 Synchronous mode Master Output / Slave Input (MOSI). |  |  |  |  |  |  |

# EFM32TG11 Family Data Sheet Pin Definitions

| Port    | Bus                   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | СНО |

|---------|-----------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| VD      | VDAC0_OUT1 / OPA1_OUT |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y | BUSAY                 |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y | BUSBY                 |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3Y | BUSCY                 |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y | BUSDY                 |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

## **Simplicity Studio**

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

Support and Community community.silabs.com

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com