Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Discontinued at Digi-Key                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT          |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-WFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-QFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b520f128im32-ar |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 General Purpose Input/Output (GPIO)

EFM32TG11 has up to 67 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

### 3.4 Clocking

## 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32TG11. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

### 3.4.2 Internal and External Oscillators

The EFM32TG11 supports two crystal oscillators and fully integrates four RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 4 to 48 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range. When crystal accuracy is not required, it can be operated in free-running mode at a number of factory-calibrated frequencies. A digital phase-locked loop (DPLL) feature allows the HFRCO to achieve higher accuracy and stability by referencing other available clock sources such as LFXO and HFXO.

- An integrated auxilliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC with a wide frequency range.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

### 3.5 Counters/Timers and PWM

### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

### 3.5.2 Wide Timer/Counter (WTIMER)

WTIMER peripherals function just as TIMER peripherals, but are 32 bits wide. They keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each WTIMER is a 32-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the WTIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit WTIMER\_0 only.

### 3.5.3 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes down to EM4H.

## 3.5.4 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

## 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

## 3.5.6 Pulse Counter (PCNT)

The Pulse Counter (PCNT) peripheral can be used for counting pulses on a single input or to decode quadrature encoded inputs. The clock for PCNT is selectable from either an external source on pin PCTNn\_S0IN or from an internal timing reference, selectable from among any of the internal oscillators, except the AUXHFRCO. The module may operate in energy mode EM0 Active, EM1 Sleep, EM2 Deep Sleep, and EM3 Stop.

### 3.5.7 Watchdog Timer (WDOG)

The watchdog timer can act both as an independent watchdog or as a watchdog synchronous with the CPU clock. It has windowed monitoring capabilities, and can generate a reset or different interrupts depending on the failure mode of the system. The watchdog can also monitor autonomous systems driven by PRS.

### 3.6 Communications and Other Digital Peripherals

### 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous/Asynchronous Receiver/Transmitter is a flexible serial I/O module. It supports full duplex asynchronous UART communication with hardware flow control as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with devices supporting:

- ISO7816 SmartCards

- IrDA

- I<sup>2</sup>S

### 3.6.2 Universal Asynchronous Receiver/Transmitter (UART)

The Universal Asynchronous Receiver/Transmitter is a subset of the USART module, supporting full duplex asynchronous UART communication with hardware flow control and RS-485.

### 3.6.3 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup> provides two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud. The LEUART includes all necessary hardware to make asynchronous serial communication possible with a minimum of software intervention and energy consumption.

## **3.6.4** Inter-Integrated Circuit Interface (I<sup>2</sup>C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C bus. It is capable of acting as both a master and a slave and supports multi-master buses. Standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also available, allowing implementation of an SMBus-compliant system. The interface provided to software by the I<sup>2</sup>C module allows precise timing control of the transmission process and highly automated transfers. Automatic recognition of slave addresses is provided in active and low energy modes.

## 3.10 Core and Memory

## 3.10.1 Processor Core

The ARM Cortex-M processor includes a 32-bit RISC processor integrating the following features and tasks in the system:

- ARM Cortex-M0+ RISC processor

- Memory Protection Unit (MPU) supporting up to 8 memory segments

- Micro-Trace Buffer (MTB)

- Up to 128 kB flash program memory

- · Up to 32 kB RAM data memory

- · Configuration and event handling of all modules

- · 2-pin Serial-Wire debug interface

## 3.10.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block, whereas the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

## 3.10.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling so-phisticated operations to be implemented.

### 3.10.4 Bootloader

All devices come pre-programmed with a UART bootloader. This bootloader resides in flash and can be erased if it is not needed. More information about the bootloader protocol and usage can be found in *AN0003: UART Bootloader*. Application notes can be found on the Silicon Labs website (www.silabs.com/32bit-appnotes) or within Simplicity Studio in the [**Documentation**] area.

| Parameter                                         | Symbol                | Test Condition                                             | Min | Тур   | Max | Unit   |

|---------------------------------------------------|-----------------------|------------------------------------------------------------|-----|-------|-----|--------|

| ADC clock frequency                               | f <sub>ADCCLK</sub>   |                                                            | _   | _     | 16  | MHz    |

| Throughput rate                                   | <b>f</b> ADCRATE      |                                                            | _   | _     | 1   | Msps   |

| Conversion time <sup>1</sup>                      | t <sub>ADCCONV</sub>  | 6 bit                                                      | _   | 7     | _   | cycles |

|                                                   |                       | 8 bit                                                      | _   | 9     | _   | cycles |

|                                                   |                       | 12 bit                                                     | —   | 13    | _   | cycles |

| Startup time of reference generator and ADC core  | t <sub>ADCSTART</sub> | WARMUPMODE <sup>4</sup> = NORMAL                           | —   | —     | 5   | μs     |

| generator and ADC core                            |                       | WARMUPMODE <sup>4</sup> = KEEPIN-<br>STANDBY               | _   |       | 2   | μs     |

|                                                   |                       | WARMUPMODE <sup>4</sup> = KEEPINSLO-<br>WACC               | _   |       | 1   | μs     |

| SNDR at 1Msps and f <sub>IN</sub> =<br>10kHz      | SNDR <sub>ADC</sub>   | Internal reference <sup>7</sup> , differential measurement | TBD | 67    | _   | dB     |

|                                                   |                       | External reference <sup>6</sup> , differential measurement | _   | 68    | _   | dB     |

| Spurious-free dynamic range (SFDR)                | SFDR <sub>ADC</sub>   | 1 MSamples/s, 10 kHz full-scale sine wave                  | _   | 75    | _   | dB     |

| Differential non-linearity (DNL)                  | DNL <sub>ADC</sub>    | 12 bit resolution, No missing co-<br>des                   | TBD |       | TBD | LSB    |

| Integral non-linearity (INL),<br>End point method | INL <sub>ADC</sub>    | 12 bit resolution                                          | TBD |       | TBD | LSB    |

| Offset error                                      | VADCOFFSETERR         |                                                            | TBD | 0     | TBD | LSB    |

| Gain error in ADC                                 | VADCGAIN              | Using internal reference                                   | _   | -0.2  | TBD | %      |

|                                                   |                       | Using external reference                                   | _   | -1    | _   | %      |

| Temperature sensor slope                          | V <sub>TS_SLOPE</sub> |                                                            | _   | -1.84 | _   | mV/°C  |

Note:

1. Derived from ADCCLK.

2. PSRR is referenced to AVDD when ANASW=0 and to DVDD when ANASW=1 in EMU\_PWRCTRL.

3. In ADCn\_BIASPROG register.

4. In ADCn CNTL register.

5. The absolute voltage allowed at any ADC input is dictated by the power rail supplied to on-chip circuitry, and may be lower than the effective full scale voltage. All ADC inputs are limited to the ADC supply (AVDD or DVDD depending on EMU PWRCTRL ANASW). Any ADC input routed through the APORT will further be limited by the IOVDD supply to the pin.

6. External reference is 1.25 V applied externally to ADCnEXTREFP, with the selection CONF in the SINGLECTRL\_REF or SCANCTRL\_REF register field and VREFP in the SINGLECTRLX\_VREFSEL or SCANCTRLX\_VREFSEL field. The differential input range with this configuration is ± 1.25 V.

7. Internal reference option used corresponds to selection 2V5 in the SINGLECTRL\_REF or SCANCTRL\_REF register field. The differential input range with this configuration is ± 1.25 V. Typical value is characterized using full-scale sine wave input. Minimum value is production-tested using sine wave input at 1.5 dB lower than full scale.

| Parameter                                    | Symbol             | Test Condition                                                                               | Min | Тур   | Мах | Unit |

|----------------------------------------------|--------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Slew rate <sup>5</sup>                       | SR                 | DRIVESTRENGTH = 3,<br>INCBW=1 <sup>3</sup>                                                   | _   | 4.7   | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 3,<br>INCBW=0                                                                | _   | 1.5   | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=1 <sup>3</sup>                                                   | _   | 1.27  | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 2,<br>INCBW=0                                                                | _   | 0.42  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.17  | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 1,<br>INCBW=0                                                                | —   | 0.058 | _   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=1 <sup>3</sup>                                                   | _   | 0.044 | —   | V/µs |

|                                              |                    | DRIVESTRENGTH = 0,<br>INCBW=0                                                                | _   | 0.015 | _   | V/µs |

| Startup time <sup>6</sup>                    | T <sub>START</sub> | DRIVESTRENGTH = 2                                                                            | _   | _     | TBD | μs   |

| Input offset voltage                         | V <sub>OSI</sub>   | DRIVESTRENGTH = 2 or 3, T =<br>25 °C                                                         | TBD | —     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0, T = 25 °C                                                            | TBD | —     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 2 or 3,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

|                                              |                    | DRIVESTRENGTH = 1 or 0,<br>across operating temperature<br>range                             | TBD | _     | TBD | mV   |

| DC power supply rejection ratio <sup>9</sup> | PSRR <sub>DC</sub> | Input referred                                                                               | —   | 70    | _   | dB   |

| DC common-mode rejection ratio <sup>9</sup>  | CMRR <sub>DC</sub> | Input referred                                                                               | _   | 70    | _   | dB   |

| Total harmonic distortion                    | THD <sub>OPA</sub> | DRIVESTRENGTH = 2, 3x Gain<br>connection, 1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V   | _   | 90    | _   | dB   |

|                                              |                    | DRIVESTRENGTH = 0, 3x Gain<br>connection, 0.1 kHz, $V_{OUT}$ = 0.1 V<br>to $V_{OPA}$ - 0.1 V | _   | 90    | _   | dB   |

## 4.1.19 Pulse Counter (PCNT)

# Table 4.26. Pulse Counter (PCNT)

| Parameter       | Symbol          | Test Condition                                | Min | Тур | Max | Unit |

|-----------------|-----------------|-----------------------------------------------|-----|-----|-----|------|

| Input frequency | F <sub>IN</sub> | Asynchronous Single and Quad-<br>rature Modes | —   | _   | 20  | MHz  |

|                 |                 | Sampled Modes with Debounce filter set to 0.  |     |     | 8   | kHz  |

## 4.1.20 Analog Port (APORT)

## Table 4.27. Analog Port (APORT)

| Parameter                     | Symbol | Test Condition       | Min | Тур | Max | Unit |

|-------------------------------|--------|----------------------|-----|-----|-----|------|

| Supply current <sup>2 1</sup> | IAPORT | Operation in EM0/EM1 | —   | 7   | —   | μA   |

|                               |        | Operation in EM2/EM3 |     | 915 |     | nA   |

### Note:

1. Specified current is for continuous APORT operation. In applications where the APORT is not requested continuously (e.g. periodic ACMP requests from LESENSE in EM2), the average current requirements can be estimated by mutiplying the duty cycle of the requests by the specified continuous current number.

2. Supply current increase that occurs when an analog peripheral requests access to APORT. This current is not included in reported module currents. Additional peripherals requesting access to APORT do not incur further current.

# 4.1.21.3 I2C Fast-mode Plus (Fm+)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min  | Тур | Мах  | Unit |

|--------------------------------------------------|---------------------|----------------|------|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0    | —   | 1000 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 0.5  | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.26 | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 50   | _   | _    | ns   |

| SDA hold time                                    | t <sub>HD_DAT</sub> |                | 100  | —   | —    | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.26 |     |      | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.26 |     | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.26 | —   | —    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 0.5  | _   | _    | μs   |

# Table 4.30. I2C Fast-mode Plus (Fm+)<sup>1</sup>

# Note:

1. For CLHR set to 0 or 1 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Fast-mode Plus, refer to the I2C chapter in the reference manual.

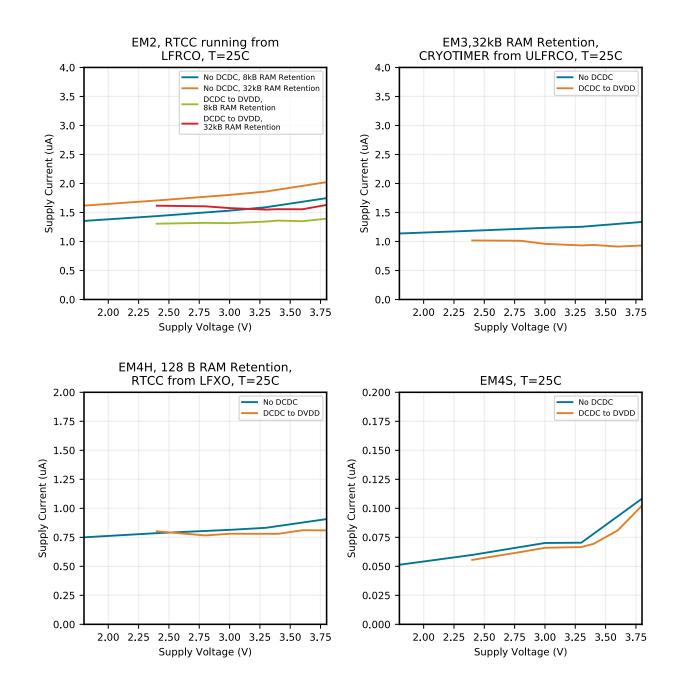

Figure 4.7. EM2, EM3, EM4H and EM4S Typical Supply Current vs. Supply

| Pin Name | Pin(s)              | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|---------------------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | 9<br>24<br>51<br>70 | Ground                        | PB3      | 10     | GPIO                                                                                                                                                                                                        |

| PB4      | 11                  | GPIO                          | PB5      | 12     | GPIO                                                                                                                                                                                                        |

| PB6      | 13                  | GPIO                          | PC1      | 14     | GPIO (5V)                                                                                                                                                                                                   |

| PC2      | 15                  | GPIO (5V)                     | PC3      | 16     | GPIO (5V)                                                                                                                                                                                                   |

| PC4      | 17                  | GPIO                          | PC5      | 18     | GPIO                                                                                                                                                                                                        |

| PB7      | 19                  | GPIO                          | PB8      | 20     | GPIO                                                                                                                                                                                                        |

| PA8      | 21                  | GPIO                          | PA9      | 22     | GPIO                                                                                                                                                                                                        |

| PA10     | 23                  | GPIO                          | PA12     | 25     | GPIO                                                                                                                                                                                                        |

| PA14     | 26                  | GPIO                          | RESETn   | 27     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 28                  | GPIO                          | PB12     | 29     | GPIO                                                                                                                                                                                                        |

| AVDD     | 30<br>34            | Analog power supply.          | PB13     | 31     | GPIO                                                                                                                                                                                                        |

| PB14     | 32                  | GPIO                          | PD0      | 35     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 36                  | GPIO                          | PD3      | 37     | GPIO                                                                                                                                                                                                        |

| PD4      | 38                  | GPIO                          | PD5      | 39     | GPIO                                                                                                                                                                                                        |

| PD6      | 40                  | GPIO                          | PD7      | 41     | GPIO                                                                                                                                                                                                        |

| PD8      | 42                  | GPIO                          | PC6      | 43     | GPIO                                                                                                                                                                                                        |

| PC7      | 44                  | GPIO                          | VREGVSS  | 45     | Voltage regulator VSS                                                                                                                                                                                       |

| VREGSW   | 46                  | DCDC regulator switching node | VREGVDD  | 47     | Voltage regulator VDD input                                                                                                                                                                                 |

| DVDD     | 48                  | Digital power supply.         | DECOUPLE | 49     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PE4      | 52                  | GPIO                          | PE5      | 53     | GPIO                                                                                                                                                                                                        |

| PE6      | 54                  | GPIO                          | PE7      | 55     | GPIO                                                                                                                                                                                                        |

| PC8      | 56                  | GPIO                          | PC9      | 57     | GPIO                                                                                                                                                                                                        |

| PC10     | 58                  | GPIO (5V)                     | PC11     | 59     | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 60                  | GPIO (5V)                     | PC14     | 61     | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 62                  | GPIO (5V)                     | PF0      | 63     | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 64                  | GPIO (5V)                     | PF2      | 65     | GPIO                                                                                                                                                                                                        |

| PF3      | 66                  | GPIO                          | PF4      | 67     | GPIO                                                                                                                                                                                                        |

| PF5      | 68                  | GPIO                          | PE8      | 71     | GPIO                                                                                                                                                                                                        |

| PE9      | 72                  | GPIO                          | PE10     | 73     | GPIO                                                                                                                                                                                                        |

| PE11     | 74                  | GPIO                          | BODEN    | 75     | Brown-Out Detector Enable. This pin<br>may be left disconnected or tied to<br>AVDD.                                                                                                                         |

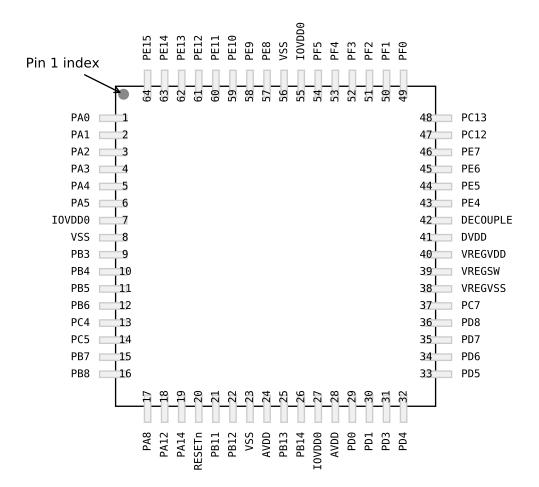

## Figure 5.3. EFM32TG11B5xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.3. EFM32TG11B5xx in Q | FP64 Device Pinout |

|-------------------------------|--------------------|

|-------------------------------|--------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>27<br>55 | Digital IO power supply 0. | VSS      | 8<br>23<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

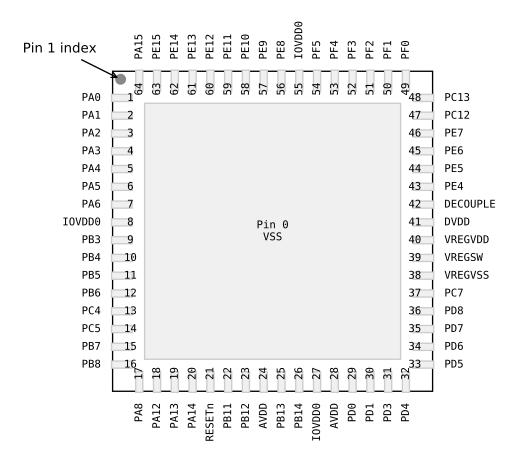

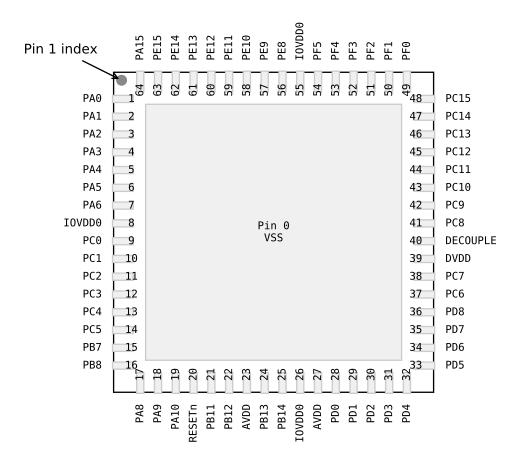

## Figure 5.6. EFM32TG11B5xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0<br>38       | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>27<br>55 | Digital IO power supply 0. | PB3      | 9      | GPIO        |

# Figure 5.8. EFM32TG11B1xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>26<br>55 | Digital IO power supply 0. | PC0      | 9      | GPIO (5V)   |

| PC1      | 10            | GPIO (5V)                  | PC2      | 11     | GPIO (5V)   |

# 5.14 GPIO Functionality Table

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of each GPIO pin, followed by the functionality available on that pin. Refer to 5.15 Alternate Functionality Overview for a list of GPIO locations available for each function.

| GPIO Name |                                                            | Pin Alternate Functi                         | onality / Description                                                               |                                                            |

|-----------|------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|

|           | Analog                                                     | Timers                                       | Communication                                                                       | Other                                                      |

| PA0       | BUSBY BUSAX<br>LCD_SEG13                                   | TIM0_CC0 #0 TIM0_CC1<br>#7 PCNT0_S0IN #4     | US1_RX #5 US3_TX #0<br>LEU0_RX #4 I2C0_SDA<br>#0                                    | CMU_CLK2 #0 PRS_CH0<br>#0 PRS_CH3 #3<br>GPIO_EM4WU0        |

| PA1       | BUSAY BUSBX<br>LCD_SEG14                                   | TIM0_CC0 #7 TIM0_CC1<br>#0 PCNT0_S1IN #4     | US3_RX #0 I2C0_SCL #0                                                               | CMU_CLK1 #0 PRS_CH1<br>#0                                  |

| PA2       | BUSBY BUSAX<br>LCD_SEG15                                   | TIM0_CC2 #0                                  | US1_RX #6 US3_CLK #0                                                                | CMU_CLK0 #0                                                |

| PA3       | BUSAY BUSBX<br>LCD_SEG16                                   | TIM0_CDTI0 #0                                | US3_CS #0 U0_TX #2                                                                  | CMU_CLK2 #1<br>CMU_CLK2 #4<br>CMU_CLKI0 #1 LES_AL-<br>TEX2 |

| PA4       | BUSBY BUSAX<br>LCD_SEG17                                   | TIM0_CDTI1 #0                                | US3_CTS #0 U0_RX #2                                                                 | LES_ALTEX3                                                 |

| PA5       | BUSAY BUSBX<br>LCD_SEG18                                   | TIM0_CDTI2 #0                                | US3_RTS #0 U0_CTS #2                                                                | LES_ALTEX4 ACMP1_O<br>#7                                   |

| PA6       | BUSBY BUSAX<br>LCD_SEG19                                   | WTIM0_CC0 #1                                 | U0_RTS #2                                                                           | PRS_CH6 #0 ACMP0_O<br>#4 GPIO_EM4WU1                       |

| PB3       | BUSAY BUSBX<br>LCD_SEG20 /<br>LCD_COM4                     | TIM1_CC3 #2<br>WTIM0_CC0 #6                  | US2_TX #1 US3_TX #2                                                                 | ACMP0_O #7                                                 |

| PB4       | BUSBY BUSAX<br>LCD_SEG21 /<br>LCD_COM5                     | WTIM0_CC1 #6                                 | US2_RX #1                                                                           |                                                            |

| PB5       | BUSAY BUSBX<br>LCD_SEG22 /<br>LCD_COM6                     | WTIM0_CC2 #6<br>PCNT0_S0IN #6                | US0_RTS #4 US2_CLK<br>#1                                                            |                                                            |

| PB6       | BUSBY BUSAX<br>LCD_SEG23 /<br>LCD_COM7                     | TIM0_CC0 #3<br>PCNT0_S1IN #6                 | US0_CTS #4 US2_CS #1                                                                |                                                            |

| PC0       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #0 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC1 #3<br>PCNT0_S0IN #2                 | CAN0_RX #0 US0_TX #5<br>US1_TX #0 US1_CS #4<br>US2_RTS #0 US3_CS #3<br>I2C0_SDA #4  | LES_CH0 PRS_CH2 #0                                         |

| PC1       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #1 BU-<br>SACMP0Y BUSACMP0X | TIM0_CC2 #3<br>WTIM0_CC0 #7<br>PCNT0_S1IN #2 | CAN0_TX #0 US0_RX #5<br>US1_TX #4 US1_RX #0<br>US2_CTS #0 US3_RTS<br>#1 I2C0_SCL #4 | LES_CH1 PRS_CH3 #0                                         |

| PC2       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #2 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI0 #3<br>WTIM0_CC1 #7                | US1_RX #4 US2_TX #0                                                                 | LES_CH2                                                    |

| PC3       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #3 BU-<br>SACMP0Y BUSACMP0X | TIM0_CDTI1 #3<br>WTIM0_CC2 #7                | US1_CLK #4 US2_RX #0                                                                | LES_CH3                                                    |

# Table 5.14. GPIO Functionality Table

| Alternate     | LOCA    | TION  |                                  |

|---------------|---------|-------|----------------------------------|

| Functionality | 0 - 3   | 4 - 7 | Description                      |

| LCD_COM0      | 0: PE4  |       | LCD driver common line number 0. |

| LCD_COM1      | 0: PE5  |       | LCD driver common line number 1. |

| LCD_COM2      | 0: PE6  |       | LCD driver common line number 2. |

| LCD_COM3      | 0: PE7  |       | LCD driver common line number 3. |

| LCD_SEG0      | 0: PF2  |       | LCD segment line 0.              |

| LCD_SEG1      | 0: PF3  |       | LCD segment line 1.              |

| LCD_SEG2      | 0: PF4  |       | LCD segment line 2.              |

| LCD_SEG3      | 0: PF5  |       | LCD segment line 3.              |

| LCD_SEG4      | 0: PE8  |       | LCD segment line 4.              |

| LCD_SEG5      | 0: PE9  |       | LCD segment line 5.              |

| LCD_SEG6      | 0: PE10 |       | LCD segment line 6.              |

| LCD_SEG7      | 0: PE11 |       | LCD segment line 7.              |

| LCD_SEG8      | 0: PE12 |       | LCD segment line 8.              |

| Alternate     | LOC                                     | ATION                       |                                                                                                                                                            |

|---------------|-----------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                   | 4 - 7                       | Description                                                                                                                                                |

| U0_TX         | 2: PA3<br>3: PC14                       | 4: PC4<br>5: PF1<br>6: PD7  | UART0 Transmit output. Also used as receive input in half duplex communication.                                                                            |

| US0_CLK       | 0: PE12<br>1: PE5<br>2: PC9<br>3: PC15  | 4: PB13<br>5: PA12          | USART0 clock input / output.                                                                                                                               |

| US0_CS        | 0: PE13<br>1: PE4<br>2: PC8<br>3: PC14  | 4: PB14<br>5: PA13          | USART0 chip select input / output.                                                                                                                         |

| US0_CTS       | 0: PE14<br>2: PC7<br>3: PC13            | 4: PB6<br>5: PB11           | USART0 Clear To Send hardware flow control input.                                                                                                          |

| US0_RTS       | 0: PE15<br>2: PC6<br>3: PC12            | 4: PB5<br>5: PD6            | USART0 Request To Send hardware flow control output.                                                                                                       |

| US0_RX        | 0: PE11<br>1: PE6<br>2: PC10<br>3: PE12 | 4: PB8<br>5: PC1            | USART0 Asynchronous Receive.<br>USART0 Synchronous mode Master Input / Slave Output (MISO).                                                                |

| US0_TX        | 0: PE10<br>1: PE7<br>2: PC11<br>3: PE13 | 4: PB7<br>5: PC0            | USART0 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART0 Synchronous mode Master Output / Slave Input (MOSI). |

| US1_CLK       | 0: PB7<br>1: PD2<br>2: PF0<br>3: PC15   | 4: PC3<br>5: PB11<br>6: PE5 | USART1 clock input / output.                                                                                                                               |

| US1_CS        | 0: PB8<br>1: PD3<br>2: PF1<br>3: PC14   | 4: PC0<br>5: PE4            | USART1 chip select input / output.                                                                                                                         |

| US1_CTS       | 1: PD4<br>2: PF3<br>3: PC6              | 4: PC12<br>5: PB13          | USART1 Clear To Send hardware flow control input.                                                                                                          |

| US1_RTS       | 1: PD5<br>2: PF4<br>3: PC7              | 4: PC13<br>5: PB14          | USART1 Request To Send hardware flow control output.                                                                                                       |

| US1_RX        | 0: PC1<br>1: PD1<br>2: PD6              | 4: PC2<br>5: PA0<br>6: PA2  | USART1 Asynchronous Receive.<br>USART1 Synchronous mode Master Input / Slave Output (MISO).                                                                |

| US1_TX        | 0: PC0<br>1: PD0<br>2: PD7              | 4: PC1<br>5: PF2<br>6: PA14 | USART1 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART1 Synchronous mode Master Output / Slave Input (MOSI). |

| Alternate     | LOC                                    | ATION             |                                                                                                                                                            |

|---------------|----------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                  | 4 - 7             | Description                                                                                                                                                |

| US2_CLK       | 0: PC4<br>1: PB5<br>2: PA9<br>3: PA15  | 5: PF2            | USART2 clock input / output.                                                                                                                               |

| US2_CS        | 0: PC5<br>1: PB6<br>2: PA10<br>3: PB11 | 5: PF5            | USART2 chip select input / output.                                                                                                                         |

| US2_CTS       | 0: PC1<br>1: PB12                      | 4: PC12<br>5: PD6 | USART2 Clear To Send hardware flow control input.                                                                                                          |

| US2_RTS       | 0: PC0<br>2: PA12<br>3: PC14           | 4: PC13<br>5: PD8 | USART2 Request To Send hardware flow control output.                                                                                                       |

| US2_RX        | 0: PC3<br>1: PB4<br>2: PA8<br>3: PA14  | 5: PF1            | USART2 Asynchronous Receive.<br>USART2 Synchronous mode Master Input / Slave Output (MISO).                                                                |

| US2_TX        | 0: PC2<br>1: PB3<br>3: PA13            | 5: PF0            | USART2 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART2 Synchronous mode Master Output / Slave Input (MOSI). |

| US3_CLK       | 0: PA2<br>1: PD7<br>2: PD4             |                   | USART3 clock input / output.                                                                                                                               |

| US3_CS        | 0: PA3<br>1: PE4<br>2: PC14<br>3: PC0  |                   | USART3 chip select input / output.                                                                                                                         |

| US3_CTS       | 0: PA4<br>1: PE5<br>2: PD6             |                   | USART3 Clear To Send hardware flow control input.                                                                                                          |

| US3_RTS       | 0: PA5<br>1: PC1<br>2: PA14<br>3: PC15 |                   | USART3 Request To Send hardware flow control output.                                                                                                       |

| US3_RX        | 0: PA1<br>1: PE7<br>2: PB7             |                   | USART3 Asynchronous Receive.<br>USART3 Synchronous mode Master Input / Slave Output (MISO).                                                                |

| US3_TX        | 0: PA0<br>1: PE6<br>2: PB3             |                   | USART3 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART3 Synchronous mode Master Output / Slave Input (MOSI). |

| VDAC0_EXT     | 0: PD6                                 |                   | Digital to analog converter VDAC0 external reference input pin.                                                                                            |

# EFM32TG11 Family Data Sheet Pin Definitions

| Port           | Bus      | CH31       | CH30   | CH29   | CH28 | CH27   | CH26 | CH25   | CH24   | CH23   | CH22   | CH21   | CH20   | CH19   | CH18   | CH17   | CH16   | CH15 | CH14 | CH13   | CH12   | CH11   | CH10 | CH9    | CH8 | CH7    | CH6    | CH5    | CH4    | CH3    | CH2 | CH1    | CH0 |

|----------------|----------|------------|--------|--------|------|--------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------|------|--------|--------|--------|------|--------|-----|--------|--------|--------|--------|--------|-----|--------|-----|

|                | <br>РА1_ |            | С<br>О | С<br>С | O    | U<br>U | O    | С<br>С | С<br>С | С<br>О | С<br>С | С<br>С | С<br>С | С<br>С | С<br>С | С<br>С | С<br>О | C    | O    | С<br>С | С<br>О | С<br>С | C    | С<br>С | ပ   | С<br>О | С<br>С | С<br>С | С<br>С | С<br>О | C   | С<br>О | O   |

| APORT1Y        | BUSAY    |            |        | PB13   |      | PB11   |      |        |        |        |        | PB5    |        | PB3    |        |        |        | PA15 |      | PA13   |        |        |      | PA9    |     |        |        | PA5    |        | PA3    |     | PA1    |     |

| APORT2Y        | BUSBY    |            | PB14   |        | PB12 |        |      |        |        |        | PB6    |        | PB4    |        |        |        |        |      | PA14 |        |        |        | PA10 |        |     |        | PA6    |        | PA4    |        | PA2 |        | PA0 |

| <b>APORT3Y</b> | BUSCY    |            |        |        |      |        |      |        |        |        |        | PF5    |        | PF3    |        | PF1    |        | PE15 |      | PE13   |        | PE11   |      | PE9    |     | PE7    |        | PE5    |        |        |     |        |     |

| APORT4Y        | BUSDY    |            |        |        |      |        |      |        |        |        |        |        | PF4    |        | PF2    |        | PF0    |      | PE14 |        | PE12   |        | PE10 |        | PE8 |        | PE6    |        | PE4    |        |     |        |     |

| OF             | PA1_     | <u>.</u> P |        |        |      |        | 1    |        |        |        |        |        |        |        |        |        |        |      |      |        |        |        |      |        |     |        |        |        |        |        |     |        |     |

| APORT1X        | BUSAX    |            | PB14   |        | PB12 |        |      |        |        |        | PB6    |        | PB4    |        |        |        |        |      | PA14 |        |        |        | PA10 |        |     |        | PA6    |        | PA4    |        | PA2 |        | PA0 |

| APORT2X        | BUSBX    |            |        | PB13   |      | PB11   |      |        |        |        |        | PB5    |        | PB3    |        |        |        | PA15 |      | PA13   |        |        |      | PA9    |     |        |        | PA5    |        | PA3    |     | PA1    |     |

| <b>APORT3X</b> | BUSCX    |            |        |        |      |        |      |        |        |        |        |        | PF4    |        | PF2    |        | PF0    |      | PE14 |        | PE12   |        | PE10 |        | PE8 |        | PE6    |        | PE4    |        |     |        |     |

| APORT4X        | BUSDX    |            |        |        |      |        |      |        |        |        |        | PF5    |        | PF3    |        | PF1    |        | PE15 |      | PE13   |        | PE11   |      | PE9    |     | PE7    |        | PE5    |        |        |     |        |     |

| OF             | A2_      | N          |        |        |      |        |      |        |        |        |        |        |        |        |        |        |        |      |      |        |        |        |      |        |     |        |        |        |        |        |     |        |     |

| APORT1Y        | BUSAY    |            |        | PB13   |      | PB11   |      |        |        |        |        | PB5    |        | PB3    |        |        |        | PA15 |      | PA13   |        |        |      | PA9    |     |        |        | PA5    |        | EA3    |     | PA1    |     |

| APORT2Y        | BUSBY    |            | PB14   |        | PB12 |        |      |        |        |        | PB6    |        | PB4    |        |        |        |        |      | PA14 |        |        |        | PA10 |        |     |        | PA6    |        | PA4    |        | PA2 |        | PA0 |

| <b>APORT3Y</b> | BUSCY    |            |        |        |      |        |      |        |        |        |        | PF5    |        | PF3    |        | PF1    |        | PE15 |      | PE13   |        | PE11   |      | PE9    |     | PE7    |        | PE5    |        |        |     |        |     |

| APORT4Y        | BUSDY    |            |        |        |      |        |      |        |        |        |        |        | PF4    |        | PF2    |        | PF0    |      | PE14 |        | PE12   |        | PE10 |        | PE8 |        | PE6    |        | PE4    |        |     |        |     |

# EFM32TG11 Family Data Sheet Pin Definitions

| Port           | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

|----------------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| OP             | A3_   | 00   | Г    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y        | BUSAY |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| <b>APORT3Y</b> | BUSCY |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| OP             | A3_   | P    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1X        | BUSAX |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PAO |

| APORT2X        | BUSBX |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | 6A9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| <b>APORT3X</b> | BUSCX |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| APORT4X        | BUSDX |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| VD             | AC    | 0_0  | UT0  | / 0  | PA0  | _οι  | JT   |      |      |      |      |      | 1    |      |      | 1    |      |      |      |      | 1    | 1    |      |     |     |     | 1   |     |     |     |     |     |     |

| APORT1Y        | BUSAY |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | 6A9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| <b>APORT3Y</b> | BUSCY |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| Dimension | Min  | Тур       | Мах  |  |  |  |  |  |  |

|-----------|------|-----------|------|--|--|--|--|--|--|

| A         | 0.70 | 0.75      | 0.80 |  |  |  |  |  |  |

| A1        | 0.00 | _         | 0.05 |  |  |  |  |  |  |

| b         | 0.20 | 0.25      | 0.30 |  |  |  |  |  |  |

| A3        |      | 0.203 REF |      |  |  |  |  |  |  |

| D         |      | 9.00 BSC  |      |  |  |  |  |  |  |

| е         |      | 0.40 BSC  |      |  |  |  |  |  |  |

| E         |      | 9.00 BSC  |      |  |  |  |  |  |  |

| D2        | 7.10 | 7.20      | 7.30 |  |  |  |  |  |  |

| E2        | 7.10 | 7.20      | 7.30 |  |  |  |  |  |  |

| L         | 0.35 | 0.40      | 0.45 |  |  |  |  |  |  |

| ааа       |      | 0.10      |      |  |  |  |  |  |  |

| bbb       |      | 0.10      |      |  |  |  |  |  |  |

| ссс       |      | 0.10      |      |  |  |  |  |  |  |

| ddd       | 0.05 |           |      |  |  |  |  |  |  |

| eee       | 0.08 |           |      |  |  |  |  |  |  |

| Nata      |      |           |      |  |  |  |  |  |  |

# Table 7.1. QFN80 Package Dimensions

# Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## Table 11.2. QFN32 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 5.00 |

| C2        | 5.00 |

| E         | 0.50 |

| X1        | 0.30 |

| Y1        | 0.80 |

| X2        | 3.80 |

| Y2        | 3.80 |

# Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

5. The stencil thickness should be 0.125 mm (5 mils).

6. The ratio of stencil aperture to land pad size can be 1:1 for all perimeter pads.

7. A 2x2 array of 0.9 mm square openings on a 1.2 mm pitch should be used for the center ground pad.

8. A No-Clean, Type-3 solder paste is recommended.

9. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.