#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Discontinued at Digi-Key                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-TQFP                                                                   |

| Supplier Device Package    | 48-TQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b520f128iq48-a |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Feature List

The EFM32TG11 highlighted features are listed below.

# ARM Cortex-M0+ CPU platform

- High performance 32-bit processor @ up to 48 MHz

- Memory Protection Unit

- Wake-up Interrupt Controller

- Flexible Energy Management System

- 37 µA/MHz in Active Mode (EM0)

- 1.30 µA EM2 Deep Sleep current (8 kB RAM retention and RTCC running from LFRCO)

- Integrated DC-DC buck converter

- Backup Power Domain

- RTCC and retention registers in a separate power domain, available in all energy modes

- Operation from backup battery when main power absent/ insufficient

- Up to 128 kB flash program memory

- Up to 32 kB RAM data memory

- Communication Interfaces

- CAN Bus Controller

- Version 2.0A and 2.0B up to 1 Mbps

- 4 × Universal Synchronous/Asynchronous Receiver/ Transmitter

- UART/SPI/SmartCard (ISO 7816)/IrDA/I2S/LIN

- Triple buffered full/half-duplex operation with flow control

- Ultra high speed (24 MHz) operation on one instance

- 1 × Universal Asynchronous Receiver/ Transmitter

- 1 × Low Energy UART

- Autonomous operation with DMA in Deep Sleep Mode

- $2 \times I^2C$  Interface with SMBus support

- Address recognition in EM3 Stop Mode

## Up to 67 General Purpose I/O Pins

- Configurable push-pull, open-drain, pull-up/down, input filter, drive strength

- Configurable peripheral I/O locations

- · 5 V tolerance on select pins

- Asynchronous external interrupts

- Output state retention and wake-up from Shutoff Mode

- Up to 8 Channel DMA Controller

- Up to 8 Channel Peripheral Reflex System (PRS) for autonomous inter-peripheral signaling

- Hardware Cryptography

- AES 128/256-bit keys

- ECC B/K163, B/K233, P192, P224, P256

- SHA-1 and SHA-2 (SHA-224 and SHA-256)

- True Random Number Generator (TRNG)

- Hardware CRC engine

- Single-cycle computation with 8/16/32-bit data and 16-bit (programmable)/32-bit (fixed) polynomial

- Security Management Unit (SMU)

- Fine-grained access control for on-chip peripherals

- Integrated Low-energy LCD Controller with up to 8 × 32 segments

- Voltage boost, contrast and autonomous animation

- Patented low-energy LCD driver

- Ultra Low-Power Precision Analog Peripherals

- 12-bit 1 Msamples/s Analog to Digital Converter (ADC)

- On-chip temperature sensor

- 2 × 12-bit 500 ksamples/s Digital to Analog Converter (VDAC)

- Up to 2 × Analog Comparator (ACMP)

- Up to 4 × Operational Amplifier (OPAMP)

- Robust current-based capacitive sensing with up to 38 inputs and wake-on-touch (CSEN)

- Up to 62 GPIO pins are analog-capable. Flexible analog peripheral-to-pin routing via Analog Port (APORT)

- Supply Voltage Monitor

#### 3.6.5 Controller Area Network (CAN)

The CAN peripheral provides support for communication at up to 1 Mbps over CAN protocol version 2.0 part A and B. It includes 32 message objects with independent identifier masks and retains message RAM in EM2. Automatic retransmittion may be disabled in order to support Time Triggered CAN applications.

#### 3.6.6 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality such as simple logic operations (AND, OR, NOT) can be applied by the PRS to the signals. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

#### 3.6.7 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface LESENSE<sup>TM</sup> is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators, ADC, and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable finite state machine which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

#### 3.7 Security Features

#### 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)

The GPCRC module implements a Cyclic Redundancy Check (CRC) function. It supports both 32-bit and 16-bit polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3), while the 16-bit polynomial can be programmed to any value, depending on the needs of the application.

#### 3.7.2 Crypto Accelerator (CRYPTO)

The Crypto Accelerator is a fast and energy-efficient autonomous hardware encryption and decryption accelerator. Tiny Gecko Series 1 devices support AES encryption and decryption with 128- or 256-bit keys, ECC over both GF(P) and GF(2<sup>m</sup>), and SHA-1 and SHA-2 (SHA-224 and SHA-256).

Supported block cipher modes of operation for AES include: ECB, CTR, CBC, PCBC, CFB, OFB, GCM, CBC-MAC, GMAC and CCM.

Supported ECC NIST recommended curves include P-192, P-224, P-256, K-163, K-233, B-163 and B-233.

The CRYPTO module allows fast processing of GCM (AES), ECC and SHA with little CPU intervention. CRYPTO also provides trigger signals for DMA read and write operations.

#### 3.7.3 True Random Number Generator (TRNG)

The TRNG module is a non-deterministic random number generator based on a full hardware solution. The TRNG is validated with NIST800-22 and AIS-31 test suites as well as being suitable for FIPS 140-2 certification (for the purposes of cryptographic key generation).

#### 3.7.4 Security Management Unit (SMU)

The Security Management Unit (SMU) allows software to set up fine-grained security for peripheral access, which is not possible in the Memory Protection Unit (MPU). Peripherals may be secured by hardware on an individual basis, such that only priveleged accesses to the peripheral's register interface will be allowed. When an access fault occurs, the SMU reports the specific peripheral involved and can optionally generate an interrupt.

#### 3.8 Analog

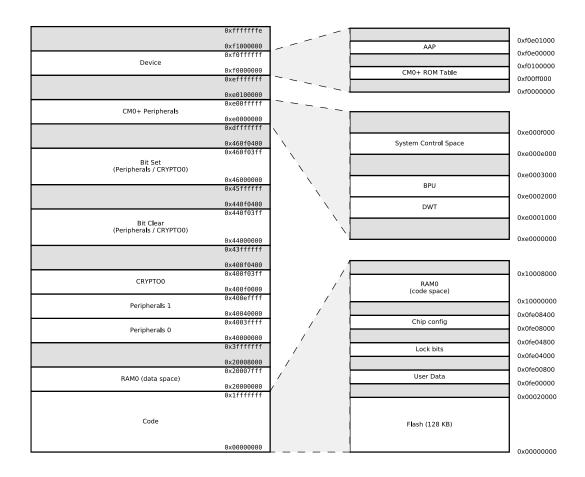

### 3.11 Memory Map

The EFM32TG11 memory map is shown in the figures below. RAM and flash sizes are for the largest memory configuration.

Figure 3.2. EFM32TG11 Memory Map — Core Peripherals and Code Space

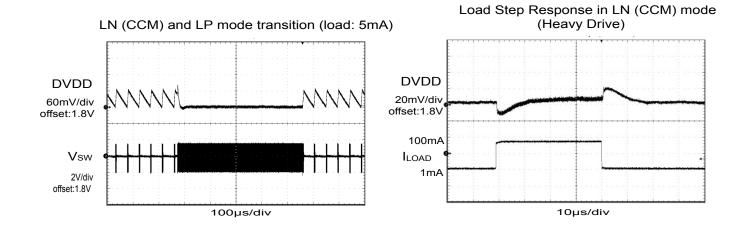

### 4.1.4 DC-DC Converter

Test conditions: L\_DCDC=4.7 µH (Murata LQH3NPN4R7MM0L), C\_DCDC=4.7 µF (Samsung CL10B475KQ8NQNC), V\_DCDC\_I=3.3 V, V\_DCDC\_O=1.8 V, I\_DCDC\_LOAD=50 mA, Heavy Drive configuration, F\_DCDC\_LN=7 MHz, unless otherwise indicated.

### Table 4.4. DC-DC Converter

| Parameter                                           | Symbol              | Test Condition                                                                                                                  | Min | Тур | Max                         | Unit |

|-----------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                 | V <sub>DCDC_I</sub> | Bypass mode, I <sub>DCDC_LOAD</sub> = 50<br>mA                                                                                  | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V output, $I_{DCDC\_LOAD}$ = 100 mA, or<br>Low power (LP) mode, 1.8 V output, $I_{DCDC\_LOAD}$ = 10 mA | 2.4 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V out-<br>put, I <sub>DCDC_LOAD</sub> = 200 mA                                                         | 2.6 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Output voltage programma-<br>ble range <sup>1</sup> | V <sub>DCDC_0</sub> |                                                                                                                                 | 1.8 | _   | V <sub>VREGVDD</sub>        | V    |

| Regulation DC accuracy                              | ACC <sub>DC</sub>   | Low Noise (LN) mode, 1.8 V tar-<br>get output                                                                                   | TBD | _   | TBD                         | V    |

| Regulation window <sup>4</sup>                      | WIN <sub>REG</sub>  | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 75 µA                | TBD | _   | TBD                         | V    |

|                                                     |                     | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 10 mA                | TBD | _   | TBD                         | V    |

| Steady-state output ripple                          | V <sub>R</sub>      |                                                                                                                                 | _   | 3   | —                           | mVpp |

| Output voltage under/over-<br>shoot                 | Vov                 | CCM Mode (LNFORCECCM <sup>3</sup> = 1), Load changes between 0 mA and 100 mA                                                    | _   | 25  | TBD                         | mV   |

|                                                     |                     | DCM Mode (LNFORCECCM <sup>3</sup> = 0), Load changes between 0 mA and 10 mA                                                     | _   | 45  | TBD                         | mV   |

|                                                     |                     | Overshoot during LP to LN<br>CCM/DCM mode transitions com-<br>pared to DC level in LN mode                                      | _   | 200 | -                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>CCM (LNFORCECCM <sup>3</sup> = 1) mode<br>transitions compared to DC level<br>in LN mode      | _   | 40  | _                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>DCM (LNFORCECCM <sup>3</sup> = 0) mode<br>transitions compared to DC level<br>in LN mode      | _   | 100 | _                           | mV   |

| DC line regulation                                  | V <sub>REG</sub>    | Input changes between V <sub>VREGVDD_MAX</sub> and 2.4 V                                                                        | _   | 0.1 | -                           | %    |

| DC load regulation                                  | I <sub>REG</sub>    | Load changes between 0 mA and 100 mA in CCM mode                                                                                | —   | 0.1 | _                           | %    |

### 4.1.5 Backup Supply Domain

| Parameter                                                   | Symbol               | Test Condition                                  | Min | Тур  | Max | Unit |

|-------------------------------------------------------------|----------------------|-------------------------------------------------|-----|------|-----|------|

| Backup supply voltage range                                 | V <sub>BU_VIN</sub>  |                                                 | TBD | —    | 3.8 | V    |

| PWRRES resistor                                             | R <sub>PWRRES</sub>  | EMU_BUCTRL_PWRRES =<br>RES0                     | TBD | 3900 | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES1                     | TBD | 1800 | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES2                     | TBD | 1330 | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES3                     | TBD | 815  | TBD | Ω    |

| Output impedance between<br>BU_VIN and BU_VOUT <sup>2</sup> | R <sub>BU_VOUT</sub> | EMU_BUCTRL_VOUTRES =<br>STRONG                  | TBD | 110  | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_VOUTRES =<br>MED                     | TBD | 775  | TBD | Ω    |

|                                                             |                      | EMU_BUCTRL_VOUTRES =<br>WEAK                    | TBD | 6500 | TBD | Ω    |

| Supply current                                              | I <sub>BU_VIN</sub>  | BU_VIN not powering backup do-<br>main          | _   | 10   | TBD | nA   |

|                                                             |                      | BU_VIN powering backup do-<br>main <sup>1</sup> |     | 450  | TBD | nA   |

#### Table 4.5. Backup Supply Domain

### Note:

1. Additional current required by backup circuitry when backup is active. Includes supply current of backup switches and backup regulator. Does not include supply current required for backed-up circuitry.

2. BU\_VOUT and BU\_STAT signals are not available in all package configurations. Check the device pinout for availability.

#### 4.1.6 Current Consumption

### 4.1.6.1 Current Consumption 3.3 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 3.3 V. T = 25 °C. DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

### Table 4.6. Current Consumption 3.3 V without DC-DC Converter

| Parameter                                                              | Symbol              | Test Condition                                                       | Min | Тур  | Max | Unit   |

|------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|-----|------|-----|--------|

| mode with all peripherals dis-                                         | I <sub>ACTIVE</sub> | 48 MHz crystal, CPU running while loop from flash                    | _   | 45   | _   | µA/MHz |

| abled                                                                  |                     | 48 MHz HFRCO, CPU running while loop from flash                      |     | 44   | TBD | µA/MHz |

|                                                                        |                     | 48 MHz HFRCO, CPU running<br>Prime from flash                        |     | 57   |     | µA/MHz |

|                                                                        |                     | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash                |     | 71   | _   | µA/MHz |

|                                                                        |                     | 32 MHz HFRCO, CPU running while loop from flash                      |     | 45   | _   | µA/MHz |

|                                                                        |                     | 26 MHz HFRCO, CPU running while loop from flash                      |     | 46   | TBD | µA/MHz |

|                                                                        |                     | 16 MHz HFRCO, CPU running while loop from flash                      |     | 50   |     | µA/MHz |

|                                                                        |                     | 1 MHz HFRCO, CPU running while loop from flash                       | —   | 161  | TBD | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis-           | IACTIVE_VS          | 19 MHz HFRCO, CPU running while loop from flash                      | —   | 41   | _   | µA/MHz |

| abled and voltage scaling enabled                                      |                     | 1 MHz HFRCO, CPU running while loop from flash                       | _   | 145  | _   | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1</sub>    | 48 MHz crystal                                                       | —   | 34   | _   | µA/MHz |

| mode with all peripherals disabled                                     |                     | 48 MHz HFRCO                                                         | —   | 33   | TBD | µA/MHz |

|                                                                        |                     | 32 MHz HFRCO                                                         | —   | 34   |     | µA/MHz |

|                                                                        |                     | 26 MHz HFRCO                                                         | —   | 35   | TBD | µA/MHz |

|                                                                        |                     | 16 MHz HFRCO                                                         | —   | 39   | _   | µA/MHz |

|                                                                        |                     | 1 MHz HFRCO                                                          | —   | 150  | TBD | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1_VS</sub> | 19 MHz HFRCO                                                         | —   | 32   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled |                     | 1 MHz HFRCO                                                          | _   | 136  |     | µA/MHz |

| Current consumption in EM2<br>mode, with voltage scaling               | I <sub>EM2_VS</sub> | Full 32 kB RAM retention and RTCC running from LFXO                  |     | 1.48 | _   | μA     |

| enabled                                                                |                     | Full 32 kB RAM retention and<br>RTCC running from LFRCO              | _   | 1.86 |     | μΑ     |

|                                                                        |                     | 8 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup> |     | 1.59 | TBD | μΑ     |

| Current consumption in EM3<br>mode, with voltage scaling<br>enabled    | I <sub>EM3_VS</sub> | Full 32 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO   |     | 1.23 | TBD | μA     |

### 4.1.9.5 Auxiliary High-Frequency RC Oscillator (AUXHFRCO)

| Parameter                              | Symbol                             | Test Condition                                                                      | Min | Тур | Мах | Unit  |

|----------------------------------------|------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Frequency accuracy                     | fauxhfrco_acc                      | At production calibrated frequen-<br>cies, across supply voltage and<br>temperature | TBD | _   | TBD | %     |

| Start-up time                          | t <sub>AUXHFRCO</sub>              | f <sub>AUXHFRCO</sub> ≥ 19 MHz                                                      | _   | 400 | _   | ns    |

|                                        |                                    | 4 < f <sub>AUXHFRCO</sub> < 19 MHz                                                  | _   | 1.4 | _   | μs    |

|                                        |                                    | f <sub>AUXHFRCO</sub> ≤ 4 MHz                                                       | _   | 2.5 | _   | μs    |

| Current consumption on all             | I <sub>AUXHFRCO</sub>              | f <sub>AUXHFRCO</sub> = 48 MHz                                                      | _   | 238 | TBD | μA    |

| supplies                               |                                    | f <sub>AUXHFRCO</sub> = 38 MHz                                                      | —   | 196 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 32 MHz                                                      | _   | 160 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 26 MHz                                                      | _   | 137 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 19 MHz                                                      | _   | 110 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 16 MHz                                                      | _   | 101 | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 13 MHz                                                      | _   | 78  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 7 MHz                                                       | _   | 54  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 4 MHz                                                       | _   | 30  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 2 MHz                                                       | _   | 27  | TBD | μA    |

|                                        |                                    | f <sub>AUXHFRCO</sub> = 1 MHz                                                       | _   | 25  | TBD | μA    |

| Coarse trim step size (% of period)    | SS <sub>AUXHFR-</sub><br>CO_COARSE |                                                                                     |     | 0.8 | _   | %     |

| Fine trim step size (% of pe-<br>riod) | SS <sub>AUXHFR-</sub><br>CO_FINE   |                                                                                     |     | 0.1 | _   | %     |

| Period jitter                          | PJ <sub>AUXHFRCO</sub>             |                                                                                     |     | 0.2 | _   | % RMS |

### Table 4.15. Auxiliary High-Frequency RC Oscillator (AUXHFRCO)

### 4.1.9.6 Ultra-low Frequency RC Oscillator (ULFRCO)

#### Table 4.16. Ultra-low Frequency RC Oscillator (ULFRCO)

| Parameter             | Symbol              | Test Condition | Min | Тур | Мах | Unit |

|-----------------------|---------------------|----------------|-----|-----|-----|------|

| Oscillation frequency | f <sub>ULFRCO</sub> |                | TBD | 1   | TBD | kHz  |

### 4.1.12 Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Мах | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | I <sub>VMON</sub>       | In EM0 or EM1, 1 supply monitored, T $\leq$ 85 °C                | _    | 6.3  | TBD | μA   |

|                                    |                         | In EM0 or EM1, 4 supplies monitored, T $\leq$ 85 °C              | —    | 12.5 | TBD | μA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshold       | —    | 62   |     | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | _    | 99   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold | —    | 99   | _   | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | —    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    | _   | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | _    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  |     | mV   |

|                                    |                         | Fine                                                             | _    | 20   | _   | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | _    | 460  | _   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  |      | 26   | _   | mV   |

### Table 4.19. Voltage Monitor (VMON)

### 4.1.13 Analog to Digital Converter (ADC)

Specified at 1 Msps, ADCCLK = 16 MHz, BIASPROG = 0, GPBIASACC = 0, unless otherwise indicated.

### Table 4.20. Analog to Digital Converter (ADC)

| Parameter                                                                                                                                                         | Symbol                             | Test Condition                                                           | Min                 | Тур | Мах                | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|---------------------|-----|--------------------|------|

| Resolution                                                                                                                                                        | VRESOLUTION                        |                                                                          | 6                   | —   | 12                 | Bits |

| Input voltage range <sup>5</sup>                                                                                                                                  | V <sub>ADCIN</sub>                 | Single ended                                                             | _                   | —   | V <sub>FS</sub>    | V    |

|                                                                                                                                                                   |                                    | Differential                                                             | -V <sub>FS</sub> /2 | _   | V <sub>FS</sub> /2 | V    |

| Input range of external refer-<br>ence voltage, single ended<br>and differential                                                                                  | V <sub>ADCREFIN_P</sub>            |                                                                          | 1                   | _   | V <sub>AVDD</sub>  | V    |

| Power supply rejection <sup>2</sup>                                                                                                                               | PSRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | —                  | dB   |

| Analog input common mode rejection ratio                                                                                                                          | CMRR <sub>ADC</sub>                | At DC                                                                    | _                   | 80  | -                  | dB   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                                                  | I <sub>ADC_CONTI-</sub><br>NOUS_LP | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>    | _                   | 270 | TBD                | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                                                                                              |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 1 <sup>3</sup>   | _                   | 125 | -                  | μA   |

|                                                                                                                                                                   |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 1 <sup>3</sup> | _                   | 80  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                                                  | I <sub>ADC_NORMAL_LP</sub>         | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 45  | -                  | μA   |

| Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL                                                                                                      |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>     | _                   | 8   | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                                                  | IADC_STAND-<br>BY_LP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>  | _                   | 105 | -                  | μA   |

| Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC                                                                     |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 1 <sup>3</sup>   | _                   | 70  | _                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                                                  | I <sub>ADC_CONTI-</sub><br>NOUS_HP | 1 Msps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>    | _                   | 325 | -                  | μA   |

| Continous operation. WAR-<br>MUPMODE <sup>4</sup> = KEEPADC-<br>WARM                                                                                              |                                    | 250 ksps / 4 MHz ADCCLK, BIA-<br>SPROG = 6, GPBIASACC = 0 <sup>3</sup>   | _                   | 175 | -                  | μA   |

|                                                                                                                                                                   |                                    | 62.5 ksps / 1 MHz ADCCLK, BIA-<br>SPROG = 15, GPBIASACC = 0 <sup>3</sup> | _                   | 125 | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.                                                                                                  | IADC_NORMAL_HP                     | 35 ksps / 16 MHz ADCCLK, BIA-SPROG = 0, GPBIASACC = 0 $^3$               | _                   | 85  | -                  | μA   |

| Duty-cycled operation. WAR-<br>MUPMODE <sup>4</sup> = NORMAL                                                                                                      |                                    | 5 ksps / 16 MHz ADCCLK BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>     | _                   | 16  | -                  | μA   |

| Current from all supplies, us-<br>ing internal reference buffer.<br>Duty-cycled operation.<br>AWARMUPMODE <sup>4</sup> = KEEP-<br>INSTANDBY or KEEPIN-<br>SLOWACC | IADC_STAND-<br>BY_HP               | 125 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>  | —                   | 160 | -                  | μA   |

|                                                                                                                                                                   |                                    | 35 ksps / 16 MHz ADCCLK, BIA-<br>SPROG = 0, GPBIASACC = 0 <sup>3</sup>   | _                   | 125 | -                  | μA   |

| Current from HFPERCLK                                                                                                                                             | IADC_CLK                           | HFPERCLK = 16 MHz                                                        | _                   | 166 | _                  | μΑ   |

Figure 4.9. DC-DC Converter Transition Waveforms

# 5. Pin Definitions

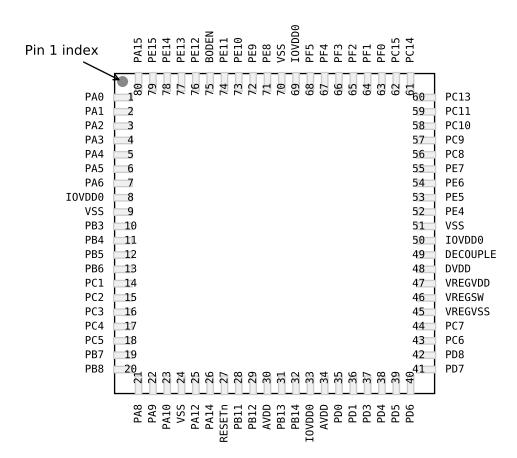

### 5.1 EFM32TG11B5xx in QFP80 Device Pinout

#### Figure 5.1. EFM32TG11B5xx in QFP80 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Table 5.1. | EFM32TG11B5xx in QFP80 Device Pinout |

|------------|--------------------------------------|

|            |                                      |

| Pin Name | Pin(s) | Description | Pin Name | Pin(s)              | Description                |

|----------|--------|-------------|----------|---------------------|----------------------------|

| PA0      | 1      | GPIO        | PA1      | 2                   | GPIO                       |

| PA2      | 3      | GPIO        | PA3      | 4                   | GPIO                       |

| PA4      | 5      | GPIO        | PA5      | 6                   | GPIO                       |

| PA6      | 7      | GPIO        | IOVDD0   | 8<br>33<br>50<br>69 | Digital IO power supply 0. |

| GPIO Name |                                                            | Pin Alternate Functi                                                               | onality / Description                                                     |                                                      |

|-----------|------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|

|           | Analog                                                     | Timers                                                                             | Communication                                                             | Other                                                |

| PD5       | BUSADC0Y BUSADC0X<br>OPA2_OUT                              | WTIM0_CDTI1 #4<br>WTIM1_CC3 #1                                                     | US1_RTS #1 U0_CTS #5<br>LEU0_RX #0 I2C1_SCL<br>#3                         |                                                      |

| PD6       | BUSADC0Y BUSADC0X<br>ADC0_EXTP<br>VDAC0_EXT OPA1_P         | TIM1_CC0 #4<br>WTIM0_CDTI2 #4<br>WTIM1_CC0 #2 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US0_RTS #5 US1_RX #2<br>US2_CTS #5 US3_CTS<br>#2 U0_RTS #5 I2C0_SDA<br>#1 | CMU_CLK2 #2 LES_AL-<br>TEX0 PRS_CH5 #2<br>ACMP0_O #2 |

| PD7       | BUSADC0Y BUSADC0X<br>ADC0_EXTN OPA1_N                      | TIM1_CC1 #4<br>WTIM1_CC1 #2 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3                   | US1_TX #2 US3_CLK #1<br>U0_TX #6 I2C0_SCL #1                              | CMU_CLK0 #2 LES_AL-<br>TEX1 ACMP1_O #2               |

| PD8       | BU_VIN                                                     | WTIM1_CC2 #2                                                                       | US2_RTS #5                                                                | CMU_CLK1 #1                                          |

| PC6       | BUSACMP0Y BU-<br>SACMP0X OPA3_P<br>LCD_SEG32               | WTIM1_CC3 #2                                                                       | US0_RTS #2 US1_CTS<br>#3 I2C0_SDA #2                                      | LES_CH6                                              |

| PC7       | BUSACMP0Y BU-<br>SACMP0X OPA3_N<br>LCD_SEG33               | WTIM1_CC0 #3                                                                       | US0_CTS #2 US1_RTS<br>#3 I2C0_SCL #2                                      | LES_CH7                                              |

| PE4       | BUSDY BUSCX<br>LCD_COM0                                    | WTIM0_CC0 #0<br>WTIM1_CC1 #4                                                       | US0_CS #1 US1_CS #5<br>US3_CS #1 U0_RX #6<br>I2C0_SDA #7                  |                                                      |

| PE5       | BUSCY BUSDX<br>LCD_COM1                                    |                                                                                    |                                                                           |                                                      |

| PE6       | BUSDY BUSCX<br>LCD_COM2                                    | WTIM0_CC2 #0<br>WTIM1_CC3 #4                                                       | US0_RX #1 US3_TX #1                                                       | PRS_CH6 #2                                           |

| PE7       | BUSCY BUSDX<br>LCD_COM3                                    | WTIM1_CC0 #5                                                                       | US0_TX #1 US3_RX #1                                                       | PRS_CH7 #2                                           |

| PC8       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG34                         |                                                                                    | US0_CS #2                                                                 | LES_CH8 PRS_CH4 #0                                   |

| PC9       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG35                         |                                                                                    | US0_CLK #2                                                                | LES_CH9 PRS_CH5 #0<br>GPIO_EM4WU2                    |

| PC10      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_RX #2                                                                 | LES_CH10                                             |

| PC11      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_TX #2 I2C1_SDA #4                                                     | LES_CH11                                             |

| PC12      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0 BU-<br>SACMP1Y BUSACMP1X | TIM1_CC3 #0                                                                        | US0_RTS #3 US1_CTS<br>#4 US2_CTS #4 U0_RTS<br>#3                          | CMU_CLK0 #1<br>LES_CH12                              |

| PC13      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #1 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI0 #1<br>TIM1_CC0 #0 TIM1_CC2<br>#4 PCNT0_S0IN #0                          | US0_CTS #3 US1_RTS<br>#4 US2_RTS #4 U0_CTS<br>#3                          | LES_CH13                                             |

| PC14      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI1 #1<br>TIM1_CC1 #0 TIM1_CC3<br>#4 LETIM0_OUT0 #5<br>PCNT0_S1IN #0        | US0_CS #3 US1_CS #3<br>US2_RTS #3 US3_CS #2<br>U0_TX #3 LEU0_TX #5        | LES_CH14 PRS_CH0 #2                                  |

#### 5.15 Alternate Functionality Overview

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings and the associated GPIO pin. Refer to 5.14 GPIO Functionality Table for a list of functions available on each GPIO pin.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     | Alternate LOCATION |         |                                                                          |

|---------------|--------------------|---------|--------------------------------------------------------------------------|

| Functionality | 0 - 3              | 4 - 7   | Description                                                              |

|               | 0: PE13            | 4: PA6  |                                                                          |

| ACMP0_O       | 2: PD6<br>3: PB11  | 7: PB3  | Analog comparator ACMP0, digital output.                                 |

|               | 0: PF2             | 4: PA14 |                                                                          |

| ACMP1_O       | 2: PD7<br>3: PA12  | 7: PA5  | Analog comparator ACMP1, digital output.                                 |

|               | 0: PD7             |         |                                                                          |

| ADC0_EXTN     |                    |         | Analog to digital converter ADC0 external reference input negative pin.  |

|               | 0: PD6             |         |                                                                          |

| ADC0_EXTP     |                    |         | Analog to digital converter ADC0 external reference input positive pin.  |

|               | 0: PF1             |         |                                                                          |

| BOOT_RX       |                    |         | Bootloader RX.                                                           |

|               | 0: PF0             |         |                                                                          |

| BOOT_TX       |                    |         | Bootloader TX.                                                           |

|               | 0: PA8             |         |                                                                          |

| BU_STAT       |                    |         | Backup Power Domain status, whether or not the system is in backup mode. |

|               | 0: PD8             |         |                                                                          |

| BU_VIN        |                    |         | Battery input for Backup Power Domain.                                   |

|               | 0: PA12            |         |                                                                          |

| BU_VOUT       |                    |         | Power output for Backup Power Domain.                                    |

|               | 0: PC0<br>1: PF0   |         |                                                                          |

| CAN0_RX       | 2: PD0             |         | CAN0 RX.                                                                 |

#### Table 5.15. Alternate Functionality Overview

| Alternate     | LOC                                                                           | ATION                      |                                                      |  |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------|----------------------------|------------------------------------------------------|--|--|--|--|--|--|--|

| Functionality | 0 - 3                                                                         | 4 - 7                      | Description                                          |  |  |  |  |  |  |  |

| TIM0_CC0      | 0: PA0<br>2: PD1                                                              | 4: PF0<br>5: PC4<br>6: PA8 | Timer 0 Capture Compare input / output channel 0.    |  |  |  |  |  |  |  |

|               | 3: PB6                                                                        | 7: PA1                     |                                                      |  |  |  |  |  |  |  |

|               | 0: PA1                                                                        | 4: PF1<br>5: PC5           |                                                      |  |  |  |  |  |  |  |

| TIM0_CC1      | 2: PD2<br>3: PC0                                                              | 6: PA9<br>7: PA0           | Timer 0 Capture Compare input / output channel 1.    |  |  |  |  |  |  |  |

|               | 0: PA2                                                                        | 4: PF2                     |                                                      |  |  |  |  |  |  |  |

| TIM0_CC2      | 2: PD3<br>3: PC1                                                              | 6: PA10<br>7: PA13         | Timer 0 Capture Compare input / output channel 2.    |  |  |  |  |  |  |  |

| TIM0_CDTI0    | 0: PA3<br>1: PC13<br>2: PF3<br>3: PC2                                         | 4: PB7                     | Timer 0 Complimentary Dead Time Insertion channel 0. |  |  |  |  |  |  |  |

| TIM0_CDTI1    | 0: PA4<br>1: PC14<br>2: PF4<br>3: PC3                                         | 4: PB8                     | Timer 0 Complimentary Dead Time Insertion channel 1. |  |  |  |  |  |  |  |

| TIM0_CDTI2    | CDTI2<br>CDTI2<br>0: PA5<br>1: PC15<br>2: PF5<br>3: PC4<br>4: PB11<br>4: PB11 |                            | Timer 0 Complimentary Dead Time Insertion channel 2. |  |  |  |  |  |  |  |

| TIM1_CC0      | 0: PC13<br>1: PE10                                                            | 4: PD6<br>5: PF2           | Timer 1 Capture Compare input / output channel 0.    |  |  |  |  |  |  |  |

|               | 3: PB7                                                                        |                            |                                                      |  |  |  |  |  |  |  |

| TIM1_CC1      | 0: PC14<br>1: PE11                                                            | 4: PD7<br>5: PF3           | Timer 1 Capture Compare input / output channel 1.    |  |  |  |  |  |  |  |

|               | 3: PB8                                                                        |                            |                                                      |  |  |  |  |  |  |  |

| TIM1_CC2      | 0: PC15<br>1: PE12                                                            | 4: PC13<br>5: PF4          | Timer 1 Capture Compare input / output channel 2.    |  |  |  |  |  |  |  |

|               | 3: PB11                                                                       |                            |                                                      |  |  |  |  |  |  |  |

| TIM1_CC3      | 0: PC12<br>1: PE13<br>2: PB3<br>3: PB12                                       | 4: PC14<br>6: PF5          | Timer 1 Capture Compare input / output channel 3.    |  |  |  |  |  |  |  |

| U0_CTS        | 2: PA5<br>3: PC13                                                             | 4: PB7<br>5: PD5           | UART0 Clear To Send hardware flow control input.     |  |  |  |  |  |  |  |

| U0_RTS        | 2: PA6<br>3: PC12                                                             | 4: PB8<br>5: PD6           | UART0 Request To Send hardware flow control output.  |  |  |  |  |  |  |  |

| U0_RX         | 2: PA4<br>3: PC15                                                             | 4: PC5<br>5: PF2<br>6: PE4 | UART0 Receive input.                                 |  |  |  |  |  |  |  |

| Port    | Bus              | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7  | CH6  | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

|---------|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|-----|-----|

| APORT0X | BUSACMP1X        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PC15 | PC14 | PC13 | PC12 | PC11 | PC10 | PC9 | PC8 |

| APORT0Y | <b>BUSACMP1Y</b> |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PC15 | PC14 | PC13 | PC12 | PC11 | PC10 | PC9 | PC8 |

| APORT1X | BUSAX            |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |      | PA6  |      | PA4  |      | PA2  |     | PAO |

| APORT1Y | BUSAY            |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |      |      | PA5  |      | PA3  |      | PA1 |     |

| APORT2X | BUSBX            |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |      |      | PA5  |      | PA3  |      | PA1 |     |

| APORT2Y | BUSBY            |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |      | PA6  |      | PA4  |      | PA2  |     | PA0 |

| APORT3X | BUSCX            |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |      | PE6  |      | PE4  |      |      |     |     |

| APORT3Y | BUSCY            |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7  |      | PE5  |      |      |      |     |     |

| APORT4X | BUSDX            |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7  |      | PE5  |      |      |      |     |     |

| APORT4Y | BUSDY            |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |      | PE6  |      | PE4  |      |      |     |     |

# Table 5.17. ACMP1 Bus and Pin Mapping

| Port           | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СН9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

|----------------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| OP             | A0_   | N    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y        | BUSAY |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | 9Yd |     | PA4 |     | PA2 |     | PA0 |

| APORT3Y        | BUSCY |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y        | BUSDY |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| OF             | A0_   | P    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1X        | BUSAX |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT2X        | BUSBX |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| <b>APORT3X</b> | BUSCX |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | 93d |     | PE4 |     |     |     |     |

| APORT4X        | BUSDX |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

# Table 5.20. VDAC0 / OPA Bus and Pin Mapping

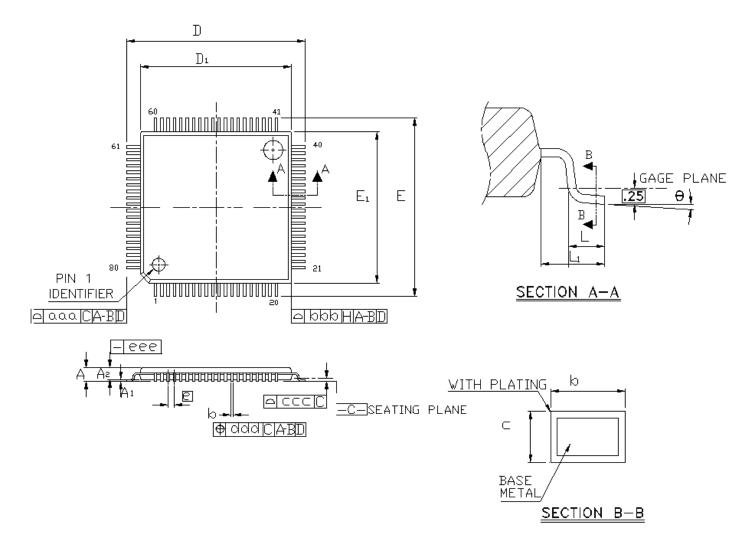

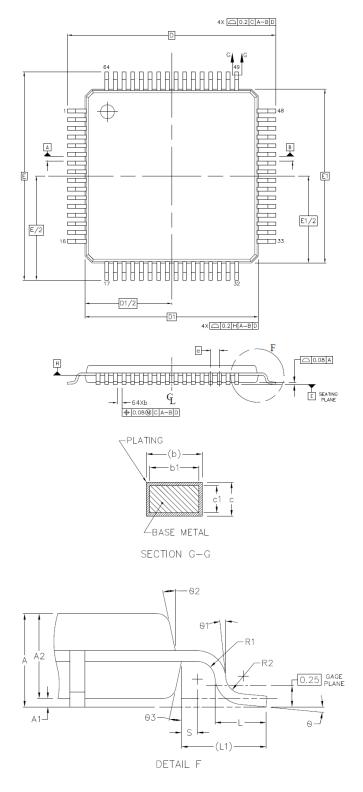

## 6. TQFP80 Package Specifications

### 6.1 TQFP80 Package Dimensions

Figure 6.1. TQFP80 Package Drawing

## 8. TQFP64 Package Specifications

#### 8.1 TQFP64 Package Dimensions

Figure 8.1. TQFP64 Package Drawing

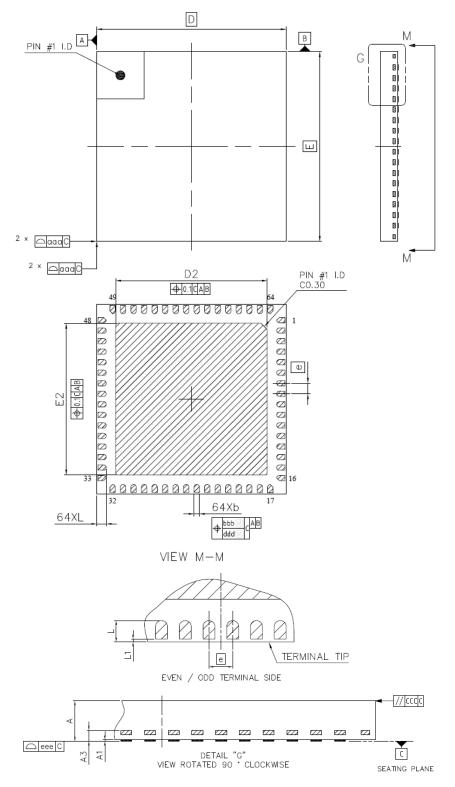

## 9. QFN64 Package Specifications

### 9.1 QFN64 Package Dimensions

Figure 9.1. QFN64 Package Drawing

#### Table 9.2. QFN64 PCB Land Pattern Dimensions

| Dimension | Тур  |

|-----------|------|

| C1        | 8.90 |

| C2        | 8.90 |

| E         | 0.50 |

| X1        | 0.30 |

| Y1        | 0.85 |

| X2        | 7.30 |

| Y2        | 7.30 |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

6. The stencil thickness should be 0.125 mm (5 mils).

7. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

8. A 3x3 array of 1.45 mm square openings on a 2.00 mm pitch can be used for the center ground pad.

9. A No-Clean, Type-3 solder paste is recommended.

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.