Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b520f128iq64-a |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. System Overview

## 3.1 Introduction

The Tiny Gecko Series 1 product family is well suited for any battery operated application as well as other systems requiring high performance and low energy consumption. This section gives a short introduction to the MCU system. The detailed functional description can be found in the Tiny Gecko Series 1 Reference Manual. Any behavior that does not conform to the specifications in this data sheet or the functional descriptions in the Tiny Gecko Series 1 Reference Manual are detailed in the EFM32TG11 Errata document.

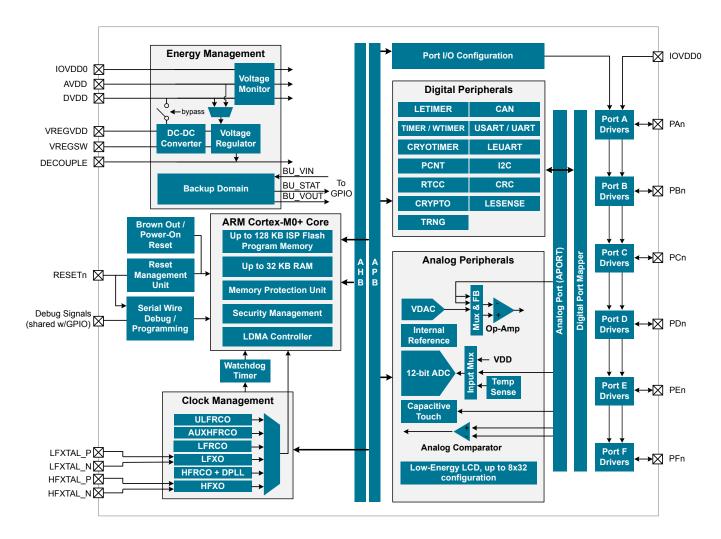

A block diagram of the Tiny Gecko Series 1 family is shown in Figure 3.1 Detailed EFM32TG11 Block Diagram on page 10. The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Detailed EFM32TG11 Block Diagram

### 3.2 Power

The EFM32TG11 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. An optional integrated DC-DC buck regulator can be utilized to further reduce the current consumption. The DC-DC regulator requires one external inductor and one external capacitor.

The EFM32TG11 device family includes support for internal supply voltage scaling, as well as two different power domain groups for peripherals. These enhancements allow for further supply current reductions and lower overall power consumption.

AVDD and VREGVDD need to be 1.8 V or higher for the MCU to operate across all conditions; however the rest of the system will operate down to 1.62 V, including the digital supply and I/O. This means that the device is fully compatible with 1.8 V components. Running from a sufficiently high supply, the device can use the DC-DC to regulate voltage not only for itself, but also for other PCB components, supplying up to a total of 200 mA.

## 3.2.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to turn off the power to unused RAM blocks, and it contains control registers for the DC-DC regulator and the Voltage Monitor (VMON). The VMON is used to monitor multiple supply voltages. It has multiple channels which can be programmed individually by the user to determine if a sensed supply has fallen below a chosen threshold.

### 3.2.2 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents and provides up to 90% efficiency in energy modes EM0, EM1, EM2 and EM3, and can supply up to 200 mA to the device and surrounding PCB components. Protection features include programmable current limiting, short-circuit protection, and dead-time protection. The DC-DC converter may also enter bypass mode when the input voltage is too low for efficient operation. In bypass mode, the DC-DC input supply is internally connected directly to its output through a low resistance switch. Bypass mode also supports in-rush current limiting to prevent input supply voltage droops due to excessive output current transients.

### 3.2.3 EM2 and EM3 Power Domains

The EFM32TG11 has three independent peripheral power domains for use in EM2 and EM3. Two of these domains are dynamic and can be shut down to save energy. Peripherals associated with the two dynamic power domains are listed in Table 3.1 EM2 and EM3 Peripheral Power Subdomains on page 11. If all of the peripherals in a peripheral power domain are unused, the power domain for that group will be powered off in EM2 and EM3, reducing the overall current consumption of the device. Other EM2, EM3, and EM4-capable peripherals and functions not listed in the table below reside on the primary power domain, which is always on in EM2 and EM3.

| Peripheral Power Domain 1 | Peripheral Power Domain 2 |

|---------------------------|---------------------------|

| ACMP0                     | ACMP1                     |

| PCNT0                     | CSEN                      |

| ADC0                      | VDAC0                     |

| LETIMER0                  | LEUART0                   |

| LESENSE                   | 12C0                      |

| APORT                     | 12C1                      |

| -                         | IDAC                      |

| -                         | LCD                       |

#### Table 3.1. EM2 and EM3 Peripheral Power Subdomains

### 3.3 General Purpose Input/Output (GPIO)

EFM32TG11 has up to 67 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

#### 3.4 Clocking

## 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32TG11. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

#### 3.4.2 Internal and External Oscillators

The EFM32TG11 supports two crystal oscillators and fully integrates four RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 4 to 48 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range. When crystal accuracy is not required, it can be operated in free-running mode at a number of factory-calibrated frequencies. A digital phase-locked loop (DPLL) feature allows the HFRCO to achieve higher accuracy and stability by referencing other available clock sources such as LFXO and HFXO.

- An integrated auxilliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC with a wide frequency range.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

#### 3.5 Counters/Timers and PWM

#### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

#### 3.5.2 Wide Timer/Counter (WTIMER)

WTIMER peripherals function just as TIMER peripherals, but are 32 bits wide. They keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each WTIMER is a 32-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the WTIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit WTIMER\_0 only.

#### 3.5.3 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes down to EM4H.

## 3.10 Core and Memory

## 3.10.1 Processor Core

The ARM Cortex-M processor includes a 32-bit RISC processor integrating the following features and tasks in the system:

- ARM Cortex-M0+ RISC processor

- Memory Protection Unit (MPU) supporting up to 8 memory segments

- Micro-Trace Buffer (MTB)

- Up to 128 kB flash program memory

- · Up to 32 kB RAM data memory

- · Configuration and event handling of all modules

- · 2-pin Serial-Wire debug interface

## 3.10.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block, whereas the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

## 3.10.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling so-phisticated operations to be implemented.

### 3.10.4 Bootloader

All devices come pre-programmed with a UART bootloader. This bootloader resides in flash and can be erased if it is not needed. More information about the bootloader protocol and usage can be found in *AN0003: UART Bootloader*. Application notes can be found on the Silicon Labs website (www.silabs.com/32bit-appnotes) or within Simplicity Studio in the [**Documentation**] area.

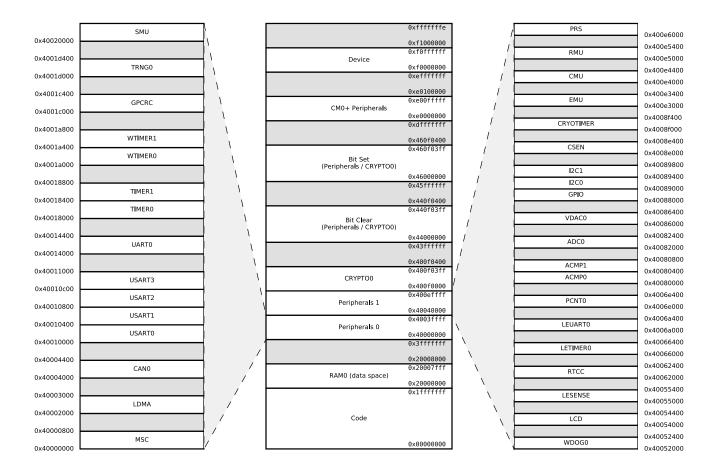

Figure 3.3. EFM32TG11 Memory Map — Peripherals

## 3.12 Configuration Summary

The features of the EFM32TG11 are a subset of the feature set described in the device reference manual. The table below describes device specific implementation of the features. Remaining modules support full configuration.

| Table 3.2. | Configuration | Summary |

|------------|---------------|---------|

|------------|---------------|---------|

| Module  | Configuration               | Pin Connections                 |

|---------|-----------------------------|---------------------------------|

| USART0  | IrDA, SmartCard             | US0_TX, US0_RX, US0_CLK, US0_CS |

| USART1  | I <sup>2</sup> S, SmartCard | US1_TX, US1_RX, US1_CLK, US1_CS |

| USART2  | IrDA, SmartCard, High-Speed | US2_TX, US2_RX, US2_CLK, US2_CS |

| USART3  | I <sup>2</sup> S, SmartCard | US3_TX, US3_RX, US3_CLK, US3_CS |

| TIMER0  | with DTI                    | TIM0_CC[2:0], TIM0_CDTI[2:0]    |

| TIMER1  | -                           | TIM1_CC[3:0]                    |

| WTIMER0 | with DTI                    | WTIM0_CC[2:0], WTIM0_CDTI[2:0]  |

| WTIMER1 | -                           | WTIM1_CC[3:0]                   |

| Parameter                                       | Symbol                | Test Condition                                                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-----------------------|----------------------------------------------------------------|-----|-----|-----|------|

| Max load current                                | I <sub>LOAD_MAX</sub> | Low noise (LN) mode, Heavy Drive <sup>2</sup> , T $\leq$ 85 °C | _   | _   | 200 | mA   |

|                                                 |                       | Low noise (LN) mode, Heavy<br>Drive <sup>2</sup> , T > 85 °C   | _   | _   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Medium Drive <sup>2</sup>                 | _   | _   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Light Drive <sup>2</sup>                  | _   | _   | 50  | mA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0         | _   | _   | 75  | μA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3         | _   | _   | 10  | mA   |

| DCDC nominal output ca-<br>pacitor <sup>5</sup> | C <sub>DCDC</sub>     | 25% tolerance                                                  | 1   | 4.7 | 4.7 | μF   |

| DCDC nominal output induc-<br>tor               | L <sub>DCDC</sub>     | 20% tolerance                                                  | 4.7 | 4.7 | 4.7 | μH   |

| Resistance in Bypass mode                       | R <sub>BYP</sub>      |                                                                | _   | 1.2 | TBD | Ω    |

### Note:

1. Due to internal dropout, the DC-DC output will never be able to reach its input voltage, V<sub>VREGVDD</sub>.

- 2. Drive levels are defined by configuration of the PFETCNT and NFETCNT registers. Light Drive: PFETCNT=NFETCNT=3; Medium Drive: PFETCNT=NFETCNT=7; Heavy Drive: PFETCNT=15.

- 3. LPCMPBIASEMxx refers to either LPCMPBIASEM234H in the EMU\_DCDCMISCCTRL register or LPCMPBIASEM01 in the EMU\_DCDCLOEM01CFG register, depending on the energy mode.

4. LP mode controller is a hysteretic controller that maintains the output voltage within the specified limits.

5. Output voltage under/over-shoot and regulation are specified with C<sub>DCDC</sub> 4.7 μF. Different settings for DCDCLNCOMPCTRL must be used if C<sub>DCDC</sub> is lower than 4.7 μF. See Application Note AN0948 for details.

| Parameter                  | Symbol            | Test Condition                       | Min | Тур | Мах | Unit |

|----------------------------|-------------------|--------------------------------------|-----|-----|-----|------|

| Output fall time, From 70% | t <sub>IOOF</sub> | C <sub>L</sub> = 50 pF,              | —   | 1.8 | —   | ns   |

| to 30% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              |     | 4.5 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Output rise time, From 30% | t <sub>IOOR</sub> | C <sub>L</sub> = 50 pF,              |     | 2.2 |     | ns   |

| to 70% of V <sub>IO</sub>  |                   | DRIVESTRENGTH <sup>1</sup> = STRONG, |     |     |     |      |

|                            |                   | SLEWRATE = 0x6 <sup>1</sup>          |     |     |     |      |

|                            |                   | C <sub>L</sub> = 50 pF,              | _   | 7.4 | _   | ns   |

|                            |                   | DRIVESTRENGTH <sup>1</sup> = WEAK,   |     |     |     |      |

|                            |                   | SLEWRATE <sup>1</sup> = 0x6          |     |     |     |      |

| Note:                      | 1                 | 1                                    | 1   | 1   | 1   | 1    |

| Parameter                                 | Symbol                 | Test Condition                                             | Min | Тур      | Мах | Unit |

|-------------------------------------------|------------------------|------------------------------------------------------------|-----|----------|-----|------|

| Hysteresis (V <sub>CM</sub> = 1.25 V,     | V <sub>ACMPHYST</sub>  | HYSTSEL <sup>5</sup> = HYST0                               | TBD | 0        | TBD | mV   |

| $BIASPROG^4 = 0x10, FULL-BIAS^4 = 1)$     |                        | HYSTSEL <sup>5</sup> = HYST1                               | TBD | 18       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST2                               | TBD | 33       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST3                               | TBD | 46       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST4                               | TBD | 57       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST5                               | TBD | 68       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST6                               | TBD | 79       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST7                               | TBD | 90       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST8                               | TBD | 0        | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST9                               | TBD | -18      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST10                              | TBD | -33      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST11                              | TBD | -45      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST12                              | TBD | -57      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST13                              | TBD | -67      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST14                              | TBD | -78      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST15                              | TBD | -88      | TBD | mV   |

| Comparator delay <sup>3</sup>             | t <sub>ACMPDELAY</sub> | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                        | _   | 30       | _   | μs   |

|                                           |                        | $BIASPROG^4 = 0x10, FULLBIAS^4 = 0$                        | _   | 3.7      | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1 |     | 360      | _   | ns   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1 | _   | 35       | _   | ns   |

| Offset voltage                            | VACMPOFFSET            | BIASPROG <sup>4</sup> =0x10, FULLBIAS <sup>4</sup><br>= 1  | TBD | _        | TBD | mV   |

| Reference voltage                         | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | TBD | 1.25     | TBD | V    |

|                                           |                        | Internal 2.5 V reference                                   | TBD | 2.5      | TBD | V    |

| Capacitive sense internal re-<br>sistance | R <sub>CSRES</sub>     | CSRESSEL <sup>6</sup> = 0                                  | —   | infinite | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 1                                  | —   | 15       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 2                                  |     | 27       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 3                                  | —   | 39       |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 4                                  |     | 51       |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 5                                  | _   | 100      | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 6                                  |     | 162      | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 7                                  |     | 235      | _   | kΩ   |

| Parameter                   | Symbol                                         | Test Condition                                                                   | Min               | Тур             | Мах             | Unit      |

|-----------------------------|------------------------------------------------|----------------------------------------------------------------------------------|-------------------|-----------------|-----------------|-----------|

| Note:                       | l                                              |                                                                                  |                   |                 |                 |           |

| 1. Supply current the load. | specifications are for VD                      | AC circuitry operating with static outpo                                         | ut only and do n  | not include cur | rent required   | to drive  |

|                             | ode, the output is define<br>ngle-ended range. | d as the difference between two single                                           | e-ended outputs   | s. Absolute vol | ltage on each   | output is |

| 3. Entire range is          | monotonic and has no m                         | nissing codes.                                                                   |                   |                 |                 |           |

|                             | PERCLK is dependent<br>DAC module is enabled   | on HFPERCLK frequency. This currer<br>in the CMU.                                | nt contributes to | the total supp  | bly current use | ed when   |

|                             |                                                | pe from 10% to 90% of full scale. Offs<br>at 10% of full scale with the measured |                   | by comparing    | actual VDAC     | output at |

|                             |                                                | $\Delta V_{OUT}$ ), VDAC output at 90% of full set                               | aala              |                 |                 |           |

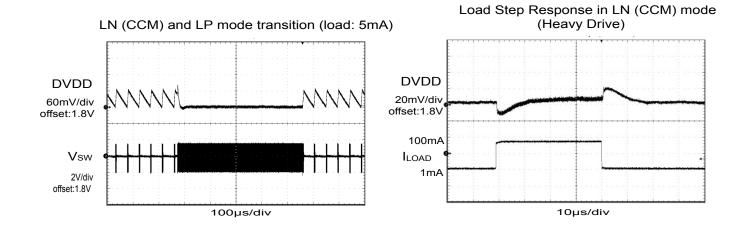

Figure 4.9. DC-DC Converter Transition Waveforms

| Pin Name | Pin(s)   | Description                                                                         | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|-------------------------------------------------------------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB4      | 10       | GPIO                                                                                | PB5      | 11     | GPIO                                                                                                                                                                                                        |

| PB6      | 12       | GPIO                                                                                | PC0      | 13     | GPIO (5V)                                                                                                                                                                                                   |

| PC1      | 14       | GPIO (5V)                                                                           | PC2      | 15     | GPIO (5V)                                                                                                                                                                                                   |

| PC3      | 16       | GPIO (5V)                                                                           | PC4      | 17     | GPIO                                                                                                                                                                                                        |

| PC5      | 18       | GPIO                                                                                | PB7      | 19     | GPIO                                                                                                                                                                                                        |

| PB8      | 20       | GPIO                                                                                | PA8      | 21     | GPIO                                                                                                                                                                                                        |

| PA9      | 22       | GPIO                                                                                | PA10     | 23     | GPIO                                                                                                                                                                                                        |

| PA12     | 24       | GPIO                                                                                | PA13     | 25     | GPIO (5V)                                                                                                                                                                                                   |

| PA14     | 26       | GPIO                                                                                | RESETn   | 27     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 28       | GPIO                                                                                | PB12     | 29     | GPIO                                                                                                                                                                                                        |

| AVDD     | 30<br>34 | Analog power supply.                                                                | PB13     | 31     | GPIO                                                                                                                                                                                                        |

| PB14     | 32       | GPIO                                                                                | PD0      | 35     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 36       | GPIO                                                                                | PD2      | 37     | GPIO (5V)                                                                                                                                                                                                   |

| PD3      | 38       | GPIO                                                                                | PD4      | 39     | GPIO                                                                                                                                                                                                        |

| PD5      | 40       | GPIO                                                                                | PD6      | 41     | GPIO                                                                                                                                                                                                        |

| PD7      | 42       | GPIO                                                                                | PD8      | 43     | GPIO                                                                                                                                                                                                        |

| PC6      | 44       | GPIO                                                                                | PC7      | 45     | GPIO                                                                                                                                                                                                        |

| VREGSW   | 47       | DCDC regulator switching node                                                       | VREGVDD  | 48     | Voltage regulator VDD input                                                                                                                                                                                 |

| DVDD     | 49       | Digital power supply.                                                               | DECOUPLE | 50     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PE4      | 52       | GPIO                                                                                | PE5      | 53     | GPIO                                                                                                                                                                                                        |

| PE6      | 54       | GPIO                                                                                | PE7      | 55     | GPIO                                                                                                                                                                                                        |

| PC8      | 56       | GPIO                                                                                | PC9      | 57     | GPIO                                                                                                                                                                                                        |

| PC10     | 58       | GPIO (5V)                                                                           | PC11     | 59     | GPIO (5V)                                                                                                                                                                                                   |

| PC12     | 60       | GPIO (5V)                                                                           | PC13     | 61     | GPIO (5V)                                                                                                                                                                                                   |

| PC14     | 62       | GPIO (5V)                                                                           | PC15     | 63     | GPIO (5V)                                                                                                                                                                                                   |

| PF0      | 64       | GPIO (5V)                                                                           | PF1      | 65     | GPIO (5V)                                                                                                                                                                                                   |

| PF2      | 66       | GPIO                                                                                | PF3      | 67     | GPIO                                                                                                                                                                                                        |

| PF4      | 68       | GPIO                                                                                | PF5      | 69     | GPIO                                                                                                                                                                                                        |

| PE8      | 71       | GPIO                                                                                | PE9      | 72     | GPIO                                                                                                                                                                                                        |

| PE10     | 73       | GPIO                                                                                | PE11     | 74     | GPIO                                                                                                                                                                                                        |

| BODEN    | 75       | Brown-Out Detector Enable. This pin<br>may be left disconnected or tied to<br>AVDD. | PE12     | 76     | GPIO                                                                                                                                                                                                        |

| PE13     | 77       | GPIO                                                                                | PE14     | 78     | GPIO                                                                                                                                                                                                        |

| Pin Name | Pin(s)   | Description                                                                                              | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|----------|----------------------------------------------------------------------------------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13       | GPIO                                                                                                     | PC5      | 14     | GPIO                                                                                                                                                                                                        |

| PB7      | 15       | GPIO                                                                                                     | PB8      | 16     | GPIO                                                                                                                                                                                                        |

| PA8      | 17       | GPIO                                                                                                     | PA12     | 18     | GPIO                                                                                                                                                                                                        |

| PA14     | 19       | GPIO                                                                                                     | RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21       | GPIO                                                                                                     | PB12     | 22     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.                                                                                     | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26       | GPIO                                                                                                     | PD0      | 29     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 30       | GPIO                                                                                                     | PD3      | 31     | GPIO                                                                                                                                                                                                        |

| PD4      | 32       | GPIO                                                                                                     | PD5      | 33     | GPIO                                                                                                                                                                                                        |

| PD6      | 34       | GPIO                                                                                                     | PD7      | 35     | GPIO                                                                                                                                                                                                        |

| PD8      | 36       | GPIO                                                                                                     | PC7      | 37     | GPIO                                                                                                                                                                                                        |

| VREGVSS  | 38       | Voltage regulator VSS                                                                                    | VREGSW   | 39     | DCDC regulator switching node                                                                                                                                                                               |

| VREGVDD  | 40       | Voltage regulator VDD input                                                                              | DVDD     | 41     | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 42       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PE4      | 43     | GPIO                                                                                                                                                                                                        |

| PE5      | 44       | GPIO                                                                                                     | PE6      | 45     | GPIO                                                                                                                                                                                                        |

| PE7      | 46       | GPIO                                                                                                     | PC12     | 47     | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 48       | GPIO (5V)                                                                                                | PF0      | 49     | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50       | GPIO (5V)                                                                                                | PF2      | 51     | GPIO                                                                                                                                                                                                        |

| PF3      | 52       | GPIO                                                                                                     | PF4      | 53     | GPIO                                                                                                                                                                                                        |

| PF5      | 54       | GPIO                                                                                                     | PE8      | 57     | GPIO                                                                                                                                                                                                        |

| PE9      | 58       | GPIO                                                                                                     | PE10     | 59     | GPIO                                                                                                                                                                                                        |

| PE11     | 60       | GPIO                                                                                                     | PE12     | 61     | GPIO                                                                                                                                                                                                        |

| PE13     | 62       | GPIO                                                                                                     | PE14     | 63     | GPIO                                                                                                                                                                                                        |

| PE15     | 64       | GPIO                                                                                                     |          |        |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

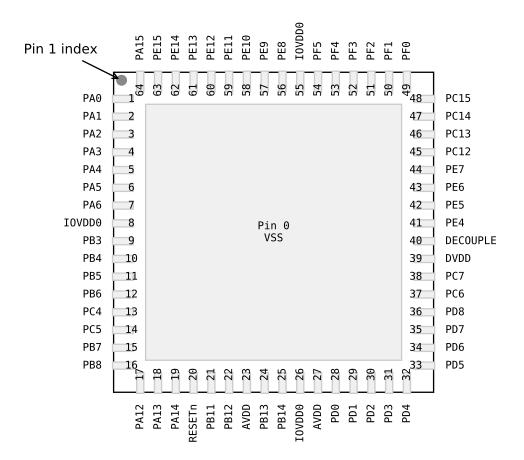

## Figure 5.7. EFM32TG11B3xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>26<br>55 | Digital IO power supply 0. | PB3      | 9      | GPIO        |

| PB4      | 10            | GPIO                       | PB5      | 11     | GPIO        |

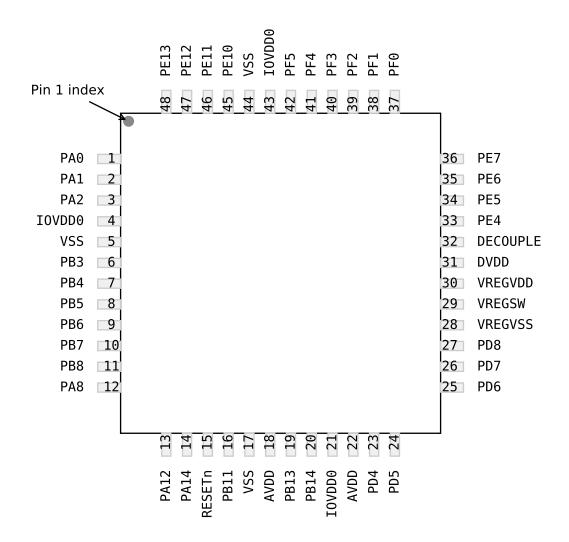

## Figure 5.9. EFM32TG11B5xx in QFP48 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description | Pin Name | Pin(s)        | Description                |

|----------|---------------|-------------|----------|---------------|----------------------------|

| PA0      | 1             | GPIO        | PA1      | 2             | GPIO                       |

| PA2      | 3             | GPIO        | IOVDD0   | 4<br>21<br>43 | Digital IO power supply 0. |

| VSS      | 5<br>17<br>44 | Ground      | PB3      | 6             | GPIO                       |

| PB4      | 7             | GPIO        | PB5      | 8             | GPIO                       |

| PB6      | 9             | GPIO        | PB7      | 10            | GPIO                       |

| Pin Name | Pin(s) | Description           | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|-----------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB7      | 11     | GPIO                  | PB8      | 12       | GPIO                                                                                                                                                                                                        |

| PA8      | 13     | GPIO                  | PA9      | 14       | GPIO                                                                                                                                                                                                        |

| PA10     | 15     | GPIO                  | RESETn   | 16       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 17     | GPIO                  | AVDD     | 19<br>23 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 20     | GPIO                  | PB14     | 21       | GPIO                                                                                                                                                                                                        |

| PD4      | 24     | GPIO                  | PD5      | 25       | GPIO                                                                                                                                                                                                        |

| PD6      | 26     | GPIO                  | PD7      | 27       | GPIO                                                                                                                                                                                                        |

| DVDD     | 28     | Digital power supply. | DECOUPLE | 29       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PC8      | 30     | GPIO                  | PC9      | 31       | GPIO                                                                                                                                                                                                        |

| PC10     | 32     | GPIO (5V)             | PC11     | 33       | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 34     | GPIO (5V)             | PC14     | 35       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 36     | GPIO (5V)             | PF0      | 37       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 38     | GPIO (5V)             | PF2      | 39       | GPIO                                                                                                                                                                                                        |

| PF3      | 40     | GPIO                  | PF4      | 41       | GPIO                                                                                                                                                                                                        |

| PF5      | 42     | GPIO                  | PE10     | 45       | GPIO                                                                                                                                                                                                        |

| PE11     | 46     | GPIO                  | PE12     | 47       | GPIO                                                                                                                                                                                                        |

| PE13     | 48     | GPIO                  |          |          |                                                                                                                                                                                                             |

| Note:    |        |                       |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Alternate     | LOCATION                               |                   |                                                                                                                                                            |  |  |

|---------------|----------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Functionality | 0 - 3                                  | 4 - 7             | Description                                                                                                                                                |  |  |

| US2_CLK       | 0: PC4<br>1: PB5<br>2: PA9<br>3: PA15  | 5: PF2            | USART2 clock input / output.                                                                                                                               |  |  |

| US2_CS        | 0: PC5<br>1: PB6<br>2: PA10<br>3: PB11 | 5: PF5            | USART2 chip select input / output.                                                                                                                         |  |  |

| US2_CTS       | 0: PC1<br>1: PB12                      | 4: PC12<br>5: PD6 | USART2 Clear To Send hardware flow control input.                                                                                                          |  |  |

| US2_RTS       | 0: PC0<br>2: PA12<br>3: PC14           | 4: PC13<br>5: PD8 | USART2 Request To Send hardware flow control output.                                                                                                       |  |  |

| US2_RX        | 0: PC3<br>1: PB4<br>2: PA8<br>3: PA14  | 5: PF1            | USART2 Asynchronous Receive.<br>USART2 Synchronous mode Master Input / Slave Output (MISO).                                                                |  |  |

| US2_TX        | 0: PC2<br>1: PB3<br>3: PA13            | 5: PF0            | USART2 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART2 Synchronous mode Master Output / Slave Input (MOSI). |  |  |

| US3_CLK       | 0: PA2<br>1: PD7<br>2: PD4             |                   | USART3 clock input / output.                                                                                                                               |  |  |

| US3_CS        | 0: PA3<br>1: PE4<br>2: PC14<br>3: PC0  |                   | USART3 chip select input / output.                                                                                                                         |  |  |

| US3_CTS       | 0: PA4<br>1: PE5<br>2: PD6             |                   | USART3 Clear To Send hardware flow control input.                                                                                                          |  |  |

| US3_RTS       | 0: PA5<br>1: PC1<br>2: PA14<br>3: PC15 |                   | USART3 Request To Send hardware flow control output.                                                                                                       |  |  |

| US3_RX        | 0: PA1<br>1: PE7<br>2: PB7             |                   | USART3 Asynchronous Receive.<br>USART3 Synchronous mode Master Input / Slave Output (MISO).                                                                |  |  |

| US3_TX        | 0: PA0<br>1: PE6<br>2: PB3             |                   | USART3 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART3 Synchronous mode Master Output / Slave Input (MOSI). |  |  |

| VDAC0_EXT     | 0: PD6                                 |                   | Digital to analog converter VDAC0 external reference input pin.                                                                                            |  |  |

| Dimension | Min       | Тур       | Мах  |  |  |

|-----------|-----------|-----------|------|--|--|

| A         | 0.70      | 0.75      | 0.80 |  |  |

| A1        | 0.00      | _         | 0.05 |  |  |

| b         | 0.20      | 0.25      | 0.30 |  |  |

| A3        | 0.203 REF |           |      |  |  |

| D         | 9.00 BSC  |           |      |  |  |

| е         | 0.40 BSC  |           |      |  |  |

| E         | 9.00 BSC  |           |      |  |  |

| D2        | 7.10      | 7.20 7.30 |      |  |  |

| E2        | 7.10      | 7.20      | 7.30 |  |  |

| L         | 0.35      | 0.40      | 0.45 |  |  |

| ааа       | 0.10      |           |      |  |  |

| bbb       | 0.10      |           |      |  |  |

| ссс       | 0.10      |           |      |  |  |

| ddd       | 0.05      |           |      |  |  |

| eee       | 0.08      |           |      |  |  |

| Nata      |           |           |      |  |  |

## Table 7.1. QFN80 Package Dimensions

## Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| Dimension | Min            | Тур       | Мах  |  |  |

|-----------|----------------|-----------|------|--|--|

| A         | _              | 1.15      | 1.20 |  |  |

| A1        | 0.05           | _         | 0.15 |  |  |

| A2        | 0.95           | 1.00      | 1.05 |  |  |

| b         | 0.17           | 0.22 0.27 |      |  |  |

| b1        | 0.17           | 0.20      | 0.23 |  |  |

| с         | 0.09           | _         | 0.20 |  |  |

| c1        | 0.09           | —         | 0.16 |  |  |

| D         | 12.00 BSC      |           |      |  |  |

| D1        | 10.00 BSC      |           |      |  |  |

| e         | 0.50 BSC       |           |      |  |  |

| E         | 12.00 BSC      |           |      |  |  |

| E1        | 10.00 BSC      |           |      |  |  |

| L         | 0.45 0.60 0.75 |           |      |  |  |

| L1        | 1.00 REF       |           |      |  |  |

| R1        | 0.08           | —         | —    |  |  |

| R2        | 0.08           | _         | 0.20 |  |  |

| S         | 0.20           |           |      |  |  |

| θ         | 0              | 3.5 7     |      |  |  |

| θ1        | 0              | — 0.10    |      |  |  |

| θ2        | 11             | 12 13     |      |  |  |

| θ3        | 11             | 12 13     |      |  |  |

| Note:     |                | ·         |      |  |  |

## Table 8.1. TQFP64 Package Dimensions

Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 8.2 TQFP64 PCB Land Pattern

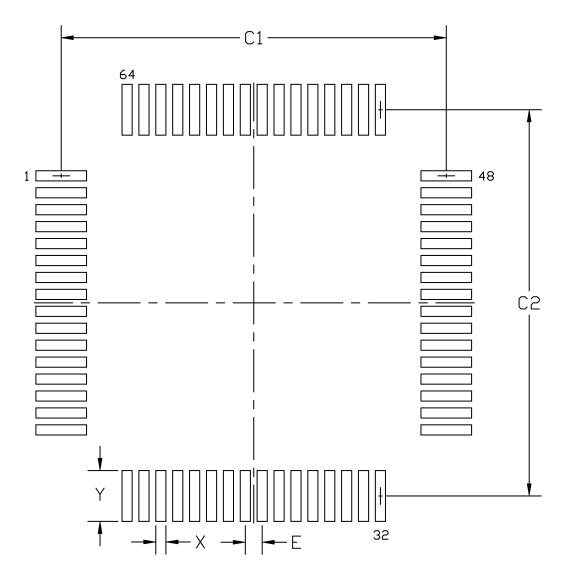

Figure 8.2. TQFP64 PCB Land Pattern Drawing

## 9.2 QFN64 PCB Land Pattern

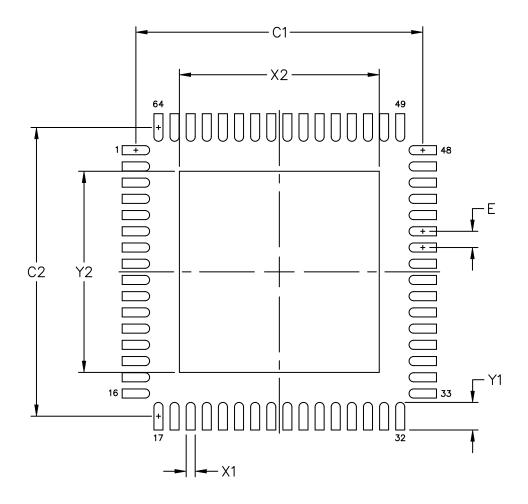

Figure 9.2. QFN64 PCB Land Pattern Drawing