Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 63                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b540f64gq80-ar |

|    | 3.10 Core and Memory                                 | .16  |

|----|------------------------------------------------------|------|

|    | 3.10.1 Processor Core                                |      |

|    | 3.10.2 Memory System Controller (MSC)                |      |

|    | 3.10.3 Linked Direct Memory Access Controller (LDMA) |      |

|    | 3.10.4 Bootloader                                    |      |

|    | 3.11 Memory Map                                      | .17  |

|    | 3.12 Configuration Summary                           | .18  |

| 4. | Electrical Specifications                            | . 19 |

|    | 4.1 Electrical Characteristics                       |      |

|    | 4.1.1 Absolute Maximum Ratings                       |      |

|    | 4.1.2 Operating Conditions                           |      |

|    | 4.1.3 Thermal Characteristics                        | .22  |

|    | 4.1.4 DC-DC Converter                                | .23  |

|    | 4.1.5 Backup Supply Domain                           | .25  |

|    | 4.1.6 Current Consumption                            |      |

|    | 4.1.7 Wake Up Times                                  |      |

|    | 4.1.8 Brown Out Detector (BOD)                       |      |

|    | 4.1.9 Oscillators                                    |      |

|    | 4.1.10 Flash Memory Characteristics                  |      |

|    | 4.1.11 General-Purpose I/O (GPIO)                    |      |

|    | 4.1.12 Voltage Monitor (VMON)                        |      |

|    | 4.1.13 Analog to Digital Converter (ADC)             |      |

|    | 4.1.14 Analog Comparator (ACMP)                      |      |

|    | 4.1.16 Capacitive Sense (CSEN)                       |      |

|    | 4.1.17 Operational Amplifier (OPAMP)                 |      |

|    | 4.1.18 LCD Driver                                    |      |

|    | 4.1.19 Pulse Counter (PCNT)                          |      |

|    | 4.1.20 Analog Port (APORT)                           |      |

|    | 4.1.21 I2C                                           |      |

|    | 4.1.22 USART SPI                                     |      |

|    | 4.2 Typical Performance Curves                       | .64  |

|    | 4.2.1 Supply Current                                 |      |

|    | 4.2.2 DC-DC Converter                                |      |

| 5. | Pin Definitions                                      | 72   |

| •  | 5.1 EFM32TG11B5xx in QFP80 Device Pinout             |      |

|    | 5.2 EFM32TG11B5xx in QFN80 Device Pinout             |      |

|    |                                                      |      |

|    | 5.3 EFM32TG11B5xx in QFP64 Device Pinout             | .78  |

|    | 5.4 EFM32TG11B3xx in QFP64 Device Pinout             | .80  |

|    | 5.5 EFM32TG11B1xx in QFP64 Device Pinout             | .82  |

|    | 5.6 EFM32TG11B5xx in QFN64 Device Pinout             | .84  |

|    | 5.7 EFM32TG11B3xx in QFN64 Device Pinout             | .86  |

|    | 5.8 FFM32TG11R1xx in OFN64 Device Pinout             | 88   |

#### 3.3 General Purpose Input/Output (GPIO)

EFM32TG11 has up to 67 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

#### 3.4 Clocking

### 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32TG11. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

#### 3.4.2 Internal and External Oscillators

The EFM32TG11 supports two crystal oscillators and fully integrates four RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 4 to 48 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system. The HFRCO employs fast startup at minimal

energy consumption combined with a wide frequency range. When crystal accuracy is not required, it can be operated in free-running mode at a number of factory-calibrated frequencies. A digital phase-locked loop (DPLL) feature allows the HFRCO to achieve

higher accuracy and stability by referencing other available clock sources such as LFXO and HFXO.

- An integrated auxilliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC with a wide frequency range.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

# 3.5 Counters/Timers and PWM

### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER 0 only.

#### 3.5.2 Wide Timer/Counter (WTIMER)

WTIMER peripherals function just as TIMER peripherals, but are 32 bits wide. They keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each WTIMER is a 32-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the WTIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit WTIMER 0 only.

#### 3.5.3 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes down to EM4H.

# 4. Electrical Specifications

#### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on  $T_{AMB}$ =25 °C and  $V_{DD}$ = 3.3 V, by production test and/or technology characterization.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

Refer to 4.1.2.1 General Operating Conditions for more details about operational supply and temperature limits.

### 4.1.1 Absolute Maximum Ratings

Stresses above those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

**Table 4.1. Absolute Maximum Ratings**

| Parameter                           | Symbol                 | Test Condition                         | Min  | Тур | Max                            | Unit   |

|-------------------------------------|------------------------|----------------------------------------|------|-----|--------------------------------|--------|

| Storage temperature range           | T <sub>STG</sub>       |                                        | -50  | _   | 150                            | °C     |

| Voltage on any supply pin           | $V_{\text{DDMAX}}$     |                                        | -0.3 | _   | 3.8                            | V      |

| Voltage ramp rate on any supply pin | V <sub>DDRAMPMAX</sub> |                                        | _    | _   | 1                              | V / µs |

| DC voltage on any GPIO pin          | V <sub>DIGPIN</sub>    | 5V tolerant GPIO pins <sup>1 2 3</sup> | -0.3 | _   | Min of 5.25<br>and IOVDD<br>+2 | V      |

|                                     |                        | LCD pins <sup>3</sup>                  | -0.3 | _   | Min of 3.8<br>and IOVDD<br>+2  | V      |

|                                     |                        | Standard GPIO pins                     | -0.3 | _   | IOVDD+0.3                      | V      |

| Total current into VDD power lines  | I <sub>VDDMAX</sub>    | Source                                 | _    | _   | 200                            | mA     |

| Total current into VSS ground lines | I <sub>VSSMAX</sub>    | Sink                                   | _    | _   | 200                            | mA     |

| Current per I/O pin                 | I <sub>IOMAX</sub>     | Sink                                   | _    | _   | 50                             | mA     |

|                                     |                        | Source                                 | _    | _   | 50                             | mA     |

| Current for all I/O pins            | I <sub>IOALLMAX</sub>  | Sink                                   | _    | _   | 200                            | mA     |

|                                     |                        | Source                                 | _    | _   | 200                            | mA     |

| Junction temperature                | TJ                     | -G grade devices                       | -40  | _   | 105                            | °C     |

|                                     |                        | -I grade devices                       | -40  | _   | 125                            | °C     |

#### Note:

- 1. When a GPIO pin is routed to the analog module through the APORT, the maximum voltage = IOVDD.

- 2. Valid for IOVDD in valid operating range or when IOVDD is undriven (high-Z). If IOVDD is connected to a low-impedance source below the valid operating range (e.g. IOVDD shorted to VSS), the pin voltage maximum is IOVDD + 0.3 V, to avoid exceeding the maximum IO current specifications.

- 3. To operate above the IOVDD supply rail, over-voltage tolerance must be enabled according to the GPIO\_Px\_OVTDIS register. Pins with over-voltage tolerance disabled have the same limits as Standard GPIO.

# 4.1.12 Voltage Monitor (VMON)

Table 4.19. Voltage Monitor (VMON)

| Parameter                          | Symbol                  | Test Condition                                                   | Min  | Тур  | Max | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------|------|------|-----|------|

| Supply current (including I_SENSE) | I <sub>VMON</sub>       | In EM0 or EM1, 1 supply monitored, T ≤ 85 °C                     | _    | 6.3  | TBD | μΑ   |

|                                    |                         | In EM0 or EM1, 4 supplies monitored, T ≤ 85 °C                   | _    | 12.5 | TBD | μΑ   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and above threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 1 supply monitored and below threshold       | _    | 62   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all above threshold | _    | 99   | _   | nA   |

|                                    |                         | In EM2, EM3 or EM4, 4 supplies monitored and all below threshold | _    | 99   | _   | nA   |

| Loading of monitored supply        | I <sub>SENSE</sub>      | In EM0 or EM1                                                    | _    | 2    | _   | μA   |

|                                    |                         | In EM2, EM3 or EM4                                               | _    | 2    | _   | nA   |

| Threshold range                    | V <sub>VMON_RANGE</sub> |                                                                  | 1.62 | _    | 3.4 | V    |

| Threshold step size                | N <sub>VMON_STESP</sub> | Coarse                                                           | _    | 200  | _   | mV   |

|                                    |                         | Fine                                                             | _    | 20   | _   | mV   |

| Response time                      | t <sub>VMON_RES</sub>   | Supply drops at 1V/µs rate                                       | _    | 460  | _   | ns   |

| Hysteresis                         | V <sub>VMON_HYST</sub>  |                                                                  | _    | 26   |     | mV   |

| Parameter                                               | Symbol                   | Test Condition                                                                              | Min | Тур  | Max | Unit |

|---------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------|-----|------|-----|------|

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal 1.25V reference                                            | _   | 60.4 | _   | dB   |

| Noise band limited to 250 kHz                           |                          | 500 ksps, single-ended, internal 2.5V reference                                             | _   | 61.6 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                               | _   | 64.0 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 1.25V reference                                            | _   | 63.3 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 2.5V reference                                             | _   | 64.4 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                  | _   | 65.8 | _   | dB   |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference                                            | _   | 65.3 | _   | dB   |

| Noise band limited to 22 kHz                            |                          | 500 ksps, single-ended, internal 2.5V reference                                             | _   | 66.7 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                  | _   | 68.5 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 1.25V reference                                            | _   | 67.8 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 2.5V reference                                             | _   | 69.0 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                               | _   | 70.0 | _   | dB   |

| Total harmonic distortion                               | THD                      |                                                                                             | _   | 70.2 | _   | dB   |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                                                             | TBD | _    | TBD | LSB  |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                                                             | TBD | _    | TBD | LSB  |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T = 25 °C                                                                                   | TBD | _    | TBD | mV   |

|                                                         |                          | Across operating temperature range                                                          | TBD | _    | TBD | mV   |

| Gain error <sup>5</sup>                                 | $V_{GAIN}$               | T = 25 °C, Low-noise internal reference (REFSEL = 1V25LN or 2V5LN)                          | TBD | _    | TBD | %    |

|                                                         |                          | Across operating temperature range, Low-noise internal reference (REFSEL = 1V25LN or 2V5LN) | TBD | _    | TBD | %    |

| External load capactiance,<br>OUTSCALE=0                | C <sub>LOAD</sub>        |                                                                                             | _   | _    | 75  | pF   |

| Parameter                             | Symbol           | Test Condition                                        | Min | Тур  | Max | Unit  |

|---------------------------------------|------------------|-------------------------------------------------------|-----|------|-----|-------|

| Open-loop gain                        | G <sub>OL</sub>  | DRIVESTRENGTH = 3                                     | _   | 135  | _   | dB    |

|                                       |                  | DRIVESTRENGTH = 2                                     | _   | 137  | _   | dB    |

|                                       |                  | DRIVESTRENGTH = 1                                     | _   | 121  | _   | dB    |

|                                       |                  | DRIVESTRENGTH = 0                                     | _   | 109  | _   | dB    |

| Loop unit-gain frequency <sup>7</sup> | UGF              | DRIVESTRENGTH = 3, Buffer connection                  | _   | 3.38 | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 2, Buffer connection                  | _   | 0.9  | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 1, Buffer connection                  | _   | 132  | _   | kHz   |

|                                       |                  | DRIVESTRENGTH = 0, Buffer connection                  | _   | 34   | _   | kHz   |

|                                       |                  | DRIVESTRENGTH = 3, 3x Gain connection                 | _   | 2.57 | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 2, 3x Gain connection                 | _   | 0.71 | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 1, 3x Gain connection                 | _   | 113  | _   | kHz   |

|                                       |                  | DRIVESTRENGTH = 0, 3x Gain connection                 | _   | 28   | _   | kHz   |

| Phase margin                          | PM               | DRIVESTRENGTH = 3, Buffer connection                  | _   | 67   | _   | 0     |

|                                       |                  | DRIVESTRENGTH = 2, Buffer connection                  | _   | 69   | _   | 0     |

|                                       |                  | DRIVESTRENGTH = 1, Buffer connection                  | _   | 63   | _   | o     |

|                                       |                  | DRIVESTRENGTH = 0, Buffer connection                  | _   | 68   | _   | o     |

| Output voltage noise                  | N <sub>OUT</sub> | DRIVESTRENGTH = 3, Buffer connection, 10 Hz - 10 MHz  | _   | 146  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 2, Buffer connection, 10 Hz - 10 MHz  | _   | 163  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 1, Buffer connection, 10 Hz - 1 MHz   | _   | 170  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 0, Buffer connection, 10 Hz - 1 MHz   | _   | 176  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 3, 3x Gain connection, 10 Hz - 10 MHz | _   | 313  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 2, 3x Gain connection, 10 Hz - 10 MHz | _   | 271  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 1, 3x Gain connection, 10 Hz - 1 MHz  | _   | 247  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 0, 3x Gain connection, 10 Hz - 1 MHz  | _   | 245  | _   | μVrms |

# 4.1.21.3 I2C Fast-mode Plus (Fm+)<sup>1</sup>

Table 4.30. I2C Fast-mode Plus (Fm+)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min  | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|------|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0    | _   | 1000 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 0.5  | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.26 | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 50   | _   | _    | ns   |

| SDA hold time                                    | t <sub>HD_DAT</sub> |                | 100  | _   | _    | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.26 | _   | _    | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.26 | _   | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.26 | _   | _    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 0.5  | _   | _    | μs   |

# Note:

- 1. For CLHR set to 0 or 1 in the I2Cn\_CTRL register.

- 2. For the minimum HFPERCLK frequency required in Fast-mode Plus, refer to the I2C chapter in the reference manual.

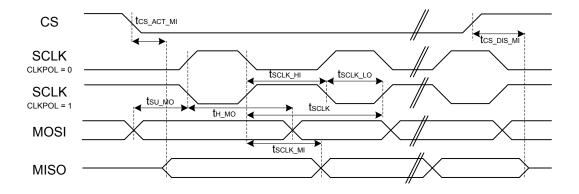

### **SPI Slave Timing**

Table 4.32. SPI Slave Timing

| Parameter                         | Symbol                 | Test Condition | Min                                           | Тур | Max                                 | Unit |

|-----------------------------------|------------------------|----------------|-----------------------------------------------|-----|-------------------------------------|------|

| SCLK period <sup>1 3 2</sup>      | t <sub>SCLK</sub>      |                | 6 *<br>t <sub>HFPERCLK</sub>                  | _   | _                                   | ns   |

| SCLK high time <sup>1 3 2</sup>   | t <sub>SCLK_HI</sub>   |                | 2.5 * t <sub>HFPERCLK</sub>                   | _   | _                                   | ns   |

| SCLK low time <sup>1 3 2</sup>    | t <sub>SCLK_LO</sub>   |                | 2.5 * the | _   | _                                   | ns   |

| CS active to MISO <sup>1 3</sup>  | t <sub>CS_ACT_MI</sub> |                | 20                                            | _   | 70                                  | ns   |

| CS disable to MISO <sup>1 3</sup> | tcs_dis_mi             |                | 15                                            |     | 150                                 | ns   |

| MOSI setup time <sup>1 3</sup>    | t <sub>SU_MO</sub>     |                | 4                                             | _   | _                                   | ns   |

| MOSI hold time <sup>1 3 2</sup>   | t <sub>H_MO</sub>      |                | 7                                             | _   | _                                   | ns   |

| SCLK to MISO <sup>1 3 2</sup>     | tsclk_MI               |                | 14 + 1.5 * t <sub>HFPERCLK</sub>              | _   | 40 + 2.5 *<br>t <sub>HFPERCLK</sub> | ns   |

### Note:

- 1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

- $2.\,t_{\mbox{\scriptsize HFPERCLK}}$  is one period of the selected HFPERCLK.

- 3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ ).

Figure 4.2. SPI Slave Timing Diagram

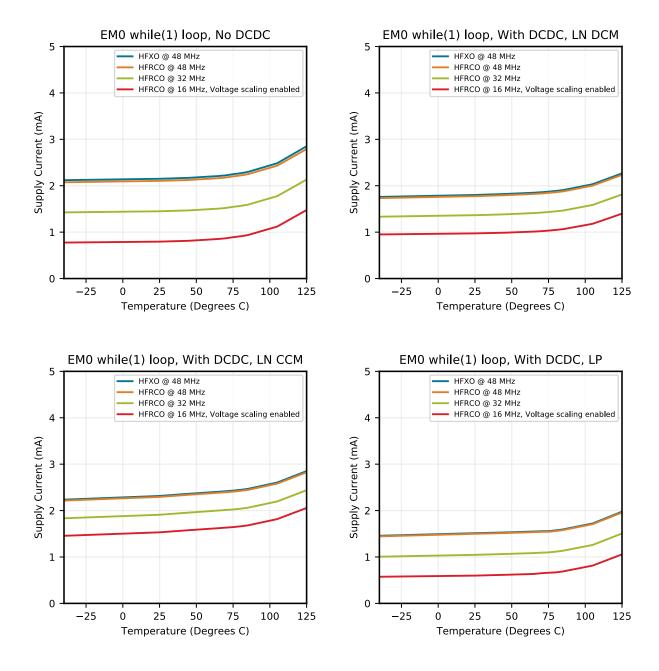

# 4.2 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

### 4.2.1 Supply Current

Figure 4.3. EM0 Active Mode Typical Supply Current vs. Temperature

| Pin Name | Pin(s)   | Description                                                                   | Pin Name | Pin(s) | Description                                                                                                                                                                                 |

|----------|----------|-------------------------------------------------------------------------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB4      | 10       | GPIO                                                                          | PB5      | 11     | GPIO                                                                                                                                                                                        |

| PB6      | 12       | GPIO                                                                          | PC0      | 13     | GPIO (5V)                                                                                                                                                                                   |

| PC1      | 14       | GPIO (5V)                                                                     | PC2      | 15     | GPIO (5V)                                                                                                                                                                                   |

| PC3      | 16       | GPIO (5V)                                                                     | PC4      | 17     | GPIO                                                                                                                                                                                        |

| PC5      | 18       | GPIO                                                                          | PB7      | 19     | GPIO                                                                                                                                                                                        |

| PB8      | 20       | GPIO                                                                          | PA8      | 21     | GPIO                                                                                                                                                                                        |

| PA9      | 22       | GPIO                                                                          | PA10     | 23     | GPIO                                                                                                                                                                                        |

| PA12     | 24       | GPIO                                                                          | PA13     | 25     | GPIO (5V)                                                                                                                                                                                   |

| PA14     | 26       | GPIO                                                                          | RESETn   | 27     | Reset input, active low. To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. |

| PB11     | 28       | GPIO                                                                          | PB12     | 29     | GPIO                                                                                                                                                                                        |

| AVDD     | 30<br>34 | Analog power supply.                                                          | PB13     | 31     | GPIO                                                                                                                                                                                        |

| PB14     | 32       | GPIO                                                                          | PD0      | 35     | GPIO (5V)                                                                                                                                                                                   |

| PD1      | 36       | GPIO                                                                          | PD2      | 37     | GPIO (5V)                                                                                                                                                                                   |

| PD3      | 38       | GPIO                                                                          | PD4      | 39     | GPIO                                                                                                                                                                                        |

| PD5      | 40       | GPIO                                                                          | PD6      | 41     | GPIO                                                                                                                                                                                        |

| PD7      | 42       | GPIO                                                                          | PD8      | 43     | GPIO                                                                                                                                                                                        |

| PC6      | 44       | GPIO                                                                          | PC7      | 45     | GPIO                                                                                                                                                                                        |

| VREGSW   | 47       | DCDC regulator switching node                                                 | VREGVDD  | 48     | Voltage regulator VDD input                                                                                                                                                                 |

| DVDD     | 49       | Digital power supply.                                                         | DECOUPLE | 50     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                    |

| PE4      | 52       | GPIO                                                                          | PE5      | 53     | GPIO                                                                                                                                                                                        |

| PE6      | 54       | GPIO                                                                          | PE7      | 55     | GPIO                                                                                                                                                                                        |

| PC8      | 56       | GPIO                                                                          | PC9      | 57     | GPIO                                                                                                                                                                                        |

| PC10     | 58       | GPIO (5V)                                                                     | PC11     | 59     | GPIO (5V)                                                                                                                                                                                   |

| PC12     | 60       | GPIO (5V)                                                                     | PC13     | 61     | GPIO (5V)                                                                                                                                                                                   |

| PC14     | 62       | GPIO (5V)                                                                     | PC15     | 63     | GPIO (5V)                                                                                                                                                                                   |

| PF0      | 64       | GPIO (5V)                                                                     | PF1      | 65     | GPIO (5V)                                                                                                                                                                                   |

| PF2      | 66       | GPIO                                                                          | PF3      | 67     | GPIO                                                                                                                                                                                        |

| PF4      | 68       | GPIO                                                                          | PF5      | 69     | GPIO                                                                                                                                                                                        |

| PE8      | 71       | GPIO                                                                          | PE9      | 72     | GPIO                                                                                                                                                                                        |

| PE10     | 73       | GPIO                                                                          | PE11     | 74     | GPIO                                                                                                                                                                                        |

| BODEN    | 75       | Brown-Out Detector Enable. This pin may be left disconnected or tied to AVDD. | PE12     | 76     | GPIO                                                                                                                                                                                        |

| PE13     | 77       | GPIO                                                                          | PE14     | 78     | GPIO                                                                                                                                                                                        |

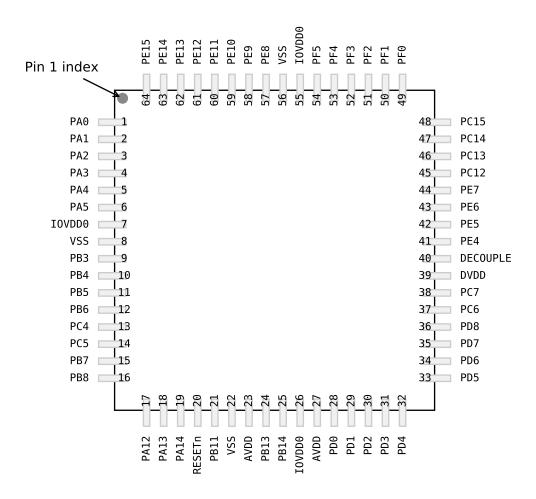

### 5.4 EFM32TG11B3xx in QFP64 Device Pinout

Figure 5.4. EFM32TG11B3xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

Table 5.4. EFM32TG11B3xx in QFP64 Device Pinout

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>26<br>55 | Digital IO power supply 0. | VSS      | 8<br>22<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

| Pin Name | Pin(s)   | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                 |

|----------|----------|-------------------------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB4      | 10       | GPIO                          | PB5      | 11     | GPIO                                                                                                                                                                                        |

| PB6      | 12       | GPIO                          | PC4      | 13     | GPIO                                                                                                                                                                                        |

| PC5      | 14       | GPIO                          | PB7      | 15     | GPIO                                                                                                                                                                                        |

| PB8      | 16       | GPIO                          | PA8      | 17     | GPIO                                                                                                                                                                                        |

| PA12     | 18       | GPIO                          | PA13     | 19     | GPIO (5V)                                                                                                                                                                                   |

| PA14     | 20       | GPIO                          | RESETn   | 21     | Reset input, active low. To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. |

| PB11     | 22       | GPIO                          | PB12     | 23     | GPIO                                                                                                                                                                                        |

| AVDD     | 24<br>28 | Analog power supply.          | PB13     | 25     | GPIO                                                                                                                                                                                        |

| PB14     | 26       | GPIO                          | PD0      | 29     | GPIO (5V)                                                                                                                                                                                   |

| PD1      | 30       | GPIO                          | PD3      | 31     | GPIO                                                                                                                                                                                        |

| PD4      | 32       | GPIO                          | PD5      | 33     | GPIO                                                                                                                                                                                        |

| PD6      | 34       | GPIO                          | PD7      | 35     | GPIO                                                                                                                                                                                        |

| PD8      | 36       | GPIO                          | PC7      | 37     | GPIO                                                                                                                                                                                        |

| VREGSW   | 39       | DCDC regulator switching node | VREGVDD  | 40     | Voltage regulator VDD input                                                                                                                                                                 |

| DVDD     | 41       | Digital power supply.         | DECOUPLE | 42     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                    |

| PE4      | 43       | GPIO                          | PE5      | 44     | GPIO                                                                                                                                                                                        |

| PE6      | 45       | GPIO                          | PE7      | 46     | GPIO                                                                                                                                                                                        |

| PC12     | 47       | GPIO (5V)                     | PC13     | 48     | GPIO (5V)                                                                                                                                                                                   |

| PF0      | 49       | GPIO (5V)                     | PF1      | 50     | GPIO (5V)                                                                                                                                                                                   |

| PF2      | 51       | GPIO                          | PF3      | 52     | GPIO                                                                                                                                                                                        |

| PF4      | 53       | GPIO                          | PF5      | 54     | GPIO                                                                                                                                                                                        |

| PE8      | 56       | GPIO                          | PE9      | 57     | GPIO                                                                                                                                                                                        |

| PE10     | 58       | GPIO                          | PE11     | 59     | GPIO                                                                                                                                                                                        |

| PE12     | 60       | GPIO                          | PE13     | 61     | GPIO                                                                                                                                                                                        |

| PE14     | 62       | GPIO                          | PE15     | 63     | GPIO                                                                                                                                                                                        |

| PA15     | 64       | GPIO                          |          |        |                                                                                                                                                                                             |

# Note:

1. GPIO with 5V tolerance are indicated by (5V).

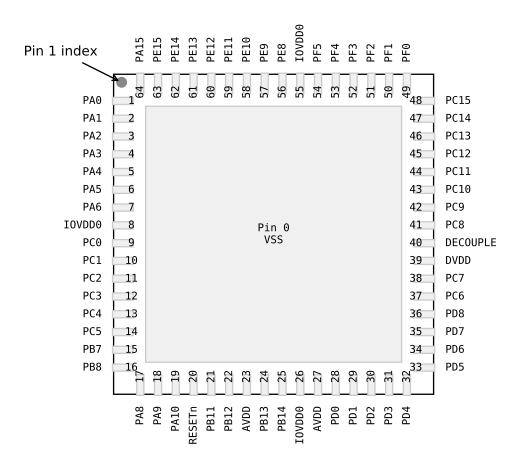

### 5.8 EFM32TG11B1xx in QFN64 Device Pinout

Figure 5.8. EFM32TG11B1xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

Table 5.8. EFM32TG11B1xx in QFN64 Device Pinout

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>26<br>55 | Digital IO power supply 0. | PC0      | 9      | GPIO (5V)   |

| PC1      | 10            | GPIO (5V)                  | PC2      | 11     | GPIO (5V)   |

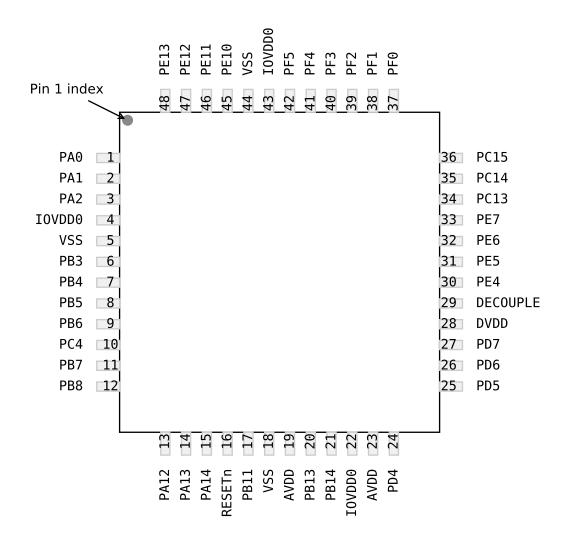

#### 5.10 EFM32TG11B3xx in QFP48 Device Pinout

Figure 5.10. EFM32TG11B3xx in QFP48 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

Table 5.10. EFM32TG11B3xx in QFP48 Device Pinout

| Pin Name | Pin(s)        | Description | Pin Name | Pin(s)        | Description                |

|----------|---------------|-------------|----------|---------------|----------------------------|

| PA0      | 1             | GPIO        | PA1      | 2             | GPIO                       |

| PA2      | 3             | GPIO        | IOVDD0   | 4<br>22<br>43 | Digital IO power supply 0. |

| VSS      | 5<br>18<br>44 | Ground      | PB3      | 6             | GPIO                       |

| PB4      | 7             | GPIO        | PB5      | 8             | GPIO                       |

| PB6      | 9             | GPIO        | PC4      | 10            | GPIO                       |

| Pin Name | Pin(s) | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                 |

|----------|--------|-------------------------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA14     | 8      | GPIO                          | RESETn   | 9      | Reset input, active low. To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. |

| PB11     | 10     | GPIO                          | AVDD     | 11     | Analog power supply.                                                                                                                                                                        |

| PB13     | 12     | GPIO                          | PB14     | 13     | GPIO                                                                                                                                                                                        |

| PD4      | 15     | GPIO                          | PD5      | 16     | GPIO                                                                                                                                                                                        |

| PD6      | 17     | GPIO                          | PD7      | 18     | GPIO                                                                                                                                                                                        |

| VREGSW   | 20     | DCDC regulator switching node | VREGVDD  | 21     | Voltage regulator VDD input                                                                                                                                                                 |

| DVDD     | 22     | Digital power supply.         | DECOUPLE | 23     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                    |

| PE4      | 24     | GPIO                          | PE5      | 25     | GPIO                                                                                                                                                                                        |

| PC15     | 26     | GPIO (5V)                     | PF0      | 27     | GPIO (5V)                                                                                                                                                                                   |

| PF1      | 28     | GPIO (5V)                     | PF2      | 29     | GPIO                                                                                                                                                                                        |

| PE11     | 31     | GPIO                          | PE12     | 32     | GPIO                                                                                                                                                                                        |

# Note:

1. GPIO with 5V tolerance are indicated by (5V).

| GPIO Name | Pin Alternate Functionality / Description                  |                                                                        |                                                                           |                                                      |

|-----------|------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|

|           | Analog                                                     | Timers                                                                 | Communication                                                             | Other                                                |

| PD5       | BUSADC0Y BUSADC0X<br>OPA2_OUT                              | WTIM0_CDTI1 #4<br>WTIM1_CC3 #1                                         | US1_RTS #1 U0_CTS #5<br>LEU0_RX #0 I2C1_SCL<br>#3                         |                                                      |

| PD6       | BUSADC0Y BUSADC0X<br>ADC0_EXTP<br>VDAC0_EXT OPA1_P         | TIM1_CC0 #4 WTIM0_CDTI2 #4 WTIM1_CC0 #2 LE- TIM0_OUT0 #0 PCNT0_S0IN #3 | US0_RTS #5 US1_RX #2<br>US2_CTS #5 US3_CTS<br>#2 U0_RTS #5 I2C0_SDA<br>#1 | CMU_CLK2 #2 LES_AL-<br>TEX0 PRS_CH5 #2<br>ACMP0_O #2 |

| PD7       | BUSADC0Y BUSADC0X<br>ADC0_EXTN OPA1_N                      | TIM1_CC1 #4 WTIM1_CC1 #2 LE- TIM0_OUT1 #0 PCNT0_S1IN #3                | US1_TX #2 US3_CLK #1<br>U0_TX #6 I2C0_SCL #1                              | CMU_CLK0 #2 LES_AL-<br>TEX1 ACMP1_O #2               |

| PD8       | BU_VIN                                                     | WTIM1_CC2 #2                                                           | US2_RTS #5                                                                | CMU_CLK1 #1                                          |

| PC6       | BUSACMP0Y BU-<br>SACMP0X OPA3_P<br>LCD_SEG32               | WTIM1_CC3 #2                                                           | US0_RTS #2 US1_CTS<br>#3 I2C0_SDA #2                                      | LES_CH6                                              |

| PC7       | BUSACMPOY BU-<br>SACMPOX OPA3_N<br>LCD_SEG33               | WTIM1_CC0 #3                                                           | US0_CTS #2 US1_RTS<br>#3 I2C0_SCL #2                                      | LES_CH7                                              |

| PE4       | BUSDY BUSCX<br>LCD_COM0                                    | WTIM0_CC0 #0<br>WTIM1_CC1 #4                                           | US0_CS #1 US1_CS #5<br>US3_CS #1 U0_RX #6<br>I2C0_SDA #7                  |                                                      |

| PE5       | BUSCY BUSDX<br>LCD_COM1                                    | WTIM0_CC1 #0<br>WTIM1_CC2 #4                                           | US0_CLK #1 US1_CLK<br>#6 US3_CTS #1<br>I2C0_SCL #7                        |                                                      |

| PE6       | BUSDY BUSCX<br>LCD_COM2                                    | WTIM0_CC2 #0<br>WTIM1_CC3 #4                                           | US0_RX #1 US3_TX #1                                                       | PRS_CH6 #2                                           |

| PE7       | BUSCY BUSDX<br>LCD_COM3                                    | WTIM1_CC0 #5                                                           | US0_TX #1 US3_RX #1                                                       | PRS_CH7 #2                                           |

| PC8       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG34                         |                                                                        | US0_CS #2                                                                 | LES_CH8 PRS_CH4 #0                                   |

| PC9       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG35                         |                                                                        | US0_CLK #2                                                                | LES_CH9 PRS_CH5 #0<br>GPIO_EM4WU2                    |

| PC10      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                        | US0_RX #2                                                                 | LES_CH10                                             |

| PC11      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                        | US0_TX #2 I2C1_SDA #4                                                     | LES_CH11                                             |

| PC12      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0 BU-<br>SACMP1Y BUSACMP1X | TIM1_CC3 #0                                                            | US0_RTS #3 US1_CTS<br>#4 US2_CTS #4 U0_RTS<br>#3                          | CMU_CLK0 #1<br>LES_CH12                              |

| PC13      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #1 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI0 #1 TIM1_CC0 #0 TIM1_CC2 #4 PCNT0_S0IN #0                    | US0_CTS #3 US1_RTS<br>#4 US2_RTS #4 U0_CTS<br>#3                          | LES_CH13                                             |

| PC14      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI1 #1 TIM1_CC1 #0 TIM1_CC3 #4 LETIM0_OUT0 #5 PCNT0_S1IN #0     | US0_CS #3 US1_CS #3<br>US2_RTS #3 US3_CS #2<br>U0_TX #3 LEU0_TX #5        | LES_CH14 PRS_CH0 #2                                  |

| Alternate               | LOCA    | ATION |                                                                  |

|-------------------------|---------|-------|------------------------------------------------------------------|

| Functionality           | 0 - 3   | 4 - 7 | Description                                                      |

| LCD_SEG9                | 0: PE13 |       | LCD segment line 9.                                              |

| LCD_SEG10               | 0: PE14 |       | LCD segment line 10.                                             |

| LCD_SEG11               | 0: PE15 |       | LCD segment line 11.                                             |

| LCD_SEG12               | 0: PA15 |       | LCD segment line 12.                                             |

| LCD_SEG13               | 0: PA0  |       | LCD segment line 13.                                             |

| LCD_SEG14               | 0: PA1  |       | LCD segment line 14.                                             |

| LCD_SEG15               | 0: PA2  |       | LCD segment line 15.                                             |

| LCD_SEG16               | 0: PA3  |       | LCD segment line 16.                                             |

| LCD_SEG17               | 0: PA4  |       | LCD segment line 17.                                             |

| LCD_SEG18               | 0: PA5  |       | LCD segment line 18.                                             |

| LCD_SEG19               | 0: PA6  |       | LCD segment line 19.                                             |

| LCD_SEG20 /<br>LCD_COM4 | 0: PB3  |       | LCD segment line 20. This pin may also be used as LCD COM line 4 |

| LCD_SEG21 /<br>LCD_COM5 | 0: PB4  |       | LCD segment line 21. This pin may also be used as LCD COM line 5 |

| Alternate     | Iternate LOCATION                      |                   |                                                                                                                                                     |  |  |

|---------------|----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Functionality | 0 - 3                                  | 4 - 7             | Description                                                                                                                                         |  |  |

| US2_CLK       | 0: PC4<br>1: PB5<br>2: PA9<br>3: PA15  | 5: PF2            | USART2 clock input / output.                                                                                                                        |  |  |

| US2_CS        | 0: PC5<br>1: PB6<br>2: PA10<br>3: PB11 | 5: PF5            | USART2 chip select input / output.                                                                                                                  |  |  |

| US2_CTS       | 0: PC1<br>1: PB12                      | 4: PC12<br>5: PD6 | USART2 Clear To Send hardware flow control input.                                                                                                   |  |  |

| US2_RTS       | 0: PC0<br>2: PA12<br>3: PC14           | 4: PC13<br>5: PD8 | USART2 Request To Send hardware flow control output.                                                                                                |  |  |

| US2_RX        | 0: PC3<br>1: PB4<br>2: PA8<br>3: PA14  | 5: PF1            | USART2 Asynchronous Receive.  USART2 Synchronous mode Master Input / Slave Output (MISO).                                                           |  |  |

| US2_TX        | 0: PC2<br>1: PB3                       | 5: PF0            | USART2 Asynchronous Transmit. Also used as receive input in half duplex communication.                                                              |  |  |

|               | 3: PA13                                |                   | USART2 Synchronous mode Master Output / Slave Input (MOSI).                                                                                         |  |  |

| US3_CLK       | 0: PA2<br>1: PD7<br>2: PD4             |                   | USART3 clock input / output.                                                                                                                        |  |  |

| US3_CS        | 0: PA3<br>1: PE4<br>2: PC14<br>3: PC0  |                   | USART3 chip select input / output.                                                                                                                  |  |  |

| US3_CTS       | 0: PA4<br>1: PE5<br>2: PD6             |                   | USART3 Clear To Send hardware flow control input.                                                                                                   |  |  |

| US3_RTS       | 0: PA5<br>1: PC1<br>2: PA14<br>3: PC15 |                   | USART3 Request To Send hardware flow control output.                                                                                                |  |  |

| US3_RX        | 0: PA1<br>1: PE7<br>2: PB7             |                   | USART3 Asynchronous Receive. USART3 Synchronous mode Master Input / Slave Output (MISO).                                                            |  |  |

| US3_TX        | 0: PA0<br>1: PE6<br>2: PB3             |                   | USART3 Asynchronous Transmit. Also used as receive input in half duplex communication.  USART3 Synchronous mode Master Output / Slave Input (MOSI). |  |  |

| VDAC0_EXT     | 0: PD6                                 |                   | Digital to analog converter VDAC0 external reference input pin.                                                                                     |  |  |

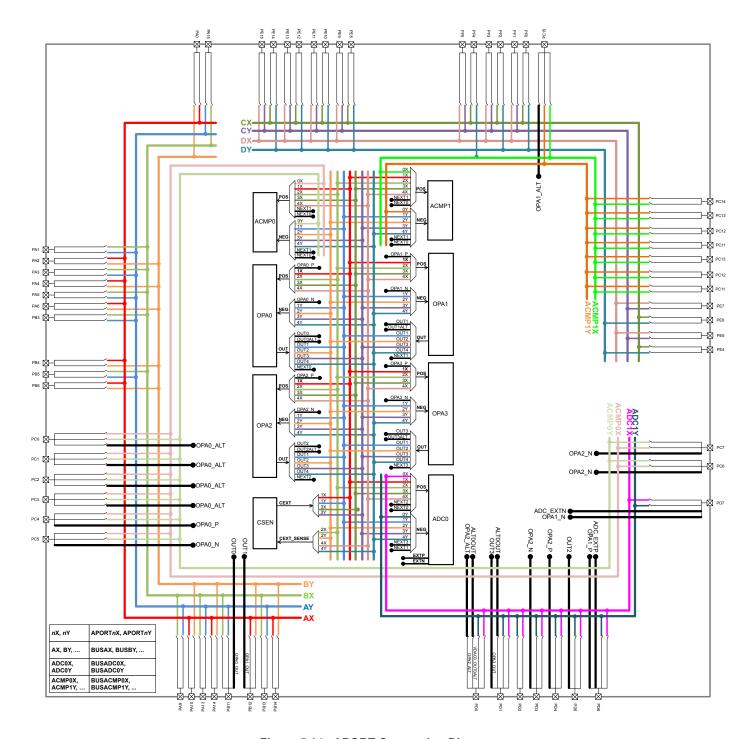

### 5.16 Analog Port (APORT) Client Maps

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. Figure 5.14 APORT Connection Diagram on page 119 shows the APORT routing for this device family (note that available features may vary by part number). A complete description of APORT functionality can be found in the Reference Manual.

Figure 5.14. APORT Connection Diagram

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin

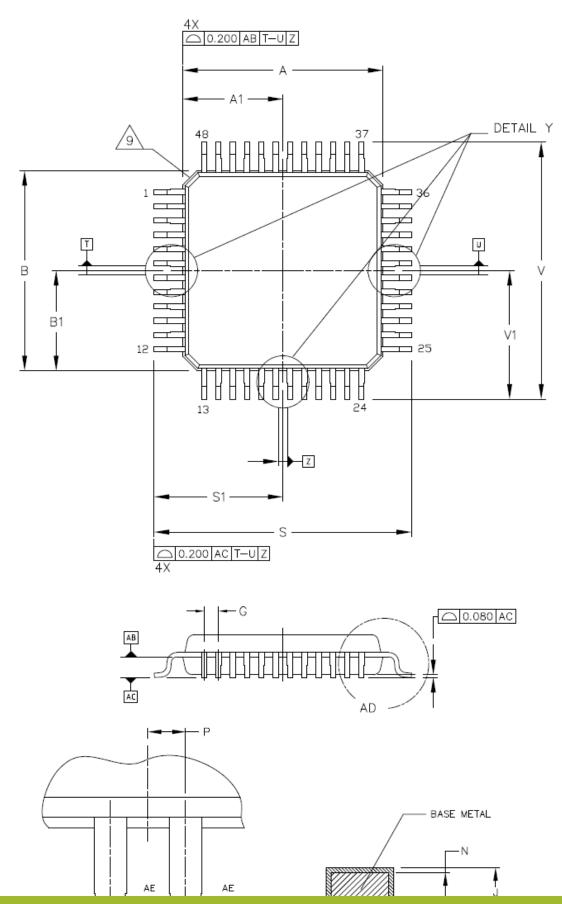

# 10. TQFP48 Package Specifications

# 10.1 TQFP48 Package Dimensions