Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                |                                                                           |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                               |

| Data Converters            | A/D 12bit SAR; D/A 12bit                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-WFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-QFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg11b540f64im32-ar |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.1.6.2 Current Consumption 3.3 V using DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = IOVDD = 3.3 V, DVDD = 1.8 V DC-DC output. T = 25 °C. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

| Parameter                                                    | Symbol      | Test Condition                                        | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------|-------------|-------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>mode with all peripherals dis- | IACTIVE_DCM | 48 MHz crystal, CPU running while loop from flash     | _   | 38   | -   | µA/MHz |

| abled, DCDC in Low Noise<br>DCM mode <sup>2</sup>            |             | 48 MHz HFRCO, CPU running while loop from flash       | _   | 37   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>Prime from flash         | _   | 45   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash | _   | 53   | _   | µA/MHz |

|                                                              |             | 32 MHz HFRCO, CPU running while loop from flash       | _   | 43   | _   | µA/MHz |

|                                                              |             | 26 MHz HFRCO, CPU running while loop from flash       |     | 47   | _   | µA/MHz |

|                                                              |             | 16 MHz HFRCO, CPU running while loop from flash       |     | 61   | _   | µA/MHz |

|                                                              |             | 1 MHz HFRCO, CPU running while loop from flash        |     | 587  | _   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis- | IACTIVE_CCM | 48 MHz crystal, CPU running while loop from flash     | _   | 49   | _   | µA/MHz |

| abled, DCDC in Low Noise<br>CCM mode <sup>1</sup>            |             | 48 MHz HFRCO, CPU running while loop from flash       |     | 48   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>Prime from flash         | _   | 55   | _   | µA/MHz |

|                                                              |             | 48 MHz HFRCO, CPU running<br>CoreMark loop from flash |     | 63   | _   | µA/MHz |

|                                                              |             | 32 MHz HFRCO, CPU running while loop from flash       |     | 60   | _   | µA/MHz |

|                                                              |             | 26 MHz HFRCO, CPU running while loop from flash       |     | 68   | _   | µA/MHz |

|                                                              |             | 16 MHz HFRCO, CPU running while loop from flash       |     | 96   | _   | µA/MHz |

|                                                              |             | 1 MHz HFRCO, CPU running while loop from flash        |     | 1157 | _   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis- | IACTIVE_LPM | 32 MHz HFRCO, CPU running while loop from flash       | _   | 32   | _   | µA/MHz |

| abled, DCDC in LP mode <sup>3</sup>                          |             | 26 MHz HFRCO, CPU running while loop from flash       |     | 33   | _   | µA/MHz |

|                                                              |             | 16 MHz HFRCO, CPU running while loop from flash       |     | 36   | _   | µA/MHz |

|                                                              |             | 1 MHz HFRCO, CPU running while loop from flash        | _   | 156  | _   | µA/MHz |

# 4.1.9.3 Low-Frequency RC Oscillator (LFRCO)

| Symbol             | Test Condition                     | Min                                                                                                                                                                                                                                                                           | Тур                                                                                                                                                                                                                                                                                        | Мах                                                                                                                                                                                                                                                                                                                                                                     | Unit                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>LFRCO</sub> | ENVREF <sup>2</sup> = 1            | TBD                                                                                                                                                                                                                                                                           | 32.768                                                                                                                                                                                                                                                                                     | TBD                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | ENVREF <sup>2</sup> = 1, T > 85 °C | TBD                                                                                                                                                                                                                                                                           | 32.768                                                                                                                                                                                                                                                                                     | TBD                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | ENVREF <sup>2</sup> = 0            | TBD                                                                                                                                                                                                                                                                           | 32.768                                                                                                                                                                                                                                                                                     | TBD                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                                                                                                                                                                                                                                                                                                  |

| t <sub>LFRCO</sub> |                                    | _                                                                                                                                                                                                                                                                             | 500                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                         | μs                                                                                                                                                                                                                                                                                                                                                                                   |

| I <sub>LFRCO</sub> | ENVREF = 1 in<br>CMU_LFRCOCTRL     | _                                                                                                                                                                                                                                                                             | 370                                                                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                       | nA                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | ENVREF = 0 in<br>CMU_LFRCOCTRL     | _                                                                                                                                                                                                                                                                             | 520                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                         | nA                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | f <sub>LFRCO</sub>                 | $\begin{tabular}{ c c c c } \hline f_{LFRCO} & ENVREF^2 = 1 \\ \hline ENVREF^2 = 1, \ T > 85 \ ^{\circ}C \\ \hline ENVREF^2 = 0 \\ \hline t_{LFRCO} & \hline \\ \hline l_{LFRCO} & ENVREF = 1 \ in \\ \hline CMU_LFRCOCTRL \\ \hline ENVREF = 0 \ in \\ \hline \end{tabular}$ | $\begin{tabular}{ c c c c } \hline f_{LFRCO} & ENVREF^2 = 1 & TBD \\ \hline ENVREF^2 = 1, T > 85 \ ^{\circ}C & TBD \\ \hline ENVREF^2 = 0 & TBD \\ \hline t_{LFRCO} & & \\ \hline l_{LFRCO} & ENVREF = 1 \ in \\ \hline CMU_LFRCOCTRL & \\ \hline ENVREF = 0 \ in & \\ \hline \end{array}$ | $ \begin{array}{c c} f_{LFRCO} & ENVREF^2 = 1 & TBD & 32.768 \\ \hline ENVREF^2 = 1, T > 85 \ ^{\circ}C & TBD & 32.768 \\ \hline ENVREF^2 = 0 & TBD & 32.768 \\ \hline ENVREF^2 = 0 & TBD & 32.768 \\ \hline t_{LFRCO} & \hline & & 500 \\ \hline l_{LFRCO} & ENVREF = 1 \ in \\ \hline CMU_LFRCOCTRL & & 370 \\ \hline ENVREF = 0 \ in & & 520 \\ \hline \end{array} $ | $ \begin{array}{c c} f_{LFRCO} & ENVREF^2 = 1 & TBD & 32.768 & TBD \\ \hline ENVREF^2 = 1, T > 85 \ ^{\circ}C & TBD & 32.768 & TBD \\ \hline ENVREF^2 = 0 & TBD & 32.768 & TBD \\ \hline ENVREF^2 = 0 & TBD & 32.768 & TBD \\ \hline t_{LFRCO} & & & 500 & \\ \hline t_{LFRCO} & ENVREF = 1 \ ^{\circ}n & & 370 & \\ \hline ENVREF = 0 \ ^{\circ}n & & 520 & \\ \hline \end{array} $ |

# Table 4.13. Low-Frequency RC Oscillator (LFRCO)

1. Block is supplied by AVDD if ANASW = 0, or DVDD if ANASW=1 in EMU\_PWRCTRL register.

2. In CMU\_LFRCOCTRL register.

| Parameter                              | Symbol                    | Test Condition                                                                      | Min | Тур | Max | Unit  |

|----------------------------------------|---------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Frequency accuracy                     | f <sub>HFRCO_ACC</sub>    | At production calibrated frequen-<br>cies, across supply voltage and<br>temperature | TBD | _   | TBD | %     |

| Start-up time                          | t <sub>HFRCO</sub>        | f <sub>HFRCO</sub> ≥ 19 MHz                                                         | _   | 300 | —   | ns    |

|                                        |                           | 4 < f <sub>HFRCO</sub> < 19 MHz                                                     | _   | 1   | —   | μs    |

|                                        |                           | f <sub>HFRCO</sub> ≤ 4 MHz                                                          | _   | 2.5 | _   | μs    |

| Current consumption on all             | I <sub>HFRCO</sub>        | f <sub>HFRCO</sub> = 48 MHz                                                         |     | 258 | TBD | μA    |

| supplies                               |                           | f <sub>HFRCO</sub> = 38 MHz                                                         | _   | 218 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 32 MHz                                                         |     | 182 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 26 MHz                                                         |     | 156 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 19 MHz                                                         |     | 130 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 16 MHz                                                         |     | 112 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 13 MHz                                                         |     | 101 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 7 MHz                                                          |     | 80  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 4 MHz                                                          |     | 29  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 2 MHz                                                          |     | 26  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 1 MHz                                                          |     | 24  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 40 MHz, DPLL enabled                                           |     | 393 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 32 MHz, DPLL enabled                                           |     | 313 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 16 MHz, DPLL enabled                                           |     | 180 | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 4 MHz, DPLL enabled                                            |     | 46  | TBD | μA    |

|                                        |                           | f <sub>HFRCO</sub> = 1 MHz, DPLL enabled                                            |     | 33  | TBD | μA    |

| Coarse trim step size (% of period)    | SS <sub>HFRCO_COARS</sub> |                                                                                     |     | 0.8 | _   | %     |

| Fine trim step size (% of pe-<br>riod) | SS <sub>HFRCO_FINE</sub>  |                                                                                     |     | 0.1 | -   | %     |

| Period jitter                          | PJ <sub>HFRCO</sub>       |                                                                                     |     | 0.2 | _   | % RMS |

# Table 4.14. High-Frequency RC Oscillator (HFRCO)

| Parameter                                               | Symbol                   | Test Condition                                                                                         | Min | Тур  | Мах | Unit |

|---------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal 1.25V reference                                                       | _   | 60.4 | _   | dB   |

| Noise band limited to 250<br>kHz                        |                          | 500 ksps, single-ended, internal<br>2.5V reference                                                     | —   | 61.6 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 64.0 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 63.3 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 64.4 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 65.8 |     | dB   |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference                                                       | _   | 65.3 |     | dB   |

| Noise band limited to 22 kHz                            |                          | 500 ksps, single-ended, internal<br>2.5V reference                                                     | _   | 66.7 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 68.5 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 67.8 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 69.0 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 70.0 |     | dB   |

| Total harmonic distortion                               | THD                      |                                                                                                        |     | 70.2 |     | dB   |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                                                                        | TBD | _    | TBD | LSB  |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                                                                        | TBD | _    | TBD | LSB  |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T = 25 °C                                                                                              | TBD | _    | TBD | mV   |

|                                                         |                          | Across operating temperature range                                                                     | TBD | _    | TBD | mV   |

| Gain error <sup>5</sup>                                 | V <sub>GAIN</sub>        | T = 25 °C, Low-noise internal ref-<br>erence (REFSEL = 1V25LN or<br>2V5LN)                             | TBD | _    | TBD | %    |

|                                                         |                          | Across operating temperature<br>range, Low-noise internal refer-<br>ence (REFSEL = 1V25LN or<br>2V5LN) | TBD | _    | TBD | %    |

| External load capactiance,<br>OUTSCALE=0                | C <sub>LOAD</sub>        |                                                                                                        | —   | _    | 75  | pF   |

| Parameter                   | Symbol                                         | Test Condition                                                                   | Min               | Тур             | Мах             | Unit      |

|-----------------------------|------------------------------------------------|----------------------------------------------------------------------------------|-------------------|-----------------|-----------------|-----------|

| Note:                       | l                                              |                                                                                  |                   |                 |                 |           |

| 1. Supply current the load. | specifications are for VD                      | AC circuitry operating with static outpo                                         | ut only and do n  | not include cur | rent required   | to drive  |

|                             | ode, the output is define<br>ngle-ended range. | d as the difference between two single                                           | e-ended outputs   | s. Absolute vol | ltage on each   | output is |

| 3. Entire range is          | monotonic and has no m                         | nissing codes.                                                                   |                   |                 |                 |           |

|                             | PERCLK is dependent<br>DAC module is enabled   | on HFPERCLK frequency. This currer<br>in the CMU.                                | nt contributes to | the total supp  | bly current use | ed when   |

|                             |                                                | pe from 10% to 90% of full scale. Offs<br>at 10% of full scale with the measured |                   | by comparing    | actual VDAC     | output at |

|                             |                                                | $\Delta V_{OUT}$ ), VDAC output at 90% of full set                               | aala              |                 |                 |           |

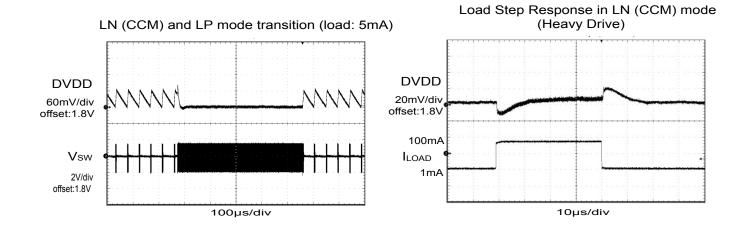

Figure 4.9. DC-DC Converter Transition Waveforms

| Pin Name | Pin(s) | Description                                                                                              | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|----------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                                                                                                     | PC5      | 14       | GPIO                                                                                                                                                                                                        |

| PB7      | 15     | GPIO                                                                                                     | PB8      | 16       | GPIO                                                                                                                                                                                                        |

| PA8      | 17     | GPIO                                                                                                     | PA9      | 18       | GPIO                                                                                                                                                                                                        |

| PA10     | 19     | GPIO                                                                                                     | RESETn   | 20       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21     | GPIO                                                                                                     | AVDD     | 23<br>27 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 24     | GPIO                                                                                                     | PB14     | 25       | GPIO                                                                                                                                                                                                        |

| PD0      | 28     | GPIO (5V)                                                                                                | PD1      | 29       | GPIO                                                                                                                                                                                                        |

| PD2      | 30     | GPIO (5V)                                                                                                | PD3      | 31       | GPIO                                                                                                                                                                                                        |

| PD4      | 32     | GPIO                                                                                                     | PD5      | 33       | GPIO                                                                                                                                                                                                        |

| PD6      | 34     | GPIO                                                                                                     | PD7      | 35       | GPIO                                                                                                                                                                                                        |

| PD8      | 36     | GPIO                                                                                                     | PC6      | 37       | GPIO                                                                                                                                                                                                        |

| PC7      | 38     | GPIO                                                                                                     | DVDD     | 39       | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PC8      | 41       | GPIO                                                                                                                                                                                                        |

| PC9      | 42     | GPIO                                                                                                     | PC10     | 43       | GPIO (5V)                                                                                                                                                                                                   |

| PC11     | 44     | GPIO (5V)                                                                                                | PC12     | 45       | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 46     | GPIO (5V)                                                                                                | PC14     | 47       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 48     | GPIO (5V)                                                                                                | PF0      | 49       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50     | GPIO (5V)                                                                                                | PF2      | 51       | GPIO                                                                                                                                                                                                        |

| PF3      | 52     | GPIO                                                                                                     | PF4      | 53       | GPIO                                                                                                                                                                                                        |

| PF5      | 54     | GPIO                                                                                                     | PE8      | 57       | GPIO                                                                                                                                                                                                        |

| PE9      | 58     | GPIO                                                                                                     | PE10     | 59       | GPIO                                                                                                                                                                                                        |

| PE11     | 60     | GPIO                                                                                                     | PE12     | 61       | GPIO                                                                                                                                                                                                        |

| PE13     | 62     | GPIO                                                                                                     | PE14     | 63       | GPIO                                                                                                                                                                                                        |

| PE15     | 64     | GPIO                                                                                                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

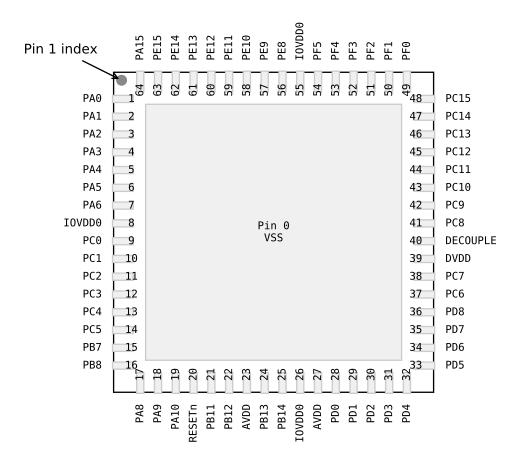

### Figure 5.8. EFM32TG11B1xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.14 GPIO Functionality Table or 5.15 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VREGVSS  | 0             | Voltage regulator VSS      | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>26<br>55 | Digital IO power supply 0. | PC0      | 9      | GPIO (5V)   |

| PC1      | 10            | GPIO (5V)                  | PC2      | 11     | GPIO (5V)   |

| Pin Name | Pin(s) | Description           | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|-----------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB8      | 8      | GPIO                  | RESETn   | 9        | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 10     | GPIO                  | AVDD     | 11<br>15 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 12     | GPIO                  | PB14     | 13       | GPIO                                                                                                                                                                                                        |

| PD4      | 16     | GPIO                  | PD5      | 17       | GPIO                                                                                                                                                                                                        |

| PD6      | 18     | GPIO                  | PD7      | 19       | GPIO                                                                                                                                                                                                        |

| DVDD     | 20     | Digital power supply. | DECOUPLE | 21       | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PC13     | 22     | GPIO (5V)             | PC14     | 23       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 24     | GPIO (5V)             | PF0      | 25       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 26     | GPIO (5V)             | PF2      | 27       | GPIO                                                                                                                                                                                                        |

| PE10     | 29     | GPIO                  | PE11     | 30       | GPIO                                                                                                                                                                                                        |

| PE12     | 31     | GPIO                  | PE13     | 32       | GPIO                                                                                                                                                                                                        |

| Note:    |        | ,                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| GPIO Name |                                                            | Pin Alternate Functi                                                               | onality / Description                                                     |                                                      |

|-----------|------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|

|           | Analog                                                     | Timers                                                                             | Communication                                                             | Other                                                |

| PD5       | BUSADC0Y BUSADC0X<br>OPA2_OUT                              | WTIM0_CDTI1 #4<br>WTIM1_CC3 #1                                                     | US1_RTS #1 U0_CTS #5<br>LEU0_RX #0 I2C1_SCL<br>#3                         |                                                      |

| PD6       | BUSADC0Y BUSADC0X<br>ADC0_EXTP<br>VDAC0_EXT OPA1_P         | TIM1_CC0 #4<br>WTIM0_CDTI2 #4<br>WTIM1_CC0 #2 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US0_RTS #5 US1_RX #2<br>US2_CTS #5 US3_CTS<br>#2 U0_RTS #5 I2C0_SDA<br>#1 | CMU_CLK2 #2 LES_AL-<br>TEX0 PRS_CH5 #2<br>ACMP0_O #2 |

| PD7       | BUSADC0Y BUSADC0X<br>ADC0_EXTN OPA1_N                      | TIM1_CC1 #4<br>WTIM1_CC1 #2 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3                   | US1_TX #2 US3_CLK #1<br>U0_TX #6 I2C0_SCL #1                              | CMU_CLK0 #2 LES_AL-<br>TEX1 ACMP1_O #2               |

| PD8       | BU_VIN                                                     | WTIM1_CC2 #2                                                                       | US2_RTS #5                                                                | CMU_CLK1 #1                                          |

| PC6       | BUSACMP0Y BU-<br>SACMP0X OPA3_P<br>LCD_SEG32               | WTIM1_CC3 #2                                                                       | US0_RTS #2 US1_CTS<br>#3 I2C0_SDA #2                                      | LES_CH6                                              |

| PC7       | BUSACMP0Y BU-<br>SACMP0X OPA3_N<br>LCD_SEG33               | WTIM1_CC0 #3                                                                       | US0_CTS #2 US1_RTS<br>#3 I2C0_SCL #2                                      | LES_CH7                                              |

| PE4       | BUSDY BUSCX<br>LCD_COM0                                    | WTIM0_CC0 #0<br>WTIM1_CC1 #4                                                       | US0_CS #1 US1_CS #5<br>US3_CS #1 U0_RX #6<br>I2C0_SDA #7                  |                                                      |

| PE5       | BUSCY BUSDX<br>LCD_COM1                                    | WTIM0_CC1 #0<br>WTIM1_CC2 #4                                                       | US0_CLK #1 US1_CLK<br>#6 US3_CTS #1<br>I2C0_SCL #7                        |                                                      |

| PE6       | BUSDY BUSCX<br>LCD_COM2                                    | WTIM0_CC2 #0<br>WTIM1_CC3 #4                                                       | US0_RX #1 US3_TX #1                                                       | PRS_CH6 #2                                           |

| PE7       | BUSCY BUSDX<br>LCD_COM3                                    | WTIM1_CC0 #5                                                                       | US0_TX #1 US3_RX #1                                                       | PRS_CH7 #2                                           |

| PC8       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG34                         |                                                                                    | US0_CS #2                                                                 | LES_CH8 PRS_CH4 #0                                   |

| PC9       | BUSACMP1Y BU-<br>SACMP1X LCD_SEG35                         |                                                                                    | US0_CLK #2                                                                | LES_CH9 PRS_CH5 #0<br>GPIO_EM4WU2                    |

| PC10      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_RX #2                                                                 | LES_CH10                                             |

| PC11      | BUSACMP1Y BU-<br>SACMP1X                                   |                                                                                    | US0_TX #2 I2C1_SDA #4                                                     | LES_CH11                                             |

| PC12      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #0 BU-<br>SACMP1Y BUSACMP1X | TIM1_CC3 #0                                                                        | US0_RTS #3 US1_CTS<br>#4 US2_CTS #4 U0_RTS<br>#3                          | CMU_CLK0 #1<br>LES_CH12                              |

| PC13      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #1 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI0 #1<br>TIM1_CC0 #0 TIM1_CC2<br>#4 PCNT0_S0IN #0                          | US0_CTS #3 US1_RTS<br>#4 US2_RTS #4 U0_CTS<br>#3                          | LES_CH13                                             |

| PC14      | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2 BU-<br>SACMP1Y BUSACMP1X | TIM0_CDTI1 #1<br>TIM1_CC1 #0 TIM1_CC3<br>#4 LETIM0_OUT0 #5<br>PCNT0_S1IN #0        | US0_CS #3 US1_CS #3<br>US2_RTS #3 US3_CS #2<br>U0_TX #3 LEU0_TX #5        | LES_CH14 PRS_CH0 #2                                  |

#### 5.15 Alternate Functionality Overview

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings and the associated GPIO pin. Refer to 5.14 GPIO Functionality Table for a list of functions available on each GPIO pin.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate LOCATION |                   | ATION   |                                                                          |  |  |  |  |  |

|--------------------|-------------------|---------|--------------------------------------------------------------------------|--|--|--|--|--|

| Functionality      | 0 - 3             | 4 - 7   | Description                                                              |  |  |  |  |  |

|                    | 0: PE13           | 4: PA6  |                                                                          |  |  |  |  |  |

| ACMP0_O            | 2: PD6<br>3: PB11 | 7: PB3  | Analog comparator ACMP0, digital output.                                 |  |  |  |  |  |

|                    | 0: PF2            | 4: PA14 |                                                                          |  |  |  |  |  |

| ACMP1_O            | 2: PD7<br>3: PA12 | 7: PA5  | Analog comparator ACMP1, digital output.                                 |  |  |  |  |  |

|                    | 0: PD7            |         |                                                                          |  |  |  |  |  |

| ADC0_EXTN          |                   |         | Analog to digital converter ADC0 external reference input negative pin.  |  |  |  |  |  |

|                    | 0: PD6            |         |                                                                          |  |  |  |  |  |

| ADC0_EXTP          |                   |         | Analog to digital converter ADC0 external reference input positive pin.  |  |  |  |  |  |

|                    | 0: PF1            |         |                                                                          |  |  |  |  |  |

| BOOT_RX            |                   |         | Bootloader RX.                                                           |  |  |  |  |  |

|                    | 0: PF0            |         |                                                                          |  |  |  |  |  |

| BOOT_TX            |                   |         | Bootloader TX.                                                           |  |  |  |  |  |

|                    | 0: PA8            |         |                                                                          |  |  |  |  |  |

| BU_STAT            |                   |         | Backup Power Domain status, whether or not the system is in backup mode. |  |  |  |  |  |

|                    | 0: PD8            |         |                                                                          |  |  |  |  |  |

| BU_VIN             |                   |         | Battery input for Backup Power Domain.                                   |  |  |  |  |  |

|                    | 0: PA12           |         |                                                                          |  |  |  |  |  |

| BU_VOUT            |                   |         | Power output for Backup Power Domain.                                    |  |  |  |  |  |

|                    | 0: PC0<br>1: PF0  |         |                                                                          |  |  |  |  |  |

| CAN0_RX            | 2: PD0            |         | CAN0 RX.                                                                 |  |  |  |  |  |

#### Table 5.15. Alternate Functionality Overview

| Alternate     | LOCA                                  | ATION              |                                                                                                                                                                                      |  |  |  |  |  |  |

|---------------|---------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Functionality | 0 - 3                                 | 4 - 7              | Description                                                                                                                                                                          |  |  |  |  |  |  |

| CAN0_TX       | 0: PC1<br>1: PF2<br>2: PD1            |                    | CAN0 TX.                                                                                                                                                                             |  |  |  |  |  |  |

| CMU_CLK0      | 0: PA2<br>1: PC12<br>2: PD7           | 4: PF2<br>5: PA12  | Clock Management Unit, clock output number 0.                                                                                                                                        |  |  |  |  |  |  |

| CMU_CLK1      | 0: PA1<br>1: PD8<br>2: PE12           | 4: PF3<br>5: PB11  | Clock Management Unit, clock output number 1.                                                                                                                                        |  |  |  |  |  |  |

| CMU_CLK2      | 0: PA0<br>1: PA3<br>2: PD6            | 4: PA3             | Clock Management Unit, clock output number 2.                                                                                                                                        |  |  |  |  |  |  |

| CMU_CLKI0     | 0: PD4<br>1: PA3<br>2: PB8<br>3: PB13 | 6: PE12<br>7: PB11 | Clock Management Unit, clock input number 0.                                                                                                                                         |  |  |  |  |  |  |

| DBG_SWCLKTCK  | 0: PF0                                |                    | Debug-interface Serial Wire clock input and JTAG Test Clock.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull down.                            |  |  |  |  |  |  |

| DBG_SWDIOTMS  | 0: PF1                                |                    | Debug-interface Serial Wire data input / output and JTAG Test Mode Select.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull up.                |  |  |  |  |  |  |

| DBG_TDI       | 0: PF5                                |                    | Debug-interface JTAG Test Data In.<br>Note that this function becomes available after the first valid JTAG command is re-<br>ceived, and has a built-in pull up when JTAG is active. |  |  |  |  |  |  |

| DBG_TDO       | 0: PF2                                |                    | Debug-interface JTAG Test Data Out.<br>Note that this function becomes available after the first valid JTAG command is re-<br>ceived.                                                |  |  |  |  |  |  |

| GPIO_EM4WU0   | 0: PA0                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| GPIO_EM4WU1   | 0: PA6                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| GPIO_EM4WU2   | 0: PC9                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| GPIO_EM4WU3   | 0: PF1                                |                    | Pin can be used to wake the system up from EM4                                                                                                                                       |  |  |  |  |  |  |

| Alternate     | LOCA    | TION  |                                  |  |  |  |  |  |  |  |  |

|---------------|---------|-------|----------------------------------|--|--|--|--|--|--|--|--|

| Functionality | 0 - 3   | 4 - 7 | Description                      |  |  |  |  |  |  |  |  |

| LCD_COM0      | 0: PE4  |       | LCD driver common line number 0. |  |  |  |  |  |  |  |  |

| LCD_COM1      | 0: PE5  |       | LCD driver common line number 1. |  |  |  |  |  |  |  |  |

| LCD_COM2      | 0: PE6  |       | LCD driver common line number 2. |  |  |  |  |  |  |  |  |

| LCD_COM3      | 0: PE7  |       | LCD driver common line number 3. |  |  |  |  |  |  |  |  |

| LCD_SEG0      | 0: PF2  |       | LCD segment line 0.              |  |  |  |  |  |  |  |  |

| LCD_SEG1      | 0: PF3  |       | LCD segment line 1.              |  |  |  |  |  |  |  |  |

| LCD_SEG2      | 0: PF4  |       | LCD segment line 2.              |  |  |  |  |  |  |  |  |

| LCD_SEG3      | 0: PF5  |       | LCD segment line 3.              |  |  |  |  |  |  |  |  |

| LCD_SEG4      | 0: PE8  |       | LCD segment line 4.              |  |  |  |  |  |  |  |  |

| LCD_SEG5      | 0: PE9  |       | LCD segment line 5.              |  |  |  |  |  |  |  |  |

| LCD_SEG6      | 0: PE10 |       | LCD segment line 6.              |  |  |  |  |  |  |  |  |

| LCD_SEG7      | 0: PE11 |       | LCD segment line 7.              |  |  |  |  |  |  |  |  |

| LCD_SEG8      | 0: PE12 |       | LCD segment line 8.              |  |  |  |  |  |  |  |  |

| Alternate     | LOC                                   | ATION                        |                                            |  |  |  |  |  |  |  |  |

|---------------|---------------------------------------|------------------------------|--------------------------------------------|--|--|--|--|--|--|--|--|

| Functionality | 0 - 3                                 | 4 - 7                        | Description                                |  |  |  |  |  |  |  |  |

| LES_CH4       | 0: PC4                                |                              | LESENSE channel 4.                         |  |  |  |  |  |  |  |  |

| LES_CH5       | 0: PC5                                |                              | LESENSE channel 5.                         |  |  |  |  |  |  |  |  |

| LES_CH6       | 0: PC6                                |                              | LESENSE channel 6.                         |  |  |  |  |  |  |  |  |

| LES_CH7       | 0: PC7                                |                              | LESENSE channel 7.                         |  |  |  |  |  |  |  |  |

| LES_CH8       | 0: PC8                                |                              | LESENSE channel 8.                         |  |  |  |  |  |  |  |  |

| LES_CH9       | 0: PC9                                |                              | LESENSE channel 9.                         |  |  |  |  |  |  |  |  |

| LES_CH10      | 0: PC10                               |                              | LESENSE channel 10.                        |  |  |  |  |  |  |  |  |

| LES_CH11      | 0: PC11                               |                              | LESENSE channel 11.                        |  |  |  |  |  |  |  |  |

| LES_CH12      | 0: PC12                               |                              | LESENSE channel 12.                        |  |  |  |  |  |  |  |  |

| LES_CH13      | 0: PC13                               |                              | LESENSE channel 13.                        |  |  |  |  |  |  |  |  |

| LES_CH14      | 0: PC14                               |                              | LESENSE channel 14.                        |  |  |  |  |  |  |  |  |

| LES_CH15      | 0: PC15                               |                              | LESENSE channel 15.                        |  |  |  |  |  |  |  |  |

| LETIM0_OUT0   | 0: PD6<br>1: PB11<br>2: PF0<br>3: PC4 | 4: PE12<br>5: PC14<br>6: PA8 | Low Energy Timer LETIM0, output channel 0. |  |  |  |  |  |  |  |  |

| Alternate     | LOC                        | ATION  |                                                        |

|---------------|----------------------------|--------|--------------------------------------------------------|

| Functionality | 0 - 3                      | 4 - 7  | Description                                            |

| WTIM1_CC3     | 0: PD1<br>1: PD5<br>2: PC6 | 4: PE6 | Wide timer 1 Capture Compare input / output channel 3. |

| Port    | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СН9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

|---------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CE      | CEXT  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1X | BUSAX |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT1Y | BUSAY |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | PA9 |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT3X | BUSCX |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

| APORT3Y | BUSCY |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| CE      | хт_   | SEN  | ISE  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT2X | BUSBX |      |      | PB13 |      | PB11 |      |      |      |      |      | PB5  |      | PB3  |      |      |      | PA15 |      | PA13 |      |      |      | 6Yd |     |     |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y | BUSBY |      | PB14 |      | PB12 |      |      |      |      |      | PB6  |      | PB4  |      |      |      |      |      | PA14 |      |      |      | PA10 |     |     |     | PA6 |     | PA4 |     | PA2 |     | PAO |

| APORT4X | BUSDX |      |      |      |      |      |      |      |      |      |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     |     |     |

| APORT4Y | BUSDY |      |      |      |      |      |      |      |      |      |      |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     |     |

# Table 5.19. CSEN Bus and Pin Mapping

| Dimension | Min       | Тур  | Мах  |  |  |  |  |  |  |  |  |  |

|-----------|-----------|------|------|--|--|--|--|--|--|--|--|--|

| A         | 0.70      | 0.75 | 0.80 |  |  |  |  |  |  |  |  |  |

| A1        | 0.00      | _    | 0.05 |  |  |  |  |  |  |  |  |  |

| b         | 0.20      | 0.25 | 0.30 |  |  |  |  |  |  |  |  |  |

| A3        | 0.203 REF |      |      |  |  |  |  |  |  |  |  |  |

| D         | 9.00 BSC  |      |      |  |  |  |  |  |  |  |  |  |

| е         | 0.40 BSC  |      |      |  |  |  |  |  |  |  |  |  |

| E         | 9.00 BSC  |      |      |  |  |  |  |  |  |  |  |  |

| D2        | 7.10      | 7.20 | 7.30 |  |  |  |  |  |  |  |  |  |

| E2        | 7.10      | 7.20 | 7.30 |  |  |  |  |  |  |  |  |  |

| L         | 0.35      | 0.40 | 0.45 |  |  |  |  |  |  |  |  |  |

| ааа       |           | 0.10 |      |  |  |  |  |  |  |  |  |  |

| bbb       |           | 0.10 |      |  |  |  |  |  |  |  |  |  |

| ссс       |           | 0.10 |      |  |  |  |  |  |  |  |  |  |

| ddd       |           | 0.05 |      |  |  |  |  |  |  |  |  |  |

| eee       |           | 0.08 |      |  |  |  |  |  |  |  |  |  |

| Nata      |           |      |      |  |  |  |  |  |  |  |  |  |

## Table 7.1. QFN80 Package Dimensions

# Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

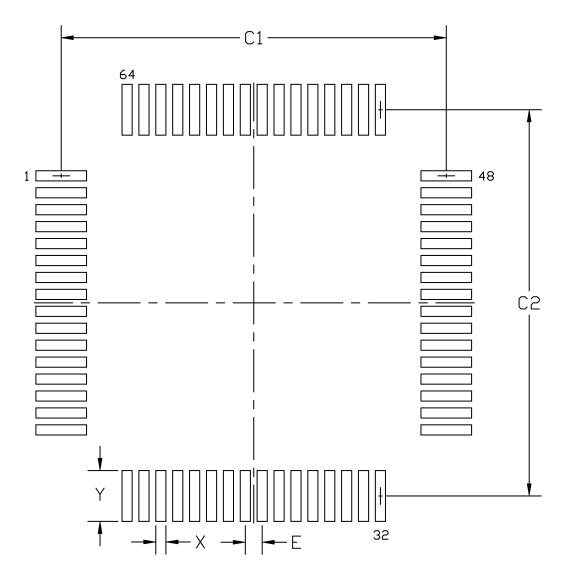

## 8.2 TQFP64 PCB Land Pattern

Figure 8.2. TQFP64 PCB Land Pattern Drawing

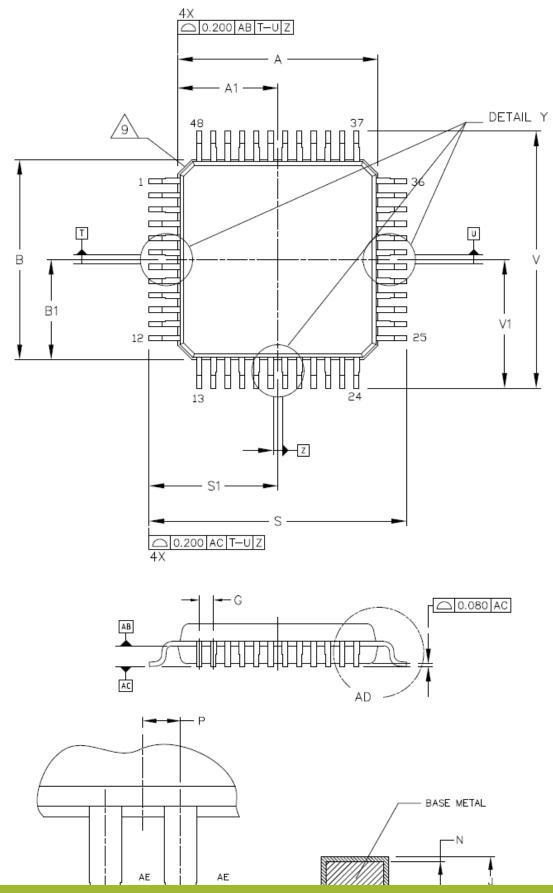

# 10. TQFP48 Package Specifications

# 10.1 TQFP48 Package Dimensions

| Dimension | Min            | Тур    | Мах  |  |  |  |  |  |  |  |  |  |

|-----------|----------------|--------|------|--|--|--|--|--|--|--|--|--|

| A         | 0.70           | 0.75   | 0.80 |  |  |  |  |  |  |  |  |  |

| A1        | 0.00           | ) — () |      |  |  |  |  |  |  |  |  |  |

| A3        | 0.203 REF      |        |      |  |  |  |  |  |  |  |  |  |

| b         | 0.20 0.25 0.30 |        |      |  |  |  |  |  |  |  |  |  |

| D         | 5.0 BSC        |        |      |  |  |  |  |  |  |  |  |  |

| D2/E2     | 3.60 3.70 3.80 |        |      |  |  |  |  |  |  |  |  |  |

| E         | 5.0 BSC        |        |      |  |  |  |  |  |  |  |  |  |

| е         | 0.50 BSC       |        |      |  |  |  |  |  |  |  |  |  |

| L         | 0.35           | 0.40   | 0.45 |  |  |  |  |  |  |  |  |  |

| ааа       |                | 0.10   |      |  |  |  |  |  |  |  |  |  |

| bbb       |                | 0.10   |      |  |  |  |  |  |  |  |  |  |

| ссс       |                | 0.10   |      |  |  |  |  |  |  |  |  |  |

| ddd       |                | 0.05   |      |  |  |  |  |  |  |  |  |  |

| eee       |                | 0.08   |      |  |  |  |  |  |  |  |  |  |

| •• .      |                |        |      |  |  |  |  |  |  |  |  |  |

## Table 11.1. QFN32 Package Dimensions

Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MO-220, Variation VKKD-4.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.