# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 20MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x12b; D/A 2x12b                                           |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f001-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

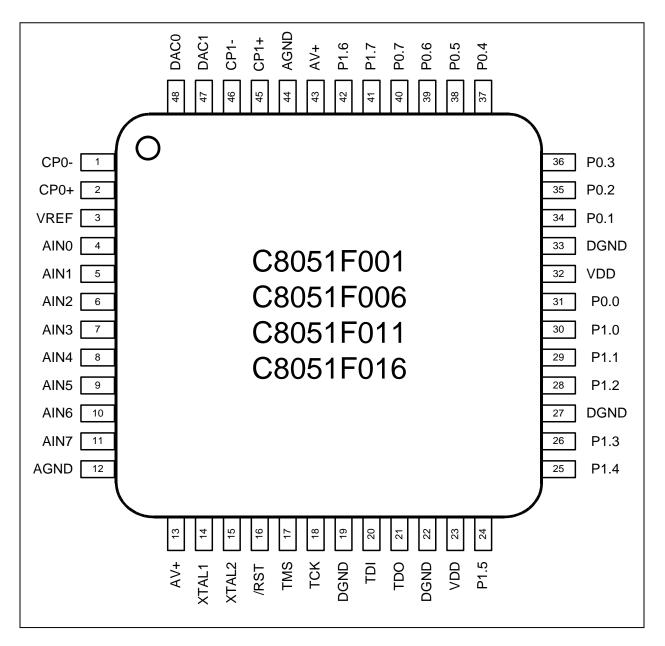

Figure 4.3. TQFP-48 Pinout Diagram

|         | I Igui                           |               | 0001011        |                 | i negister      | (0000110       | (012)             |              |

|---------|----------------------------------|---------------|----------------|-----------------|-----------------|----------------|-------------------|--------------|

| R/W     |                                  | R/W           | R/W            | R/W             | R/W             | R/W            | R/W               | Reset Value  |

| ADCE    |                                  | ADCINT        | ADBUSY         | ADSTM1          | ADSTM0          | ADWINT         | ADLJST            | 00000000     |

| Bit7    | Bit6                             | Bit5          | Bit4           | Bit3            | Bit2            | Bit1           | Bit0              | SFR Address: |

|         |                                  |               |                |                 |                 |                | (bit addressable) | 0xE8         |

| Bit7:   | ADCEN: ADC                       | Enable Bit    |                |                 |                 |                |                   |              |

|         | 0: ADC Disable                   | ed. ADC is i  | n low power    | shutdown.       |                 |                |                   |              |

|         | 1: ADC Enable                    |               |                |                 | onversions.     |                |                   |              |

| Bit6:   | ADCTM: ADC                       | Track Mode    | Bit            | -               |                 |                |                   |              |

|         | 0: When the Al                   | DC is enabled | l, tracking is | always done     | unless a con    | version is in  | process           |              |

|         | 1: Tracking De                   | fined by ADS  | STM1-0 bits    |                 |                 |                |                   |              |

|         | ADST                             |               |                |                 |                 |                |                   |              |

|         |                                  | -             |                | te of 1 to AD   |                 |                |                   |              |

|         |                                  |               |                | flow of Time    |                 | for 3 SAR clo  | ocks              |              |

|         |                                  |               |                | /STR input is   |                 |                | _                 |              |

| D: -    |                                  |               |                | flow of Time    | er 2 and last f | for 3 SAR clo  | ocks              |              |

| Bit5:   | ADCINT: ADC                      |               | -              | terrupt Flag    |                 |                |                   |              |

|         | (Must be cleared                 |               |                |                 | 1               | . (1           | 4                 |              |

|         | 0: ADC has not                   |               |                |                 | e last time thi | s flag was cl  | eared             |              |

| Bit4:   | 1: ADC has con                   |               | a conversion   |                 |                 |                |                   |              |

| DII4:   | ADBUSY: ADO<br>Read              |               |                |                 |                 |                |                   |              |

|         | 0: ADC Conver                    | rsion comple  | te or no valid | l data has bee  | n converted     | since a reset  | The falling       |              |

|         |                                  |               |                | ipt when ena    |                 | since a reset. | The family        |              |

|         | 1: ADC Busy c                    |               |                | T' mien enu     |                 |                |                   |              |

|         | Write                            |               |                |                 |                 |                |                   |              |

|         | 0: No effect                     |               |                |                 |                 |                |                   |              |

|         | 1: Starts ADC                    | Conversion if | ADSTM1-0       | 0 = 00b         |                 |                |                   |              |

| Bits3-2 | ADSTM1-0: AI                     | DC Start of C | onversion M    | lode Bits       |                 |                |                   |              |

|         | 00: ADC conve                    |               |                |                 |                 |                |                   |              |

|         | 01: ADC conve                    |               |                |                 |                 |                |                   |              |

|         | 10: ADC conve                    |               |                |                 |                 |                |                   |              |

|         | 11: ADC conve                    |               |                |                 | er 2            |                |                   |              |

| Bit1:   | ADWINT: ADO                      |               | -              | rupt Flag       |                 |                |                   |              |

|         | (Must be cleared                 |               |                | 11.             | 1               |                |                   |              |

|         | 0: ADC Windo                     |               |                |                 | urred           |                |                   |              |

| D:40.   | 1: ADC Windo                     | -             |                | n occurred      |                 |                |                   |              |

| Bit0:   | ADLJST: ADC                      | •             |                | right instified |                 |                |                   |              |

|         | 0: Data in ADC<br>1: Data in ADC |               |                |                 |                 |                |                   |              |

|         | 1. Data III ADC                  | UR.ADCUL      | Registers is I | ien justified   |                 |                |                   |              |

|         |                                  |               |                |                 |                 |                |                   |              |

### Figure 5.7. ADC0CN: ADC Control Register (C8051F00x)

### Figure 5.15. 12-Bit ADC Window Interrupt Examples, Left Justified Data

| Input Voltage<br>(AD0 - AGND) | ADC Data<br>Word | _                      |

|-------------------------------|------------------|------------------------|

| REF x (4095/4096)             | 0xFFF0           |                        |

|                               |                  | ADWINT<br>not affected |

|                               | 0x2010           |                        |

| REF x (512/4096)              | 0x2000           | ADC0LTH:ADC0LTL        |

|                               | 0x1FF0<br>0x1010 | ADWINT=1               |

| REF x (256/4096)              | 0x1000           | ADC0GTH:ADC0GTL        |

|                               | 0x0FF0           | ADWINT<br>not affected |

| 0                             | 0x0000           |                        |

#### Given:

AMX0SL = 0x00, AMX0CF = 0x00, ADLJST = 1, ADC0LTH:ADC0LTL = 0x2000,ADC0GTH:ADC0GTL = 0x1000.

An ADC End of Conversion will cause an ADC Window Compare Interrupt (ADWINT=1) if the resulting ADC Data Word is < 0x2000 and > 0x1000.

| Input Voltage<br>(AD0 - AGND) | ADC Data<br>Word |                        |

|-------------------------------|------------------|------------------------|

| REF x (4095/4096)             | 0xFFF0           | ADWINT=1               |

|                               | 0x2010           |                        |

| REF x (512/4096)              | 0x2000           | ADC0GTH:ADC0GTL        |

|                               | 0x1FF0<br>0x1010 | ADWINT<br>not affected |

| REF x (256/4096)              | 0x1000           | ADC0LTH:ADC0LTL        |

|                               | 0x0FF0           | ADWINT=1               |

| 0                             | 0x0000           | ] ]                    |

#### Given:

AMX0SL = 0x00, AMX0CF = 0x00, ADLJST = 1, ADC0LTH:ADC0LTL = 0x1000, ADC0GTH:ADC0GTL = 0x2000.

An ADC End of Conversion will cause an ADC Window Compare Interrupt (ADWINT=1) if the resulting ADC Data Word is < 0x1000 or > 0x2000.

ADC Data

Word

0x7FF0

0x1010

0x1000

0x0FF0

0x0000

0xFFF0

0xFFE0

0x8000

ADWINT=1

ADC0GTH:ADC0GTL

ADC0LTH:ADC0LTL

ADWINT=1

ADWINT not affected

| Input Voltage<br>(AD0 - AD1) | ADC Data<br>Word |                        | Input Voltage<br>(AD0 - AD1) |

|------------------------------|------------------|------------------------|------------------------------|

| REF x (2047/2048)            | 0x7FF0           |                        | REF x (2047/2048)            |

|                              |                  | ADWINT<br>not affected |                              |

|                              | 0x1010           |                        |                              |

| REF x (256/2048)             | 0x1000           | ADC0LTH:ADC0LTL        | REF x (256/2048)             |

|                              | 0x0FF0<br>0x0000 | ADWINT=1               |                              |

| REF x (-1/2048)              | 0xFFF0           | ADC0GTH:ADC0GTL        | REF x (-1/2048)              |

|                              | 0xFFE0           |                        |                              |

|                              |                  | ADWINT<br>not affected |                              |

| -REF                         | 0x8000           |                        | -REF                         |

|                              |                  |                        |                              |

#### Given:

#### AMX0SL = 0x00, AMX0CF = 0x01, ADLJST = 1, ADC0LTH:ADC0LTH = 0xFFF0, ADC0GTH:ADC0GTL = 0x1000.

An ADC End of Conversion will cause an ADC Window Compare Interrupt (ADWINT=1) if the resulting ADC Data Word is < 0x1000 and > 0xFFF0. (Two's Complement math.)

AMX0SL = 0x00, AMX0CF = 0x01, ADLJST = 1,

ADC0LTH:ADC0LTL = 0x1000,

ADC0GTH:ADC0GTL = 0xFFF0.

An ADC End of Conversion will cause an ADC Window Compare Interrupt (ADWINT=1) if the resulting ADC Data Word is < 0xFFF0 or > 0x1000. (Two's Complement math.)

Given:

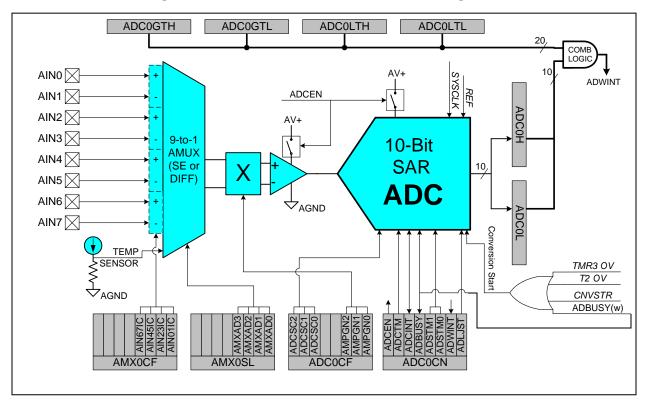

### 6. ADC (10-Bit, C8051F010/1/2/5/6/7 Only)

The ADC subsystem for the C8051F010/1/2/5/6/7 consists of a 9-channel, configurable analog multiplexer (AMUX), a programmable gain amplifier (PGA), and a 100ksps, 10-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector (see block diagram in Figure 6.1). The AMUX, PGA, Data Conversion Modes, and Window Detector are all configurable under software control via the Special Function Register's shown in Figure 6.1. The ADC subsystem (ADC, track-and-hold and PGA) is enabled only when the ADCEN bit in the ADC Control register (ADC0CN, Figure 6.7) is set to 1. The ADC subsystem is in low power shutdown when this bit is 0. The Bias Enable bit (BIASE) in the REF0CN register (see Figure 9.2) must be set to 1 in order to supply bias to the ADC.

#### 6.1. Analog Multiplexer and PGA

Eight of the AMUX channels are available for external measurements while the ninth channel is internally connected to an on-board temperature sensor (temperature transfer function is shown in Figure 6.3). Note that the PGA gain is applied to the temperature sensor reading. AMUX input pairs can be programmed to operate in either the differential or single-ended mode. This allows the user to select the best measurement technique for each input channel, and even accommodates mode changes "on-the-fly". The AMUX defaults to all single-ended inputs upon reset. There are two registers associated with the AMUX: the Channel Selection register AMX0SL (Figure 6.5), and the Configuration register AMX0CF (Figure 6.4). The table in Figure 6.5 shows AMUX functionality by channel for each possible configuration. The PGA amplifies the AMUX output signal by an amount determined by the AMPGN2-0 bits in the ADC Configuration register, ADC0CF (Figure 6.6). The PGA can be software-programmed for gains of 0.5, 1, 2, 4, 8 or 16. It defaults to unity gain on reset.

### Figure 6.5. AMX0SL: AMUX Channel Select Register (C8051F01x)

| W  | ŀ     | R/W<br>-           | R/W     | R/W                                  |             | R/W<br>1XAD3       | R/W<br>AMXAD2 | R/W<br>AMXAI       | 1    | R/W H<br>XAD0 (        |

|----|-------|--------------------|---------|--------------------------------------|-------------|--------------------|---------------|--------------------|------|------------------------|

| 7  | I     | Bit6               | Bit5    | Bit4                                 |             | Bit3               | Bit2          | Bit1               | ]    | Bit0 S                 |

| 0: | AMXAI | 03-0: AM           | UX Addr | Write = do<br>ess Bits<br>lected per | chart be    |                    | 2.0           |                    |      |                        |

|    |       | 0000               | 0001    | 0010                                 | <b>0011</b> | AMXAD:<br>0100     | <b>0101</b>   | 0110               | 0111 | 1                      |

| 1  | 0000  | AIN0               | AIN1    | AIN2                                 | AIN3        | AIN4               | AIN5          | AIN6               | AIN7 | 1xxxTEMPSENSOR         |

|    | 0001  | +(AIN0)<br>-(AIN1) |         | AIN2                                 | AIN3        | AIN4               | AIN5          | AIN6               | AIN7 | TEMP<br>SENSOR         |

|    | 0010  | AIN0               | AIN1    | +(AIN2)<br>-(AIN3)                   |             | AIN4               | AIN5          | AIN6               | AIN7 | TEMP<br>SENSOR         |

|    | 0011  | +(AIN0)<br>-(AIN1) |         | +(AIN2)<br>-(AIN3)                   |             | AIN4               | AIN5          | AIN6               | AIN7 | TEMP<br>SENSOR         |

|    | 0100  | AIN0               | AIN1    | AIN2                                 | AIN3        | +(AIN4)<br>-(AIN5) |               | AIN6               | AIN7 | TEMP<br>SENSOR         |

|    | 0101  | +(AIN0)<br>-(AIN1) |         | AIN2                                 | AIN3        | +(AIN4)<br>-(AIN5) |               | AIN6               | AIN7 | TEMP<br>SENSOR         |

|    | 0110  | AIN0               | AIN1    | +(AIN2)<br>-(AIN3)                   |             | +(AIN4)<br>-(AIN5) |               | AIN6               | AIN7 | TEMP<br>SENSOR         |

|    | 0111  | +(AIN0)<br>-(AIN1) |         | +(AIN2)<br>-(AIN3)                   |             | +(AIN4)<br>-(AIN5) |               | AIN6               | AIN7 | TEMP<br>SENSOR         |

|    | 1000  | AIN0               | AIN1    | AIN2                                 | AIN3        | AIN4               | AIN5          | +(AIN6)<br>-(AIN7) |      | TEMP<br>SENSOR         |

|    | 1001  | +(AIN0)<br>-(AIN1) |         | AIN2                                 | AIN3        | AIN4               | AIN5          | +(AIN6)<br>-(AIN7) |      | TEMP<br>SENSOR         |

| •  | 1010  | AIN0               | AIN1    | +(AIN2)<br>-(AIN3)                   |             | AIN4               | AIN5          | +(AIN6)<br>-(AIN7) |      | TEMP<br>SENSOR         |

|    | 1011  | +(AIN0)<br>-(AIN1) |         | +(AIN2)<br>-(AIN3)                   |             | AIN4               | AIN5          | +(AIN6)<br>-(AIN7) |      | TEMP<br>SENSOR         |

|    | 1100  | AIN0               | AIN1    | AIN2                                 | AIN3        | +(AIN4)<br>-(AIN5) |               | +(AIN6)<br>-(AIN7) |      | TEMP<br>SENSOR<br>TEMP |

|    | 1101  | +(AIN0)<br>-(AIN1) |         | AIN2                                 | AIN3        | +(AIN4)<br>-(AIN5) |               | +(AIN6)<br>-(AIN7) |      | SENSOR                 |

|    | 1110  | AIN0               | AIN1    | +(AIN2)<br>-(AIN3)                   |             | +(AIN4)<br>-(AIN5) |               | +(AIN6)<br>-(AIN7) |      | TEMP<br>SENSOR         |

|    | 1111  | +(AIN0)<br>-(AIN1) |         | +(AIN2)<br>-(AIN3)                   |             | +(AIN4)<br>-(AIN5) |               | +(AIN6)<br>-(AIN7) |      | TEMP<br>SENSOR         |

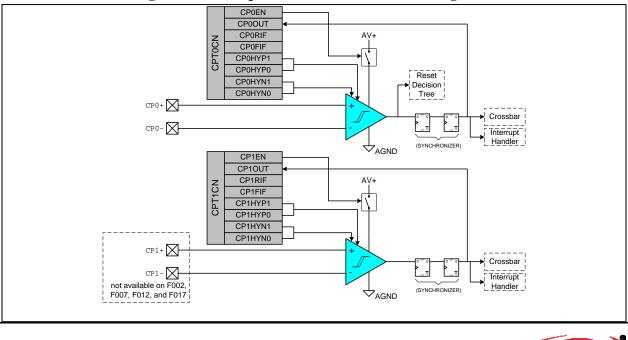

### 8. COMPARATORS

The MCU family has two on-chip analog voltage comparators as shown in Figure 8.1. The inputs of each Comparator are available at the package pins. The output of each comparator is optionally available at the package pins via the I/O crossbar (see Section 15.1). When assigned to package pins, each comparator output can be programmed to operate in open drain or push-pull modes (see section 15.3).

The hysteresis of each comparator is software-programmable via its respective Comparator control register (CPT0CN, CPT1CN). The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage. The output of the comparator can be polled in software, or can be used as an interrupt source. Each comparator can be individually enabled or disabled (shutdown). When disabled, the comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, its interrupt capability is suspended and its supply current falls to less than  $1\mu$ A. Comparator 0 inputs can be externally driven from -0.25V to (AV+) + 0.25V without damage or upset.

The Comparator 0 hysteresis is programmed using bits 3-0 in the Comparator 0 Control Register CPT0CN (shown in Figure 8.3). The amount of *negative* hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Figure 8.2, settings of 10, 4 or 2mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of *positive* hysteresis is determined by the setting the CP0HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section 10.4). The CPOFIF flag is set upon a Comparator 0 falling-edge interrupt, and the CPORIF flag is set upon the Comparator 0 rising-edge interrupt. Once set, these bits remain set until cleared by the CPU. The Output State of Comparator 0 can be obtained at any time by reading the CPOOUT bit. Note the comparator output and interrupt should be ignored until the comparator settles after power-up. Comparator 0 is enabled by setting the CPOEN bit, and is disabled by clearing this bit. Note there is a 20usec settling time for the comparator output to stabilize after setting the CPOEN bit or a power-up. Comparator 0 can also be programmed as a reset source. For details, see Section 13.

The operation of Comparator 1 is identical to that of Comparator 0, except the Comparator 1 is controlled by the CPT1CN Register (Figure 8.4). Comparator 1 can not be programmed as a reset source. Also, the input pins for Comparator 1 are not pinned out on the F002, F007, F012, or F017 devices. The complete electrical specifications for the Comparators are given in Table 8.1.

Figure 8.1. Comparator Functional Block Diagram

| R/W                                                                                       | R/W                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                      | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reset Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                                                                         | -                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                       | TEMPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BIASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REFBE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bit6                                                                                      | Bit5                                                                                                                                                        | Bit4                                                                                                                                                                                                                                                                                                     | Bit3                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit2                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SFR Address:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                           |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0xD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UNUSED. Read                                                                              | d = 00000b;                                                                                                                                                 | Write = don'                                                                                                                                                                                                                                                                                             | t care                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TEMPE: Tempe                                                                              | rature Senso                                                                                                                                                | r Enable Bit                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0: Internal Tem                                                                           | perature Sen                                                                                                                                                | sor Off.                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1: Internal Tem                                                                           | perature Sen                                                                                                                                                | sor On.                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BIASE: Bias En                                                                            | able Bit for A                                                                                                                                              | ADC and DA                                                                                                                                                                                                                                                                                               | AC's                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0: Internal Bias                                                                          | Off.                                                                                                                                                        |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1: Internal Bias                                                                          | On (required                                                                                                                                                | l for use of A                                                                                                                                                                                                                                                                                           | DC or DAC                                                                                                                                                                                                                                                                                                                                                                                                                               | 's).                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>REFBE:</b> Interna                                                                     | l Voltage Re                                                                                                                                                | ference Buff                                                                                                                                                                                                                                                                                             | er Enable Bit                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0: Internal Reference Buffer Off. System reference can be driven from external source on  |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1                                                                                         |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1: Internal Reference Buffer On. System reference provided by internal voltage reference. |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                           |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                           |                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                           | UNUSED. Read<br>TEMPE: Tempe<br>0: Internal Tem<br>I: Internal Tem<br>BIASE: Bias En<br>0: Internal Bias<br>REFBE: Interna<br>0: Internal Refe<br>VREF pin. | <ul> <li>UNUSED. Read = 00000b;</li> <li>TEMPE: Temperature Senso</li> <li>0: Internal Temperature Sen</li> <li>BIASE: Bias Enable Bit for A</li> <li>0: Internal Bias Off.</li> <li>1: Internal Bias On (required REFBE: Internal Voltage Re</li> <li>0: Internal Reference Buffer VREF pin.</li> </ul> | <ul> <li>UNUSED. Read = 00000b; Write = don'<br/>TEMPE: Temperature Sensor Enable Bit</li> <li>0: Internal Temperature Sensor Off.</li> <li>1: Internal Temperature Sensor On.</li> <li>BIASE: Bias Enable Bit for ADC and DA</li> <li>0: Internal Bias Off.</li> <li>1: Internal Bias On (required for use of A<br/>REFBE: Internal Voltage Reference Buffe</li> <li>0: Internal Reference Buffer Off. System<br/>VREF pin.</li> </ul> | <ul> <li>UNUSED. Read = 00000b; Write = don't care<br/>TEMPE: Temperature Sensor Enable Bit</li> <li>0: Internal Temperature Sensor Off.</li> <li>1: Internal Temperature Sensor On.</li> <li>BIASE: Bias Enable Bit for ADC and DAC's</li> <li>0: Internal Bias Off.</li> <li>1: Internal Bias On (required for use of ADC or DAC<br/>REFBE: Internal Voltage Reference Buffer Enable Bit</li> <li>0: Internal Reference Buffer Off. System reference ca<br/>VREF pin.</li> </ul> | <ul> <li>UNUSED. Read = 00000b; Write = don't care</li> <li>TEMPE: Temperature Sensor Enable Bit</li> <li>0: Internal Temperature Sensor Off.</li> <li>1: Internal Temperature Sensor On.</li> <li>BIASE: Bias Enable Bit for ADC and DAC's</li> <li>0: Internal Bias Off.</li> <li>1: Internal Bias On (required for use of ADC or DAC's).</li> <li>REFBE: Internal Voltage Reference Buffer Enable Bit</li> <li>0: Internal Reference Buffer Off. System reference can be driven for VREF pin.</li> </ul> | <ul> <li>UNUSED. Read = 00000b; Write = don't care</li> <li>TEMPE: Temperature Sensor Enable Bit</li> <li>0: Internal Temperature Sensor Off.</li> <li>1: Internal Temperature Sensor On.</li> <li>BIASE: Bias Enable Bit for ADC and DAC's</li> <li>0: Internal Bias Off.</li> <li>1: Internal Bias On (required for use of ADC or DAC's).</li> <li>REFBE: Internal Voltage Reference Buffer Enable Bit</li> <li>0: Internal Reference Buffer Off. System reference can be driven from external VREF pin.</li> </ul> | <ul> <li>UNUSED. Read = 00000b; Write = don't care</li> <li>TEMPE: Temperature Sensor Enable Bit</li> <li>0: Internal Temperature Sensor Off.</li> <li>1: Internal Temperature Sensor On.</li> <li>BIASE: Bias Enable Bit for ADC and DAC's</li> <li>0: Internal Bias Off.</li> <li>1: Internal Bias On (required for use of ADC or DAC's).</li> <li>REFBE: Internal Voltage Reference Buffer Enable Bit</li> <li>0: Internal Reference Buffer Off. System reference can be driven from external source on</li> </ul> |

### Figure 9.2. REF0CN: Reference Control Register

#### Table 9.1. Reference Electrical Characteristics

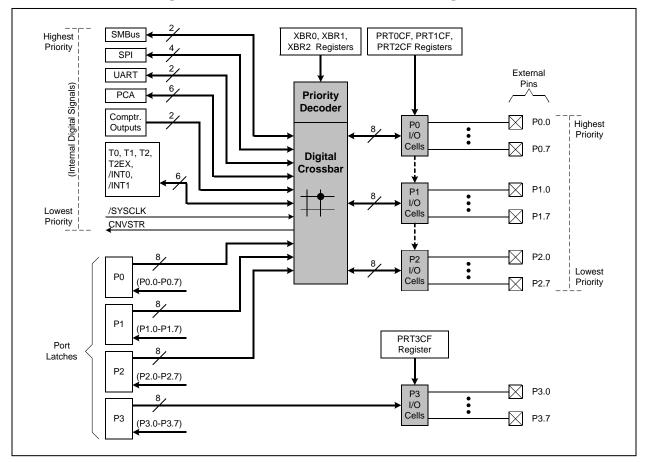

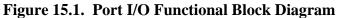

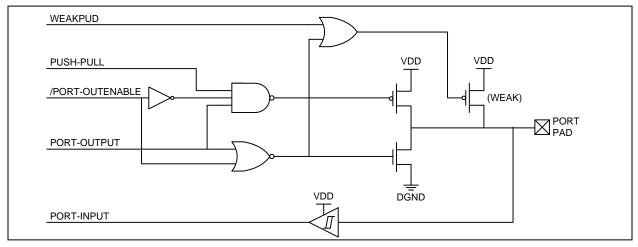

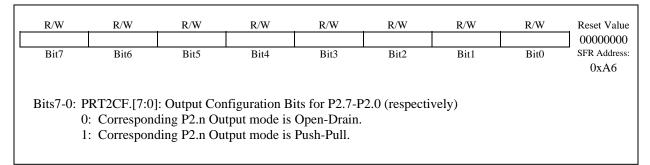

VDD = 3.0V, AV + = 3.0V,  $-40^{\circ}C$  to  $+85^{\circ}C$  unless otherwise specified.