### Silicon Labs - C8051F002 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 20MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT          |

| Number of I/O              | 8                                                           |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | ·                                                           |

| RAM Size                   | 256 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 4x12b; D/A 2x12b                                        |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f002 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

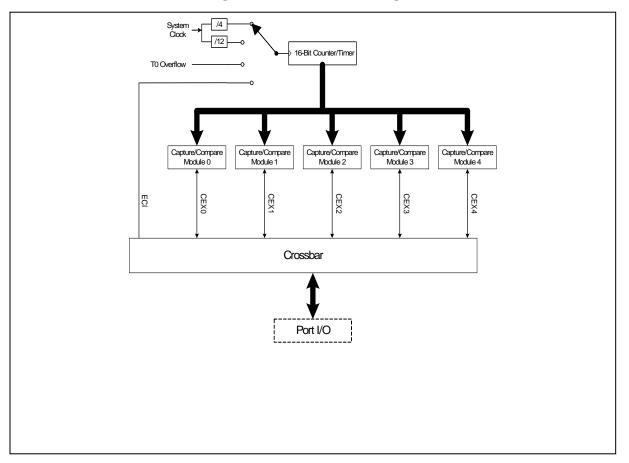

## **1.5.** Programmable Counter Array

The C8051F000 MCU family has an on-board Programmable Counter/Timer Array (PCA) in addition to the four 16-bit general-purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer timebase with 5 programmable capture/compare modules. The timebase gets its clock from one of four sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflow, or an External Clock Input (ECI).

Each capture/compare module can be configured to operate in one of four modes: Edge-Triggered Capture, Software Timer, High Speed Output, or Pulse Width Modulator. The PCA Capture/Compare Module I/O and External Clock Input are routed to the MCU Port I/O via the Digital Crossbar.

## **1.6.** Serial Ports

The C8051F000 MCU Family includes a Full-Duplex UART, SPI Bus, and I2C/SMBus. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little intervention by the CPU. The serial buses do not "share" resources such as timers, interrupts, or Port I/O, so any or all of the serial buses may be used together.

## 2. ABSOLUTE MAXIMUM RATINGS\*

| Ambient temperature under bias                                    | 55 to 125°C                |

|-------------------------------------------------------------------|----------------------------|

| Storage Temperature                                               | 65 to 150°C                |

| Voltage on any Pin (except VDD and Port I/O) with respect to DGND | $-0.3V$ to (VDD $+ 0.3V$ ) |

| Voltage on any Port I/O Pin or /RST with respect to DGND          | 0.3V to 5.8V               |

| Voltage on VDD with respect to DGND                               | 0.3V to 4.2V               |

| Maximum Total current through VDD, AV+, DGND and AGND             | 800mA                      |

| Maximum output current sunk by any Port pin                       | 100mA                      |

| Maximum output current sunk by any other I/O pin                  | 25mA                       |

| Maximum output current sourced by any Port pin                    | 100mA                      |

| Maximum output current sourced by any other I/O pin               | 25mA                       |

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 3. GLOBAL DC ELECTRICAL CHARACTERISTICS

| PARAMETER                                              | CONDITIONS                                                            | MIN | TYP  | MAX | UNITS |

|--------------------------------------------------------|-----------------------------------------------------------------------|-----|------|-----|-------|

| Analog Supply Voltage                                  | (Note 1)                                                              | 2.7 | 3.0  | 3.6 | V     |

| Analog Supply Current                                  | Internal REF, ADC, DAC, Comparators all active                        |     | 1    | 2   | mA    |

| Analog Supply Current with analog sub-systems inactive | Internal REF, ADC, DAC, Comparators all disabled, oscillator disabled |     | 5    | 20  | μΑ    |

| Analog-to-Digital Supply<br>Delta (   VDD – AV+   )    |                                                                       |     |      | 0.5 | V     |

| Digital Supply Voltage                                 |                                                                       | 2.7 | 3.0  | 3.6 | V     |

| Digital Supply Current with                            | VDD = 2.7V, Clock=25MHz                                               |     | 12.5 |     | mA    |

| CPU active                                             | VDD = 2.7V, Clock=1MHz                                                |     | 0.5  |     | mA    |

|                                                        | VDD = 2.7V, Clock=32kHz                                               |     | 10   |     | μΑ    |

| Digital Supply Current                                 | Oscillator not running                                                |     | 5    |     | μΑ    |

| (shutdown)                                             |                                                                       |     |      |     |       |

| Digital Supply RAM Data<br>Retention Voltage           |                                                                       |     | 1.5  |     | V     |

| Specified Operating<br>Temperature Range               |                                                                       | -40 |      | +85 | °C    |

| SYSCLK (System Clock<br>Frequency)                     | C8051F005/6/7, C8051F015/6/7<br>(Note 2)                              | 0   |      | 25  | MHz   |

| SYSCLK (System Clock<br>Frequency)                     | C8051F000/1/2, C8051F010/1/2<br>(Note 2)                              | 0   |      | 20  | MHz   |

| Tsysl (SYSCLK Low Time)                                |                                                                       | 18  |      |     | ns    |

| Tsysh (SYSCLK High Time)                               |                                                                       | 18  |      |     | ns    |

-40°C to +85°C unless otherwise specified.

Note 1: Analog Supply AV+ must be greater than 1V for VDD monitor to operate. Note 2: SYSCLK must be at least 32 kHz to enable debugging.

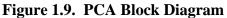

Figure 4.5. LQFP-32 Pinout Diagram

| R/W         | R/W            | R/W           | R/W           | R/W           | R/W    | R/W    | R/W    | Reset Value  |

|-------------|----------------|---------------|---------------|---------------|--------|--------|--------|--------------|

| ADCSC2      | ADCSC1         | ADCSC0        | -             | -             | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |

| Bit7        | Bit6           | Bit5          | Bit4          | Bit3          | Bit2   | Bit1   | Bit0   | SFR Address: |

|             |                |               |               |               |        |        |        | 0xBC         |

| Bits7-5. AD | CSC2-0. AL     | C SAR Conv    | version Clock | e Period Bits |        |        |        |              |

|             |                | version Clock |               |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | Conversion C  | •             |               | )      |        |        |              |

|             |                | d = 00b; Writ |               | ,             | ,<br>, |        |        |              |

|             |                | DC Internal A |               |               |        |        |        |              |

|             | ): Gain = 1    |               | 1             |               |        |        |        |              |

| 001         | : Gain = 2     |               |               |               |        |        |        |              |

| 010         | ): $Gain = 4$  |               |               |               |        |        |        |              |

| 011         | : Gain = 8     |               |               |               |        |        |        |              |

| 10x         | : Gain = 16    |               |               |               |        |        |        |              |

| 11x         | : Gain $= 0.5$ | i             |               |               |        |        |        |              |

|             |                |               |               |               |        |        |        |              |

## Figure 5.6. ADC0CF: ADC Configuration Register (C8051F00x)

33

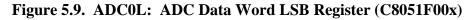

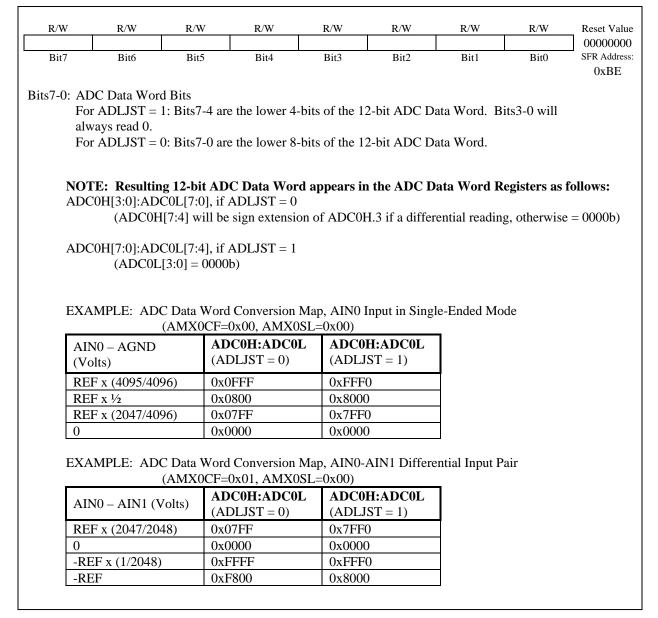

|      | Figure 3.                                                       | J. ADCU                       |      | ata woru | MOD KCg |               | JIFUUX)       |             |

|------|-----------------------------------------------------------------|-------------------------------|------|----------|---------|---------------|---------------|-------------|

| R/W  | R/W                                                             | R/W                           | R/W  | R/W      | R/W     | R/W           | R/W           | Reset Value |

|      |                                                                 |                               |      |          |         |               |               | 0000000     |

| Bit7 | Bit6                                                            | Bit5                          | Bit4 | Bit3     | Bit2    | Bit1          | Bit0          | SFR Address |

|      |                                                                 |                               |      |          |         |               |               | 0xBF        |

| Fo   | DC Data Word<br>or ADLJST = 1<br>or ADLJST = (<br>2-bit ADC Dat | 1: Upper 8-b<br>): Bits7-4 ar |      |          |         | are the upper | 4-bits of the | ;           |

### Figure 5.8. ADC0H: ADC Data Word MSB Register (C8051F00x)

| R/W          | R/W             | R/W           | R/W            | R/W                                      | R/W             | R/W            | R/W               | Reset Value |

|--------------|-----------------|---------------|----------------|------------------------------------------|-----------------|----------------|-------------------|-------------|

| ADCE         | N ADCTM         | ADCINT        | ADBUSY         | ADSTM1                                   | ADSTM0          | ADWINT         | ADLJST            | 0000000     |

| Bit7         | Bit6            | Bit5          | Bit4           | Bit3                                     | Bit2            | Bit1           | Bit0              | SFR Addres  |

|              |                 |               |                |                                          |                 |                | (bit addressable) | 0xE8        |

| Bit7:        | ADCEN: ADC      | Enable Bit    |                |                                          |                 |                |                   |             |

|              | 0: ADC Disabl   | ed. ADC is i  | n low power    | shutdown.                                |                 |                |                   |             |

|              | 1: ADC Enable   |               |                |                                          | onversions.     |                |                   |             |

| Bit6:        | ADCTM: ADC      |               |                | •                                        |                 |                |                   |             |

|              | 0: When the A   | DC is enable  | d, tracking is | always done                              | unless a con    | version is in  | process           |             |

|              | 1: Tracking De  |               |                | -                                        |                 |                | -                 |             |

|              | ADST            | M1-0:         |                |                                          |                 |                |                   |             |

|              | 00: Ti          | acking starts | with the writ  | te of 1 to AD                            | BUSY and la     | asts for 3 SA  | R clocks          |             |

|              | 01: Tı          | acking starte | d by the over  | flow of Time                             | er 3 and last f | For 3 SAR clo  | ocks              |             |

|              | 10: A           | DC tracks on  | ly when CNV    | /STR input is                            | s logic low     |                |                   |             |

|              | 11: Ti          | acking starte | d by the over  | flow of Time                             | er 2 and last f | for 3 SAR clo  | ocks              |             |

| Bit5:        | ADCINT: ADC     | C Conversion  | Complete In    | terrupt Flag                             |                 |                |                   |             |

|              | (Must be cleare |               |                |                                          |                 |                |                   |             |

|              | 0: ADC has no   |               |                |                                          | e last time thi | s flag was cl  | eared             |             |

|              | 1: ADC has co   |               | a conversion   |                                          |                 |                |                   |             |

| Bit4:        | ADBUSY: AD      | C Busy Bit    |                |                                          |                 |                |                   |             |

|              | Read            |               |                |                                          |                 |                |                   |             |

|              | 0: ADC Conve    |               |                |                                          |                 | since a reset. | The falling       |             |

|              |                 | BUSY genera   |                | ipt when ena                             | bled.           |                |                   |             |

|              | 1: ADC Busy of  | converting da | ta             |                                          |                 |                |                   |             |

|              | Write           |               |                |                                          |                 |                |                   |             |

|              | 0: No effect    |               |                |                                          |                 |                |                   |             |

|              | 1: Starts ADC   |               |                |                                          |                 |                |                   |             |

| Bits3-2:     | ADSTM1-0: A     |               |                |                                          |                 |                |                   |             |

|              | 00: ADC conv    |               |                |                                          |                 |                |                   |             |

|              | 01: ADC conv    |               |                |                                          |                 |                |                   |             |

|              | 10: ADC conv    |               |                |                                          |                 |                |                   |             |

| <b>D</b> . 4 | 11: ADC conv    |               | •              |                                          | her 2           |                |                   |             |

| Bit1:        | ADWINT: AD      |               |                | rupt Flag                                |                 |                |                   |             |

|              | (Must be cleare |               |                |                                          |                 |                |                   |             |

|              | 0: ADC Windo    |               |                |                                          | urred           |                |                   |             |

| D'/0         | 1: ADC Windo    |               |                | n occurred                               |                 |                |                   |             |

| Bit0:        | ADLJST: ADC     |               |                | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. |                 |                |                   |             |

|              | 0: Data in ADC  |               |                |                                          |                 |                |                   |             |

|              | 1: Data in ADO  | LUH:ADCUL     | Registers is   | iert justified                           |                 |                |                   |             |

|              |                 |               |                |                                          |                 |                |                   |             |

|              |                 |               |                |                                          |                 |                |                   |             |

## Figure 6.7. ADC0CN: ADC Control Register (C8051F01x)

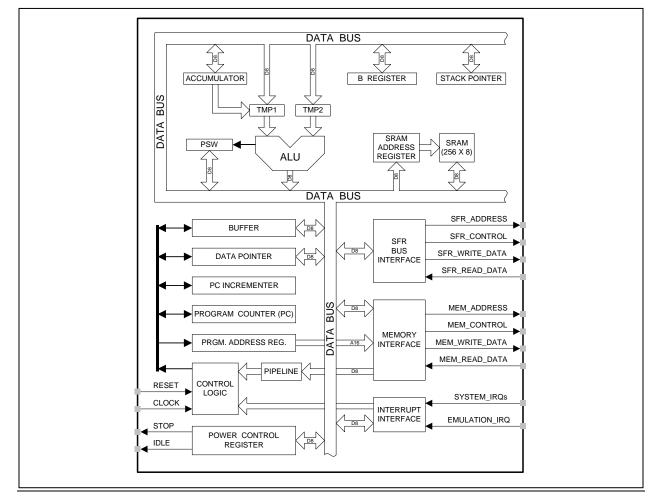

## 10. CIP-51 CPU

The MCUs' system CPU is the CIP-51. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set. Standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are four 16-bit counter/timers (see description in Section 19), a full-duplex UART (see description in Section 18), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (see Section 10.3), and four byte-wide I/O Ports (see description in Section 14). The CIP-51 also includes on-chip debug hardware (see description in Section 21), and interfaces directly with the MCUs' analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

#### Features

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 10.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25MHz Clock

- 0 to 25MHz Clock Frequency (on 'F0x5/6/7)

- Four Byte-Wide I/O Ports

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Circuitry

- Program and Data Memory Security

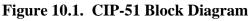

Figure 10.2. Memory Map

### 10.2.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

The MCUs also have built-in hardware for a stack record. The stack record is a 32-bit shift register, where each Push or increment SP pushes one record bit onto the register, and each Call or interrupt pushes two record bits onto the register. (A Pop or decrement SP pops one record bit, and a Return pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the Stack, and can notify the debug software even with the MCU running full-speed debug.

| Address | Register | Description                                | Page No.  |

|---------|----------|--------------------------------------------|-----------|

| 0xC7    | ADC0LTH  | ADC Less-Than Data Word (High Byte)        | 36*, 47** |

| 0xC6    | ADC0LTL  | ADC Less-Than Data Word (Low Byte)         | 36*, 47** |

| 0xBA    | AMX0CF   | ADC MUX Configuration                      | 31*, 42** |

| 0xBB    | AMX0SL   | ADC MUX Channel Selection                  | 32*, 43** |

| 0xF0    | В        | B Register                                 | 76        |

| 0x8E    | CKCON    | Clock Control                              | 144       |

| 0x9E    | CPT0CN   | Comparator 0 Control                       | 56        |

| 0x9F    | CPT1CN   | Comparator 1 Control                       | 58        |

| 0xD4    | DAC0CN   | DAC 0 Control                              | 52        |

| 0xD3    | DAC0H    | DAC 0 Data Word (High Byte)                | 52        |

| 0xD2    | DAC0L    | DAC 0 Data Word (Low Byte)                 | 52        |

| 0xD7    | DAC1CN   | DAC 1 Control                              | 53        |

| 0xD6    | DAC1H    | DAC 1 Data Word (High Byte)                | 53        |

| 0xD5    | DAC1L    | DAC 1 Data Word (Low Byte)                 | 53        |

| 0x83    | DPH      | Data Pointer (High Byte)                   | 74        |

| 0x82    | DPL      | Data Pointer (Low Byte)                    | 74        |

| 0xE6    | EIE1     | Extended Interrupt Enable 1                | 81        |

| 0xE7    | EIE2     | Extended Interrupt Enable 2                | 82        |

| 0xF6    | EIP1     | External Interrupt Priority 1              | 83        |

| 0xF7    | EIP2     | External Interrupt Priority 2              | 84        |

| 0xAF    | EMI0CN   | External Memory Interface Control          | 92***     |

| 0xB7    | FLACL    | Flash Access Limit                         | 90***     |

| 0xB6    | FLSCL    | Flash Memory Timing Prescaler              | 91        |

| 0xA8    | IE       | Interrupt Enable                           | 79        |

| 0xB8    | IP       | Interrupt Priority Control                 | 80        |

| 0xB2    | OSCICN   | Internal Oscillator Control                | 100       |

| 0xB1    | OSCXCN   | External Oscillator Control                | 101       |

| 0x80    | P0       | Port 0 Latch                               | 109       |

| 0x90    | P1       | Port 1 Latch                               | 110       |

| 0xA0    | P2       | Port 2 Latch                               | 111       |

| 0xB0    | P3       | Port 3 Latch                               | 112       |

| 0xD8    | PCA0CN   | Programmable Counter Array 0 Control       | 160       |

| 0xFA    | PCA0CPH0 | PCA Capture Module 0 Data Word (High Byte) | 163       |

| 0xFB    | PCA0CPH1 | PCA Capture Module 1 Data Word (High Byte) | 163       |

| 0xFC    | PCA0CPH2 | PCA Capture Module 2 Data Word (High Byte) | 163       |

| 0xFD    | PCA0CPH3 | PCA Capture Module 3 Data Word (High Byte) | 163       |

| 0xFE    | PCA0CPH4 | PCA Capture Module 4 Data Word (High Byte) | 163       |

| 0xEA    | PCA0CPL0 | PCA Capture Module 0 Data Word (Low Byte)  | 163       |

| 0xEB    | PCA0CPL1 | PCA Capture Module 1 Data Word (Low Byte)  | 163       |

| 0xEC    | PCA0CPL2 | PCA Capture Module 2 Data Word (Low Byte)  | 163       |

| 0xED    | PCA0CPL3 | PCA Capture Module 3 Data Word (Low Byte)  | 163       |

| Figure 10.6. | <b>PSW: Program</b> | n Status Word |

|--------------|---------------------|---------------|

|--------------|---------------------|---------------|

| CY      | R/W                                                                               | R/W                                                                                                           | R/W                                                                       | R/W                                                             | R/W                                                | R/W                    | R/W                       | Reset Valu         |

|---------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|------------------------|---------------------------|--------------------|

|         | AC                                                                                | F0                                                                                                            | RS1                                                                       | RS0                                                             | OV                                                 | F1                     | PARITY                    | 0000000            |

| Bit7    | Bit6                                                                              | Bit5                                                                                                          | Bit4                                                                      | Bit3                                                            | Bit2                                               | Bit1                   | Bit0<br>(bit addressable) | SFR Addres<br>0xD0 |

| Bit7:   | CY: Carry Fla<br>This bit is set<br>(subtraction).                                | when the las                                                                                                  |                                                                           |                                                                 |                                                    | (addition) o           | or a borrow               |                    |

| Bit6:   | AC: Auxiliary<br>This bit is set<br>borrow from (<br>operations.                  | when the las                                                                                                  |                                                                           |                                                                 |                                                    |                        |                           |                    |

| Bit5:   | F0: User Flag<br>This is a bit-ad                                                 |                                                                                                               | eneral purpo                                                              | se flag for us                                                  | e under softw                                      | are control            |                           |                    |

| Bits4-3 | RS1-RS0: Reg<br>These bits sele                                                   |                                                                                                               |                                                                           | used during                                                     | register acces                                     | ses.                   |                           |                    |

|         | RS1 RS                                                                            | 0 Registe                                                                                                     | er Bank                                                                   | Address                                                         |                                                    |                        |                           |                    |

|         | 0 0                                                                               |                                                                                                               |                                                                           | x00-0x07                                                        |                                                    |                        |                           |                    |

|         | 0 1                                                                               |                                                                                                               |                                                                           | x08-0x0F                                                        |                                                    |                        |                           |                    |

|         | 1 0                                                                               |                                                                                                               | 2 0                                                                       | x10-0x17                                                        |                                                    |                        |                           |                    |

|         | 1 1                                                                               | ,                                                                                                             | 3 0                                                                       | x18-0x1F                                                        |                                                    |                        |                           |                    |

| Bit2:   | <ul> <li>A MUL i</li> <li>A DIV in</li> <li>The OV bit is other cases.</li> </ul> | Rn, A" instr<br>7 Flag.<br>to 1 under th<br>, ADDC, or 5<br>nstruction re<br>istruction cau<br>6 cleared to 0 | uction.<br>e following o<br>SUBB instru<br>sults in an o<br>ises a divide | circumstance:<br>ction causes<br>verflow (resu<br>-by-zero conc | s:<br>a sign-change<br>lt is greater th<br>lition. | overflow.<br>an 255) . |                           |                    |

| Bit1:   | F1: User Flag<br>This is a bit-a                                                  |                                                                                                               | eneral purpo                                                              | se flag for us                                                  | e under softw                                      | are control            |                           |                    |

|         | DADITV. Dor                                                                       | ity Flag.                                                                                                     |                                                                           |                                                                 |                                                    |                        |                           |                    |

|       | R/W                                                                  | R/W                            | R/W                           | R/W          | R/W           | R/W          | R/W  | Reset Valu         |

|-------|----------------------------------------------------------------------|--------------------------------|-------------------------------|--------------|---------------|--------------|------|--------------------|

| EXVLD |                                                                      | EX7                            | EX6                           | EX5          | EX4           | EADC0        | ET3  | 0000000            |

| Bit7  | Bit6                                                                 | Bit5                           | Bit4                          | Bit3         | Bit2          | Bit1         | Bit0 | SFR Addres<br>0xE7 |

| Bit7: | EXVLD: Enal<br>This bit sets th<br>0: Disable all<br>1: Enable inte  | ne masking o<br>XTLVLD ir      | f the XTLVL<br>iterrupts.     | D interrupt. |               | -            |      |                    |

| Bit6: | Reserved. Mu                                                         |                                | •                             |              | LD Hug (Or    |              |      |                    |

| Dito. | Reserved. Int                                                        |                                | iteaus 0.                     |              |               |              |      |                    |

| Bit5: | EX7: Enable F<br>This bit sets th<br>0: Disable Ex<br>1: Enable inte | ne masking o<br>ternal Interru | f External Int<br>1pt 7.      | -            | al Interrupt  | 7 input pin. |      |                    |

| Bit4: | EX6: Enable I<br>This bit sets th<br>0: Disable Ex<br>1: Enable inte | ne masking o<br>ternal Interru | f External Int<br>1pt 6.      | -            | al Interrupt  | 6 input pin. |      |                    |

| Bit3: | EX5: Enable I<br>This bit sets th<br>0: Disable Ex<br>1: Enable inte | ne masking o<br>ternal Interru | f External Int<br>pt 5.       | 1            | al Interrupt  | 5 input pin. |      |                    |

| Bit2: | EX4: Enable I<br>This bit sets th<br>0: Disable Ex<br>1: Enable inte | ne masking o<br>ternal Interru | f External Int<br>1pt 4.      | -            | al Interrupt  | 4 input pin. |      |                    |

| Bit1: | EADC0: Enab<br>This bit sets th<br>0: Disable AI<br>1: Enable inte   | ne masking o<br>DC0 Convers    | f the ADC0 I<br>ion Interrupt | End of Conv  | ersion Interr | -            |      |                    |

| Bit0: | ET3: Enable T<br>This bit sets th                                    | ne masking o<br>Timer 3 inte   | f the Timer 3 rrupts.         | -            | ag (TMR3C     |              |      |                    |

## Figure 10.12. EIE2: Extended Interrupt Enable 2

### **11.2.** Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX instruction and read using the MOVC instruction.

The MCU incorporates an additional 128-byte sector of Flash memory located at 0x8000 – 0x807F. This sector can be used for program code or data storage. However, its smaller sector size makes it particularly well suited as general purpose, non-volatile scratchpad memory. Even though Flash memory can be written a single byte at a time, an entire sector must be erased first. In order to change a single byte of a multi-byte data set, the data must be moved to temporary storage. Next, the sector is erased, the data set updated and the data set returned to the original sector. The 128-byte sector-size facilitates updating data without wasting program memory space by allowing the use of internal data RAM for temporary storage. (A normal 512-byte sector is too large to be stored in the 256-byte internal data memory.)

### **11.3.** Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as prevent the viewing of proprietary program code and constants. The Program Store Write Enable (PSCTL.0) and the Program Store Erase Enable (PSCTL.1) bits protect the Flash memory from accidental modification by software. These bits must be explicitly set to logic 1 before software can modify the Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the JTAG interface or by software running on the system controller.

A set of security lock bytes stored at 0x7DFE and 0x7DFF protect the Flash program memory from being read or altered across the JTAG interface. Each bit in a security lock-byte protects one 4kbyte block of memory. Clearing a bit to logic 0 in a Read lock byte prevents the corresponding block of Flash memory from being read across the JTAG interface. Clearing a bit in the Write/Erase lock byte protects the block from JTAG erasures and/or writes. The Read lock byte is at location 0x7DFF. The Write/Erase lock byte is located at 0x7DFE. Figure 11.2 shows the location and bit definitions of the security bytes. The 512-byte sector containing the lock bytes can be written to, but not erased by software. Writing to the reserved area should not be performed.

| Figure 11.1. | <b>PSCTL:</b> | Program | Store     | RW | Control   |

|--------------|---------------|---------|-----------|----|-----------|

|              |               |         | ~ • • • • |    | 001101 01 |

| R/W     | R/W              | R/W            | R/W             | R/W             | R/W            | R/W            | R/W        | Reset Value |

|---------|------------------|----------------|-----------------|-----------------|----------------|----------------|------------|-------------|

| -       | -                | -              | -               | -               | -              | PSEE           | PSWE       | 00000000    |

| Bit7    | Bit6             | Bit5           | Bit4            | Bit3            | Bit2           | Bit1           | Bit0       | SFR Address |

|         |                  |                |                 |                 |                |                |            |             |

| Bits7-2 | : UNUSED. Re     | ead = 000000   | 0b, Write = de  | on't care.      |                |                |            |             |

| Bit1:   | PSEE: Program    | n Store Eras   | e Enable.       |                 |                |                |            |             |

|         | Setting this bit | allows an e    | ntire page of   | the Flash pro   | gram memor     | y to be erased | d provided |             |

|         | the PSWE bit     | is also set. A | After setting t | his bit, a writ | te to Flash me | emory using    | the MOVX   |             |

|         | instruction wil  |                |                 |                 |                | dressed by the | e MOVX     |             |

|         | instruction. The |                |                 |                 | not matter.    |                |            |             |

|         | 0: Flash progra  |                |                 |                 |                |                |            |             |

|         | 1: Flash progra  | am memory      | erasure enabl   | ed.             |                |                |            |             |

| Bit0:   | PSWE: Progra     |                |                 |                 |                |                |            |             |

|         | Setting this bit |                | •••             |                 |                | •              | ng the     |             |

|         | MOVX instruc     |                |                 |                 | ore writing d  | lata.          |            |             |

|         | 0: Write to Fla  |                |                 |                 |                |                |            |             |

|         | 1: Write to Fla  | ish program    | memory enab     | oled.           |                |                |            |             |

|         |                  |                |                 |                 |                |                |            |             |

|         |                  |                |                 |                 |                |                |            |             |

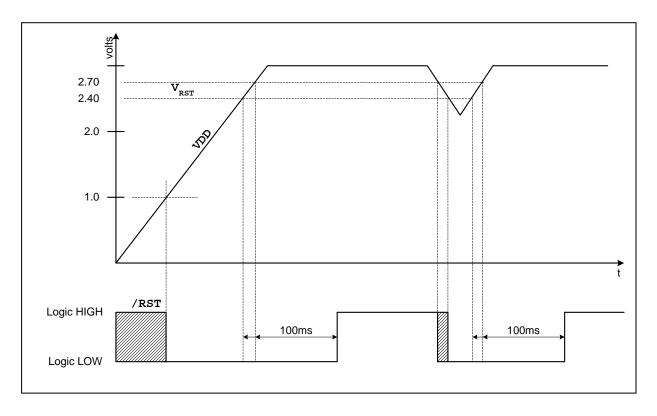

## **13.1.** Power-on Reset

The C8051F000 family incorporates a power supply monitor that holds the MCU in the reset state until VDD rises above the  $V_{RST}$  level during power-up. (See Figure 13.2 for timing diagram, and refer to Table 13.1 for the Electrical Characteristics of the power supply monitor circuit.) The /RST pin is asserted (low) until the end of the 100ms VDD Monitor timeout in order to allow the VDD supply to become stable.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. All of the other reset flags in the RSTSRC Register are indeterminate. PORSF is cleared by a reset from any other source. Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset.

### **13.2.** Software Forced Reset

Writing a 1 to the PORSF bit forces a Power-On Reset as described in Section 13.1.

## Figure 13.2. VDD Monitor Timing Diagram

## 13.3. Power-fail Reset

When a power-down transition or power irregularity causes VDD to drop below  $V_{RST}$ , the power supply monitor will drive the /RST pin low and return the CIP-51 to the reset state (see Figure 13.2). When VDD returns to a level above  $V_{RST}$ , the CIP-51 will leave the reset state in the same manner as that for the power-on reset. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if VDD dropped below the level required for data retention. If the PORSF flag is set, the data may no longer be valid.