Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 32                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x12b; D/A 2x12b                                            |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f005-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE OF CONTENTS

| 1. | SYSTEM OVERVIEW                                                            | . 8 |

|----|----------------------------------------------------------------------------|-----|

|    | Table 1.1. Product Selection Guide                                         | 8   |

|    | Figure 1.1. C8051F000/05/10/15 Block Diagram                               | 9   |

|    | Figure 1.2. C8051F001/06/11/16 Block Diagram                               |     |

|    | Figure 1.3. C8051F002/07/12/17 Block Diagram                               |     |

|    | 1.1. CIP-51 <sup>™</sup> CPU                                               |     |

|    | Figure 1.4. Comparison of Peak MCU Execution Speeds                        | 12  |

|    | Figure 1.5. On-Board Clock and Reset                                       | 13  |

|    | 1.2. On-Board Memory                                                       | 14  |

|    | Figure 1.6. On-Board Memory Map                                            | 14  |

|    | 1.3. JTAG Debug and Boundary Scan                                          |     |

|    | Figure 1.7. Debug Environment Diagram                                      |     |

|    | 1.4. Programmable Digital I/O and Crossbar                                 | 16  |

|    | Figure 1.8. Digital Crossbar Diagram                                       | 16  |

|    | 1.5. Programmable Counter Array                                            | 17  |

|    | Figure 1.9. PCA Block Diagram                                              |     |

|    | 1.6. Serial Ports                                                          |     |

|    | 1.7. Analog to Digital Converter                                           | 18  |

|    | Figure 1.10. ADC Diagram                                                   |     |

|    | 1.8. Comparators and DACs                                                  |     |

|    | Figure 1.11. Comparator and DAC Diagram                                    |     |

| 2. | ABSOLUTE MAXIMUM RATINGS*                                                  |     |

| 3. | GLOBAL DC ELECTRICAL CHARACTERISTICS                                       | 20  |

| 4. | PINOUT AND PACKAGE DEFINITIONS                                             |     |

|    | Table 4.1. Pin Definitions                                                 |     |

|    | Figure 4.1. TQFP-64 Pinout Diagram                                         |     |

|    | Figure 4.2. TQFP-64 Package Drawing                                        |     |

|    | Figure 4.3. TQFP-48 Pinout Diagram                                         |     |

|    | Figure 4.4. TQFP-48 Package Drawing                                        |     |

|    | Figure 4.5. LQFP-32 Pinout Diagram                                         |     |

|    | Figure 4.6. LQFP-32 Package Drawing                                        |     |

| 5. | ADC (12-Bit, C8051F000/1/2/5/6/7 Only)                                     |     |

|    | Figure 5.1. 12-Bit ADC Functional Block Diagram.                           |     |

|    | 5.1. Analog Multiplexer and PGA                                            |     |

|    | 5.2. ADC Modes of Operation                                                |     |

|    | Figure 5.2. 12-Bit ADC Track and Conversion Example Timing                 |     |

|    | Figure 5.3. Temperature Sensor Transfer Function                           | 31  |

|    | Figure 5.4. AMX0CF: AMUX Configuration Register (C8051F00x)                | 31  |

|    | Figure 5.5. AMX0SL: AMUX Channel Select Register (C8051F00x)               | 32  |

|    | Figure 5.6. ADC0CF: ADC Configuration Register (C8051F00x)                 | 33  |

|    | Figure 5.7. ADC0CN: ADC Control Register (C8051F00x)                       | 34  |

|    | Figure 5.8. ADC0H: ADC Data Word MSB Register (C8051F00x)                  |     |

|    | Figure 5.9. ADC0L: ADC Data Word LSB Register (C8051F00x)                  |     |

|    | 5.3. ADC Programmable Window Detector                                      |     |

|    | Figure 5.10. ADC0GTH: ADC Greater-Than Data High Byte Register (C8051F00x) |     |

|    | Figure 5.11. ADC0GTL: ADC Greater-Than Data Low Byte Register (C8051F00x)  |     |

|    | Figure 5.12. ADC0LTH: ADC Less-Than Data High Byte Register (C8051F00x)    |     |

|    | Figure 5.13. ADC0LTL: ADC Less-Than Data Low Byte Register (C8051F00x)     |     |

|    | Figure 5.14. 12-Bit ADC Window Interrupt Examples, Right Justified Data    |     |

|    | Figure 5.15. 12-Bit ADC Window Interrupt Examples, Left Justified Data     |     |

|    | Figure 5.15. 12-Bit ADC Window Interrupt Examples, Left Justified Data     | 38  |

|     | Table 18.2. Oscillator Frequencies for Standard Baud Rates                             |  |

|-----|----------------------------------------------------------------------------------------|--|

|     | Figure 18.8. SBUF: Serial (UART) Data Buffer Register                                  |  |

|     | Figure 18.9. SCON: Serial Port Control Register                                        |  |

| 19. | TIMERS                                                                                 |  |

|     | 19.1. Timer 0 and Timer 1                                                              |  |

|     | Figure 19.1. T0 Mode 0 Block Diagram.                                                  |  |

|     | Figure 19.2. T0 Mode 2 Block Diagram.                                                  |  |

|     | Figure 19.3. T0 Mode 3 Block Diagram.                                                  |  |

|     | Figure 19.4. TCON: Timer Control Register                                              |  |

|     | Figure 19.5. TMOD: Timer Mode Register                                                 |  |

|     | Figure 19.6. CKCON: Clock Control Register                                             |  |

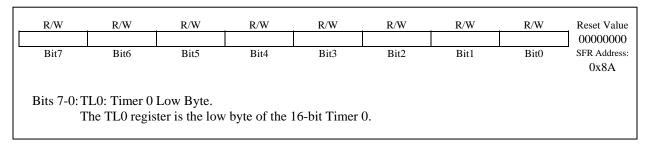

|     | Figure 19.7. TLO: Timer 0 Low Byte                                                     |  |

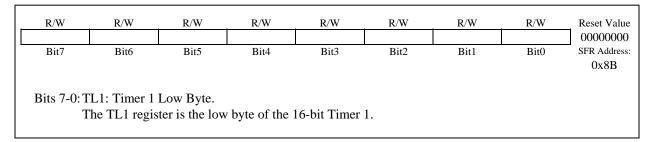

|     | Figure 19.8. TL1: Timer 1 Low Byte                                                     |  |

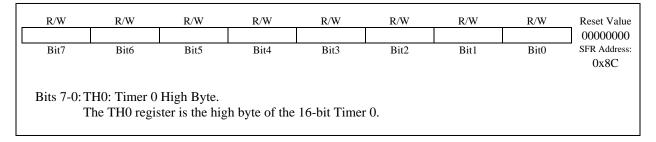

|     | Figure 19.9. THO: Timer 0 High Byte                                                    |  |

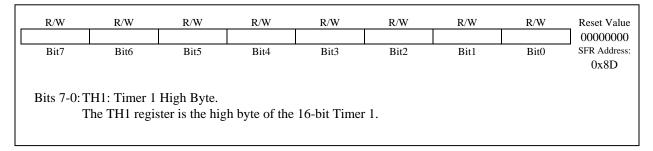

|     | Figure 19.10. TH1: Timer 1 High Byte                                                   |  |

|     | 19.2. Timer 2                                                                          |  |

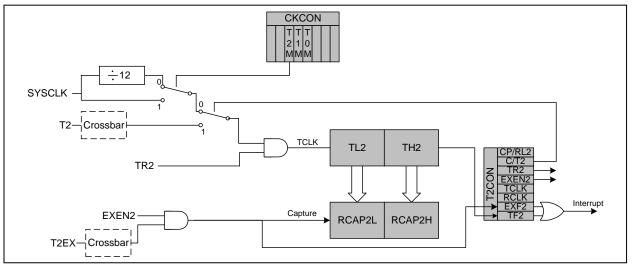

|     | Figure 19.11. T2 Mode 0 Block Diagram                                                  |  |

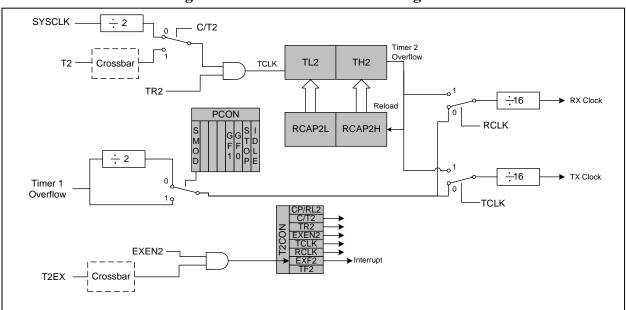

|     | Figure 19.12. T2 Mode 1 Block Diagram.                                                 |  |

|     | Figure 19.13. T2 Mode 2 Block Diagram.                                                 |  |

|     | Figure 19.14. T2CON: Timer 2 Control Register                                          |  |

|     | Figure 19.15. RCAP2L: Timer 2 Capture Register Low Byte                                |  |

|     | Figure 19.16. RCAP2H: Timer 2 Capture Register High Byte                               |  |

|     | Figure 19.17. TL2: Timer 2 Low Byte                                                    |  |

|     | Figure 19.18. TH2: Timer 2 High Byte                                                   |  |

|     | 19.3. Timer 3                                                                          |  |

|     | Figure 19.19. Timer 3 Block Diagram                                                    |  |

|     | Figure 19.20. TMR3CN: Timer 3 Control Register                                         |  |

|     | Figure 19.21. TMR3RLL: Timer 3 Reload Register Low Byte                                |  |

|     | Figure 19.22. TMR3RLH: Timer 3 Reload Register High Byte                               |  |

|     | Figure 19.22. TMR3REIT. Timer 3 Keroad Register High Byte                              |  |

|     | Figure 19.24. TMR3H: Timer 3 High Byte                                                 |  |

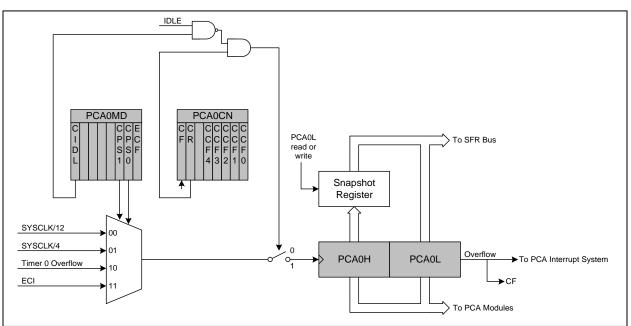

| 20  | PROGRAMMABLE COUNTER ARRAY                                                             |  |

| 20. |                                                                                        |  |

|     | Figure 20.1. PCA Block Diagram                                                         |  |

|     | 20.1. Capture/Compare Modules                                                          |  |

|     | Table 20.1. PCA0CPM Register Settings for PCA Capture/Compare Modules                  |  |

|     | Figure 20.2. PCA Interrupt Block Diagram.                                              |  |

|     | Figure 20.3. PCA Capture Mode Diagram                                                  |  |

|     | Figure 20.4. PCA Software Timer Mode Diagram.                                          |  |

|     | Figure 20.5. PCA High Speed Output Mode Diagram                                        |  |

|     | Figure 20.6. PCA PWM Mode Diagram                                                      |  |

|     | 20.2. PCA Counter/Timer                                                                |  |

|     | Table 20.2.     PCA Timebase Input Options.       Fine     20.7       PCA Construction |  |

|     | Figure 20.7. PCA Counter/Timer Block Diagram                                           |  |

|     | 20.3. Register Descriptions for PCA                                                    |  |

|     | Figure 20.8. PCA0CN: PCA Control Register                                              |  |

|     | Figure 20.9. PCA0MD: PCA Mode Register                                                 |  |

|     | Figure 20.10. PCA0CPMn: PCA Capture/Compare Registers                                  |  |

|     | Figure 20.11. PCA0L: PCA Counter/Timer Low Byte                                        |  |

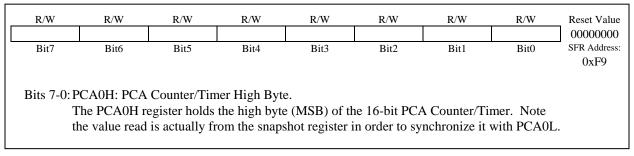

|     | Figure 20.12. PCA0H: PCA Counter/Timer High Byte                                       |  |

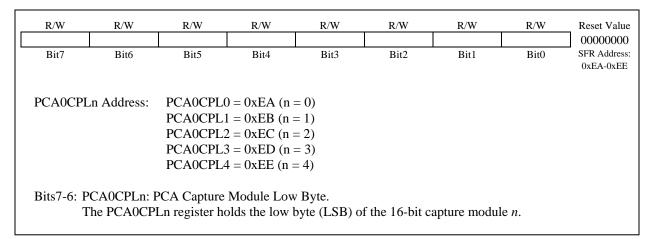

|     | Figure 20.13. PCA0CPLn: PCA Capture Module Low Byte                                    |  |

|     | Figure 20.14. PCA0CPHn: PCA Capture Module High Byte                                   |  |

| 21. | JTAG (IEEE 1149.1)                                                                     |  |

|     | Figure 21.1. IR: JTAG Instruction Register                                             |  |

|     | 21.1. Boundary Scan                                                                    |  |

Figure 1.1. C8051F000/05/10/15 Block Diagram

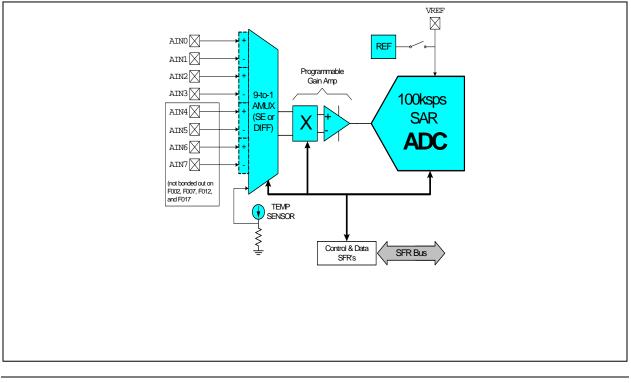

#### **1.7.** Analog to Digital Converter

The C8051F000/1/2/5/6/7 has an on-chip 12-bit SAR ADC with a 9-channel input multiplexer and programmable gain amplifier. With a maximum throughput of 100ksps, the ADC offers true 12-bit accuracy with an INL of  $\pm$ 1LSB. The ADC in the C8051F010/1/2/5/6/7 is similar, but with 10-bit resolution. Each ADC has a maximum throughput of 100ksps. Each ADC has an INL of  $\pm$ 1LSB, offering true 12-bit accuracy with the C8051F00x, and true 10-bit accuracy with the C8051F01x. There is also an on-board 15ppm voltage reference, or an external reference may be used via the VREF pin.

The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. One input channel is tied to an internal temperature sensor, while the other eight channels are available externally. Each pair of the eight external input channels can be configured as either two single-ended inputs or a single differential input. The system controller can also put the ADC into shutdown to save power.

A programmable gain amplifier follows the analog multiplexer. The gain can be set in software from 0.5 to 16 in powers of 2. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset (in differential mode, a DAC could be used to provide the DC offset).

Conversions can be started in four ways; a software command, an overflow on Timer 2, an overflow on Timer 3, or an external signal input. This flexibility allows the start of conversion to be triggered by software events, external HW signals, or convert continuously. A completed conversion causes an interrupt, or a status bit can be polled in software to determine the end of conversion. The resulting 10 or 12-bit data word is latched into two SFRs upon completion of a conversion. The data can be right or left justified in these registers under software control.

Compare registers for the ADC data can be configured to interrupt the controller when ADC data is within a specified window. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within the specified window.

#### Figure 1.10. ADC Diagram

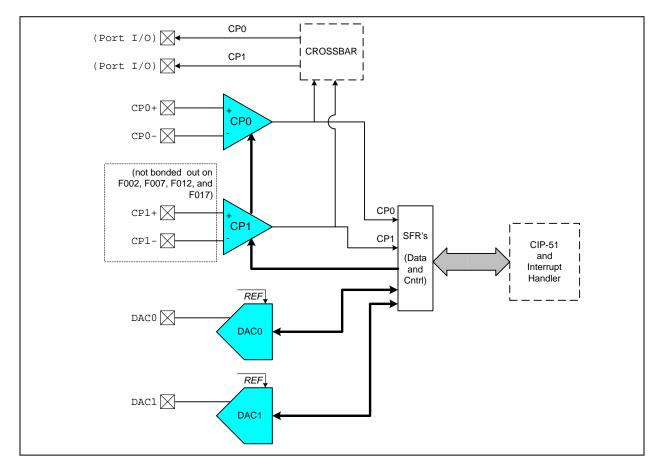

#### **1.8.** Comparators and DACs

The C8051F000 MCU Family has two 12-bit DACs and two comparators on chip (the second comparator, CP1, is not bonded out on the F002, F007, F012, and F017). The MCU data and control interface to each comparator and DAC is via the Special Function Registers. The MCU can place any DAC or comparator in low power shutdown mode.

The comparators have software programmable hysteresis. Each comparator can generate an interrupt on its rising edge, falling edge, or both. The comparators' output state can also be polled in software. These interrupts are capable of waking up the MCU from idle mode. The comparator outputs can be programmed to appear on the Port I/O pins via the Crossbar.

The DACs are voltage output mode and use the same voltage reference as the ADC. They are especially useful as references for the comparators or offsets for the differential inputs of the ADC.

Figure 1.11. Comparator and DAC Diagram

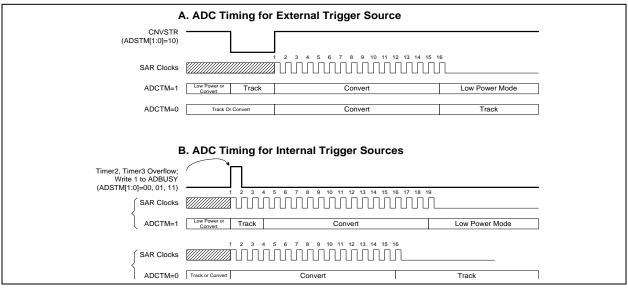

#### **5.2. ADC** Modes of Operation

The ADC uses VREF to determine its full-scale voltage, thus the reference must be properly configured before performing a conversion (see Section 9). The ADC has a maximum conversion speed of 100ksps. The ADC conversion clock is derived from the system clock. Conversion clock speed can be reduced by a factor of 2, 4, 8 or 16 via the ADCSC bits in the ADC0CF Register. This is useful to adjust conversion speed to accommodate different system clock speeds.

A conversion can be initiated in one of four ways, depending on the programmed states of the ADC Start of Conversion Mode bits (ADSTM1, ADSTM0) in ADC0CN. Conversions may be initiated by:

- 1. Writing a 1 to the ADBUSY bit of ADC0CN;

- 2. A Timer 3 overflow (i.e. timed continuous conversions);

- 3. A rising edge detected on the external ADC convert start signal, CNVSTR;

- 4. A Timer 2 overflow (i.e. timed continuous conversions).

Writing a 1 to ADBUSY provides software control of the ADC whereby conversions are performed "on-demand". During conversion, the ADBUSY bit is set to 1 and restored to 0 when conversion is complete. The falling edge of ADBUSY triggers an interrupt (when enabled) and sets the ADCINT interrupt flag. Note: When conversions are performed "on-demand", the ADCINT flag, not ADBUSY, should be polled to determine when the conversion has completed. Converted data is available in the ADC data word MSB and LSB registers, ADCOH, ADCOL. Converted data can be either left or right justified in the ADCOH:ADCOL register pair (see example in Figure 5.9) depending on the programmed state of the ADLJST bit in the ADCOCN register.

The ADCTM bit in register ADC0CN controls the ADC track-and-hold mode. In its default state, the ADC input is continuously tracked, except when a conversion is in progress. Setting ADCTM to 1 allows one of four different low power track-and-hold modes to be specified by states of the ADSTM1-0 bits (also in ADC0CN):

- 1. Tracking begins with a write of 1 to ADBUSY and lasts for 3 SAR clocks;

- 2. Tracking starts with an overflow of Timer 3 and lasts for 3 SAR clocks;

- 3. Tracking is active only when the CNVSTR input is low;

- 4. Tracking starts with an overflow of Timer 2 and lasts for 3 SAR clocks.

Modes 1, 2 and 4 (above) are useful when the start of conversion is triggered with a software command or when the ADC is operated continuously. Mode 3 is used when the start of conversion is triggered by external hardware. In this case, the track-and-hold is in its low power mode at times when the CNVSTR input is high. Tracking can also be disabled (shutdown) when the entire chip is in low power standby or sleep modes.

#### Figure 5.2. 12-Bit ADC Track and Conversion Example Timing

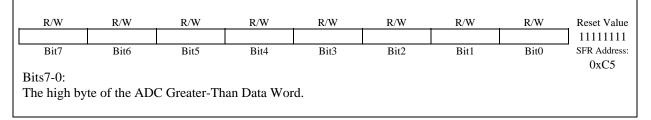

#### 5.3. ADC Programmable Window Detector

The ADC programmable window detector is very useful in many applications. It continuously compares the ADC output to user-programmed limits and notifies the system when an out-of-band condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (ADWINT in ADCOCN) can also be used in polled mode. The high and low bytes of the reference words are loaded into the ADC Greater-Than and ADC Less-Than registers (ADC0GTH, ADC0GTL, ADC0LTH, and ADC0LTL). Figure 5.14 and Figure 5.15 show example comparisons for reference. Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADC0GTx and ADC0LTx registers.

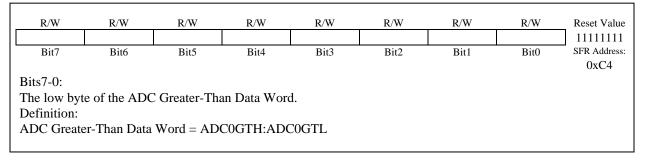

#### Figure 5.10. ADC0GTH: ADC Greater-Than Data High Byte Register (C8051F00x)

#### Figure 5.11. ADC0GTL: ADC Greater-Than Data Low Byte Register (C8051F00x)

#### Figure 5.12. ADC0LTH: ADC Less-Than Data High Byte Register (C8051F00x)

| R/W                             | R/W                  | R/W                 | R/W                | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000000 |

|---------------------------------|----------------------|---------------------|--------------------|------|------|------|------|-------------------------|

| Bit7<br>Bits7-0:<br>The high by | Bit6<br>te of the AD | Bit5<br>C Less-Than | Bit4<br>Data Word. | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xC7    |

#### Figure 5.13. ADC0LTL: ADC Less-Than Data Low Byte Register (C8051F00x)

| R/W         | R/W                          | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000000 |

|-------------|------------------------------|------|------|------|------|------|------|-------------------------|

| Bit7        | Bit6                         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xC6    |

| Definition: | re the low by<br>Гhan Data W |      |      |      |      |      |      |                         |

| R/W     | R                                                                                  | R/W             | R/W          | R/W                   | R/W        | R/W          | R/W     | Reset Valu  |  |  |  |

|---------|------------------------------------------------------------------------------------|-----------------|--------------|-----------------------|------------|--------------|---------|-------------|--|--|--|

| CP1EN   | CP1OUT                                                                             | CP1RIF          | CP1FIF       | CP1HYP1               | CP1HYP0    | CP1HYN1      | CP1HYN0 | 00000000    |  |  |  |

| Bit7    | Bit6                                                                               | Bit5            | Bit4         | Bit3                  | Bit2       | Bit1         | Bit0    | SFR Address |  |  |  |

|         |                                                                                    |                 |              |                       |            |              |         | 0x9F        |  |  |  |

| Bit7:   | CP1EN: Com                                                                         |                 |              |                       |            |              |         |             |  |  |  |

|         | 0: Comparato                                                                       |                 |              |                       |            |              |         |             |  |  |  |

|         | 1: Comparato                                                                       |                 |              |                       |            |              |         |             |  |  |  |

| Bit6:   | CP1OUT: Con                                                                        |                 |              | Flag                  |            |              |         |             |  |  |  |

|         | 0: Voltage on                                                                      |                 |              |                       |            |              |         |             |  |  |  |

|         | 1: Voltage on                                                                      |                 |              |                       |            |              |         |             |  |  |  |

| Bit5:   | CP1RIF: Com                                                                        |                 |              |                       |            |              |         |             |  |  |  |

|         | 0: No Comparator 1 Rising-Edge Interrupt has occurred since this flag was cleared  |                 |              |                       |            |              |         |             |  |  |  |

|         | 1: Comparator 1 Rising-Edge Interrupt has occurred since this flag was cleared     |                 |              |                       |            |              |         |             |  |  |  |

| Bit4:   | CP1FIF: Com                                                                        |                 |              |                       |            |              |         |             |  |  |  |

|         | 0: No Comparator 1 Falling-Edge Interrupt has occurred since this flag was cleared |                 |              |                       |            |              |         |             |  |  |  |

|         | 1: Comparato                                                                       |                 |              |                       |            | ag was clear | ed      |             |  |  |  |

| Bit3-2: | CP1HYP1-0:                                                                         |                 |              | ysteresis Cont        | rol Bits   |              |         |             |  |  |  |

|         | 00: Positive H                                                                     | Iysteresis Di   | sabled       |                       |            |              |         |             |  |  |  |

|         | 01: Positive H                                                                     | Iysteresis = 2  | 2mV          |                       |            |              |         |             |  |  |  |

|         | 10: Positive H                                                                     | Iysteresis = 4  | 4mV          |                       |            |              |         |             |  |  |  |

|         | 11: Positive H                                                                     |                 |              |                       |            |              |         |             |  |  |  |

| Bit1-0: | CP1HYN1-0:                                                                         | Comparator      | 1 Negative H | <b>Iysteresis</b> Con | ntrol Bits |              |         |             |  |  |  |

|         | 00: Negative Hysteresis Disabled                                                   |                 |              |                       |            |              |         |             |  |  |  |

|         | 01: Negative                                                                       | Hysteresis =    | 2mV          |                       |            |              |         |             |  |  |  |

|         | 10: Negative                                                                       | Hysteresis =    | 4mV          |                       |            |              |         |             |  |  |  |

|         | 11: Negative                                                                       | I Internation - | 10mV         |                       |            |              |         |             |  |  |  |

### Figure 8.4. CPT1CN: Comparator 1 Control Register

### Figure 10.10. IP: Interrupt Priority

| -<br>D:47 |                                                                                                                                                                                                                                                  | R/W                                              | R/W                                            | R/W                                   | R/W        | R/W  | R/W                       | Reset Value         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------|---------------------------------------|------------|------|---------------------------|---------------------|

| D:47      | -                                                                                                                                                                                                                                                | PT2                                              | PS                                             | PT1                                   | PX1        | PT0  | PX0                       | 0000000             |

| Bit7      | Bit6                                                                                                                                                                                                                                             | Bit5                                             | Bit4                                           | Bit3                                  | Bit2       | Bit1 | Bit0<br>(bit addressable) | SFR Address<br>0xB8 |

| Bit5:     | UNUSED. Re<br>PT2 Timer 2 I<br>This bit sets th<br>0: Timer 2 int<br>1: Timer 2 int                                                                                                                                                              | nterrupt Prio<br>e priority of<br>errupts set to | rity Control.<br>the Timer 2<br>low priority   | interrupts.                           |            |      |                           |                     |

| Bit4:     | PS: Serial Port<br>This bit sets th<br>0: UART inte<br>1: UART inte                                                                                                                                                                              | t (UART) Int<br>e priority of<br>rrupts set to   | errupt Priori<br>the Serial Po<br>low priority | ty Control.<br>ort (UART) i<br>level. | nterrupts. |      |                           |                     |

|           | <ul> <li>PT1: Timer 1 Interrupt Priority Control.</li> <li>This bit sets the priority of the Timer 1 interrupts.</li> <li>0: Timer 1 interrupts set to low priority level.</li> <li>1: Timer 1 interrupts set to high priority level.</li> </ul> |                                                  |                                                |                                       |            |      |                           |                     |

|           | PX1: External<br>This bit sets th<br>0: External In<br>1: External In                                                                                                                                                                            | e priority of terrupt 1 set                      | the External<br>to low priori                  | Interrupt 1 i<br>ty level.            | nterrupts. |      |                           |                     |

|           | <ul> <li>PT0: Timer 0 Interrupt Priority Control.</li> <li>This bit sets the priority of the Timer 0 interrupts.</li> <li>0: Timer 0 interrupt set to low priority level.</li> <li>1: Timer 0 interrupt set to high priority level.</li> </ul>   |                                                  |                                                |                                       |            |      |                           |                     |

|           | PX0: External<br>This bit sets th<br>0: External In                                                                                                                                                                                              | e priority of terrupt 0 set                      | the External                                   | Interrupt 0 i<br>ty level.            | nterrupts. |      |                           |                     |

| R      | R/W                  | R/W            | R/W            | R              | R             | R/W           | R             | Reset Value  |

|--------|----------------------|----------------|----------------|----------------|---------------|---------------|---------------|--------------|

| JTAGRS | Γ CNVRSEF            | CORSEF         | SWRSEF         | WDTRSF         | MCDRSF        | PORSF         | PINRSF        | XXXXXXXX     |

| Bit7   | Bit6                 | Bit5           | Bit4           | Bit3           | Bit2          | Bit1          | Bit0          | SFR Address: |

|        |                      |                |                |                |               |               |               | 0xEF         |

|        |                      |                |                |                |               |               |               |              |

| (Note: | Do not use read      | -modify-wri    | te operations  | on this regis  | ter.)         |               |               |              |

|        |                      |                |                |                |               |               |               |              |

|        |                      |                |                |                |               |               |               |              |

| Bit7:  | JTAGRST. J7          |                |                |                |               |               |               |              |

|        | 0: JTAG is no        |                | n reset state. |                |               |               |               |              |

|        | 1: JTAG is in        |                |                |                |               |               |               |              |

| Bit6:  | CNVRSEF: C           | onvert Start   | Reset Source   | Enable and     | Flag          |               |               |              |

|        | Write                |                |                |                |               |               |               |              |

|        | 0: CNVSTR i          |                |                |                |               |               |               |              |

|        | 1: CNVSTR i          | s a reset sou  | rce (active lo | w)             |               |               |               |              |

|        | Read                 | •              |                |                |               |               |               |              |

|        | 0: Source of p       |                |                |                |               |               |               |              |

| D'/ 5  | 1: Source of p       |                |                |                |               |               |               |              |

| Bit5:  | CORSEF: Con          | nparator 0 Re  | eset Enable a  | nd Flag        |               |               |               |              |

|        | Write                | . 0 :          | 4              |                |               |               |               |              |

|        | 0: Comparato         |                |                |                |               |               |               |              |

|        | 1: Comparato<br>Read | r 0 is a reset | source (activ  | e low)         |               |               |               |              |

|        | Note: The valu       | 10 road from   | CODSEE         | ot defined if  | Comparator    | 0 has not had | n anablad as  |              |

|        | a reset source.      |                | CORSEPTS       | iot defined fi | Comparator    | o has not bee | in enabled as |              |

|        | 0: Source of p       | rior reset w   | as not from C  | omparator 0    |               |               |               |              |

|        | 1: Source of p       |                |                |                |               |               |               |              |

| Bit4:  | SWRSF: Softv         |                |                |                |               |               |               |              |

| Dit i. | Write                | ware Reset I   | oree and r ha  | >              |               |               |               |              |

|        | 0: No Effect         |                |                |                |               |               |               |              |

|        | 1: Forces an in      | nternal reset  | . /RST pin is  | not effected   |               |               |               |              |

|        | Read                 |                | I I I          |                |               |               |               |              |

|        | 0: Prior reset       | source was r   | not from write | e to the SWR   | SF bit.       |               |               |              |

|        | 1: Prior reset       | source was f   | rom write to   | the SWRSF      | oit.          |               |               |              |

| Bit3:  | WDTRSF: Wa           | atchdog Tim    | er Reset Flag  |                |               |               |               |              |

|        | 0: Source of p       | prior reset wa | as not from V  | VDT timeout.   |               |               |               |              |

|        | 1: Source of p       | prior reset wa | as from WDT    | timeout.       |               |               |               |              |

| Bit2:  | MCDRSF: Mi           | ssing Clock    | Detector Flag  | g              |               |               |               |              |

|        | 0: Source of p       |                |                |                |               |               |               |              |

|        | 1: Source of p       |                |                |                | tector timeou | t.            |               |              |

| Bit1:  | PORSF: Powe          | er-On Reset I  | Force and Fla  | ıg             |               |               |               |              |

|        | Write                |                |                |                |               |               |               |              |

|        | 0: No effect         |                |                |                |               |               |               |              |

|        | 1: Forces a Po       | ower-On Res    | et. /RST is c  | lriven low.    |               |               |               |              |

|        | Read                 | •              |                | 0 D            |               |               |               |              |

|        | 0: Source of p       |                |                |                |               |               |               |              |

| D:40   | 1: Source of p       |                |                |                |               |               |               |              |

| Bit0:  | PINRSF: HW           |                | -              | ост ":»        |               |               |               |              |

|        | 0: Source of p       |                |                |                |               |               |               |              |

|        | 1: Source of p       | mor reset wa   | as moin /KST   | pm.            |               |               |               |              |

|        |                      |                |                |                |               |               |               |              |

|        |                      |                |                |                |               |               |               |              |

### Figure 13.4. RSTSRC: Reset Source Register

| R/W<br>P3.7 | R/W<br>P3.6                                                                                          | R/W<br>P3.5   | R/W<br>P3.4 | R/W<br>P3.3  | R/W<br>P3.2 | R/W<br>P3.1  | R/W<br>P3.0               | Reset Value<br>11111111 |

|-------------|------------------------------------------------------------------------------------------------------|---------------|-------------|--------------|-------------|--------------|---------------------------|-------------------------|

| Bit7        | Bit6                                                                                                 | Bit5          | Bit4        | Bit3         | Bit2        | Bit1         | Bit0<br>(bit addressable) | SFR Address:<br>0xB0    |

|             | P3.[7:0]<br>(Write)<br>D: Logic Low<br>1: Logic High<br>(Read)<br>D: P3.n is logi<br>1: P3.n is logi | o Output (hig | h-impedance | if correspon | ding PRT3Cl | F.n bit = 0) |                           |                         |

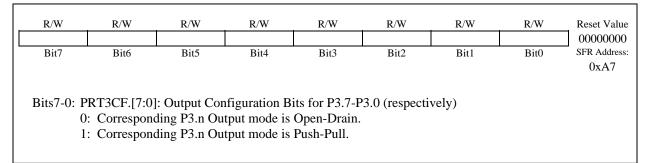

### Figure 15.13. P3: Port3 Register

#### Table 15.2. Port I/O DC Electrical Characteristics

VDD = 2.7 to 3.6V, -40°C to +85°C unless otherwise specified.

| PARAMETER             | CONDITIONS                                  | MIN   | ТҮР   | MAX   | UNITS |

|-----------------------|---------------------------------------------|-------|-------|-------|-------|

| Output High Voltage   | $I_{OH} = -10uA$ , Port I/O push-pull       | VDD – |       |       | V     |

|                       |                                             | 0.1   |       |       |       |

|                       | $I_{OH} = -3mA$ , Port I/O push-pull        | VDD – |       |       |       |

|                       |                                             | 0.7   |       |       |       |

|                       | I <sub>OH</sub> = -10mA, Port I/O push-pull |       | VDD – |       |       |

|                       |                                             |       | 0.8   |       |       |

| Output Low Voltage    | $I_{OL} = 10uA$                             |       |       | 0.1   | V     |

|                       | $I_{OL} = 8.5 \text{mA}$                    |       |       | 0.6   |       |

|                       | $I_{OL} = 25 \text{mA}$                     |       | 1.0   |       |       |

| Input High Voltage    |                                             | 0.7 x |       |       | V     |

|                       |                                             | VDD   |       |       |       |

| Input Low Voltage     |                                             |       |       | 0.3 x | V     |

|                       |                                             |       |       | VDD   |       |

| Input Leakage Current | DGND < Port Pin < VDD, Pin Tri-state        |       |       |       | μA    |

|                       | Weak Pull-up Off                            |       |       | ±1    |       |

|                       | Weak Pull-up On                             |       | 30    |       |       |

| Capacitive Loading    |                                             |       | 5     |       | pF    |

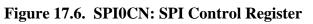

| R/W   | R/W                                                                                                                                                                                                                                                                                                                                                           | R/W                                                                                                                                                                                                                                                            | R/W             | R           | R              | R/W            | R/W                       | Reset Value         |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|----------------|----------------|---------------------------|---------------------|--|--|

| SPIF  | WCOL                                                                                                                                                                                                                                                                                                                                                          | MODF                                                                                                                                                                                                                                                           | RXOVRN          | TXBSY       | SLVSEL         | MSTEN          | SPIEN                     | 00000000            |  |  |

| Bit7  | Bit6                                                                                                                                                                                                                                                                                                                                                          | Bit5                                                                                                                                                                                                                                                           | Bit4            | Bit3        | Bit2           | Bit1           | Bit0<br>(bit addressable) | SFR Address<br>0xF8 |  |  |

| Bit7: | SPIF: SPI Inte<br>This bit is set<br>setting this bit<br>not automatica                                                                                                                                                                                                                                                                                       | to logic 1 by causes the (                                                                                                                                                                                                                                     | CPU to vector   | to the SPI0 | interrupt serv | vice routine.  |                           |                     |  |  |

| Bit6: | This bit is set                                                                                                                                                                                                                                                                                                                                               | COL: Write Collision Flag.<br>his bit is set to logic 1 by hardware (and generates a SPI interrupt) to indicate a write to<br>sPI data register was attempted while a data transfer was in progress. It is cleared by<br>oftware.                              |                 |             |                |                |                           |                     |  |  |

| Bit5: | This bit is set collision is de                                                                                                                                                                                                                                                                                                                               | MODF: Mode Fault Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI interrupt) when a master mode<br>collision is detected (NSS is low and MSTEN = 1). This bit is not automatically cleared by<br>hardware. It must be cleared by software. |                 |             |                |                |                           |                     |  |  |

| Bit4: | RXOVRN: Receive Overrun Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI interrupt) when the receive<br>buffer still holds unread data from a previous transfer and the last bit of the current transfer<br>is shifted into the SPI shift register. This bit is not automatically cleared by hardware. It<br>must be cleared by software. |                                                                                                                                                                                                                                                                |                 |             |                |                |                           |                     |  |  |

| Bit3: | TXBSY: Tran<br>This bit is set<br>cleared by har                                                                                                                                                                                                                                                                                                              | to logic 1 by                                                                                                                                                                                                                                                  | hardware wh     |             | mode transfe   | r is in progre | ss. It is                 |                     |  |  |

| Bit2: | SLVSEL: Slave Selected Flag.<br>This bit is set to logic 1 whenever the NSS pin is low indicating it is enabled as a slave. It<br>is cleared to logic 0 when NSS is high (slave disabled).                                                                                                                                                                    |                                                                                                                                                                                                                                                                |                 |             |                |                |                           |                     |  |  |

| Bit1: | MSTEN: Mas<br>0: Disable mas<br>1: Enable mas                                                                                                                                                                                                                                                                                                                 | ster mode.                                                                                                                                                                                                                                                     | Operate in slav |             |                |                |                           |                     |  |  |

| Bit0: | SPIEN: SPI E<br>This bit enable<br>0: SPI disable                                                                                                                                                                                                                                                                                                             | es/disables tl                                                                                                                                                                                                                                                 | he SPI.         |             |                |                |                           |                     |  |  |

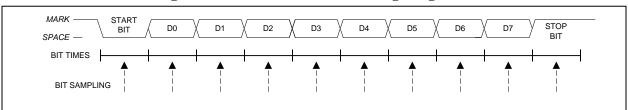

Mode 1 provides standard asynchronous, full duplex communication using a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit (see the timing diagram in Figure 18.4). Data are transmitted from the TX pin and received at the RX pin (see the interconnection diagram in Figure 18.5). On receive, the eight data bits are stored in SBUF and the stop bit goes into RB8 (SCON.2).

Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit (SCON.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF receive register if the following conditions are met: RI must be logic 0, and if SM2 is logic 1, the stop bit must be logic 1.

If these conditions are met, the eight bits of data are stored in SBUF, the stop bit is stored in RB8, and the RI flag is set. If these conditions are not met, SBUF and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI is set.

Figure 18.4. UART Mode 1 Timing Diagram

The baud rate generated in Mode 1 is a function of timer overflow. The UART can use Timer 1 operating in 8-bit *Counter/Timer with Auto-Reload Mode*, or Timer 2 operating in *Baud Rate Generator Mode* to generate the baud rate (note that the TX and RX clock sources are selected separately). On each timer overflow event (a rollover from all ones (0xFF for Timer 1, 0xFFFF for Timer 2) to zero), a clock is sent to the baud rate logic.

When Timer 1 is selected as a baud rate source, the SMOD bit (PCON.7) selects whether or not to divide the Timer 1 overflow rate by two. On reset, the SMOD bit is logic 0, thus selecting the lower speed baud rate by default. The SMOD bit affects the baud rate generated by Timer 1 as follows:

Mode 1 Baud Rate =  $(1/32) * T1_OVERFLOWRATE$  (when the SMOD bit is set to logic 0). Mode 1 Baud Rate =  $(1/16) * T1_OVERFLOWRATE$  (when the SMOD bit is set to logic 1).

When Timer 2 is selected as a baud rate source, the baud rate generated by Timer 2 is as follows:

Mode 1 Baud Rate =  $(1 / 16) * T2_OVERFLOWRATE$ .

The Timer 1 overflow rate is determined by the Timer 1 clock source (T1CLK) and reload value (TH1). The frequency of T1CLK can be selected as SYSCLK, SYSCLK/12, or an external clock source. The Timer 1 overflow rate can be calculated as follows:

$$T1_OVERFLOWRATE = T1CLK / (256 - TH1).$$

For example, assume TMOD = 0x20. If T1M (CKCON.4) is logic 1, then the above equation becomes:

$T1_OVERFLOWRATE = (SYSCLK) / (256 - TH1).$

If T1M (CKCON.4) is logic 0, then the above equation becomes:

$T1_OVERFLOWRATE = (SYSCLK/12) / (256 - TH1).$

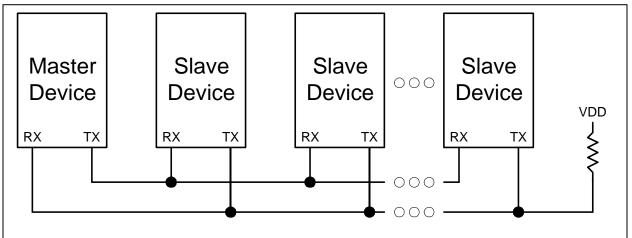

#### 18.2. Multiprocessor Communications

Modes 2 and 3 support multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the SM2 bit (SCON.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic one (RB8 = 1) signifying an address byte has been received. In the UART's interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its SM2 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their SM2 bits set and do not generate interrupts on the received, the addressed slave resets its SM2 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 18.7. UART Multi-Processor Mode Interconnect Diagram

| Figure 19.5. | TMOD: Timer Mode Register |

|--------------|---------------------------|

|              |                           |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Coun 0: Timer Fe 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} 0011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Coun0: Timer Fe1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                                    | enabled only<br>nter/Timer 1 S<br>Function: Tim<br>r Function: Ti                                                                       | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.        | T0M0<br>Bit0 | 00000000<br>SFR Address<br>0x89 |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------|-------------|--------------|---------------------------------|--|--|--|

| Bit7: GATE1: Tin<br>0: Timer 1 e<br>1: Timer 1 e<br>Bit6: C/T1: Coun<br>0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>$\overline{11M1}$<br>0<br>0<br>1<br>1<br>Bit3: GATE0: Tin<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                      | imer 1 Gate C<br>enabled when<br>enabled only<br>nter/Timer 1 S<br>Function: Tim<br>r Function: Tim<br>M0: Timer 1 M                    | Control.<br>TR1 = 1 irres<br>when $TR1 = 1$<br>Select.<br>er 1 incrementer<br>mer 1 incrementer<br>Mode Select. | pective of /IN<br>AND /INT1<br>ed by clock de | T1 logic leve<br>= logic level<br>fined by T11 | el.<br>one. | Bit0         |                                 |  |  |  |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Count 0: Timer Fu 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} = 0 0110011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Count0: Timer Fu1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                           | enabled when<br>enabled only<br>nter/Timer 1 S<br>function: Tim<br>r Function: Ti<br>M0: Timer 1 M                                      | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.        |              | 0.0.89                          |  |  |  |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Count 0: Timer Fu 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} = 0 0110011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Count0: Timer Fu1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                           | enabled when<br>enabled only<br>nter/Timer 1 S<br>function: Tim<br>r Function: Ti<br>M0: Timer 1 M                                      | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.        |              |                                 |  |  |  |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Count 0: Timer Fu 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} = 0 0110011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Count0: Timer Fu1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                           | enabled when<br>enabled only<br>nter/Timer 1 S<br>function: Tim<br>r Function: Ti<br>M0: Timer 1 M                                      | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.        |              |                                 |  |  |  |

| 1: Timer 1 eBit6: $C/T1: Counter$<br>$0: Timer Fu1: Counter(T1).Bits5-4:T1M1-T1MThese bits sBits5-4:T1M1-T1MThese bits sBit3:GATE0: Time 00: Timer 0 e1: Timer 0 eBit2:C/T0: Counter(T0).Bits1-0:T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                                                                       | enabled only<br>nter/Timer 1 S<br>Function: Tim<br>r Function: Ti<br>M0: Timer 1 M                                                      | when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer<br>Aode Select.                                    | AND /INT1                                     | = logic level                                  | one.        |              |                                 |  |  |  |

| Bit6: C/T1: Count<br>0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>Bit3: GATE0: Tim<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Count<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                     | nter/Timer 1 S<br>Function: Tim<br>r Function: Ti<br>M0: Timer 1 N                                                                      | Select.<br>er 1 incremente<br>mer 1 incremer<br>Aode Select.                                                    | ed by clock de                                | fined by T11                                   |             |              |                                 |  |  |  |

| 0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>1<br>Bit3: GATE0: Tim<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                      | Function: Tim<br>r Function: Ti<br>40: Timer 1 M                                                                                        | er 1 incremente<br>mer 1 incremer<br>Aode Select.                                                               |                                               |                                                | M hit (CKCO |              |                                 |  |  |  |

| 0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>1<br>Bit3: GATE0: Tim<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Counter<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                   | Function: Tim<br>r Function: Ti<br>40: Timer 1 M                                                                                        | er 1 incremente<br>mer 1 incremer<br>Aode Select.                                                               |                                               |                                                | M bit (CKCO |              |                                 |  |  |  |

| 1: Counter (T1).         Bits5-4: T1M1-T1M These bits s <b>T1M1</b> 0         0         1         0         1         1         Bit3: GATE0: Timer 0 et al.: C/T0: Counter (T0).         Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                       | r Function: Ti<br>40: Timer 1 N                                                                                                         | mer 1 incremer<br>Aode Select.                                                                                  |                                               |                                                |             | N.4).        |                                 |  |  |  |

| (T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>Bit3: GATE0: Tit<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A0: Timer 1 M                                                                                                                           | Aode Select.                                                                                                    | , ,                                           |                                                |             |              | L                               |  |  |  |

| Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>1<br>Bit3: GATE0: Tit<br>0: Timer 0 c<br>1: Timer 0 c<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                         |                                                                                                                 |                                               |                                                |             | 1 1          |                                 |  |  |  |

| These bits s T1M1 0 0 1 1 1 Bit3: GATE0: Tit 0: Timer 0 e 1: Timer 0 e 1: C/T0: Coun 0: Timer Fe 1: Counter (T0). Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                         |                                                                                                                 |                                               |                                                |             |              |                                 |  |  |  |

| T1M1           0           0           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1 | select the Tin                                                                                                                          |                                                                                                                 |                                               |                                                |             |              |                                 |  |  |  |

| 00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                         | ner 1 operation                                                                                                 | mode.                                         |                                                |             |              |                                 |  |  |  |

| 00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                         |                                                                                                                 |                                               |                                                |             |              |                                 |  |  |  |

| 01111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                         | ode                                                                                                             |                                               |                                                |             |              |                                 |  |  |  |

| 11111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                         | Mode 0: 13-bit counter/timer                                                                                    |                                               |                                                |             |              |                                 |  |  |  |

| IBit3:GATE0: Tim<br>0: Timer 0 eBit2:C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).Bits1-0:T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                         | Mode 1: 16-bit counter/timer                                                                                    |                                               |                                                |             |              |                                 |  |  |  |