Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 20MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 32                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b; D/A 2x12b                                            |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f010-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Table 18.2. Oscillator Frequencies for Standard Baud Rates                         |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | Figure 18.8. SBUF: Serial (UART) Data Buffer Register                              |     |

|     | Figure 18.9. SCON: Serial Port Control Register                                    |     |

| 19. | TIMERS                                                                             |     |

|     | 19.1. Timer 0 and Timer 1                                                          |     |

|     | Figure 19.1. T0 Mode 0 Block Diagram.                                              |     |

|     | Figure 19.2. T0 Mode 2 Block Diagram.                                              |     |

|     | Figure 19.3. T0 Mode 3 Block Diagram.                                              |     |

|     | Figure 19.4. TCON: Timer Control Register                                          |     |

|     | Figure 19.5. TMOD: Timer Mode Register                                             |     |

|     | Figure 19.6. CKCON: Clock Control Register                                         |     |

|     | Figure 19.7. TLO: Timer 0 Low Byte                                                 |     |

|     | Figure 19.8. TL1: Timer 1 Low Byte                                                 |     |

|     | Figure 19.9. THO: Timer 0 High Byte                                                |     |

|     | Figure 19.10. TH1: Timer 1 High Byte                                               |     |

|     | 19.2. Timer 2                                                                      |     |

|     | Figure 19.11. T2 Mode 0 Block Diagram                                              |     |

|     | Figure 19.12. T2 Mode 1 Block Diagram.                                             |     |

|     | Figure 19.13. T2 Mode 2 Block Diagram.                                             |     |

|     | Figure 19.14. T2CON: Timer 2 Control Register                                      |     |

|     | Figure 19.15. RCAP2L: Timer 2 Capture Register Low Byte                            |     |

|     | Figure 19.16. RCAP2H: Timer 2 Capture Register High Byte                           |     |

|     | Figure 19.17. TL2: Timer 2 Low Byte                                                |     |

|     | Figure 19.18. TH2: Timer 2 High Byte                                               |     |

|     | 19.3. Timer 3                                                                      |     |

|     | Figure 19.19. Timer 3 Block Diagram                                                |     |

|     | Figure 19.20. TMR3CN: Timer 3 Control Register                                     |     |

|     | Figure 19.21. TMR3RLL: Timer 3 Reload Register Low Byte                            |     |

|     | Figure 19.22. TMR3RLH: Timer 3 Reload Register High Byte                           |     |

|     | Figure 19.22. TMR3REIT. Timer 3 Keroad Register High Byte                          |     |

|     | Figure 19.24. TMR3H: Timer 3 High Byte                                             |     |

| 20  | PROGRAMMABLE COUNTER ARRAY                                                         |     |

| 20. |                                                                                    |     |

|     | Figure 20.1. PCA Block Diagram                                                     |     |

|     | 20.1. Capture/Compare Modules                                                      |     |

|     | Table 20.1. PCA0CPM Register Settings for PCA Capture/Compare Modules              |     |

|     | Figure 20.2. PCA Interrupt Block Diagram.                                          |     |

|     | Figure 20.3. PCA Capture Mode Diagram                                              |     |

|     | Figure 20.4. PCA Software Timer Mode Diagram.                                      |     |

|     | Figure 20.5. PCA High Speed Output Mode Diagram                                    |     |

|     | Figure 20.6. PCA PWM Mode Diagram                                                  |     |

|     | 20.2. PCA Counter/Timer                                                            |     |

|     | Table 20.2.     PCA Timebase Input Options.       Figure 20.7     PCA Construction |     |

|     | Figure 20.7. PCA Counter/Timer Block Diagram                                       |     |

|     | 20.3. Register Descriptions for PCA                                                |     |

|     | Figure 20.8. PCA0CN: PCA Control Register                                          |     |

|     | Figure 20.9. PCA0MD: PCA Mode Register                                             |     |

|     | Figure 20.10. PCA0CPMn: PCA Capture/Compare Registers                              |     |

|     | Figure 20.11. PCA0L: PCA Counter/Timer Low Byte                                    |     |

|     | Figure 20.12. PCA0H: PCA Counter/Timer High Byte                                   |     |

|     | Figure 20.13. PCA0CPLn: PCA Capture Module Low Byte                                |     |

|     | Figure 20.14. PCA0CPHn: PCA Capture Module High Byte                               |     |

| 21. | JTAG (IEEE 1149.1)                                                                 |     |

|     | Figure 21.1. IR: JTAG Instruction Register                                         |     |

|     | 21.1. Boundary Scan                                                                | 165 |

Figure 1.1. C8051F000/05/10/15 Block Diagram

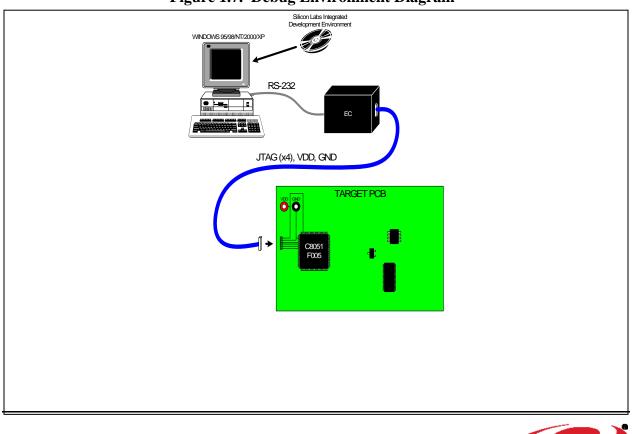

## 1.3. JTAG Debug and Boundary Scan

The C8051F000 family has on-chip JTAG and debug circuitry that provide *non-intrusive, full speed, in-circuit debug using the production part installed in the end application* using the four-pin JTAG I/F. The JTAG port is fully compliant to IEEE 1149.1, providing full boundary scan for test and manufacturing purposes.

Silicon Labs' debug system supports inspection and modification of memory and registers, breakpoints, watchpoints, a stack monitor, and single stepping. No additional target RAM, program memory, timers, or communications channels are required. All the digital and analog peripherals are functional and work correctly while debugging. All the peripherals (except for the ADC) are stalled when the MCU is halted, during single stepping, or at a breakpoint in order to keep them in sync.

The C8051F000DK, C8051F005DK, C8051F010DK, and C8051F015DK are development kits with all the hardware and software necessary to develop application code and perform in-circuit debug with the C8051F000/1/2, F005/6/7, F010/1/2, and F015/6/7 MCUs respectively. The kit includes software with a developer's studio and debugger, an integrated 8051 assembler, and an RS-232 to JTAG protocol translator module referred to as the EC. It also has a target application board with the associated MCU installed and a large prototyping area, plus the RS-232 and JTAG cables, and wall-mount power supply. The Development Kit requires a Windows 95/98/NT/2000/XP computer with one available RS-232 serial port. As shown in Figure 1.7, the PC is connected via RS-232 to the EC. A six-inch ribbon cable connects the EC to the user's application board, picking up the four JTAG pins and VDD and GND. The EC takes its power from the application board. It requires roughly 20mA at 2.7-3.6V. For applications where there is not sufficient power available from the target board, the provided power supply can be connected directly to the EC.

This is a vastly superior configuration for developing and debugging embedded applications compared to standard MCU Emulators, which use on-board "ICE Chips" and target cables and require the MCU in the application board to be socketed. Silicon Labs' debug environment both increases ease of use and preserves the performance of the precision analog peripherals.

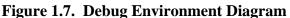

Figure 4.6. LQFP-32 Package Drawing

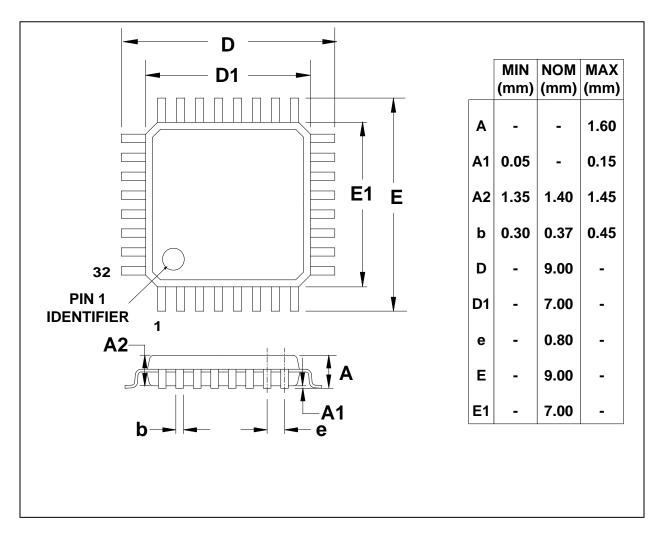

# 7. DACs, 12 BIT VOLTAGE MODE

The C8051F000 MCU family has two 12-bit voltage-mode Digital to Analog Converters. Each DAC has an output swing of 0V to VREF-1LSB for a corresponding input code range of 0x000 to 0xFFF. Using DAC0 as an example, the 12-bit data word is written to the low byte (DAC0L) and high byte (DAC0H) data registers. Data is latched into DAC0 after a write to the corresponding DAC0H register, **so the write sequence should be DAC0L followed by DAC0H** if the full 12-bit resolution is required. The DAC can be used in 8-bit mode by initializing DAC0L to the desired value (typically 0x00), and writing data to only DAC0H with the data shifted to the left. DAC0 Control Register (DAC0CN) provides a means to enable/disable DAC0 and to modify its input data formatting.

The DAC0 enable/disable function is controlled by the DAC0EN bit (DAC0CN.7). Writing a 1 to DAC0EN enables DAC0 while writing a 0 to DAC0EN disables DAC0. While disabled, the output of DAC0 is maintained in a high-impedance state, and the DAC0 supply current falls to  $1\mu$ A or less. Also, the Bias Enable bit (BIASE) in the REF0CN register (see Figure 9.2) must be set to 1 in order to supply bias to DAC0. The voltage reference for DAC0 must also be set properly (see Section 9).

In some instances, input data should be shifted prior to a DAC0 write operation to properly justify data within the DAC input registers. This action would typically require one or more load and shift operations, adding software overhead and slowing DAC throughput. To alleviate this problem, the data-formatting feature provides a means for the user to program the orientation of the DAC0 data word within data registers DAC0H and DAC0L. The three DAC0DF bits (DAC0CN.[2:0]) allow the user to specify one of five data word orientations as shown in the DAC0CN register definition.

DAC1 is functionally the same as DAC0 described above. The electrical specifications for both DAC0 and DAC1 are given in Table 7.1.

Figure 7.1. DAC Functional Block Diagram

## 8. COMPARATORS

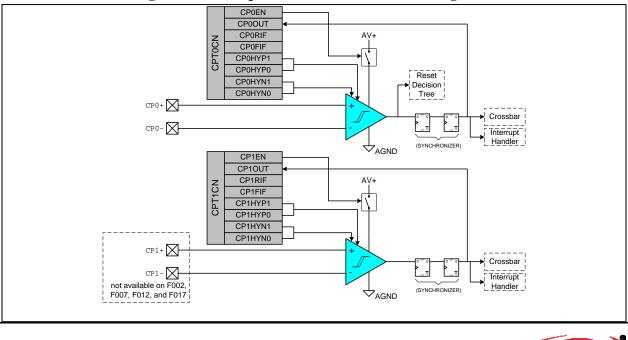

The MCU family has two on-chip analog voltage comparators as shown in Figure 8.1. The inputs of each Comparator are available at the package pins. The output of each comparator is optionally available at the package pins via the I/O crossbar (see Section 15.1). When assigned to package pins, each comparator output can be programmed to operate in open drain or push-pull modes (see section 15.3).

The hysteresis of each comparator is software-programmable via its respective Comparator control register (CPT0CN, CPT1CN). The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage. The output of the comparator can be polled in software, or can be used as an interrupt source. Each comparator can be individually enabled or disabled (shutdown). When disabled, the comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, its interrupt capability is suspended and its supply current falls to less than  $1\mu$ A. Comparator 0 inputs can be externally driven from -0.25V to (AV+) + 0.25V without damage or upset.

The Comparator 0 hysteresis is programmed using bits 3-0 in the Comparator 0 Control Register CPT0CN (shown in Figure 8.3). The amount of *negative* hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Figure 8.2, settings of 10, 4 or 2mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of *positive* hysteresis is determined by the setting the CP0HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section 10.4). The CPOFIF flag is set upon a Comparator 0 falling-edge interrupt, and the CPORIF flag is set upon the Comparator 0 rising-edge interrupt. Once set, these bits remain set until cleared by the CPU. The Output State of Comparator 0 can be obtained at any time by reading the CPOOUT bit. Note the comparator output and interrupt should be ignored until the comparator settles after power-up. Comparator 0 is enabled by setting the CPOEN bit, and is disabled by clearing this bit. Note there is a 20usec settling time for the comparator output to stabilize after setting the CPOEN bit or a power-up. Comparator 0 can also be programmed as a reset source. For details, see Section 13.

The operation of Comparator 1 is identical to that of Comparator 0, except the Comparator 1 is controlled by the CPT1CN Register (Figure 8.4). Comparator 1 can not be programmed as a reset source. Also, the input pins for Comparator 1 are not pinned out on the F002, F007, F012, or F017 devices. The complete electrical specifications for the Comparators are given in Table 8.1.

Figure 8.1. Comparator Functional Block Diagram

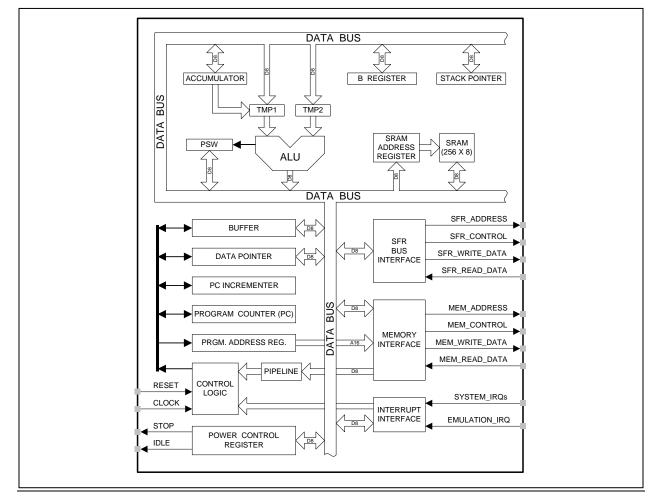

## 10. CIP-51 CPU

The MCUs' system CPU is the CIP-51. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set. Standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are four 16-bit counter/timers (see description in Section 19), a full-duplex UART (see description in Section 18), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (see Section 10.3), and four byte-wide I/O Ports (see description in Section 14). The CIP-51 also includes on-chip debug hardware (see description in Section 21), and interfaces directly with the MCUs' analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

### Features

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 10.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25MHz Clock

- 0 to 25MHz Clock Frequency (on 'F0x5/6/7)

- Four Byte-Wide I/O Ports

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Circuitry

- Program and Data Memory Security

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's maximum system clock at 25MHz, it has a peak throughput of 25MIPS. The CIP-51 has a total of 109 instructions. The number of instructions versus the system clock cycles required to execute them is as follows:

| Instructions      | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

|-------------------|----|----|-----|----|-----|---|-----|---|---|

| Clocks to Execute | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

#### **Programming and Debugging Support**

A JTAG-based serial interface is provided for in-system programming of the Flash program memory and communication with on-chip debug support circuitry. The reprogrammable Flash can also be read and changed a single byte at a time by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support circuitry facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints and watch points, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive and non-invasive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Laboratories and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, macro assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via its JTAG interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

### **10.1. INSTRUCTION SET**

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>TM</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>TM</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### **10.1.1. Instruction and CPU Timing**

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 10.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 10.1.2. MOVX Instruction and Program Memory

The MOVX instruction is typically used to access external data memory. In the CIP-51, the MOVX instruction can access the on-chip program memory space implemented as reprogrammable Flash memory using the control bits in the PSCTL register (see Figure 11.1). This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. For the products with RAM mapped into external data memory space (C8051F005/06/07/15/16/17), MOVX is still used to read/write this memory with the PSCTL

| Address    | Register      | Description                       | Page No. |

|------------|---------------|-----------------------------------|----------|

| 0x89       | TMOD          | Counter/Timer Mode                | 143      |

| 0x91       | TMR3CN        | Timer 3 Control                   | 152      |

| 0x95       | TMR3H         | Timer 3 High                      | 153      |

| 0x94       | TMR3L         | Timer 3 Low                       | 153      |

| 0x93       | TMR3RLH       | Timer 3 Reload High               | 153      |

| 0x92       | TMR3RLL       | Timer 3 Reload Low                | 153      |

| 0xFF       | WDTCN         | Watchdog Timer Control            | 96       |

| 0xE1       | XBR0          | Port I/O Crossbar Configuration 1 | 105      |

| 0xE2       | XBR1          | Port I/O Crossbar Configuration 2 | 107      |

| 0xE3       | XBR2          | Port I/O Crossbar Configuration 3 | 108      |

| 0x84-86, 0 | x96-97, 0x9C, |                                   |          |

| 0xA1-A3,   | 0xA9-AC,      |                                   |          |

| 0xAE, 0xB  | 3-B5, 0xB9,   | Reserved                          |          |

| 0xBD, 0xC  | C9, 0xCE,     |                                   |          |

| 0xDF, 0xE  | 4-E5, 0xF1-F5 |                                   |          |

\* Refers to a register in the C8051F000/1/2/5/6/7 only. \*\* Refers to a register in the C8051F010/1/2/5/6/7 only. \*\*\* Refers to a register in the C8051F005/06/07/15/16/17 only.

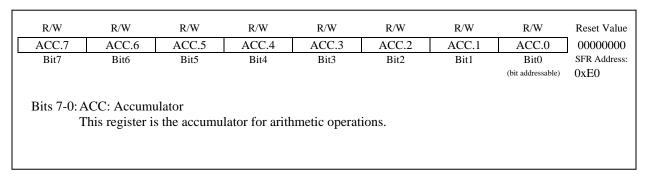

## Figure 10.7. ACC: Accumulator

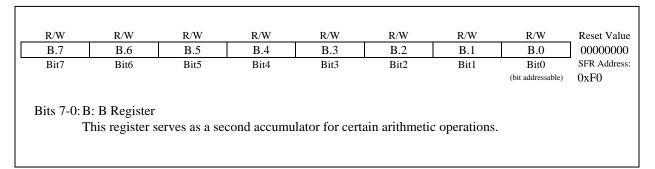

### Figure 10.8. B: B Register

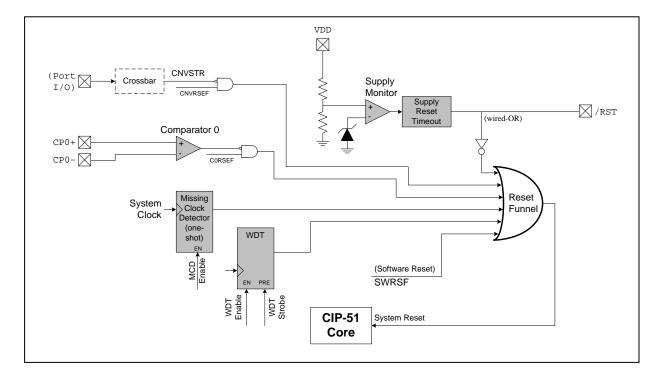

## **13. RESET SOURCES**

The reset circuitry of the MCUs allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the CIP-51 halts program execution, forces the external port pins to a known state and initializes the SFRs to their defined reset values. Interrupts and timers are disabled. On exit, the program counter (PC) is reset, and program execution starts at location 0x0000.

All of the SFRs are reset to predefined values. The reset values of the SFR bits are defined in the SFR detailed descriptions. The contents of internal data memory are not changed during a reset and any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack are not altered.

The I/O port latches are reset to 0xFF (all logic ones), activating internal weak pull-ups which take the external I/O pins to a high state. The weak pull-ups are enabled during and after the reset. If the source of reset is from the VDD Monitor or writing a 1 to PORSF, the /RST pin is driven low until the end of the VDD reset timeout.

On exit from the reset state, the MCU uses the internal oscillator running at 2MHz as the system clock by default. Refer to Section 14 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled using its longest timeout interval. (Section 13.8 details the use of the Watchdog Timer.)

There are seven sources for putting the MCU into the reset state: power-on/power-fail, external /RST pin, external CNVSTR signal, software commanded, Comparator 0, Missing Clock Detector, and Watchdog Timer. Each reset source is described below:

### 13.4. External Reset

The external /RST pin provides a means for external circuitry to force the MCU into a reset state. Asserting an active-low signal on the /RST pin will cause the MCU to enter the reset state. Although there is a weak internal pullup, it may be desirable to provide an external pull-up and/or decoupling of the /RST pin to avoid erroneous noise-induced resets. The MCU will remain in reset until at least 12 clock cycles after the active-low /RST signal is removed. The PINRSF flag (RSTSRC.0) is set on exit from an external reset. The /RST pin is also 5V tolerant.

### 13.5. Missing Clock Detector Reset

The Missing Clock Detector is essentially a one-shot circuit that is triggered by the MCU system clock. If the system clock goes away for more than  $100\mu$ s, the one-shot will time out and generate a reset. After a Missing Clock Detector reset, the MCDRSF flag (RSTSRC.2) will be set, signifying the MSD as the reset source; otherwise, this bit reads 0. The state of the /RST pin is unaffected by this reset. Setting the MSCLKE bit in the OSCICN register (see Figure 14.2) enables the Missing Clock Detector.

### **13.6.** Comparator 0 Reset

Comparator 0 can be configured as an active-low reset input by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator 0 should be enabled using CPT0CN.7 (see Figure 8.3) at least 20µs prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. When configured as a reset, if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the MCU is put into the reset state. After a Comparator 0 Reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator 0 as the reset source; otherwise, this bit reads 0. The state of the /RST pin is unaffected by this reset. Also, Comparator 0 can generate a reset with or without the system clock.

### 13.7. External CNVSTR Pin Reset

The external CNVSTR signal can be configured as an active-low reset input by writing a 1 to the CNVRSEF flag (RSTSRC.6). The CNVSTR signal can appear on any of the P0, P1, or P2 I/O pins as described in Section 15.1. (Note that the Crossbar must be configured for the CNVSTR signal to be routed to the appropriate Port I/O.) The Crossbar should be configured and enabled before the CNVRSEF is set to configure CNVSTR as a reset source. When configured as a reset, CNVSTR is active-low and level sensitive. After a CNVSTR reset, the CNVRSEF flag (RSTSRC.6) will read 1 signifying CNVSTR as the reset source; otherwise, this bit reads 0. The state of the /RST pin is unaffected by this reset.

### 13.8. Watchdog Timer Reset

The MCU includes a programmable Watchdog Timer (WDT) running off the system clock. The WDT will force the MCU into the reset state when the watchdog timer overflows. To prevent the reset, the WDT must be restarted by application software before the overflow occurs. If the system experiences a software/hardware malfunction preventing the software from restarting the WDT, the WDT will overflow and cause a reset. This should prevent the system from running out of control.

The WDT is automatically enabled and started with the default maximum time interval on exit from all resets. If desired the WDT can be disabled by system software or locked on to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the /RST pin is unaffected by this reset.

95

#### 13.8.1. Watchdog Usage

The WDT consists of a 21-bit timer running from the programmed system clock. The timer measures the period between specific writes to its control register. If this period exceeds the programmed limit, a WDT reset is generated. The WDT can be enabled and disabled as needed in software, or can be permanently enabled if desired. Watchdog features are controlled via the Watchdog Timer Control Register (WDTCN) shown in Figure 13.3.

#### Enable/Reset WDT

The watchdog timer is both enabled and the countdown restarted by writing 0xA5 to the WDTCN register. The user's application software should include periodic writes of 0xA5 to WDTCN as needed to prevent a watchdog timer overflow. The WDT is enabled and restarted as a result of any system reset.

#### **Disable WDT**

Writing 0xDE followed by 0xAD to the WDTCN register disables the WDT. The following code segment illustrates disabling the WDT.

CLR EA ; disable all interrupts MOV WDTCN,#0DEh ; disable software MOV WDTCN,#0ADh ; watchdog timer SETB EA ; re-enable interrupts

The writes of 0xDE and 0xAD must occur within 4 clock cycles of each other, or the disable operation is ignored. Interrupts should be disabled during this procedure to avoid delay between the two writes.

#### **Disable WDT Lockout**

Writing 0xFF to WDTCN locks out the disable feature. Once locked out, the disable operation is ignored until the next system reset. Writing 0xFF does not enable or reset the watchdog timer. Applications always intending to use the watchdog should write 0xFF to WDTCN in their initialization code.

#### Setting WDT Interval

WDTCN.[2:0] control the watchdog timeout interval. The interval is given by the following equation:

$4^{3+WDTCN[2:0]} \times T_{SYSCLK}$ , (where  $T_{SYSCLK}$  is the system clock period).

For a 2MHz system clock, this provides an interval range of 0.032msec to 524msec. WDTCN.7 must be a 0 when setting this interval. Reading WDTCN returns the programmed interval. WDTCN.[2:0] is 111b after a system reset.

| R/W      | R/W           | R/W             | R/W             | R/W          | R/W          | R/W           | R/W      | Reset Value  |

|----------|---------------|-----------------|-----------------|--------------|--------------|---------------|----------|--------------|

|          |               |                 |                 |              |              |               |          | xxxxx111     |

| Bit7     | Bit6          | Bit5            | Bit4            | Bit3         | Bit2         | Bit1          | Bit0     | SFR Address: |

|          |               |                 |                 |              |              |               |          | 0xFF         |

|          |               |                 |                 |              |              |               |          |              |

| Bits7-0: | WDT Control   |                 |                 |              |              |               |          |              |

|          | Writing 0xA5  | both enables    | and reloads     | the WDT.     |              |               |          |              |

|          | Writing 0xDE  |                 |                 |              | ables the WI | т             |          |              |

|          | U             |                 |                 | •            |              |               |          |              |

|          | Writing 0xFF  |                 |                 | lie.         |              |               |          |              |

| Bit4:    | Watchdog Stat | •               | ,               |              |              |               |          |              |

|          | Reading the W | /DTCN.[4] b     | it indicates th | ne Watchdog  | Timer Status | <b>.</b>      |          |              |

|          | 0: WDT is ina | active          |                 |              |              |               |          |              |

|          | 1: WDT is act | tive            |                 |              |              |               |          |              |

| Bits2_0. | Watchdog Tin  |                 | Rite            |              |              |               |          |              |

| Dits2-0. | -             |                 |                 | . T          | (            |               |          |              |

|          | The WDTCN.    |                 |                 | g Timeout In | terval. when | n writing the | se bits, |              |

|          | WDTCN.7 mu    | ist be set to 0 | •               |              |              |               |          |              |

|          |               |                 |                 |              |              |               |          |              |

|          |               |                 |                 |              |              |               |          |              |

Figure 13.3. WDTCN: Watchdog Timer Control Register

| Figure 14.3. | <b>OSCXCN: External</b> | Oscillator | <b>Control Register</b> |

|--------------|-------------------------|------------|-------------------------|

|--------------|-------------------------|------------|-------------------------|

| A COLLAND | R/                                                                                                                                                                      | W R/W                                                                                                                                                                                                                                                                               | R/W                                                                                                                          | R/W                                                                      | R/W            | R/W                     | R/W     | Reset Value |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|-------------------------|---------|-------------|

| XTLVL     | D XOSC                                                                                                                                                                  | CMD2 XOSCMD1                                                                                                                                                                                                                                                                        | XOSCMD0                                                                                                                      | -                                                                        | XFCN2          | XFCN1                   | XFCN0   | 00110000    |

| Bit7      | Bi                                                                                                                                                                      | t6 Bit5                                                                                                                                                                                                                                                                             | Bit4                                                                                                                         | Bit3                                                                     | Bit2           | Bit1                    | Bit0    | SFR Address |

|           |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                     |                                                                                                                              |                                                                          |                |                         |         | 0xB1        |

| Bit7:     | XTLVLD                                                                                                                                                                  | : Crystal Oscillator                                                                                                                                                                                                                                                                | r Valid Flag                                                                                                                 |                                                                          |                |                         |         |             |

|           | (Valid on                                                                                                                                                               | ly when XOSCM                                                                                                                                                                                                                                                                       | $\mathbf{D} = 1\mathbf{x}\mathbf{x}.$                                                                                        |                                                                          |                |                         |         |             |

|           |                                                                                                                                                                         | l Oscillator is unus                                                                                                                                                                                                                                                                |                                                                                                                              |                                                                          |                |                         |         |             |

|           |                                                                                                                                                                         | l Oscillator is runn                                                                                                                                                                                                                                                                |                                                                                                                              | e (should rea                                                            | d 1ms after (  | Crystal Oscill          | ator is |             |

|           |                                                                                                                                                                         | d to avoid transien                                                                                                                                                                                                                                                                 |                                                                                                                              |                                                                          |                |                         |         |             |

| Bits6-4:  |                                                                                                                                                                         | D2-0: External Osc                                                                                                                                                                                                                                                                  |                                                                                                                              |                                                                          |                |                         |         |             |

|           |                                                                                                                                                                         | XTAL1 pin is gro                                                                                                                                                                                                                                                                    |                                                                                                                              |                                                                          |                |                         |         |             |

|           |                                                                                                                                                                         | em Clock from Ex                                                                                                                                                                                                                                                                    |                                                                                                                              |                                                                          |                | 1.11.0                  |         |             |

|           |                                                                                                                                                                         | em Clock from Ex                                                                                                                                                                                                                                                                    |                                                                                                                              |                                                                          | I AL I pin di  | vided by 2.             |         |             |

|           |                                                                                                                                                                         | C Oscillator Mode                                                                                                                                                                                                                                                                   |                                                                                                                              | by 2 stage.                                                              |                |                         |         |             |

|           |                                                                                                                                                                         | stal Oscillator Mod<br>stal Oscillator Mod                                                                                                                                                                                                                                          |                                                                                                                              | by 2 stage                                                               |                |                         |         |             |

| Bit3:     |                                                                                                                                                                         | ED. Read = undef                                                                                                                                                                                                                                                                    |                                                                                                                              |                                                                          |                |                         |         |             |

|           |                                                                                                                                                                         | ED. Read – under                                                                                                                                                                                                                                                                    |                                                                                                                              |                                                                          |                |                         |         |             |

| DI132-0.  |                                                                                                                                                                         | see table below                                                                                                                                                                                                                                                                     | of Trequency                                                                                                                 | Control Dits                                                             |                |                         |         |             |

|           | 000 111.                                                                                                                                                                | see tuble below                                                                                                                                                                                                                                                                     |                                                                                                                              |                                                                          |                |                         |         |             |

|           | XFCN                                                                                                                                                                    | Crystal (XOSCM                                                                                                                                                                                                                                                                      | ID = H                                                                                                                       | RC (XOSCM                                                                | D = 10x        | C (XOSCM                | D = 10x |             |

|           |                                                                                                                                                                         | 11x)                                                                                                                                                                                                                                                                                |                                                                                                                              | - (                                                                      | - /            | - (                     | - /     |             |

|           | 000                                                                                                                                                                     | f ≤ 12.5kHz                                                                                                                                                                                                                                                                         | f                                                                                                                            | $f \le 25 \text{kHz}$ K Factor = 0.44                                    |                |                         |         |             |

|           | 001                                                                                                                                                                     | $12.5$ kHz < f $\leq 30$                                                                                                                                                                                                                                                            |                                                                                                                              | $25$ kHz < f $\leq 3$                                                    | 50kHz          | K Factor $= 1$          |         |             |

|           | 010                                                                                                                                                                     | $30.35$ kHz < f $\leq$                                                                                                                                                                                                                                                              |                                                                                                                              | $50 \text{kHz} < \text{f} \le$                                           |                | K Factor $= 4$          |         |             |

|           | 011                                                                                                                                                                     | $93.8 \text{kHz} < f \le 20$                                                                                                                                                                                                                                                        |                                                                                                                              | $00kHz < f \le$                                                          |                | K Factor = 1            |         |             |

|           | 100                                                                                                                                                                     | $267 \text{kHz} < f \le 72$                                                                                                                                                                                                                                                         |                                                                                                                              | $200 \text{kHz} < f \le$                                                 |                | K Factor $= 3$          |         |             |

|           | 101                                                                                                                                                                     | $722 \text{kHz} < f \le 2.2$                                                                                                                                                                                                                                                        |                                                                                                                              | $400 \text{kHz} < f \le$                                                 |                | K Factor $= 1$          |         |             |

|           | 110                                                                                                                                                                     | $2.23$ MHz < f $\leq 6$                                                                                                                                                                                                                                                             |                                                                                                                              | $300 \text{kHz} < f \le$                                                 |                | K Factor $= 4$          |         |             |

|           |                                                                                                                                                                         | f > 6.74MHz                                                                                                                                                                                                                                                                         |                                                                                                                              | $.6MHz < f \le$                                                          |                | K Factor = $1$          |         |             |

|           |                                                                                                                                                                         | 1 > 0.74 WITZ                                                                                                                                                                                                                                                                       |                                                                                                                              | $1.0$ WITZ < 1 $\leq$                                                    | 3.2MITZ        | $\mathbf{K}$ Factor = 1 | 400     |             |

| CRVST     |                                                                                                                                                                         | <b>F</b> (Circuit from Fig                                                                                                                                                                                                                                                          | ure 1/1 1 Or                                                                                                                 | tion 1. XOS                                                              | $^{T}MD - 11v$ | 1                       |         |             |

|           | AL MOD<br>Choose X<br>DE (Circu<br>Choose os<br>f = 1.23(1)<br>f = freque<br>C = capac                                                                                  | E (Circuit from Fig<br>FCN value to match<br>it from Figure 14.1<br>scillation frequency<br>$0^3$ ) / ( <b>R</b> * <b>C</b> ), when<br>ncy of oscillation i<br>itor value in pF<br>up resistor value in                                                                             | h the crystal<br>, Option 2; Σ<br>, range where<br>re<br>n MHz                                                               | or ceramic re<br>KOSCMD =                                                | esonator free  |                         |         |             |

| RC MO     | AL MOD<br>Choose X<br>DE (Circu<br>Choose of<br>f = 1.23(1)<br>f = freque<br>C = capac<br>R = Pull-u<br>E (Circuit<br>Choose K                                          | FCN value to match<br>it from Figure 14.1<br>scillation frequency<br>$0^3$ / ( <b>R</b> * <b>C</b> ), when<br>ncy of oscillation i<br>itor value in pF<br>up resistor value in<br>from Figure 14.1,<br>Factor (KF) for th                                                           | ch the crystal<br>l, Option 2; Σ<br>y range where<br>re<br>n MHz<br>kΩ<br>Option 3; X0                                       | or ceramic re<br>XOSCMD = 1<br>e:<br>DSCMD = 10                          | x)             |                         |         |             |

| RC MO     | AL MOD<br>Choose X<br>DE (Circu<br>Choose os<br>f = 1.23(1)<br>f = freque<br>C = capac<br>R = Pull-t<br>E (Circuit<br>Choose K<br>f = KF / (C)                          | FCN value to match<br>it from Figure 14.1<br>scillation frequency<br>$0^3$ / ( <b>R</b> * <b>C</b> ), when<br>ncy of oscillation i<br>itor value in pF<br>up resistor value in<br>from Figure 14.1,<br>Factor (KF) for th<br><b>C</b> * <b>AV</b> +), where                         | h the crystal<br>, Option 2; 2<br>/ range where<br>n MHz<br>kΩ<br>Option 3; XC<br>e oscillation                              | or ceramic re<br>XOSCMD = 1<br>e:<br>DSCMD = 10                          | x)             |                         |         |             |

| RC MO     | AL MOD<br>Choose X<br>DE (Circu<br>Choose os<br>f = 1.23(1)<br>f = freque<br>C = capac<br>R = Pull-u<br>E (Circuit<br>Choose K<br>f = KF / (<br>f = freque              | FCN value to match<br>it from Figure 14.1<br>scillation frequency<br>$0^3$ / ( <b>R</b> * <b>C</b> ), when<br>ncy of oscillation i<br>itor value in pF<br>up resistor value in<br>from Figure 14.1,<br>Factor (KF) for th<br><b>C</b> * <b>AV</b> +), where<br>ncy of oscillation i | h the crystal<br>, Option 2; 3<br>/ range where<br>n MHz<br>kΩ<br>Option 3; X0<br>e oscillation<br>n MHz                     | or ceramic re<br>KOSCMD = 1<br>e:<br>DSCMD = 10<br>frequency de          | x)             |                         |         |             |

| RC MO     | AL MOD<br>Choose X<br>DE (Circu<br>Choose or<br>f = 1.23(1)<br>f = freque<br>C = capac<br>R = Pull-u<br>E (Circuit<br>Choose K<br>f = KF / (<br>f = freque<br>C = capac | FCN value to match<br>it from Figure 14.1<br>scillation frequency<br>$0^3$ / ( <b>R</b> * <b>C</b> ), when<br>ncy of oscillation i<br>itor value in pF<br>up resistor value in<br>from Figure 14.1,<br>Factor (KF) for th<br><b>C</b> * <b>AV</b> +), where                         | ch the crystal<br>, Option 2; 3<br>y range where<br>re<br>n MHz<br>kΩ<br>Option 3; XC<br>e oscillation<br>n MHz<br>L1, XTAL2 | or ceramic re<br>KOSCMD = 10<br>DSCMD = 10<br>frequency de<br>pins in pF | x)             |                         |         |             |

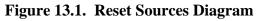

Table 15.1. Crossbar Priority Decode

In the Priority Decode Table, a dot ( $\bullet$ ) is used to show the external Port I/O pin (column) to which each signal (row) can be assigned by the user application code via programming registers XBR2, XBR1, and XBR0.

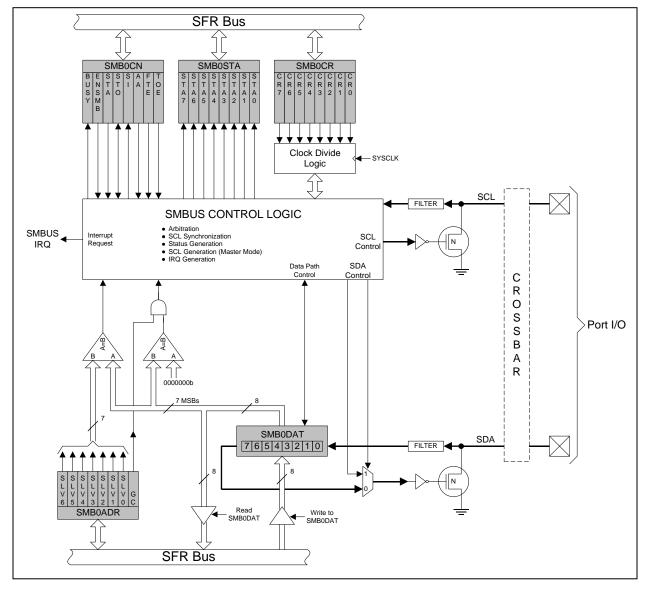

## 16. SMBus / I2C Bus

The SMBus serial I/O interface is compliant with the System Management Bus Specification, version 1.1. It is a two-wire, bi-directional serial bus, which is also compatible with the  $I^2C$  serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to  $1/8^{th}$  of the system clock if desired (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is used to accommodate devices with different speed capabilities on the same bus.

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver, and data transfers from an addressed slave transmitter to a master receiver. The master device initiates both types of data transfers and provides the serial clock pulses. The SMBus interface may operate as a master or a slave. Multiple master devices on the same bus are also supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration.

Figure 16.1. SMBus Block Diagram

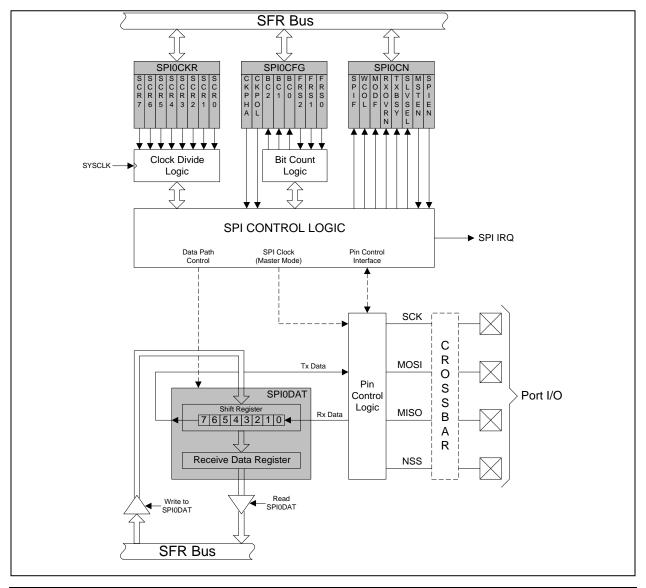

# **17. SERIAL PERIPHERAL INTERFACE BUS**

The Serial Peripheral Interface (SPI) provides access to a four-wire, full-duplex, serial bus. SPI supports the connection of multiple slave devices to a master device on the same bus. A separate slave-select signal (NSS) is used to select a slave device and enable a data transfer between the master and the selected slave. Multiple masters on the same bus are also supported. Collision detection is provided when two or more masters attempt a data transfer at the same time. The SPI can operate as either a master or a slave. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency.

When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less that 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of <sup>1</sup>/<sub>4</sub> the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock.

## Figure 17.1. SPI Block Diagram

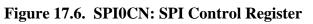

| R/W   | R/W                                                                                    | R/W                                            | R/W                                                  | R             | R               | R/W            | R/W                       | Reset Value         |

|-------|----------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|---------------|-----------------|----------------|---------------------------|---------------------|

| SPIF  | WCOL                                                                                   | MODF                                           | RXOVRN                                               | TXBSY         | SLVSEL          | MSTEN          | SPIEN                     | 00000000            |

| Bit7  | Bit6                                                                                   | Bit5                                           | Bit4                                                 | Bit3          | Bit2            | Bit1           | Bit0<br>(bit addressable) | SFR Address<br>0xF8 |

| Bit7: | SPIF: SPI Inte<br>This bit is set<br>setting this bit<br>not automatica                | to logic 1 by causes the (                     | CPU to vector                                        | to the SPI0   | interrupt serv  | vice routine.  |                           |                     |

| Bit6: | WCOL: Write<br>This bit is set<br>the SPI data re<br>software.                         | to logic 1 by                                  | hardware (an                                         |               |                 |                |                           |                     |

| Bit5: | MODF: Mode<br>This bit is set<br>collision is de<br>hardware. It r                     | to logic 1 by tected (NSS                      | is low and MS                                        | STEN $= 1$ ). |                 |                |                           |                     |

| Bit4: | RXOVRN: Re<br>This bit is set<br>buffer still hol<br>is shifted into<br>must be cleare | to logic 1 by<br>ds unread da<br>the SPI shift | y hardware (an<br>ata from a prev<br>t register. Thi | vious transfe | er and the last | bit of the cu  | rrent transfer            |                     |

| Bit3: | TXBSY: Tran<br>This bit is set<br>cleared by har                                       | to logic 1 by                                  | hardware wh                                          |               | mode transfe    | r is in progre | ss. It is                 |                     |

| Bit2: | SLVSEL: Slav<br>This bit is set<br>is cleared to lo                                    | to logic 1 wl                                  | henever the N                                        | -             | -               | t is enabled a | s a slave. It             |                     |

| Bit1: | MSTEN: Mas<br>0: Disable mas<br>1: Enable mas                                          | ster mode.                                     | Operate in slav                                      |               |                 |                |                           |                     |

| Bit0: | SPIEN: SPI E<br>This bit enable<br>0: SPI disable                                      | es/disables tl                                 | he SPI.                                              |               |                 |                |                           |                     |

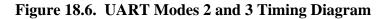

### 18.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate

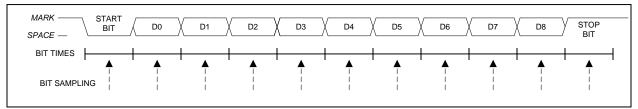

Mode 2 provides asynchronous, full-duplex communication using a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit (see timing diagram in Figure 18.6). On transmit, the ninth data bit is determined by the value in TB8 (SCON.3). It can be assigned the value of the parity flag P in the PSW or used in multiprocessor communications. On receive, the ninth data bit goes into RB8 (SCON.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit (SCON.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF receive register if the following conditions are met: RI must be logic 0, and if SM2 is logic 1, the 9<sup>th</sup> bit must be logic 1.

If these conditions are met, the eight bits of data are stored in SBUF, the ninth bit is stored in RB8 and the RI flag is set. If these conditions are not met, SBUF and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI are set.

The baud rate in Mode 2 is a direct function of the system clock frequency as follows:

Mode 2 Baud Rate =  $2^{SMOD} * (SYSCLK / 64)$ .

The SMOD bit (PCON.7) selects whether to divide SYSCLK by 32 or 64. In the formula, 2 is raised to the power SMOD, resulting in a baud rate of either 1/32 or 1/64 of the system clock frequency. On reset, the SMOD bit is logic 0, thus selecting the lower speed baud rate by default.

### 18.1.4. Mode 3: 9-Bit UART, Variable Baud Rate

Mode 3 is the same as Mode 2 in all respects except the baud rate is variable. The baud rate is determined in the same manner as for Mode 1. Mode 3 operation transmits 11 bits: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. Timer 1 or Timer 2 overflows generate the baud rate just as with Mode 1. In summary, Mode 3 transmits using the same protocol as Mode 2 but with Mode 1 baud rate generation.

| R/W     | R/W          | R/W                         | R/W                                     | R/W             | R/W             | R/W            | R/W                          | Reset Valu         |  |  |  |  |

|---------|--------------|-----------------------------|-----------------------------------------|-----------------|-----------------|----------------|------------------------------|--------------------|--|--|--|--|

| SM0     | SM1          | SM2                         | REN                                     | TB8             | RB8             | TI             | RI                           | 0000000            |  |  |  |  |

| Bit7    | Bit6         | Bit5                        | Bit4                                    | Bit3            | Bit2            | Bit1           | Bit0<br>(bit addressable)    | SFR Addres<br>0x98 |  |  |  |  |

|         |              |                             |                                         |                 |                 |                |                              |                    |  |  |  |  |

| Bits7-6 |              |                             | Operation Mode                          |                 |                 |                |                              |                    |  |  |  |  |

|         |              |                             | rial Port Operati                       | on Mode.        |                 |                |                              |                    |  |  |  |  |

|         | SM0          |                             | Iode                                    |                 |                 |                |                              |                    |  |  |  |  |

|         | 0            |                             | Iode 0: Synchron                        |                 | David Data      |                |                              |                    |  |  |  |  |

|         | 1            |                             | Iode 1: 8-Bit UA<br>Iode 2: 9-Bit UA    |                 |                 |                |                              |                    |  |  |  |  |

|         | 1            |                             | Iode 3: 9-Bit UA                        | ,               |                 |                |                              |                    |  |  |  |  |

| 1       | -            | 1 1,                        |                                         | , ·             |                 |                |                              |                    |  |  |  |  |

| Bit5:   | SM2: Mul     | ltiprocessor C              | Communication I                         | Enable.         |                 |                |                              |                    |  |  |  |  |

|         | The function | ion of this bit             | is dependent on                         | the Serial Po   | ort Operation   | Mode.          |                              |                    |  |  |  |  |

|         | Mode 0: N    |                             |                                         |                 |                 |                |                              |                    |  |  |  |  |

|         |              | Checks for val              |                                         | 1               |                 |                |                              |                    |  |  |  |  |

|         |              |                             | of stop bit is ign<br>be activated if s |                 | ia laval 1      |                |                              |                    |  |  |  |  |

|         |              |                             | cessor Commu                            |                 |                 |                |                              |                    |  |  |  |  |

|         |              | 1                           | of ninth bit is ig                      |                 | DIC.            |                |                              |                    |  |  |  |  |

|         |              |                             | an interrupt is                         |                 | ly when the n   | inth bit is lo | gic 1.                       |                    |  |  |  |  |

|         |              |                             | 1                                       | 6               |                 |                | 0                            |                    |  |  |  |  |

| Bit4:   |              | REN: Receive Enable.        |                                         |                 |                 |                |                              |                    |  |  |  |  |

|         |              |                             | es the UART rec                         | eiver.          |                 |                |                              |                    |  |  |  |  |

|         |              | 0: UART reception disabled. |                                         |                 |                 |                |                              |                    |  |  |  |  |

|         | I: UART      | reception en                | abled.                                  |                 |                 |                |                              |                    |  |  |  |  |

| Bit3:   | TB8: Nint    | h Transmissi                | on Bit.                                 |                 |                 |                |                              |                    |  |  |  |  |

|         |              |                             | oit will be assign                      |                 |                 |                | des 2 and 3. It              |                    |  |  |  |  |

|         | is not used  | 1 in Modes 0                | and 1. Set or cl                        | eared by soft   | ware as requi   | red.           |                              |                    |  |  |  |  |

| Bit2:   | RB8: Nint    | th Receive Bi               | t.                                      |                 |                 |                |                              |                    |  |  |  |  |

|         | The bit is   | assigned the                | logic level of the                      | e ninth bit rec | eived in Mod    | les 2 and 3.   | In Mode 1, if                |                    |  |  |  |  |

|         |              | gic 0, RB8 is               | assigned the log                        | ic level of th  | e received sto  | p bit. RB8     | is not used in               |                    |  |  |  |  |

|         | Mode 0.      |                             |                                         |                 |                 |                |                              |                    |  |  |  |  |

| Bit1:   | TI: Transı   | nit Interrupt l             | Flag.                                   |                 |                 |                |                              |                    |  |  |  |  |

|         |              |                             | a byte of data ha                       | s been transr   | nitted by the U | UART (after    | r the 8 <sup>th</sup> bit in |                    |  |  |  |  |

|         |              |                             | ning of the stop                        |                 |                 |                |                              |                    |  |  |  |  |

|         |              |                             | causes the CPU                          |                 | the UART int    | terrupt servi  | ce routine.                  |                    |  |  |  |  |

|         | This bit m   | ust be cleared              | d manually by so                        | oftware         |                 |                |                              |                    |  |  |  |  |

| Bit0:   | RI: Receiv   | ve Interrupt F              | lag.                                    |                 |                 |                |                              |                    |  |  |  |  |

|         |              |                             | a byte of data ha                       | s been receiv   | ed by the UA    | RT (after th   | e 8 <sup>th</sup> bit in     |                    |  |  |  |  |

|         |              |                             | p bit in other mo                       |                 |                 |                |                              |                    |  |  |  |  |

|         |              |                             | oled, setting this                      |                 |                 | or to the UA   | ART interrupt                |                    |  |  |  |  |