# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 20MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 16                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x10b; D/A 2x12b                                           |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f011-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Table 5.1.    12-Bit ADC Electrical Characteristics.                       |    |

|-----|----------------------------------------------------------------------------|----|

|     | Table 5.1.    12-Bit ADC Electrical Characteristics.                       |    |

| 6.  | ADC (10-Bit, C8051F010/1/2/5/6/7 Only)                                     | 40 |

|     | Figure 6.1. 10-Bit ADC Functional Block Diagram                            |    |

|     | 6.1. Analog Multiplexer and PGA                                            |    |

|     | 6.2. ADC Modes of Operation                                                |    |

|     | Figure 6.2. 10-Bit ADC Track and Conversion Example Timing                 |    |

|     | Figure 6.3. Temperature Sensor Transfer Function                           |    |

|     | Figure 6.4. AMX0CF: AMUX Configuration Register (C8051F01x)                |    |

|     | Figure 6.5. AMX0SL: AMUX Channel Select Register (C8051F01x)               | 43 |

|     | Figure 6.6. ADC0CF: ADC Configuration Register (C8051F01x)                 | 44 |

|     | Figure 6.7. ADC0CN: ADC Control Register (C8051F01x)                       | 45 |

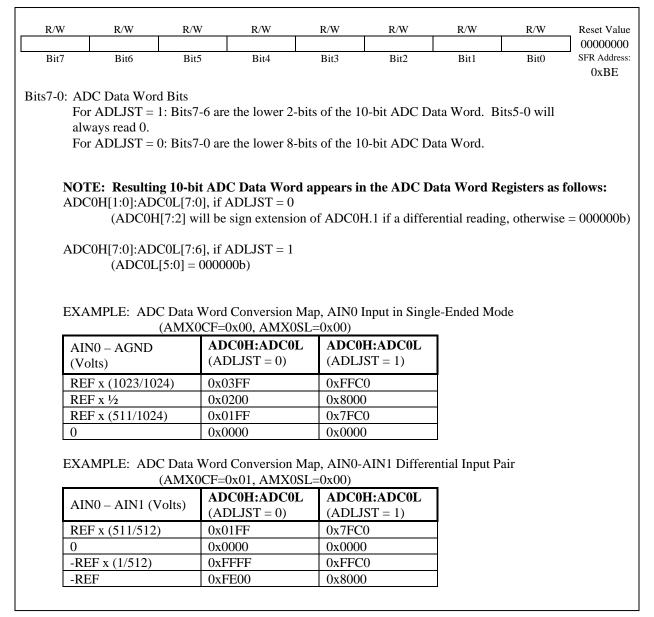

|     | Figure 6.8. ADC0H: ADC Data Word MSB Register (C8051F01x)                  | 46 |

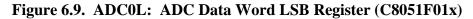

|     | Figure 6.9. ADC0L: ADC Data Word LSB Register (C8051F01x)                  | 46 |

|     | 6.3. ADC Programmable Window Detector                                      | 47 |

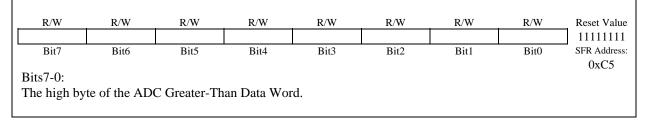

|     | Figure 6.10. ADC0GTH: ADC Greater-Than Data High Byte Register (C8051F01x) | 47 |

|     | Figure 6.11. ADC0GTL: ADC Greater-Than Data Low Byte Register (C8051F01x)  | 47 |

|     | Figure 6.12. ADC0LTH: ADC Less-Than Data High Byte Register (C8051F01x)    |    |

|     | Figure 6.13. ADC0LTL: ADC Less-Than Data Low Byte Register (C8051F01x)     |    |

|     | Figure 6.14. 10-Bit ADC Window Interrupt Examples, Right Justified Data    | 48 |

|     | Figure 6.15. 10-Bit ADC Window Interrupt Examples, Left Justified Data     |    |

|     | Figure 6.15. 10-Bit ADC Window Interrupt Examples, Left Justified Data     |    |

|     | Table 6.1.    10-Bit ADC Electrical Characteristics.                       |    |

|     | Table 6.1.    10-Bit ADC Electrical Characteristics.                       |    |

| 7.  | DACs, 12 BIT VOLTAGE MODE                                                  | 51 |

|     | Figure 7.1. DAC Functional Block Diagram                                   |    |

|     | Figure 7.2. DAC0H: DAC0 High Byte Register                                 |    |

|     | Figure 7.3. DAC0L: DAC0 Low Byte Register                                  |    |

|     | Figure 7.4. DAC0CN: DAC0 Control Register                                  |    |

|     | Figure 7.5. DAC1H: DAC1 High Byte Register                                 |    |

|     | Figure 7.6. DAC1L: DAC1 Low Byte Register                                  |    |

|     | Figure 7.7. DAC1CN: DAC1 Control Register                                  |    |

|     | Table 7.1. DAC Electrical Characteristics                                  |    |

| 8.  | COMPARATORS                                                                |    |

|     | Figure 8.1. Comparator Functional Block Diagram                            | 55 |

|     | Figure 8.2. Comparator Hysteresis Plot                                     |    |

|     | Figure 8.3. CPT0CN: Comparator 0 Control Register                          |    |

|     | Figure 8.4. CPT1CN: Comparator 1 Control Register                          |    |

|     | Table 8.1. Comparator Electrical Characteristics                           |    |

| 9.  | VOLTAGE REFERENCE                                                          | 60 |

|     | Figure 9.1. Voltage Reference Functional Block Diagram                     | 60 |

|     | Figure 9.2. REF0CN: Reference Control Register                             | 61 |

|     | Table 9.1. Reference Electrical Characteristics                            | 61 |

| 10. | CIP-51 CPU                                                                 | 62 |

|     | Figure 10.1. CIP-51 Block Diagram                                          | 62 |

|     | 10.1. INSTRUCTION SET.                                                     |    |

|     | Table 10.1. CIP-51 Instruction Set Summary                                 | 65 |

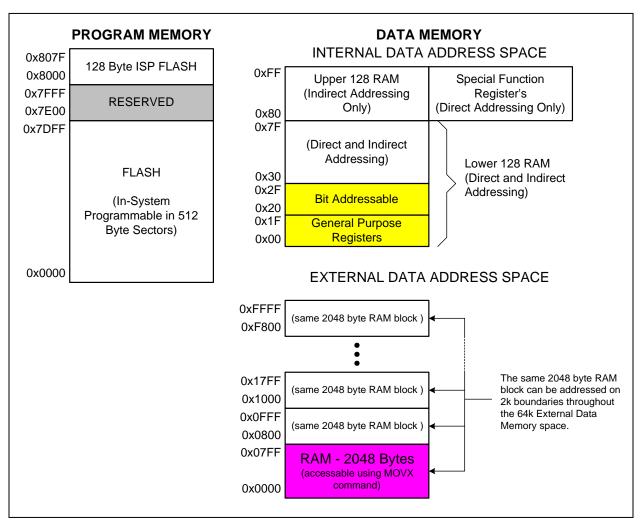

|     | 10.2. MEMORY ORGANIZATION                                                  |    |

|     | Figure 10.2. Memory Map                                                    |    |

|     | 10.3. SPECIAL FUNCTION REGISTERS                                           |    |

|     | Table 10.2. Special Function Register Memory Map                           | 70 |

|     | Table 10.3. Special Function Registers                                     | 70 |

|     | Figure 10.3. SP: Stack Pointer                                             |    |

|     | Figure 10.4. DPL: Data Pointer Low Byte                                    | 74 |

| Table 21.1. Boundary Data Register Bit Definitions | 165 |

|----------------------------------------------------|-----|

| Figure 21.2. DEVICEID: JTAG Device ID Register     |     |

| 21.2. Flash Programming Commands                   | 167 |

| Figure 21.3. FLASHCON: JTAG Flash Control Register |     |

| Figure 21.4. FLASHADR: JTAG Flash Address Register | 168 |

| Figure 21.5. FLASHDAT: JTAG Flash Data Register    | 169 |

| Figure 21.6. FLASHSCL: JTAG Flash Scale Register   |     |

| 21.3. Debug Support                                | 170 |

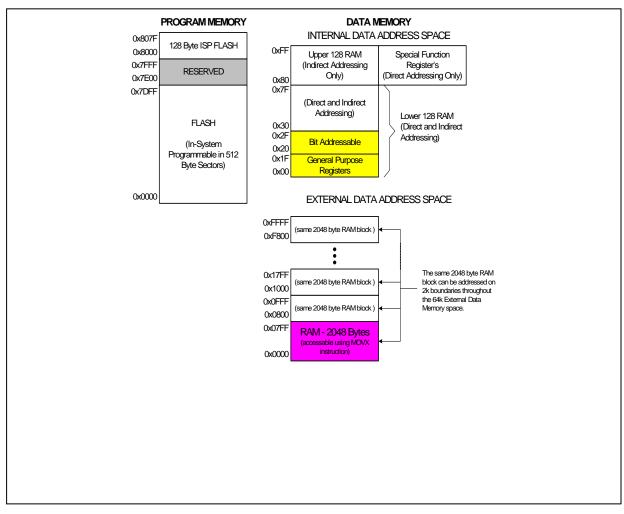

#### 1.2. On-Board Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general-purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The CIP-51 in the C8051F005/06/07/15/16/17 MCUs additionally has a 2048 byte RAM block in the external data memory address space. This 2048 byte block can be addressed over the entire 64k external data memory address range (see Figure 1.6).

The MCU's program memory consists of 32k + 128 bytes of FLASH. This memory may be reprogrammed insystem in 512 byte sectors, and requires no special off-chip programming voltage. The 512 bytes from addresses 0x7E00 to 0x7FFF are reserved for factory use. There is also a single 128-byte sector at address 0x8000 to 0x807F, which may be useful as a small table for software constants or as additional program space. See Figure 1.6 for the MCU system memory map.

#### Figure 1.6. On-Board Memory Map

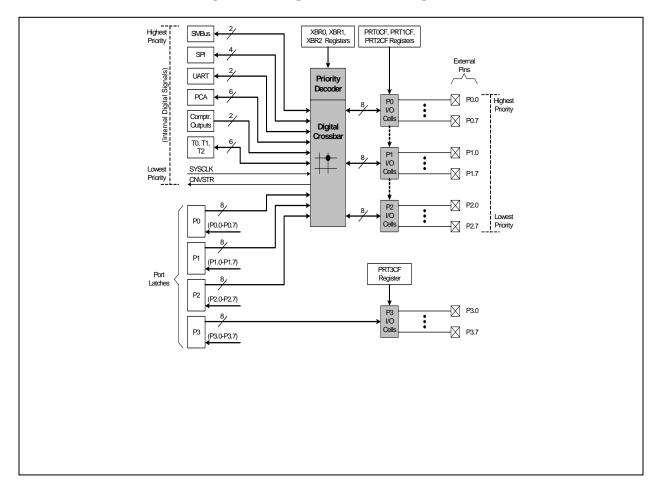

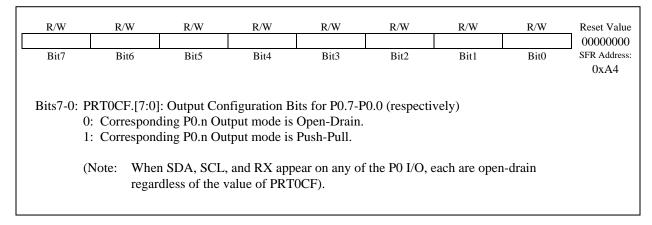

#### 1.4. Programmable Digital I/O and Crossbar

The standard 8051 Ports (0, 1, 2, and 3) are available on the MCUs. All four ports are pinned out on the F000/05/10/15. Ports 0 and 1 are pinned out on the F001/06/11/16, and only Port 0 is pinned out on the F002/07/12/17. The Ports not pinned out are still available for software use as general purpose registers. The Port I/O behave like the standard 8051 with a few enhancements.

Each Port I/O pin can be configured as either a push-pull or open-drain output. Also, the "weak pull-ups" which are normally fixed on an 8051 can be globally disabled, providing additional power saving capabilities for low power applications.

Perhaps the most unique enhancement is the Digital Crossbar. This is essentially a large digital switching network that allows mapping of internal digital system resources to Port I/O pins on P0, P1, and P2. (See Figure 1.8.) Unlike microcontrollers with standard multiplexed digital I/O, all combinations of functions are supported.

The on-board counter/timers, serial buses, HW interrupts, ADC Start of Conversion input, comparator outputs, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for his particular application.

Figure 1.8. Digital Crossbar Diagram

| R/W          | R/W             | R/W           | R/W            | R/W                                      | R/W             | R/W            | R/W               | Reset Value |

|--------------|-----------------|---------------|----------------|------------------------------------------|-----------------|----------------|-------------------|-------------|

| ADCE         | N ADCTM         | ADCINT        | ADBUSY         | ADSTM1                                   | ADSTM0          | ADWINT         | ADLJST            | 0000000     |

| Bit7         | Bit6            | Bit5          | Bit4           | Bit3                                     | Bit2            | Bit1           | Bit0              | SFR Addres  |

|              |                 |               |                |                                          |                 |                | (bit addressable) | 0xE8        |

| Bit7:        | ADCEN: ADC      | Enable Bit    |                |                                          |                 |                |                   |             |

|              | 0: ADC Disabl   | ed. ADC is i  | n low power    | shutdown.                                |                 |                |                   |             |

|              | 1: ADC Enable   |               |                |                                          | onversions.     |                |                   |             |

| Bit6:        | ADCTM: ADC      |               |                | •                                        |                 |                |                   |             |

|              | 0: When the A   | DC is enable  | d, tracking is | always done                              | unless a con    | version is in  | process           |             |

|              | 1: Tracking De  |               |                | -                                        |                 |                | -                 |             |

|              | ADST            | M1-0:         |                |                                          |                 |                |                   |             |

|              | 00: Ti          | acking starts | with the writ  | te of 1 to AD                            | BUSY and la     | asts for 3 SA  | R clocks          |             |

|              | 01: Tı          | acking starte | d by the over  | flow of Time                             | er 3 and last f | For 3 SAR clo  | ocks              |             |

|              | 10: A           | DC tracks on  | ly when CNV    | /STR input is                            | s logic low     |                |                   |             |

|              | 11: Ti          | acking starte | d by the over  | flow of Time                             | er 2 and last f | for 3 SAR clo  | ocks              |             |

| Bit5:        | ADCINT: ADC     | C Conversion  | Complete In    | terrupt Flag                             |                 |                |                   |             |

|              | (Must be cleare |               |                |                                          |                 |                |                   |             |

|              | 0: ADC has no   |               |                |                                          | e last time thi | s flag was cl  | eared             |             |

|              | 1: ADC has co   |               | a conversion   |                                          |                 |                |                   |             |

| Bit4:        | ADBUSY: AD      | C Busy Bit    |                |                                          |                 |                |                   |             |

|              | Read            |               |                |                                          |                 |                |                   |             |

|              | 0: ADC Conve    |               |                |                                          |                 | since a reset. | The falling       |             |

|              |                 | BUSY genera   |                | ipt when ena                             | bled.           |                |                   |             |

|              | 1: ADC Busy of  | converting da | ta             |                                          |                 |                |                   |             |

|              | Write           |               |                |                                          |                 |                |                   |             |

|              | 0: No effect    |               |                |                                          |                 |                |                   |             |

|              | 1: Starts ADC   |               |                |                                          |                 |                |                   |             |

| Bits3-2:     | ADSTM1-0: A     |               |                |                                          |                 |                |                   |             |

|              | 00: ADC conv    |               |                |                                          |                 |                |                   |             |

|              | 01: ADC conv    |               |                |                                          |                 |                |                   |             |

|              | 10: ADC conv    |               |                |                                          |                 |                |                   |             |

| <b>D</b> . 4 | 11: ADC conv    |               | •              |                                          | her 2           |                |                   |             |

| Bit1:        | ADWINT: AD      |               |                | rupt Flag                                |                 |                |                   |             |

|              | (Must be cleare |               |                |                                          |                 |                |                   |             |

|              | 0: ADC Windo    |               |                |                                          | urred           |                |                   |             |

| D'/0         | 1: ADC Windo    |               |                | n occurred                               |                 |                |                   |             |

| Bit0:        | ADLJST: ADC     |               |                | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. |                 |                |                   |             |

|              | 0: Data in ADC  |               |                |                                          |                 |                |                   |             |

|              | 1: Data in ADO  | LUH:ADCUL     | Registers is   | iert justified                           |                 |                |                   |             |

|              |                 |               |                |                                          |                 |                |                   |             |

|              |                 |               |                |                                          |                 |                |                   |             |

#### Figure 6.7. ADC0CN: ADC Control Register (C8051F01x)

|            | rigure o.     | o. ADCUI     | I: ADC D       | ata woru     | wisd keg      | ister (Cou    | SIFUIX)       |              |

|------------|---------------|--------------|----------------|--------------|---------------|---------------|---------------|--------------|

| R/W        | R/W           | R/W          | R/W            | R/W          | R/W           | R/W           | R/W           | Reset Value  |

|            |               |              |                |              |               |               |               | 00000000     |

| Bit7       | Bit6          | Bit5         | Bit4           | Bit3         | Bit2          | Bit1          | Bit0          | SFR Address: |

|            |               |              |                |              |               |               |               | 0xBF         |

|            |               |              |                |              |               |               |               |              |

| Bits7-0: A | DC Data Wor   | d Bits       |                |              |               |               |               |              |

| E          | or ADLJST =   | 1. Unner 8-h | its of the 10- | hit ADC Dat  | a Word        |               |               |              |

|            |               |              |                |              |               |               | 2 hits of the |              |

|            | or $ADLJST =$ |              | e the sign ext | ension of Bi | 1. Bits 1-0 a | ire the upper | 2-bits of the |              |

| 10         | )-bit ADC Dat | ta Word.     |                |              |               |               |               |              |

#### Figure 6.8. ADC0H: ADC Data Word MSB Register (C8051F01x)

#### 6.3. ADC Programmable Window Detector

The ADC programmable window detector is very useful in many applications. It continuously compares the ADC output to user-programmed limits and notifies the system when an out-of-band condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (ADWINT in ADC0CN) can also be used in polled mode. The high and low bytes of the reference words are loaded into the ADC Greater-Than and ADC Less-Than registers (ADC0GTH, ADC0GTL, ADC0LTH, and ADC0LTL). Figure 6.14 and Figure 6.15 show example comparisons for reference. Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADC0GTx and ADC0LTx registers.

#### Figure 6.10. ADC0GTH: ADC Greater-Than Data High Byte Register (C8051F01x)

#### Figure 6.11. ADC0GTL: ADC Greater-Than Data Low Byte Register (C8051F01x)

| Bit7     Bit6     Bit5     Bit4     Bit3     Bit2     Bit1     Bit0       Bits7-0: | 11111111<br>SFR Address: |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------|--------------------------|--|--|--|--|--|--|--|--|

| Bits7-0:                                                                           | 0xC4                     |  |  |  |  |  |  |  |  |

|                                                                                    | 0.101                    |  |  |  |  |  |  |  |  |

| The low byte of the ADC Greater-Than Data Word.                                    |                          |  |  |  |  |  |  |  |  |

| Definition:<br>ADC Greater-Than Data Word = ADC0GTH:ADC0GTL                        |                          |  |  |  |  |  |  |  |  |

#### Figure 6.12. ADC0LTH: ADC Less-Than Data High Byte Register (C8051F01x)

| R/W         | R/W          | R/W         | R/W              | R/W  | R/W  | R/W  | R/W  | Reset Value          |

|-------------|--------------|-------------|------------------|------|------|------|------|----------------------|

| Bit7        | Bit6         | Bit5        | Bit4             | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xC7 |

| Bits7-0:    |              |             | <b>D</b> . 111 1 |      |      |      |      |                      |

| The high by | te of the AD | C Less-Than | Data Word.       |      |      |      |      |                      |

#### Figure 6.13. ADC0LTL: ADC Less-Than Data Low Byte Register (C8051F01x)

| R/W                      | R/W            | R/W           | R/W         | R/W        | R/W  | R/W  | R/W  | Reset Value                      |

|--------------------------|----------------|---------------|-------------|------------|------|------|------|----------------------------------|

| Bit7                     | Bit6           | Bit5          | Bit4        | Bit3       | Bit2 | Bit1 | Bit0 | 00000000<br>SFR Address:<br>0xC6 |

| Bits7-0:<br>These bits : | are the low by | rte of the AD | C Less-Than | Data Word  |      |      |      |                                  |

| Definition:              |                | te of the AD  | C Less-Than | Data Word. |      |      |      |                                  |

|                          | Than Data W    | ord = ADC0    | LTH:ADC0I   | LTL        |      |      |      |                                  |

|                          |                |               |             |            |      |      |      |                                  |

SILICON LABS

### Table 6.1. 10-Bit ADC Electrical Characteristics

|                              | REF = 2.40V (REFBE=0), PGA Gain = 1, -    | 40°C to +8   |            | s otherwise |        |

|------------------------------|-------------------------------------------|--------------|------------|-------------|--------|

| PARAMETER                    | CONDITIONS                                | MIN          | ТҮР        | MAX         | UNITS  |

| DC ACCURACY                  |                                           |              |            |             |        |

| Resolution                   |                                           |              | 10         |             | bits   |

| Integral Nonlinearity        |                                           |              | ± ½        | ± 1         | LSB    |

| Differential Nonlinearity    | Guaranteed Monotonic                      |              | ± 1/2      | ± 1         | LSB    |

| Offset Error                 |                                           |              | ± 0.5      |             | LSB    |

| Full Scale Error             | Differential mode                         |              | -1.5 ±     |             | LSB    |

|                              |                                           |              | 0.5        |             |        |

| Offset Temperature           |                                           |              | ± 0.25     |             | ppm/°C |

| Coefficient                  |                                           |              |            |             | 11     |

| DYNAMIC PERFORMAN            | CE (10kHz sine-wave input, 0 to –1dB of f | ull scale, 1 | 00ksps)    |             |        |

| Signal-to-Noise Plus         |                                           | 59           | 61         |             | dB     |

| Distortion                   |                                           |              |            |             |        |

| Total Harmonic Distortion    | Up to the 5 <sup>th</sup> harmonic        |              | -70        |             | dB     |

| Spurious-Free Dynamic        |                                           |              | 80         |             | dB     |

| Range                        |                                           |              |            |             |        |

| CONVERSION RATE              |                                           |              |            |             |        |

| Conversion Time in SAR       |                                           | 16           |            |             | clocks |

| Clocks                       |                                           |              |            |             |        |

| SAR Clock Frequency          | C8051F000, 'F001, 'F002                   |              |            | 2.0         | MHz    |

|                              | C8051F005, 'F006, 'F007                   |              |            | 2.5         | MHz    |

| Track/Hold Acquisition       |                                           | 1.5          |            |             | μs     |

| Time                         |                                           |              |            |             |        |

| Throughput Rate              |                                           |              |            | 100         | ksps   |

| ANALOG INPUTS                | 1                                         | -            | 1          |             |        |

| Voltage Conversion Range     | Single-ended Mode (AINn – AGND)           | 0            |            | VREF        | V      |

|                              | Differential Mode  (AINn+) – (AINm-)      |              |            | - 1LSB      |        |

| Input Voltage                | Any AINn pin                              | AGND         |            | AV+         | V      |

| Input Capacitance            |                                           |              | 10         |             | pF     |

| TEMPERATURE SENSOR           |                                           | 1            | 1          |             |        |

| Linearity                    |                                           |              | $\pm 0.20$ |             | °C     |

| Absolute Accuracy            |                                           |              | ± 3        |             | °C     |

| Gain                         | PGA Gain = 1                              |              | 2.86       |             | mV/°C  |

| Gain Error $(\pm 1\sigma)$   | PGA Gain = 1                              |              | ± 33.5     |             | μV/°C  |

| Offset                       | PGA Gain = 1, Temp = $0^{\circ}$ C        |              | 776        |             | mV     |

| Offset Error $(\pm 1\sigma)$ | PGA Gain = 1, Temp = $0^{\circ}$ C        |              | ± 8.51     |             | mV     |

| POWER SPECIFICATION          | · •                                       |              |            |             |        |

| Power Supply Current (AV+    | Operating Mode, 100ksps                   |              | 450        | 900         | μΑ     |

| supplied to ADC)             |                                           |              |            |             |        |

| Power Supply Rejection       |                                           |              | ± 0.3      |             | mV/V   |

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's maximum system clock at 25MHz, it has a peak throughput of 25MIPS. The CIP-51 has a total of 109 instructions. The number of instructions versus the system clock cycles required to execute them is as follows:

| Instructions      | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

|-------------------|----|----|-----|----|-----|---|-----|---|---|

| Clocks to Execute | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

#### **Programming and Debugging Support**

A JTAG-based serial interface is provided for in-system programming of the Flash program memory and communication with on-chip debug support circuitry. The reprogrammable Flash can also be read and changed a single byte at a time by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support circuitry facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints and watch points, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive and non-invasive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Laboratories and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, macro assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via its JTAG interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

#### **10.1. INSTRUCTION SET**

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>TM</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>TM</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### **10.1.1. Instruction and CPU Timing**

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 10.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 10.1.2. MOVX Instruction and Program Memory

The MOVX instruction is typically used to access external data memory. In the CIP-51, the MOVX instruction can access the on-chip program memory space implemented as reprogrammable Flash memory using the control bits in the PSCTL register (see Figure 11.1). This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. For the products with RAM mapped into external data memory space (C8051F005/06/07/15/16/17), MOVX is still used to read/write this memory with the PSCTL

Figure 10.2. Memory Map

#### 10.2.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

The MCUs also have built-in hardware for a stack record. The stack record is a 32-bit shift register, where each Push or increment SP pushes one record bit onto the register, and each Call or interrupt pushes two record bits onto the register. (A Pop or decrement SP pops one record bit, and a Return pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the Stack, and can notify the debug software even with the MCU running full-speed debug.

| is bit sets th<br>XTLVLD i<br>XTLVLD i<br>served: Mus<br>7: External<br>is bit sets th<br>External In<br>External In<br>External In<br>External In<br>External In<br>External In               | PX7<br>Bit5<br>Bit5<br>Bit5<br>Bit5<br>Bit5<br>Bit5<br>Bit5<br>Bit5                                                                                                                                                         | the XTLVL<br>o low priori<br>o high prior<br>eads 0.<br>Priority Cont<br>the External<br>to low priori<br>Priority Cont<br>the External<br>to low priori                                                                                                                                                                                     | ty level.<br>ity level.<br>trol.<br>I Interrupt 7.<br>ity level.<br>rity level.<br>trol.<br>I Interrupt 6.<br>ity level.                                                                                                                                                                                                                                                                                                                                                                       | PX4<br>Bit2                                                                                          | PADC0<br>Bit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PT3<br>Bit0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00000000<br>SFR Addres:<br>0xF7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CVLD: Exte<br>is bit sets th<br>XTLVLD i<br>XTLVLD i<br>served: Mus<br>7: External<br>is bit sets th<br>External In<br>External In<br>External In<br>External In<br>External In<br>External In | ernal Clock Se<br>ne priority of<br>interrupt set t<br>interrupt set t<br>st write 0. Re<br>Interrupt 7 P<br>ne priority of<br>iterrupt 7 set t<br>Interrupt 7 set t<br>Interrupt 6 P<br>ne priority of<br>iterrupt 6 set t | ource Valid<br>the XTLVL<br>o low priori<br>o high prior<br>eads 0.<br>Priority Cont<br>the External<br>to low priori<br>Priority Cont<br>the External<br>to low priori                                                                                                                                                                      | (XTLVLD) I<br>D interrupt.<br>ty level.<br>ity level.<br>trol.<br>I Interrupt 7.<br>ity level.<br>rity level.<br>trol.<br>I Interrupt 6.<br>ity level.                                                                                                                                                                                                                                                                                                                                         |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| is bit sets th<br>XTLVLD i<br>XTLVLD i<br>served: Mus<br>7: External<br>is bit sets th<br>External In<br>External In<br>External In<br>External In<br>External In<br>External In               | ne priority of<br>interrupt set t<br>interrupt set t<br>st write 0. Ro<br>Interrupt 7 P<br>ne priority of<br>iterrupt 7 set t<br>Interrupt 7 set t<br>Interrupt 6 P<br>ne priority of<br>iterrupt 6 set t                   | the XTLVL<br>o low priori<br>o high prior<br>eads 0.<br>Priority Cont<br>the External<br>to low priori<br>Priority Cont<br>the External<br>to low priori                                                                                                                                                                                     | D interrupt.<br>ty level.<br>ity level.<br>trol.<br>l Interrupt 7.<br>ity level.<br>rity level.<br>trol.<br>l Interrupt 6.<br>ity level.                                                                                                                                                                                                                                                                                                                                                       | nterrupt Pric                                                                                        | ority Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>7: External</li> <li>is bit sets th</li> <li>External In</li> <li>External In</li> <li>6: External In</li> <li>6: External In</li> <li>External In</li> <li>External In</li> </ul>    | Interrupt 7 P<br>the priority of<br>terrupt 7 set to<br>terrupt 7 set to<br>Interrupt 6 P<br>the priority of<br>terrupt 6 set to                                                                                            | Priority Cont<br>the External<br>to low priori<br>to high prior<br>Priority Cont<br>the External<br>to low priori                                                                                                                                                                                                                            | l Interrupt 7.<br>ity level.<br>rity level.<br>trol.<br>l Interrupt 6.<br>ity level.                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| is bit sets th<br>External In<br>External In<br>6: External<br>is bit sets th<br>External In<br>External In                                                                                    | ne priority of<br>Iterrupt 7 set to<br>Iterrupt 7 set to<br>Interrupt 6 P<br>ne priority of<br>Iterrupt 6 set to                                                                                                            | the External<br>to low priori<br>to high prior<br>Priority Cont<br>the External<br>to low priori                                                                                                                                                                                                                                             | l Interrupt 7.<br>ity level.<br>rity level.<br>trol.<br>l Interrupt 6.<br>ity level.                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| is bit sets th<br>External In<br>External In                                                                                                                                                   | ne priority of<br>iterrupt 6 set                                                                                                                                                                                            | the External<br>to low priori                                                                                                                                                                                                                                                                                                                | l Interrupt 6.<br>ity level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5. Extans 1                                                                                                                                                                                    |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                              | rity level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| is bit sets th<br>External In                                                                                                                                                                  |                                                                                                                                                                                                                             | the External<br>to low priori                                                                                                                                                                                                                                                                                                                | l Interrupt 5.<br>ity level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| is bit sets th<br>External In                                                                                                                                                                  | ne priority of<br>iterrupt 4 set                                                                                                                                                                                            | the External<br>to low priori                                                                                                                                                                                                                                                                                                                | l Interrupt 4.<br>ity level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| is bit sets th<br>ADC0 End                                                                                                                                                                     | ne priority of<br>l of Conversio                                                                                                                                                                                            | the ADC0 E<br>on interrupt                                                                                                                                                                                                                                                                                                                   | End of Conver<br>set to low pri-                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rsion Interru<br>ority level.                                                                        | pt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| is bit sets th<br>Timer 3 int                                                                                                                                                                  | ne priority of terrupt set to be                                                                                                                                                                                            | the Timer 3<br>low priority                                                                                                                                                                                                                                                                                                                  | interrupts.<br>level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |