# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 20MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b; D/A 2x12b                                            |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f011-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Table 5.1.    12-Bit ADC Electrical Characteristics.                       |    |

|-----|----------------------------------------------------------------------------|----|

|     | Table 5.1.    12-Bit ADC Electrical Characteristics.                       |    |

| 6.  | ADC (10-Bit, C8051F010/1/2/5/6/7 Only)                                     | 40 |

|     | Figure 6.1. 10-Bit ADC Functional Block Diagram                            |    |

|     | 6.1. Analog Multiplexer and PGA                                            |    |

|     | 6.2. ADC Modes of Operation                                                |    |

|     | Figure 6.2. 10-Bit ADC Track and Conversion Example Timing                 |    |

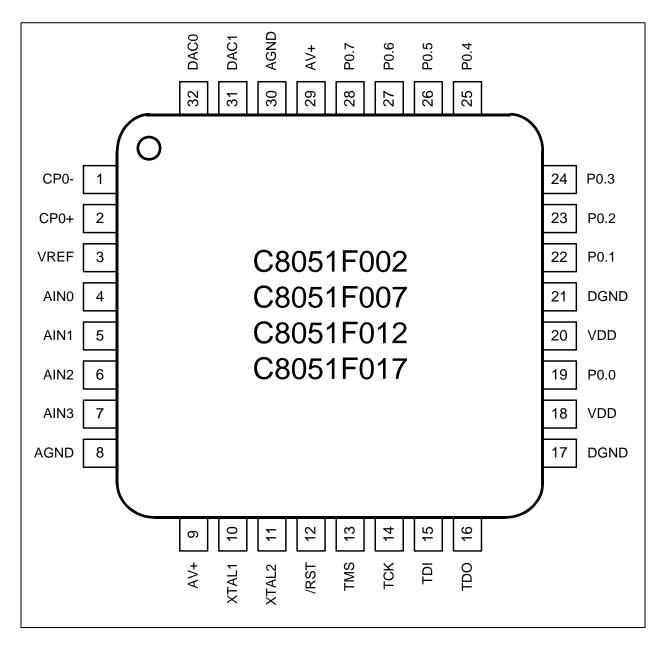

|     | Figure 6.3. Temperature Sensor Transfer Function                           |    |

|     | Figure 6.4. AMX0CF: AMUX Configuration Register (C8051F01x)                |    |

|     | Figure 6.5. AMX0SL: AMUX Channel Select Register (C8051F01x)               | 43 |

|     | Figure 6.6. ADC0CF: ADC Configuration Register (C8051F01x)                 | 44 |

|     | Figure 6.7. ADC0CN: ADC Control Register (C8051F01x)                       | 45 |

|     | Figure 6.8. ADC0H: ADC Data Word MSB Register (C8051F01x)                  | 46 |

|     | Figure 6.9. ADC0L: ADC Data Word LSB Register (C8051F01x)                  | 46 |

|     | 6.3. ADC Programmable Window Detector                                      | 47 |

|     | Figure 6.10. ADC0GTH: ADC Greater-Than Data High Byte Register (C8051F01x) | 47 |

|     | Figure 6.11. ADC0GTL: ADC Greater-Than Data Low Byte Register (C8051F01x)  | 47 |

|     | Figure 6.12. ADC0LTH: ADC Less-Than Data High Byte Register (C8051F01x)    |    |

|     | Figure 6.13. ADC0LTL: ADC Less-Than Data Low Byte Register (C8051F01x)     |    |

|     | Figure 6.14. 10-Bit ADC Window Interrupt Examples, Right Justified Data    | 48 |

|     | Figure 6.15. 10-Bit ADC Window Interrupt Examples, Left Justified Data     |    |

|     | Figure 6.15. 10-Bit ADC Window Interrupt Examples, Left Justified Data     |    |

|     | Table 6.1.    10-Bit ADC Electrical Characteristics.                       |    |

|     | Table 6.1.    10-Bit ADC Electrical Characteristics.                       |    |

| 7.  | DACs, 12 BIT VOLTAGE MODE                                                  | 51 |

|     | Figure 7.1. DAC Functional Block Diagram                                   |    |

|     | Figure 7.2. DAC0H: DAC0 High Byte Register                                 |    |

|     | Figure 7.3. DAC0L: DAC0 Low Byte Register                                  |    |

|     | Figure 7.4. DAC0CN: DAC0 Control Register                                  |    |

|     | Figure 7.5. DAC1H: DAC1 High Byte Register                                 |    |

|     | Figure 7.6. DAC1L: DAC1 Low Byte Register                                  |    |

|     | Figure 7.7. DAC1CN: DAC1 Control Register                                  |    |

|     | Table 7.1. DAC Electrical Characteristics                                  |    |

| 8.  | COMPARATORS                                                                |    |

|     | Figure 8.1. Comparator Functional Block Diagram                            | 55 |

|     | Figure 8.2. Comparator Hysteresis Plot                                     |    |

|     | Figure 8.3. CPT0CN: Comparator 0 Control Register                          |    |

|     | Figure 8.4. CPT1CN: Comparator 1 Control Register                          |    |

|     | Table 8.1. Comparator Electrical Characteristics                           |    |

| 9.  | VOLTAGE REFERENCE                                                          | 60 |

|     | Figure 9.1. Voltage Reference Functional Block Diagram                     | 60 |

|     | Figure 9.2. REF0CN: Reference Control Register                             | 61 |

|     | Table 9.1. Reference Electrical Characteristics                            | 61 |

| 10. | CIP-51 CPU                                                                 | 62 |

|     | Figure 10.1. CIP-51 Block Diagram                                          | 62 |

|     | 10.1. INSTRUCTION SET.                                                     |    |

|     | Table 10.1. CIP-51 Instruction Set Summary                                 | 65 |

|     | 10.2. MEMORY ORGANIZATION                                                  |    |

|     | Figure 10.2. Memory Map                                                    |    |

|     | 10.3. SPECIAL FUNCTION REGISTERS                                           |    |

|     | Table 10.2. Special Function Register Memory Map                           | 70 |

|     | Table 10.3. Special Function Registers                                     | 70 |

|     | Figure 10.3. SP: Stack Pointer                                             |    |

|     | Figure 10.4. DPL: Data Pointer Low Byte                                    | 74 |

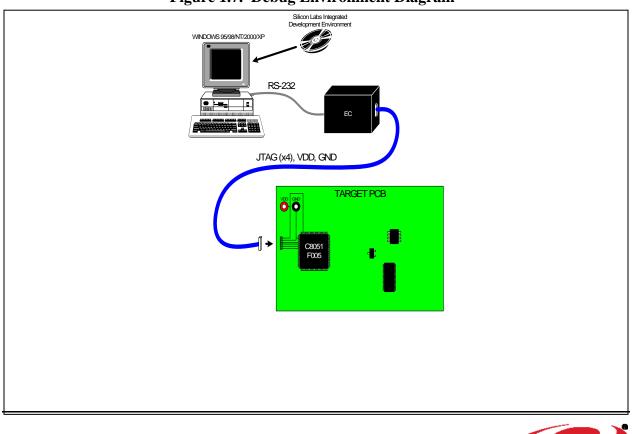

### 1.3. JTAG Debug and Boundary Scan

The C8051F000 family has on-chip JTAG and debug circuitry that provide *non-intrusive, full speed, in-circuit debug using the production part installed in the end application* using the four-pin JTAG I/F. The JTAG port is fully compliant to IEEE 1149.1, providing full boundary scan for test and manufacturing purposes.

Silicon Labs' debug system supports inspection and modification of memory and registers, breakpoints, watchpoints, a stack monitor, and single stepping. No additional target RAM, program memory, timers, or communications channels are required. All the digital and analog peripherals are functional and work correctly while debugging. All the peripherals (except for the ADC) are stalled when the MCU is halted, during single stepping, or at a breakpoint in order to keep them in sync.

The C8051F000DK, C8051F005DK, C8051F010DK, and C8051F015DK are development kits with all the hardware and software necessary to develop application code and perform in-circuit debug with the C8051F000/1/2, F005/6/7, F010/1/2, and F015/6/7 MCUs respectively. The kit includes software with a developer's studio and debugger, an integrated 8051 assembler, and an RS-232 to JTAG protocol translator module referred to as the EC. It also has a target application board with the associated MCU installed and a large prototyping area, plus the RS-232 and JTAG cables, and wall-mount power supply. The Development Kit requires a Windows 95/98/NT/2000/XP computer with one available RS-232 serial port. As shown in Figure 1.7, the PC is connected via RS-232 to the EC. A six-inch ribbon cable connects the EC to the user's application board, picking up the four JTAG pins and VDD and GND. The EC takes its power from the application board. It requires roughly 20mA at 2.7-3.6V. For applications where there is not sufficient power available from the target board, the provided power supply can be connected directly to the EC.

This is a vastly superior configuration for developing and debugging embedded applications compared to standard MCU Emulators, which use on-board "ICE Chips" and target cables and require the MCU in the application board to be socketed. Silicon Labs' debug environment both increases ease of use and preserves the performance of the precision analog peripherals.

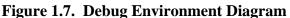

Figure 4.5. LQFP-32 Pinout Diagram

| R/W         | R/W            | R/W           | R/W           | R/W           | R/W    | R/W    | R/W    | Reset Value  |

|-------------|----------------|---------------|---------------|---------------|--------|--------|--------|--------------|

| ADCSC2      | ADCSC1         | ADCSC0        | -             | -             | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |

| Bit7        | Bit6           | Bit5          | Bit4          | Bit3          | Bit2   | Bit1   | Bit0   | SFR Address: |

|             |                |               |               |               |        |        |        | 0xBC         |

| Bits7-5. AD | CSC2-0. AL     | C SAR Conv    | version Clock | e Period Bits |        |        |        |              |

|             |                | version Clock |               |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | Conversion C  | •             |               | )      |        |        |              |

|             |                | d = 00b; Writ |               | ,             | ,<br>, |        |        |              |

|             |                | DC Internal A |               |               |        |        |        |              |

|             | ): Gain = 1    |               | 1             |               |        |        |        |              |

| 001         | : Gain = 2     |               |               |               |        |        |        |              |

| 010         | ): $Gain = 4$  |               |               |               |        |        |        |              |

| 011         | : Gain = 8     |               |               |               |        |        |        |              |

| 10x         | 10x: Gain = 16 |               |               |               |        |        |        |              |

| 11x         | : Gain $= 0.5$ | i             |               |               |        |        |        |              |

|             |                |               |               |               |        |        |        |              |

### Figure 5.6. ADC0CF: ADC Configuration Register (C8051F00x)

33

### Table 5.1. 12-Bit ADC Electrical Characteristics

| PARAMETER                                  | CONDITIONS                                | MIN           | TYP        | MAX    | UNITS      |

|--------------------------------------------|-------------------------------------------|---------------|------------|--------|------------|

| DC ACCURACY                                |                                           |               |            |        |            |

| Resolution                                 |                                           |               | 12         |        | bits       |

| Integral Nonlinearity                      |                                           |               |            | ± 1    | LSB        |

| Differential Nonlinearity                  | Guaranteed Monotonic                      |               |            | ± 1    | LSB        |

| Offset Error                               |                                           |               | -3 ± 1     |        | LSB        |

| Full Scale Error                           | Differential mode                         |               | -7 ± 3     |        | LSB        |

| Offset Temperature                         |                                           |               | ± 0.25     |        | ppm/°C     |

| Coefficient                                |                                           |               |            |        |            |

| DYNAMIC PERFORMAN                          | CE (10kHz sine-wave input, 0 to –1dB of f | full scale, 1 | 00ksps)    |        |            |

| Signal-to-Noise Plus                       |                                           | 66            | 69         |        | dB         |

| Distortion                                 |                                           |               |            |        |            |

| Total Harmonic Distortion                  | Up to the 5 <sup>th</sup> harmonic        |               | -75        |        | dB         |

| Spurious-Free Dynamic                      |                                           |               | 80         |        | dB         |

| Range                                      |                                           |               |            |        |            |

| CONVERSION RATE                            |                                           | -             | r          |        |            |

| Conversion Time in SAR                     |                                           | 16            |            |        | clocks     |

| Clocks                                     |                                           |               |            |        |            |

| SAR Clock Frequency                        | C8051F000, 'F001, 'F002                   |               |            | 2.0    | MHz        |

|                                            | C8051F005, 'F006, 'F007                   |               |            | 2.5    | MHz        |

| Track/Hold Acquisition                     |                                           | 1.5           |            |        | μs         |

| Time                                       |                                           |               |            | 100    |            |

| Throughput Rate                            |                                           |               |            | 100    | ksps       |

| ANALOG INPUTS                              |                                           |               |            |        |            |

| Voltage Conversion Range                   | Single-ended Mode (AINn – AGND)           | 0             |            | VREF   | V          |

| T , TT 1,                                  | Differential Mode  (AINn+) – (AINm-)      | A CNID        |            | - 1LSB | <b>N</b> 7 |

| Input Voltage                              | Any AINn pin                              | AGND          | 10         | AV+    | <u>V</u>   |

| Input Capacitance                          |                                           |               | 10         |        | pF         |

| TEMPERATURE SENSOR<br>Linearity            |                                           |               |            |        | 00         |

| 2                                          |                                           |               | ± 0.20     |        | °C         |

| Absolute Accuracy                          |                                           |               | $\pm 3$    |        | °C         |

| Gain                                       | PGA Gain = 1                              |               | 2.86       |        | mV/°C      |

| Gain Error $(\pm 1\sigma)$                 | PGA Gain = 1                              |               | ± 33.5     |        | μV/°C      |

| Offset                                     | PGA Gain = 1, Temp = $0^{\circ}$ C        |               | 776        |        | mV         |

| Offset Error $(\pm 1\sigma)$               | PGA Gain = 1, Temp = $0^{\circ}$ C        |               | $\pm 8.51$ |        | mV         |

| POWER SPECIFICATION                        |                                           |               |            | 1      |            |

| Power Supply Current (AV+ supplied to ADC) | Operating Mode, 100ksps                   |               | 450        | 900    | μΑ         |

| Power Supply Rejection                     |                                           |               | ± 0.3      |        | mV/V       |

Figure 6.4. AMX0CF: AMUX Configuration Register (C8051F01x)

| R/W      | R/W            | R/W            | R/W            | R/W            | R/W           | R/W            | R/W        | Reset Value  |

|----------|----------------|----------------|----------------|----------------|---------------|----------------|------------|--------------|

| -        | -              | -              | -              | AIN67IC        | AIN45IC       | AIN23IC        | AIN01IC    | 00000000     |

| Bit7     | Bit6           | Bit5           | Bit4           | Bit3           | Bit2          | Bit1           | Bit0       | SFR Address: |

|          |                |                |                |                |               |                |            | 0xBA         |

| Bits7-4: | UNUSED. Read   | d = 0000b; W   | rite = don't   | care           |               |                |            |              |

| Bit3:    | AIN67IC: AIN6  | , AIN7 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN6 and AI | N7 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN6, AIN7  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

| Bit2:    | AIN45IC: AIN4  | , AIN5 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN4 and AI | N5 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN4, AIN5  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

| Bit1:    | AIN23IC: AIN2  | , AIN3 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN2 and AI | N3 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN2, AIN3  |                |                |                | ıt pair       |                |            |              |

| Bit0:    | AIN01IC: AIN0  | , AIN1 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN0 and AI | N1 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN0, AIN1  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

|          |                |                |                |                |               |                |            |              |

| NOTE:    | The ADC Data V | Word is in 2's | s complemen    | t format for a | channels cont | figured as dif | ferential. |              |

|          |                |                |                |                |               |                |            |              |

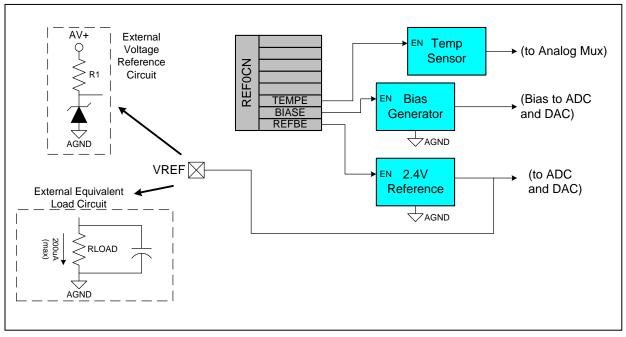

### 9. VOLTAGE REFERENCE

The voltage reference circuit consists of a 1.2V, 15ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The reference voltage on VREF can be connected to external devices in the system, as long as the maximum load seen by the VREF pin is less than 200µA to AGND (see Figure 9.1).

If a different reference voltage is required, an external reference can be connected to the VREF pin and the internal bandgap and buffer amplifier disabled in software. The external reference voltage must still be less than AV+ - 0.3V. The Reference Control Register, REF0CN (defined in Figure 9.2), provides the means to enable or disable the bandgap and buffer amplifier. The BIASE bit in REF0CN enables the bias circuitry for the ADC and DACs while the REFBE bit enables the bandgap reference and buffer amplifier which drive the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1uA (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to 1. If an external reference is used, REFBE must be set to 0 and BIASE must be set to 1. If neither the ADC nor the DAC are being used, both of these bits can be set to 0 to conserve power. The electrical specifications for the Voltage Reference are given in Table 9.1.

The temperature sensor connects to the highest order input of the A/D converter's input multiplexer (see Figure 5.1 and Figure 5.5 for details). The TEMPE bit within REFOCN enables and disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any A/D measurements performed on the sensor while disabled result in meaningless data.

Figure 9.1. Voltage Reference Functional Block Diagram

| Mnemonic                      | Description                                   | Bytes | Clock<br>Cycles |

|-------------------------------|-----------------------------------------------|-------|-----------------|

| RR A                          | Rotate A right                                | 1     | 1               |

| RRC A                         | Rotate A right through carry                  | 1     | 1               |

| SWAP A                        | Swap nibbles of A                             | 1     | 1               |

|                               | DATA TRANSFER                                 |       |                 |

| MOV A,Rn                      | Move register to A                            | 1     | 1               |

| MOV A, direct                 | Move direct byte to A                         | 2     | 2               |

| MOV A,@Ri                     | Move indirect RAM to A                        | 1     | 2               |

| MOV A,#data                   | Move immediate to A                           | 2     | 2               |

| MOV Rn,A                      | Move A to register                            | 1     | 1               |

| MOV Rn,direct                 | Move direct byte to register                  | 2     | 2               |

| MOV Rn,#data                  | Move immediate to register                    | 2     | 2               |

| MOV direct,A                  | Move A to direct byte                         | 2     | 2               |

| MOV direct,Rn                 | Move register to direct byte                  | 2     | 2               |

| MOV direct, direct            | Move direct byte to direct                    | 3     | 3               |

| MOV direct,@Ri                | Move indirect RAM to direct byte              | 2     | 2               |

| MOV direct,#data              | Move immediate to direct byte                 | 3     | 3               |

| MOV @Ri,A                     | Move A to indirect RAM                        | 1     | 2               |

| MOV @Ri,direct                | Move direct byte to indirect RAM              | 2     | 2               |

| MOV @Ri,#data                 | Move immediate to indirect RAM                | 2     | 2               |

| MOV DPTR,#data16              | Load data pointer with 16-bit constant        | 3     | 3               |

| MOVC A,@A+DPTR                | Move code byte relative DPTR to A             | 1     | 3               |

| MOVC A,@A+PC                  | Move code byte relative DFIR to A             | 1     | 3               |

| MOVC A,@A+IC<br>MOVX A,@Ri    | Move external data (8-bit address) to A       | 1     | 3               |

| MOVX @Ri,A                    | Move A to external data (8-bit address)       | 1     | 3               |

| MOVX & MOVX A, @DPTR          | Move external data (16-bit address)           | 1     | 3               |

| MOVX A, @DPTR<br>MOVX @DPTR,A | Move A to external data (16-bit address) to A | 1     | 3               |

| PUSH direct                   | Push direct byte onto stack                   | 2     | 2               |

| POP direct                    | Pop direct byte from stack                    | 2     | 2               |

|                               | Exchange register with A                      | 1     | 1               |

| XCH A,Rn<br>XCH A,direct      | Exchange direct byte with A                   | 2     | 2               |

| /                             |                                               |       |                 |

| XCH A,@Ri                     | Exchange indirect RAM with A                  | 1     | 2               |

| XCHD A,@Ri                    | Exchange low nibble of indirect RAM with A    | 1     | 2               |

| CL D C                        | BOOLEAN MANIPULATION                          | 1     | 1               |

| CLR C                         | Clear carry                                   | 1     | 1               |

| CLR bit                       | Clear direct bit                              | 2     | 2               |

| SETB C                        | Set carry                                     | 1     | 1               |

| SETB bit                      | Set direct bit                                | 2     | 2               |

| CPL C                         | Complement carry                              | 1     | 1               |

| CPL bit                       | Complement direct bit                         | 2     | 2               |

| ANL C,bit                     | AND direct bit to carry                       | 2     | 2               |

| ANL C,/bit                    | AND complement of direct bit to carry         | 2     | 2               |

| ORL C,bit                     | OR direct bit to carry                        | 2     | 2               |

| ORL C,/bit                    | OR complement of direct bit to carry          | 2     | 2               |

| MOV C,bit                     | Move direct bit to carry                      | 2     | 2               |

| MOV bit,C                     | Move carry to direct bit                      | 2     | 2               |

| JC rel                        | Jump if carry is set                          | 2     | 2/3             |

| JNC rel                       | Jump if carry not set                         | 2     | 2/3             |

| JB bit,rel                    | Jump if direct bit is set                     | 3     | 3/4             |

| JNB bit,rel                   | Jump if direct bit is not set                 | 3     | 3/4             |

| JBC bit,rel                   | Jump if direct bit is set and clear bit       | 3     | 3/4             |

| Figure 10.6. | <b>PSW: Program</b> | n Status Word |

|--------------|---------------------|---------------|

|--------------|---------------------|---------------|

| CY      | R/W                                                                               | R/W                                                                                                           | R/W                                                                       | R/W                                                             | R/W                                                | R/W                    | R/W                       | Reset Valu         |

|---------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|------------------------|---------------------------|--------------------|

|         | AC                                                                                | F0                                                                                                            | RS1                                                                       | RS0                                                             | OV                                                 | F1                     | PARITY                    | 0000000            |

| Bit7    | Bit6                                                                              | Bit5                                                                                                          | Bit4                                                                      | Bit3                                                            | Bit2                                               | Bit1                   | Bit0<br>(bit addressable) | SFR Addres<br>0xD0 |

| Bit7:   | CY: Carry Fla<br>This bit is set<br>(subtraction).                                | when the las                                                                                                  |                                                                           |                                                                 |                                                    | (addition) o           | or a borrow               |                    |

| Bit6:   | AC: Auxiliary<br>This bit is set<br>borrow from (<br>operations.                  | when the las                                                                                                  |                                                                           |                                                                 |                                                    |                        |                           |                    |

| Bit5:   | F0: User Flag<br>This is a bit-ad                                                 |                                                                                                               | eneral purpo                                                              | se flag for us                                                  | e under softw                                      | are control            |                           |                    |

| Bits4-3 | RS1-RS0: Reg<br>These bits sele                                                   |                                                                                                               |                                                                           | used during                                                     | register acces                                     | ses.                   |                           |                    |

|         | RS1 RS                                                                            | 0 Registe                                                                                                     | er Bank                                                                   | Address                                                         |                                                    |                        |                           |                    |

|         | 0 0                                                                               |                                                                                                               |                                                                           | x00-0x07                                                        |                                                    |                        |                           |                    |

|         | 0 1                                                                               |                                                                                                               |                                                                           | x08-0x0F                                                        |                                                    |                        |                           |                    |

|         | 1 0                                                                               |                                                                                                               | 2 0                                                                       | x10-0x17                                                        |                                                    |                        |                           |                    |

|         | 1 1                                                                               | ,                                                                                                             | 3 0                                                                       | x18-0x1F                                                        |                                                    |                        |                           |                    |

| Bit2:   | <ul> <li>A MUL i</li> <li>A DIV in</li> <li>The OV bit is other cases.</li> </ul> | Rn, A" instr<br>7 Flag.<br>to 1 under th<br>, ADDC, or 5<br>nstruction re<br>istruction cau<br>6 cleared to 0 | uction.<br>e following o<br>SUBB instru<br>sults in an o<br>ises a divide | circumstance:<br>ction causes<br>verflow (resu<br>-by-zero conc | s:<br>a sign-change<br>lt is greater th<br>lition. | overflow.<br>an 255) . |                           |                    |

| Bit1:   | F1: User Flag<br>This is a bit-a                                                  |                                                                                                               | eneral purpo                                                              | se flag for us                                                  | e under softw                                      | are control            |                           |                    |

|         | DADITV. Dor                                                                       | ity Flag.                                                                                                     |                                                                           |                                                                 |                                                    |                        |                           |                    |

#### 13.8.1. Watchdog Usage

The WDT consists of a 21-bit timer running from the programmed system clock. The timer measures the period between specific writes to its control register. If this period exceeds the programmed limit, a WDT reset is generated. The WDT can be enabled and disabled as needed in software, or can be permanently enabled if desired. Watchdog features are controlled via the Watchdog Timer Control Register (WDTCN) shown in Figure 13.3.

#### Enable/Reset WDT

The watchdog timer is both enabled and the countdown restarted by writing 0xA5 to the WDTCN register. The user's application software should include periodic writes of 0xA5 to WDTCN as needed to prevent a watchdog timer overflow. The WDT is enabled and restarted as a result of any system reset.

#### **Disable WDT**

Writing 0xDE followed by 0xAD to the WDTCN register disables the WDT. The following code segment illustrates disabling the WDT.

CLR EA ; disable all interrupts MOV WDTCN,#0DEh ; disable software MOV WDTCN,#0ADh ; watchdog timer SETB EA ; re-enable interrupts

The writes of 0xDE and 0xAD must occur within 4 clock cycles of each other, or the disable operation is ignored. Interrupts should be disabled during this procedure to avoid delay between the two writes.

#### **Disable WDT Lockout**

Writing 0xFF to WDTCN locks out the disable feature. Once locked out, the disable operation is ignored until the next system reset. Writing 0xFF does not enable or reset the watchdog timer. Applications always intending to use the watchdog should write 0xFF to WDTCN in their initialization code.

#### Setting WDT Interval

WDTCN.[2:0] control the watchdog timeout interval. The interval is given by the following equation:

$4^{3+WDTCN[2:0]} \times T_{SYSCLK}$ , (where  $T_{SYSCLK}$  is the system clock period).

For a 2MHz system clock, this provides an interval range of 0.032msec to 524msec. WDTCN.7 must be a 0 when setting this interval. Reading WDTCN returns the programmed interval. WDTCN.[2:0] is 111b after a system reset.

| R/W      | R/W           | R/W             | R/W             | R/W          | R/W          | R/W            | R/W      | Reset Value  |

|----------|---------------|-----------------|-----------------|--------------|--------------|----------------|----------|--------------|

|          |               |                 |                 |              |              |                |          | xxxxx111     |

| Bit7     | Bit6          | Bit5            | Bit4            | Bit3         | Bit2         | Bit1           | Bit0     | SFR Address: |

|          |               |                 |                 |              |              |                |          | 0xFF         |

|          |               |                 |                 |              |              |                |          |              |

| Bits7-0: | WDT Control   |                 |                 |              |              |                |          |              |

|          | Writing 0xA5  | both enables    | and reloads     | the WDT.     |              |                |          |              |

|          | Writing 0xDE  |                 |                 |              | ables the WI | т              |          |              |

|          | Writing 0xFF  |                 |                 | •            |              |                |          |              |

| DIA      | U             |                 |                 | lie.         |              |                |          |              |

| Bit4:    | Watchdog Stat | ,               | ,               |              |              |                |          |              |

|          | Reading the W | /DTCN.[4] b     | it indicates th | ne Watchdog  | Timer Status | s.             |          |              |

|          | 0: WDT is ina | active          |                 |              |              |                |          |              |

|          | 1: WDT is act | tive            |                 |              |              |                |          |              |

| Bits2-0: | Watchdog Tin  | neout Interval  | Bits            |              |              |                |          |              |

| 2102 01  | The WDTCN.    |                 |                 | a Timeout In | terval Whe   | n writing the  | se hits  |              |

|          | WDTCN.7 mu    |                 |                 | g Thicout In |              | ii wiiting the | se 0113, |              |

|          | wDICN./mt     | ist de set to U | •               |              |              |                |          |              |

|          |               |                 |                 |              |              |                |          |              |

Figure 13.3. WDTCN: Watchdog Timer Control Register

| R/W<br>P3.7 | R/W<br>P3.6                                                                                          | R/W<br>P3.5   | R/W<br>P3.4 | R/W<br>P3.3  | R/W<br>P3.2 | R/W<br>P3.1  | R/W<br>P3.0               | Reset Value<br>11111111 |

|-------------|------------------------------------------------------------------------------------------------------|---------------|-------------|--------------|-------------|--------------|---------------------------|-------------------------|

| Bit7        | Bit6                                                                                                 | Bit5          | Bit4        | Bit3         | Bit2        | Bit1         | Bit0<br>(bit addressable) | SFR Address:<br>0xB0    |

|             | P3.[7:0]<br>(Write)<br>D: Logic Low<br>1: Logic High<br>(Read)<br>D: P3.n is logi<br>1: P3.n is logi | o Output (hig | h-impedance | if correspon | ding PRT3Cl | F.n bit = 0) |                           |                         |

### Figure 15.13. P3: Port3 Register

### Table 15.2. Port I/O DC Electrical Characteristics

VDD = 2.7 to 3.6V, -40°C to +85°C unless otherwise specified.

| PARAMETER             | CONDITIONS                                  | MIN   | ТҮР   | MAX   | UNITS |

|-----------------------|---------------------------------------------|-------|-------|-------|-------|

| Output High Voltage   | $I_{OH} = -10uA$ , Port I/O push-pull       | VDD – |       |       | V     |

|                       |                                             | 0.1   |       |       |       |

|                       | $I_{OH} = -3mA$ , Port I/O push-pull        | VDD – |       |       |       |

|                       |                                             | 0.7   |       |       |       |

|                       | I <sub>OH</sub> = -10mA, Port I/O push-pull |       | VDD – |       |       |

|                       |                                             |       | 0.8   |       |       |

| Output Low Voltage    | $I_{OL} = 10uA$                             |       |       | 0.1   | V     |

|                       | $I_{OL} = 8.5 \text{mA}$                    |       |       | 0.6   |       |

|                       | $I_{OL} = 25 \text{mA}$                     |       | 1.0   |       |       |

| Input High Voltage    |                                             | 0.7 x |       |       | V     |

|                       |                                             | VDD   |       |       |       |

| Input Low Voltage     |                                             |       |       | 0.3 x | V     |

|                       |                                             |       |       | VDD   |       |

| Input Leakage Current | DGND < Port Pin < VDD, Pin Tri-state        |       |       |       | μA    |

|                       | Weak Pull-up Off                            |       |       | ±1    |       |

|                       | Weak Pull-up On                             |       | 30    |       |       |

| Capacitive Loading    |                                             |       | 5     |       | pF    |

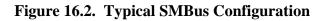

Figure 16.2 shows a typical SMBus configuration. The SMBus interface will work at any voltage between 3.0V and 5.0V and different devices on the bus may operate at different voltage levels. The SCL (serial clock) and SDA (serial data) lines are bi-directional. They must be connected to a positive power supply voltage through a pull-up resistor or similar circuit. When the bus is free, both lines are pulled high. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus will not exceed 300ns and 1000ns, respectively.

### **16.1.** Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The *I*<sup>2</sup>*C*-bus and how to use it (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification -- Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification -- Version 1.1, SBS Implementers Forum.

#### 16.6.1. Control Register

The SMBus Control register SMB0CN is used to configure and control the SMBus interface. All of the bits in the register can be read or written by software. Two of the control bits are also affected by the SMBus hardware. The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by the hardware when a valid serial interrupt condition occurs. It can only be cleared by software. The Stop flag (STO, SMB0CN.4) is cleared to logic 0 by hardware when a STOP condition is present on the bus.

Setting the ENSMB flag to logic 1 enables the SMBus interface. Clearing the ENSMB flag to logic 0 disables the SMBus interface and removes it from the bus. Momentarily clearing the ENSMB flag and then resetting it to logic 1 will reset a SMBus communication. However, ENSMB should not be used to temporarily remove a device from the bus since the bus state information will be lost. Instead, the Assert Acknowledge (AA) flag should be used to temporarily remove the device from the bus (see description of AA flag below).

Setting the Start flag (STA, SMB0CN.5) to logic 1 will put the SMBus in a master mode. If the bus is free, the SMBus hardware will generate a START condition. If the bus is not free, the SMBus hardware waits for a STOP condition to free the bus and then generates a START condition after a 5 $\mu$ s delay per the SMB0CR value. (In accordance with the SMBus protocol, the SMBus interface also considers the bus free if the bus is idle for 50 $\mu$ s and no STOP condition was recognized.) If STA is set to logic 1 while the SMBus is in master mode and one or more bytes have been transferred, a repeated START condition will be generated. To ensure proper operation, the STO flag should be explicitly cleared before setting STA to a logic 1.

When the Stop flag (STO, SMB0CN.4) is set to logic 1 while the SMBus interface is in master mode, the hardware generates a STOP condition on the SMBus. In a slave mode, the STO flag may be used to recover from an error condition. In this case, a STOP condition is not generated on the SMBus, but the SMBus hardware behaves as if a STOP condition has been received and enters the "not addressed" slave receiver mode. The SMBus hardware automatically clears the STO flag to logic 0 when a STOP condition is detected on the bus.

The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by hardware when the SMBus interface enters one of 27 possible states. If interrupts are enabled for the SMBus interface, an interrupt request is generated when the SI flag is set. The SI flag must be cleared by software. While SI is set to logic 1, the clock-low period of the serial clock will be stretched and the serial transfer is suspended.

The Assert Acknowledge flag (AA, SMB0CN.2) is used to set the level of the SDA line during the acknowledge clock cycle on the SCL line. Setting the AA flag to logic 1 will cause an ACKNOWLEDGE (low level on SDA) to be sent during the acknowledge cycle if the device has been addressed. Setting the AA flag to logic 0 will cause a NOT ACKNOWLEDGE (high level on SDA) to be sent during acknowledge cycle. After the transmission of a byte in slave mode, the slave can be temporarily removed from the bus by clearing the AA flag. The slave's own address and general call address will be ignored. To resume operation on the bus, the AA flag must be reset to logic 1 to allow the slave's address to be recognized.

Setting the SMBus Free Timer Enable bit (FTE, SMB0CN.1) to logic 1 enables the SMBus Free Timeout feature. If SCL and SDA remain high for the SMBus Free Timeout given in the SMBus Clock Rate Register (Figure 16.5), the bus will be considered free and a Start will be generated if pending. The bus free period should be greater than 50µs.

Setting the SMBus timeout enable bit (TOE, SMB0CN.0) to logic 1 enables Timer 3 to count up when the SCL line is low and Timer 3 is enabled. If Timer 3 overflows, a Timer 3 interrupt will be generated, which will alert the CPU that a SMBus SCL low timeout has occurred.

in an "off-line" state. In a multiple-master environment, the system controller should check the state of the SLVSEL flag (SPI0CN.2) to ensure the bus is free before setting the MSTEN bit and initiating a data transfer.

### **17.3.** Serial Clock Timing

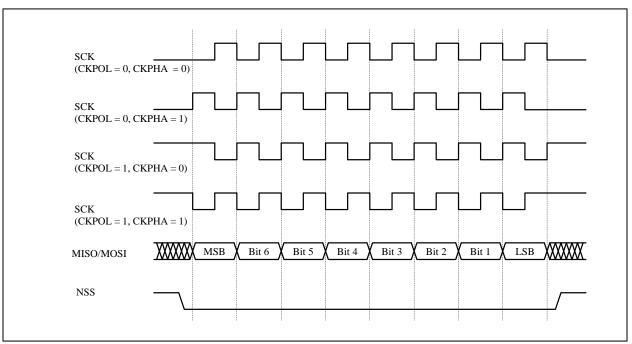

As shown in Figure 17.4, four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.7) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.6) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. Note: the SPI should be disabled (by clearing the SPIEN bit, SPI0CN.0) while changing the clock phase and polarity.

The SPI Clock Rate Register (SPIOCKR) as shown in Figure 17.7 controls the master mode serial clock frequency. This register is ignored when operating in slave mode.

Figure 17.4. Data/Clock Timing Diagram

| R/W<br>SCR7 | R/W<br>SCR6                                                                                                                                                                                                                                                                   | R/W<br>SCR5 | R/W<br>SCR4 | R/W<br>SCR3 | R/W<br>SCR2 | R/W<br>SCR1 | R/W<br>SCR0 | Reset Value<br>00000000 |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------|--|--|--|--|

| Bit7        | Bit6                                                                                                                                                                                                                                                                          | Bit5        | Bit4        | Bit3        | Bit2        | Bit1        | Bit0        | SFR Address:<br>0x9D    |  |  |  |  |

| T<br>C      | Bits7-0: SCR7-SCR0: SPI Clock Rate<br>These bits determine the frequency of the SCK output when the SPI module is<br>configured for master mode operation. The SCK clock frequency is a divided down<br>version of the system clock, and is given in the following equations: |             |             |             |             |             |             |                         |  |  |  |  |

| f           | $f_{SCK} = 0.5 * f_{SYSCLK} / (SPI0CKR + 1),$ for $0 \le SPI0CKR \le 255$ ,                                                                                                                                                                                                   |             |             |             |             |             |             |                         |  |  |  |  |

|             |                                                                                                                                                                                                                                                                               |             |             |             |             |             |             |                         |  |  |  |  |

### Figure 17.7. SPI0CKR: SPI Clock Rate Register

### 18.1. UART Operational Modes

The UART provides four operating modes (one synchronous and three asynchronous) selected by setting configuration bits in the SCON register. These four modes offer different baud rates and communication protocols. The four modes are summarized in Table 18.1 below. Detailed descriptions follow.

| Mode | Synchronization | Baud Clock                  | Data Bits | Start/Stop Bits |

|------|-----------------|-----------------------------|-----------|-----------------|

| 0    | Synchronous     | SYSCLK/12                   | 8         | None            |

| 1    | Asynchronous    | Timer 1 or Timer 2 Overflow | 8         | 1 Start, 1 Stop |

| 2    | Asynchronous    | SYSCLK/32 or SYSCLK/64      | 9         | 1 Start, 1 Stop |

| 3    | Asynchronous    | Timer 1 or Timer 2 Overflow | 9         | 1 Start, 1 Stop |

#### Table 18.1. UART Modes

#### 18.1.1. Mode 0: Synchronous Mode

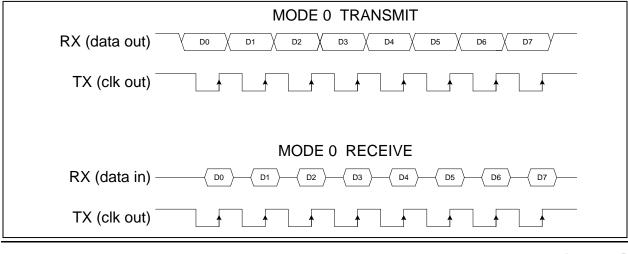

Mode 0 provides synchronous, half-duplex communication. Serial data is transmitted and received on the RX pin. The TX pin provides the shift clock for both transmit and receive. The MCU must be the master since it generates the shift clock for transmission in both directions (see the interconnect diagram in Figure 18.2).

Eight data bits are transmitted/received, LSB first (see the timing diagram in Figure 18.3). Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the eighth bit time. Data reception begins when the REN Receive Enable bit (SCON.4) is set to logic 1 and the RI Receive Interrupt Flag (SCON.0) is cleared. One cycle after the eighth bit is shifted in, the RI flag is set and reception stops until software clears the RI bit. An interrupt will occur if enabled when either TI or RI is set.

The Mode 0 baud rate is the system clock frequency divided by twelve. RX is forced to open-drain in mode 0, and an external pull-up will typically be required.

#### Figure 18.3. UART Mode 0 Timing Diagram

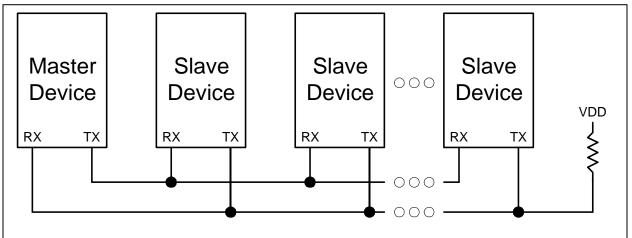

### 18.2. Multiprocessor Communications

Modes 2 and 3 support multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the SM2 bit (SCON.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic one (RB8 = 1) signifying an address byte has been received. In the UART's interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its SM2 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their SM2 bits set and do not generate interrupts on the received, the addressed slave resets its SM2 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 18.7. UART Multi-Processor Mode Interconnect Diagram

| Figure 19.5. | TMOD: Timer Mode Register |

|--------------|---------------------------|

|              |                           |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Coun 0: Timer Fe 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} 0011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Coun0: Timer Fe1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                                    | enabled only<br>nter/Timer 1 S<br>Function: Tim<br>r Function: Ti                                                    | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.                                                                                                                                                                                              | T0M0<br>Bit0 | 00000000<br>SFR Address<br>0x89 |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|--|--|--|--|--|--|--|--|

| Bit7: GATE1: Tin<br>0: Timer 1 e<br>1: Timer 1 e<br>Bit6: C/T1: Coun<br>0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>$\overline{11M1}$<br>0<br>0<br>1<br>1<br>Bit3: GATE0: Tin<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                      | imer 1 Gate C<br>enabled when<br>enabled only<br>nter/Timer 1 S<br>Function: Tim<br>r Function: Tim<br>M0: Timer 1 M | Control.<br>TR1 = 1 irres<br>when $TR1 = 1$<br>Select.<br>er 1 incrementer<br>mer 1 incrementer<br>Mode Select. | pective of /IN<br>AND /INT1<br>ed by clock de | T1 logic leve<br>= logic level<br>fined by T11 | el.<br>one.                                                                                                                                                                                       | Bit0         |                                 |  |  |  |  |  |  |  |  |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Count 0: Timer Fu 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} = 0 0110011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Count0: Timer Fu1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                           | enabled when<br>enabled only<br>nter/Timer 1 S<br>function: Tim<br>r Function: Ti<br>M0: Timer 1 M                   | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.                                                                                                                                                                                              |              | 0.0.89                          |  |  |  |  |  |  |  |  |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Count 0: Timer Fu 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} = 0 0110011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Count0: Timer Fu1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                           | enabled when<br>enabled only<br>nter/Timer 1 S<br>function: Tim<br>r Function: Ti<br>M0: Timer 1 M                   | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.                                                                                                                                                                                              |              |                                 |  |  |  |  |  |  |  |  |

| 0: Timer 1 e<br>1: Timer 1 e<br>1: Timer 1 e<br>Bit6: $C/T1: Count 0: Timer Fu 1: Counter (T1). Bits5-4: T1M1-T1M These bits s \boxed{T1M1} = 0 0110011Bit3: GATE0: Timer 0 e1: Timer 0 eBit2: C/T0: Count0: Timer Fu1: Counter(T0).Bits1-0: T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                           | enabled when<br>enabled only<br>nter/Timer 1 S<br>function: Tim<br>r Function: Ti<br>M0: Timer 1 M                   | n TR1 = 1 irres<br>when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer                                 | AND /INT1                                     | = logic level                                  | one.                                                                                                                                                                                              |              |                                 |  |  |  |  |  |  |  |  |

| 1: Timer 1 eBit6: $C/T1: Counter$<br>$0: Timer Fu1: Counter(T1).Bits5-4:T1M1-T1MThese bits sBits5-4:T1M1-T1MThese bits sBit3:GATE0: Time 00: Timer 0 e1: Timer 0 eBit2:C/T0: Counter(T0).Bits1-0:T0M1-T0M$                                                                                                                                                                                                                                                                                                                                                                                                                                                       | enabled only<br>nter/Timer 1 S<br>Function: Tim<br>r Function: Ti<br>M0: Timer 1 M                                   | when TR1 = 1<br>Select.<br>er 1 incremente<br>mer 1 incremer<br>Aode Select.                                    | AND /INT1                                     | = logic level                                  | one.                                                                                                                                                                                              |              |                                 |  |  |  |  |  |  |  |  |

| Bit6: C/T1: Count<br>0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>Bit3: GATE0: Tim<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Count<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                     | nter/Timer 1 S<br>Function: Tim<br>r Function: Ti<br>M0: Timer 1 N                                                   | Select.<br>er 1 incremente<br>mer 1 incremer<br>Aode Select.                                                    | ed by clock de                                | fined by T11                                   |                                                                                                                                                                                                   |              |                                 |  |  |  |  |  |  |  |  |

| 0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>1<br>Bit3: GATE0: Tim<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                      | Function: Tim<br>r Function: Ti<br>40: Timer 1 M                                                                     | er 1 incremente<br>mer 1 incremer<br>Aode Select.                                                               |                                               |                                                | M hit (CKCO                                                                                                                                                                                       |              |                                 |  |  |  |  |  |  |  |  |

| 0: Timer Fu<br>1: Counter<br>(T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>1<br>Bit3: GATE0: Tim<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Counter<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                   | Function: Tim<br>r Function: Ti<br>40: Timer 1 M                                                                     | er 1 incremente<br>mer 1 incremer<br>Aode Select.                                                               |                                               |                                                | M bit (CKCO                                                                                                                                                                                       |              |                                 |  |  |  |  |  |  |  |  |

| 1: Counter (T1).         Bits5-4: T1M1-T1M These bits s <b>T1M1</b> 0         0         1         0         1         1         Bit3: GATE0: Timer 0 et al.: C/T0: Counter (T0).         Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                       | r Function: Ti<br>40: Timer 1 N                                                                                      | mer 1 incremer<br>Aode Select.                                                                                  |                                               |                                                |                                                                                                                                                                                                   | N.4).        |                                 |  |  |  |  |  |  |  |  |

| (T1).<br>Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>Bit3: GATE0: Tit<br>0: Timer 0 e<br>1: Timer 0 e<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A0: Timer 1 M                                                                                                        | Aode Select.                                                                                                    | , ,                                           |                                                | <ul><li>0: Timer Function: Timer 1 incremented by clock defined by T1M bit (CKCON.4).</li><li>1: Counter Function: Timer 1 incremented by high-to-low transitions on external input pin</li></ul> |              |                                 |  |  |  |  |  |  |  |  |

| Bits5-4: T1M1-T1M<br>These bits s<br>T1M1<br>0<br>0<br>1<br>1<br>1<br>Bit3: GATE0: Tit<br>0: Timer 0 c<br>1: Timer 0 c<br>Bit2: C/T0: Coun<br>0: Timer Fu<br>1: Counter<br>(T0).<br>Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |                                                                                                                 |                                               |                                                |                                                                                                                                                                                                   | 1 1          |                                 |  |  |  |  |  |  |  |  |

| These bits s T1M1 0 0 1 1 1 Bit3: GATE0: Tit 0: Timer 0 e 1: Timer 0 e 1: C/T0: Coun 0: Timer Fe 1: Counter (T0). Bits1-0: T0M1-T0M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |                                                                                                                 |                                               |                                                |                                                                                                                                                                                                   |              |                                 |  |  |  |  |  |  |  |  |

| T1M1           0           0           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1 | select the Tin                                                                                                       |                                                                                                                 |                                               |                                                |                                                                                                                                                                                                   |              |                                 |  |  |  |  |  |  |  |  |

| 00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      | ner 1 operation                                                                                                 | mode.                                         |                                                |                                                                                                                                                                                                   |              |                                 |  |  |  |  |  |  |  |  |