Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 20MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 32КВ (32К х 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 4x10b; D/A 2x12b                                           |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f012-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Table 18.2. Oscillator Frequencies for Standard Baud Rates                             |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | Figure 18.8. SBUF: Serial (UART) Data Buffer Register                                  |     |

|     | Figure 18.9. SCON: Serial Port Control Register                                        |     |

| 19. | TIMERS                                                                                 |     |

|     | 19.1. Timer 0 and Timer 1                                                              |     |

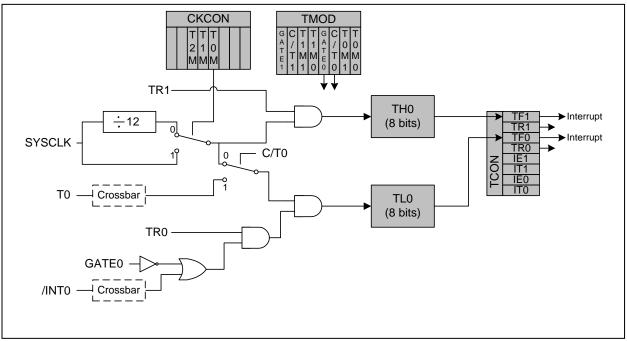

|     | Figure 19.1. T0 Mode 0 Block Diagram.                                                  |     |

|     | Figure 19.2. T0 Mode 2 Block Diagram.                                                  |     |

|     | Figure 19.3. T0 Mode 3 Block Diagram.                                                  |     |

|     | Figure 19.4. TCON: Timer Control Register                                              |     |

|     | Figure 19.5. TMOD: Timer Mode Register                                                 |     |

|     | Figure 19.6. CKCON: Clock Control Register                                             |     |

|     | Figure 19.7. TLO: Timer 0 Low Byte                                                     |     |

|     | Figure 19.8. TL1: Timer 1 Low Byte                                                     |     |

|     | Figure 19.9. THO: Timer 0 High Byte                                                    |     |

|     | Figure 19.10. TH1: Timer 1 High Byte                                                   |     |

|     | 19.2. Timer 2                                                                          |     |

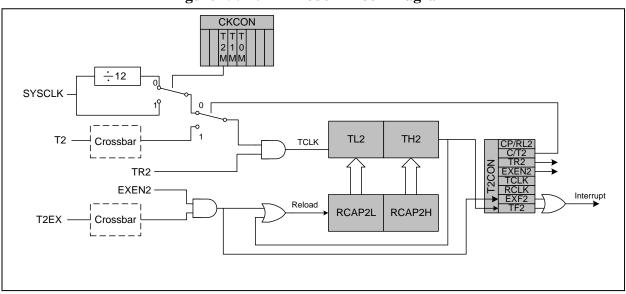

|     | Figure 19.11. T2 Mode 0 Block Diagram                                                  |     |

|     | Figure 19.12. T2 Mode 1 Block Diagram.                                                 |     |

|     | Figure 19.13. T2 Mode 2 Block Diagram.                                                 |     |

|     | Figure 19.14. T2CON: Timer 2 Control Register                                          |     |

|     | Figure 19.15. RCAP2L: Timer 2 Capture Register Low Byte                                |     |

|     | Figure 19.16. RCAP2H: Timer 2 Capture Register High Byte                               |     |

|     | Figure 19.17. TL2: Timer 2 Low Byte                                                    |     |

|     | Figure 19.18. TH2: Timer 2 High Byte                                                   |     |

|     | 19.3. Timer 3                                                                          |     |

|     | Figure 19.19. Timer 3 Block Diagram                                                    |     |

|     | Figure 19.20. TMR3CN: Timer 3 Control Register                                         |     |

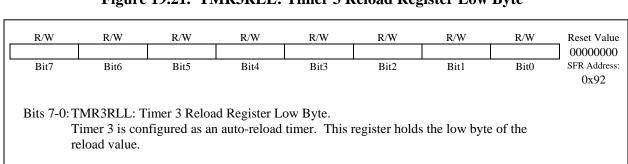

|     | Figure 19.21. TMR3RLL: Timer 3 Reload Register Low Byte                                |     |

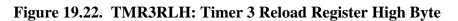

|     | Figure 19.22. TMR3RLH: Timer 3 Reload Register High Byte                               |     |

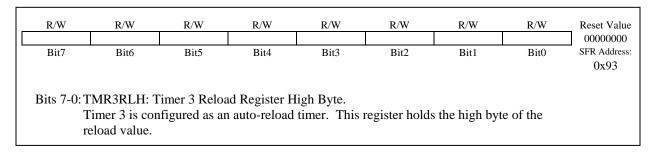

|     | Figure 19.22. TMR3REIT. Timer 3 Keroad Register High Byte                              |     |

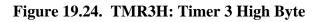

|     | Figure 19.24. TMR3H: Timer 3 High Byte                                                 |     |

| 20  | PROGRAMMABLE COUNTER ARRAY                                                             |     |

| 20. |                                                                                        |     |

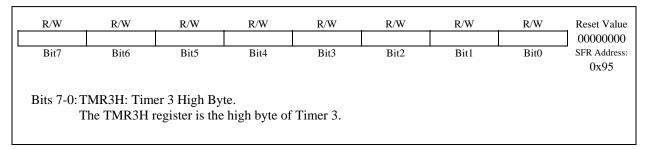

|     | Figure 20.1. PCA Block Diagram                                                         |     |

|     | 20.1. Capture/Compare Modules                                                          |     |

|     | Table 20.1. PCA0CPM Register Settings for PCA Capture/Compare Modules                  |     |

|     | Figure 20.2. PCA Interrupt Block Diagram.                                              |     |

|     | Figure 20.3. PCA Capture Mode Diagram                                                  |     |

|     | Figure 20.4. PCA Software Timer Mode Diagram.                                          |     |

|     | Figure 20.5. PCA High Speed Output Mode Diagram                                        |     |

|     | Figure 20.6. PCA PWM Mode Diagram                                                      |     |

|     | 20.2. PCA Counter/Timer                                                                |     |

|     | Table 20.2.     PCA Timebase Input Options.       Fine     20.7       PCA Construction |     |

|     | Figure 20.7. PCA Counter/Timer Block Diagram                                           |     |

|     | 20.3. Register Descriptions for PCA                                                    |     |

|     | Figure 20.8. PCA0CN: PCA Control Register                                              |     |

|     | Figure 20.9. PCA0MD: PCA Mode Register                                                 |     |

|     | Figure 20.10. PCA0CPMn: PCA Capture/Compare Registers                                  |     |

|     | Figure 20.11. PCA0L: PCA Counter/Timer Low Byte                                        |     |

|     | Figure 20.12. PCA0H: PCA Counter/Timer High Byte                                       |     |

|     | Figure 20.13. PCA0CPLn: PCA Capture Module Low Byte                                    |     |

|     | Figure 20.14. PCA0CPHn: PCA Capture Module High Byte                                   |     |

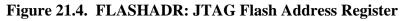

| 21. | JTAG (IEEE 1149.1)                                                                     |     |

|     | Figure 21.1. IR: JTAG Instruction Register                                             |     |

|     | 21.1. Boundary Scan                                                                    | 165 |

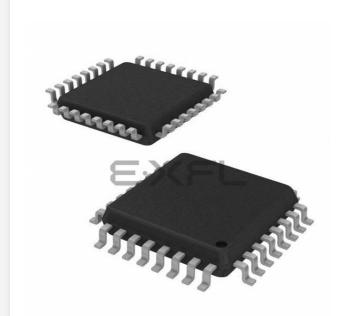

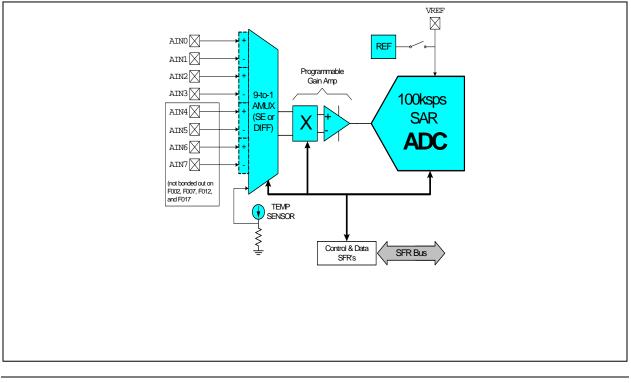

Figure 1.3. C8051F002/07/12/17 Block Diagram

#### **1.7.** Analog to Digital Converter

The C8051F000/1/2/5/6/7 has an on-chip 12-bit SAR ADC with a 9-channel input multiplexer and programmable gain amplifier. With a maximum throughput of 100ksps, the ADC offers true 12-bit accuracy with an INL of  $\pm$ 1LSB. The ADC in the C8051F010/1/2/5/6/7 is similar, but with 10-bit resolution. Each ADC has a maximum throughput of 100ksps. Each ADC has an INL of  $\pm$ 1LSB, offering true 12-bit accuracy with the C8051F00x, and true 10-bit accuracy with the C8051F01x. There is also an on-board 15ppm voltage reference, or an external reference may be used via the VREF pin.

The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. One input channel is tied to an internal temperature sensor, while the other eight channels are available externally. Each pair of the eight external input channels can be configured as either two single-ended inputs or a single differential input. The system controller can also put the ADC into shutdown to save power.

A programmable gain amplifier follows the analog multiplexer. The gain can be set in software from 0.5 to 16 in powers of 2. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset (in differential mode, a DAC could be used to provide the DC offset).

Conversions can be started in four ways; a software command, an overflow on Timer 2, an overflow on Timer 3, or an external signal input. This flexibility allows the start of conversion to be triggered by software events, external HW signals, or convert continuously. A completed conversion causes an interrupt, or a status bit can be polled in software to determine the end of conversion. The resulting 10 or 12-bit data word is latched into two SFRs upon completion of a conversion. The data can be right or left justified in these registers under software control.

Compare registers for the ADC data can be configured to interrupt the controller when ADC data is within a specified window. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within the specified window.

#### Figure 1.10. ADC Diagram

|      | Pin                          | Numb                         | oers                         |       |                                                                                  |

|------|------------------------------|------------------------------|------------------------------|-------|----------------------------------------------------------------------------------|

| Name | F000<br>F005<br>F010<br>F015 | F001<br>F006<br>F011<br>F016 | F002<br>F007<br>F012<br>F017 | Туре  | Description                                                                      |

| AIN6 | 13                           | 10                           |                              | A In  | Analog Mux Channel Input 6. (See ADC Specification for complete                  |

| AIN7 | 1.4                          | 11                           |                              | A In  | description).<br>Analog Mux Channel Input 7. (See ADC Specification for complete |

| AIN/ | 14                           | 11                           |                              | A III | description).                                                                    |

| P0.0 | 39                           | 31                           | 19                           | D I/O | Port0 Bit0. (See the Port I/O Sub-System section for complete description).      |

| P0.1 | 42                           | 34                           | 22                           | D I/O | Port0 Bit1. (See the Port I/O Sub-System section for complete description).      |

| P0.2 | 47                           | 35                           | 23                           | D I/O | Port0 Bit2. (See the Port I/O Sub-System section for complete description).      |

| P0.3 | 48                           | 36                           | 24                           | D I/O | Port0 Bit3. (See the Port I/O Sub-System section for complete description).      |

| P0.4 | 49                           | 37                           | 25                           | D I/O | Port0 Bit4. (See the Port I/O Sub-System section for complete description).      |

| P0.5 | 50                           | 38                           | 26                           | D I/O | Port0 Bit5. (See the Port I/O Sub-System section for complete description).      |

| P0.6 | 55                           | 39                           | 27                           | D I/O | Port0 Bit6. (See the Port I/O Sub-System section for complete description).      |

| P0.7 | 56                           | 40                           | 28                           | D I/O | Port0 Bit7. (See the Port I/O Sub-System section for complete description).      |

| P1.0 | 38                           | 30                           |                              | D I/O | Port1 Bit0. (See the Port I/O Sub-System section for complete description).      |

| P1.1 | 37                           | 29                           |                              | D I/O | Port1 Bit1. (See the Port I/O Sub-System section for complete description).      |

| P1.2 | 36                           | 28                           |                              | D I/O | Port1 Bit2. (See the Port I/O Sub-System section for complete description).      |

| P1.3 | 35                           | 26                           |                              | D I/O | Port1 Bit3. (See the Port I/O Sub-System section for complete description).      |

| P1.4 | 34                           | 25                           |                              | D I/O | Port1 Bit4. (See the Port I/O Sub-System section for complete description).      |

| P1.5 | 32                           | 24                           |                              | D I/O | Port1 Bit5. (See the Port I/O Sub-System section for complete description).      |

| P1.6 | 60                           | 42                           |                              | D I/O | Port1 Bit6. (See the Port I/O Sub-System section for complete description).      |

| P1.7 | 59                           | 41                           |                              | D I/O | Port1 Bit7. (See the Port I/O Sub-System section for complete description).      |

| P2.0 | 33                           |                              |                              | D I/O | Port2 Bit0. (See the Port I/O Sub-System section for complete description).      |

| P2.1 | 27                           |                              |                              | D I/O | Port2 Bit1. (See the Port I/O Sub-System section for complete description).      |

| P2.2 | 54                           |                              |                              | D I/O | Port2 Bit2. (See the Port I/O Sub-System section for complete description).      |

| P2.3 | 53                           |                              |                              | D I/O | Port2 Bit3. (See the Port I/O Sub-System section for complete description).      |

| P2.4 | 52                           |                              |                              | D I/O | Port2 Bit4. (See the Port I/O Sub-System section for complete description).      |

| P2.5 | 51                           |                              |                              | D I/O | Port2 Bit5. (See the Port I/O Sub-System section for complete description).      |

| P2.6 | 44                           |                              |                              | D I/O | Port2 Bit6. (See the Port I/O Sub-System section for complete description).      |

| P2.7 | 43                           |                              |                              | D I/O | Port2 Bit7. (See the Port I/O Sub-System section for complete description).      |

| P3.0 | 26                           |                              |                              | D I/O | Port3 Bit0. (See the Port I/O Sub-System section for complete description).      |

| P3.1 | 25                           |                              |                              | D I/O | Port3 Bit1. (See the Port I/O Sub-System section for complete description).      |

| P3.2 | 24                           |                              |                              | D I/O | Port3 Bit2. (See the Port I/O Sub-System section for complete description).      |

| P3.3 | 23                           |                              |                              | D I/O | Port3 Bit3. (See the Port I/O Sub-System section for complete description).      |

| P3.4 | 58                           |                              |                              | D I/O | Port3 Bit4. (See the Port I/O Sub-System section for complete description).      |

| P3.5 | 57                           |                              |                              | D I/O | Port3 Bit5. (See the Port I/O Sub-System section for complete description).      |

| P3.6 | 46                           |                              |                              | D I/O | Port3 Bit6. (See the Port I/O Sub-System section for complete description).      |

| P3.7 | 45                           |                              |                              | D I/O | Port3 Bit7. (See the Port I/O Sub-System section for complete description).      |

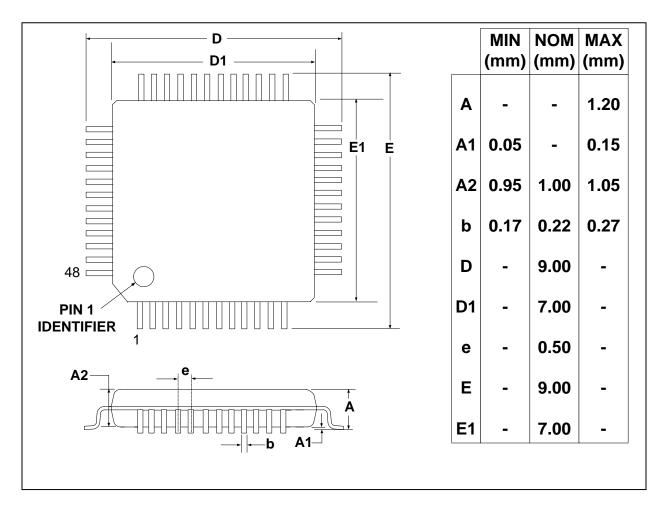

Figure 4.4. TQFP-48 Package Drawing

#### Table 5.1. 12-Bit ADC Electrical Characteristics

| PARAMETER                                  | CONDITIONS                                | MIN           | TYP        | MAX    | UNITS      |

|--------------------------------------------|-------------------------------------------|---------------|------------|--------|------------|

| DC ACCURACY                                |                                           |               |            |        |            |

| Resolution                                 |                                           |               | 12         |        | bits       |

| Integral Nonlinearity                      |                                           |               |            | ± 1    | LSB        |

| Differential Nonlinearity                  | Guaranteed Monotonic                      |               |            | ± 1    | LSB        |

| Offset Error                               |                                           |               | -3 ± 1     |        | LSB        |

| Full Scale Error                           | Differential mode                         |               | -7 ± 3     |        | LSB        |

| Offset Temperature                         |                                           |               | ± 0.25     |        | ppm/°C     |

| Coefficient                                |                                           |               |            |        |            |

| DYNAMIC PERFORMAN                          | CE (10kHz sine-wave input, 0 to –1dB of f | full scale, 1 | 00ksps)    |        |            |

| Signal-to-Noise Plus                       |                                           | 66            | 69         |        | dB         |

| Distortion                                 |                                           |               |            |        |            |

| Total Harmonic Distortion                  | Up to the 5 <sup>th</sup> harmonic        |               | -75        |        | dB         |

| Spurious-Free Dynamic                      |                                           |               | 80         |        | dB         |

| Range                                      |                                           |               |            |        |            |

| CONVERSION RATE                            |                                           | -             | r          |        |            |

| Conversion Time in SAR                     |                                           | 16            |            |        | clocks     |

| Clocks                                     |                                           |               |            |        |            |

| SAR Clock Frequency                        | C8051F000, 'F001, 'F002                   |               |            | 2.0    | MHz        |

|                                            | C8051F005, 'F006, 'F007                   |               |            | 2.5    | MHz        |

| Track/Hold Acquisition                     |                                           | 1.5           |            |        | μs         |

| Time                                       |                                           |               |            | 100    |            |

| Throughput Rate                            |                                           |               |            | 100    | ksps       |

| ANALOG INPUTS                              |                                           |               |            |        |            |

| Voltage Conversion Range                   | Single-ended Mode (AINn – AGND)           | 0             |            | VREF   | V          |

| T , TT 1,                                  | Differential Mode  (AINn+) – (AINm-)      | A CNID        |            | - 1LSB | <b>N</b> 7 |

| Input Voltage                              | Any AINn pin                              | AGND          | 10         | AV+    | <u>V</u>   |

| Input Capacitance                          |                                           |               | 10         |        | pF         |

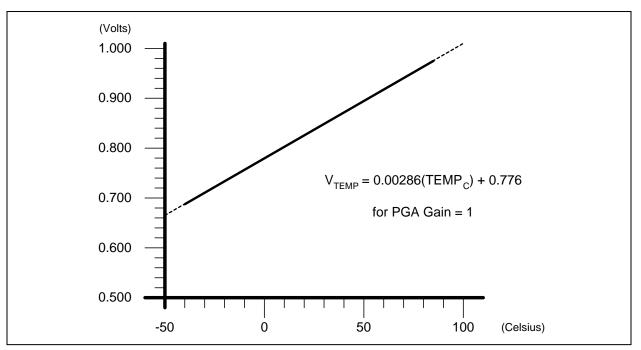

| TEMPERATURE SENSOR<br>Linearity            |                                           |               | 10.00      |        | 00         |

| 2                                          |                                           |               | ± 0.20     |        | °C         |

| Absolute Accuracy                          |                                           |               | $\pm 3$    |        | °C         |

| Gain                                       | PGA Gain = 1                              |               | 2.86       |        | mV/°C      |

| Gain Error $(\pm 1\sigma)$                 | PGA Gain = 1                              |               | ± 33.5     |        | μV/°C      |

| Offset                                     | PGA Gain = 1, Temp = $0^{\circ}$ C        |               | 776        |        | mV         |

| Offset Error $(\pm 1\sigma)$               | PGA Gain = 1, Temp = $0^{\circ}$ C        |               | $\pm 8.51$ |        | mV         |

| POWER SPECIFICATION                        |                                           |               |            | 1      |            |

| Power Supply Current (AV+ supplied to ADC) | Operating Mode, 100ksps                   |               | 450        | 900    | μΑ         |

| Power Supply Rejection                     |                                           |               | ± 0.3      |        | mV/V       |

Figure 6.4. AMX0CF: AMUX Configuration Register (C8051F01x)

| R/W      | R/W            | R/W            | R/W            | R/W            | R/W           | R/W            | R/W        | Reset Value  |

|----------|----------------|----------------|----------------|----------------|---------------|----------------|------------|--------------|

| -        | -              | -              | -              | AIN67IC        | AIN45IC       | AIN23IC        | AIN01IC    | 00000000     |

| Bit7     | Bit6           | Bit5           | Bit4           | Bit3           | Bit2          | Bit1           | Bit0       | SFR Address: |

|          |                |                |                |                |               |                |            | 0xBA         |

| Bits7-4: | UNUSED. Read   | d = 0000b; W   | rite = don't   | care           |               |                |            |              |

| Bit3:    | AIN67IC: AIN6  | , AIN7 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN6 and AI | N7 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN6, AIN7  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

| Bit2:    | AIN45IC: AIN4  | , AIN5 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN4 and AI | N5 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN4, AIN5  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

| Bit1:    | AIN23IC: AIN2  | , AIN3 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN2 and AI | N3 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN2, AIN3  |                |                |                | ıt pair       |                |            |              |

| Bit0:    | AIN01IC: AIN0  | , AIN1 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN0 and AI | N1 are indep   | endent single  | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN0, AIN1  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

|          |                |                |                |                |               |                |            |              |

| NOTE:    | The ADC Data V | Word is in 2's | s complemen    | t format for a | channels cont | figured as dif | ferential. |              |

|          |                |                |                |                |               |                |            |              |

| R/W         | R/W           | R/W           | R/W              | R/W           | R/W    | R/W    | R/W    | Reset Value  |

|-------------|---------------|---------------|------------------|---------------|--------|--------|--------|--------------|

| ADCSC2      | ADCSC1        | ADCSC0        | -                | -             | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |

| Bit7        | Bit6          | Bit5          | Bit4             | Bit3          | Bit2   | Bit1   | Bit0   | SFR Address: |

|             |               |               |                  |               |        |        |        | 0xBC         |

| Bits7-5: AD | CSC2-0: AD    | C SAR Conv    | version Clocl    | k Period Bits |        |        |        |              |

| 000         | ): SAR Conv   | version Clock | = 1 System       | Clock         |        |        |        |              |

| 001         | : SAR Conv    | version Clock | = 2 System       | Clocks        |        |        |        |              |

| 010         | : SAR Conv    | version Clock | = 4 System       | Clocks        |        |        |        |              |

| 011         | : SAR Conv    | version Clock | = 8 System       | Clocks        |        |        |        |              |

| 1xx         | : SAR Conv    | version Clock | = 16 System      | ns Clocks     |        |        |        |              |

| (No         | ote: Convers  | ion clock sho | uld be $\leq 2M$ | IHz.)         |        |        |        |              |

| Bits4-3: UN | USED. Rea     | d = 00b; Writ | e = don't can    | re            |        |        |        |              |

| Bits2-0: AN | IPGN2-0: AI   | DC Internal A | mplifier Gai     | in            |        |        |        |              |

| 000         | ): Gain = $1$ |               | -                |               |        |        |        |              |

| 001         | : Gain $= 2$  |               |                  |               |        |        |        |              |

| 010         | Chain = $4$   |               |                  |               |        |        |        |              |

| 011         | : Gain = 8    |               |                  |               |        |        |        |              |

| 10x         | : Gain = $16$ |               |                  |               |        |        |        |              |

| 11x         | : Gain = 0.5  |               |                  |               |        |        |        |              |

|             |               |               |                  |               |        |        |        |              |

#### Figure 6.6. ADC0CF: ADC Configuration Register (C8051F01x)

| R/W          | R/W             | R/W           | R/W            | R/W                                      | R/W             | R/W            | R/W               | Reset Value |

|--------------|-----------------|---------------|----------------|------------------------------------------|-----------------|----------------|-------------------|-------------|

| ADCE         | N ADCTM         | ADCINT        | ADBUSY         | ADSTM1                                   | ADSTM0          | ADWINT         | ADLJST            | 0000000     |

| Bit7         | Bit6            | Bit5          | Bit4           | Bit3                                     | Bit2            | Bit1           | Bit0              | SFR Addres  |

|              |                 |               |                |                                          |                 |                | (bit addressable) | 0xE8        |

| Bit7:        | ADCEN: ADC      | Enable Bit    |                |                                          |                 |                |                   |             |

|              | 0: ADC Disabl   | ed. ADC is i  | n low power    | shutdown.                                |                 |                |                   |             |

|              | 1: ADC Enable   |               |                |                                          | onversions.     |                |                   |             |

| Bit6:        | ADCTM: ADC      |               |                | •                                        |                 |                |                   |             |

|              | 0: When the A   | DC is enable  | d, tracking is | always done                              | unless a con    | version is in  | process           |             |

|              | 1: Tracking De  |               |                | -                                        |                 |                | -                 |             |

|              | ADST            | M1-0:         |                |                                          |                 |                |                   |             |

|              | 00: Ti          | acking starts | with the writ  | te of 1 to AD                            | BUSY and la     | asts for 3 SA  | R clocks          |             |

|              | 01: Tı          | acking starte | d by the over  | flow of Time                             | er 3 and last f | For 3 SAR clo  | ocks              |             |

|              | 10: A           | DC tracks on  | ly when CNV    | /STR input is                            | s logic low     |                |                   |             |

|              | 11: Ti          | acking starte | d by the over  | flow of Time                             | er 2 and last f | for 3 SAR clo  | ocks              |             |

| Bit5:        | ADCINT: ADC     | C Conversion  | Complete In    | terrupt Flag                             |                 |                |                   |             |

|              | (Must be cleare |               |                |                                          |                 |                |                   |             |

|              | 0: ADC has no   |               |                |                                          | e last time thi | s flag was cl  | eared             |             |

|              | 1: ADC has co   |               | a conversion   |                                          |                 |                |                   |             |

| Bit4:        | ADBUSY: AD      | C Busy Bit    |                |                                          |                 |                |                   |             |

|              | Read            |               |                |                                          |                 |                |                   |             |

|              | 0: ADC Conve    |               |                |                                          |                 | since a reset. | The falling       |             |

|              |                 | BUSY genera   |                | ipt when ena                             | bled.           |                |                   |             |

|              | 1: ADC Busy of  | converting da | ta             |                                          |                 |                |                   |             |

|              | Write           |               |                |                                          |                 |                |                   |             |

|              | 0: No effect    |               |                |                                          |                 |                |                   |             |

|              | 1: Starts ADC   |               |                |                                          |                 |                |                   |             |

| Bits3-2:     | ADSTM1-0: A     |               |                |                                          |                 |                |                   |             |

|              | 00: ADC conv    |               |                |                                          |                 |                |                   |             |

|              | 01: ADC conv    |               |                |                                          |                 |                |                   |             |

|              | 10: ADC conv    |               |                |                                          |                 |                |                   |             |

| <b>D</b> . 4 | 11: ADC conv    |               | •              |                                          | her 2           |                |                   |             |

| Bit1:        | ADWINT: AD      |               |                | rupt Flag                                |                 |                |                   |             |

|              | (Must be cleare |               |                |                                          |                 |                |                   |             |

|              | 0: ADC Windo    |               |                |                                          | urred           |                |                   |             |

| <b>D</b> '/0 | 1: ADC Windo    |               |                | n occurred                               |                 |                |                   |             |

| Bit0:        | ADLJST: ADC     |               |                | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. |                 |                |                   |             |

|              | 0: Data in ADC  |               |                |                                          |                 |                |                   |             |

|              | 1: Data in ADO  | LUH:ADCUL     | Registers is   | iert justified                           |                 |                |                   |             |

|              |                 |               |                |                                          |                 |                |                   |             |

|              |                 |               |                |                                          |                 |                |                   |             |

#### Figure 6.7. ADC0CN: ADC Control Register (C8051F01x)

register configured for accessing the external data memory space. Refer to Section 11 (Flash Memory) for further details.

| Figure 10.6. | <b>PSW: Program</b> | n Status Word |

|--------------|---------------------|---------------|

|--------------|---------------------|---------------|

| CY      | R/W                                                                               | R/W                                                                                                           | R/W                                                                       | R/W                                                             | R/W                                                | R/W                    | R/W                       | Reset Valu         |

|---------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|------------------------|---------------------------|--------------------|

|         | AC                                                                                | F0                                                                                                            | RS1                                                                       | RS0                                                             | OV                                                 | F1                     | PARITY                    | 0000000            |

| Bit7    | Bit6                                                                              | Bit5                                                                                                          | Bit4                                                                      | Bit3                                                            | Bit2                                               | Bit1                   | Bit0<br>(bit addressable) | SFR Addres<br>0xD0 |

| Bit7:   | CY: Carry Fla<br>This bit is set<br>(subtraction).                                | when the las                                                                                                  |                                                                           |                                                                 |                                                    | (addition) o           | or a borrow               |                    |

| Bit6:   | AC: Auxiliary<br>This bit is set<br>borrow from (<br>operations.                  | when the las                                                                                                  |                                                                           |                                                                 |                                                    |                        |                           |                    |

| Bit5:   | F0: User Flag<br>This is a bit-ad                                                 |                                                                                                               | eneral purpo                                                              | se flag for us                                                  | e under softw                                      | are control            |                           |                    |

| Bits4-3 | RS1-RS0: Reg<br>These bits sele                                                   |                                                                                                               |                                                                           | used during                                                     | register acces                                     | ses.                   |                           |                    |

|         | RS1 RS                                                                            | 0 Registe                                                                                                     | er Bank                                                                   | Address                                                         |                                                    |                        |                           |                    |

|         | 0 0                                                                               |                                                                                                               |                                                                           | x00-0x07                                                        |                                                    |                        |                           |                    |

|         | 0 1                                                                               |                                                                                                               |                                                                           | x08-0x0F                                                        |                                                    |                        |                           |                    |

|         | 1 0                                                                               |                                                                                                               | 2 0                                                                       | x10-0x17                                                        |                                                    |                        |                           |                    |

|         | 1 1                                                                               | ,                                                                                                             | 3 0                                                                       | x18-0x1F                                                        |                                                    |                        |                           |                    |

| Bit2:   | <ul> <li>A MUL i</li> <li>A DIV in</li> <li>The OV bit is other cases.</li> </ul> | Rn, A" instr<br>7 Flag.<br>to 1 under th<br>, ADDC, or 5<br>nstruction re<br>istruction cau<br>6 cleared to 0 | uction.<br>e following o<br>SUBB instru<br>sults in an o<br>ises a divide | circumstance:<br>ction causes<br>verflow (resu<br>-by-zero conc | s:<br>a sign-change<br>lt is greater th<br>lition. | overflow.<br>an 255) . |                           |                    |

| Bit1:   | F1: User Flag<br>This is a bit-a                                                  |                                                                                                               | eneral purpo                                                              | se flag for us                                                  | e under softw                                      | are control            |                           |                    |

|         | DADITV. Dor                                                                       | ity Flag.                                                                                                     |                                                                           |                                                                 |                                                    |                        |                           |                    |

| R/W           | R/W                              | R/W             | R/W            | R/W            | R/W             | R/W      | R/W   | Reset Value              |

|---------------|----------------------------------|-----------------|----------------|----------------|-----------------|----------|-------|--------------------------|

| PCP1R<br>Bit7 | PCP1F<br>Bit6                    | PCP0R<br>Bit5   | PCP0F<br>Bit4  | PPCA0<br>Bit3  | PWADC0<br>Bit2  | PSMB0    | PSPI0 | 00000000<br>SFR Address: |

| Blt/          | BIIO                             | B115            | B1t4           | BIt3           | BIt2            | Bit1     | Bit0  | 0xF6                     |

|               |                                  |                 |                |                |                 |          |       | OXI 0                    |

| Bit7:         | PCP1R: Comp                      | normator 1 (CD  | 1) Dising In   | tormunt Drioni | ty Control      |          |       |                          |

| DII/.         | This bit sets th                 |                 |                |                | ty Control.     |          |       |                          |

|               | 0: CP1 rising                    |                 |                |                |                 |          |       |                          |

|               | 1: CP1 rising                    | -               | -              | •              |                 |          |       |                          |

|               | 6                                |                 | 01             |                |                 |          |       |                          |

| Bit6:         | PCP1F: Comp                      | oarator 1 (CP   | 1) Falling In  | terrupt Priori | ty Control.     |          |       |                          |

|               | This bit sets th                 |                 |                |                |                 |          |       |                          |

|               | 0: CP1 falling                   |                 |                |                |                 |          |       |                          |

|               | 1: CP1 falling                   | g interrupt set | t to high pric | ority level.   |                 |          |       |                          |

| Bit5:         | PCP0R: Comp                      | parator 0 (CD   | () Dising In   | tormunt Driani | ty Control      |          |       |                          |

| DILJ.         | This bit sets th                 |                 |                |                | ty Control.     |          |       |                          |

|               | 0: CP0 rising                    |                 |                |                |                 |          |       |                          |

|               | 1: CP0 rising                    |                 |                |                |                 |          |       |                          |

|               | U                                | 1               | 0 1            | 5              |                 |          |       |                          |

| Bit4:         | PCP0F: Comp                      | oarator 0 (CP   | 0) Falling In  | terrupt Priori | ty Control.     |          |       |                          |

|               | This bit sets th                 |                 |                |                |                 |          |       |                          |

|               | 0: CP0 falling                   |                 |                |                |                 |          |       |                          |

|               | 1: CP0 falling                   | g interrupt set | to high pric   | ority level.   |                 |          |       |                          |

| Bit3:         | PPCA0: Progr                     | ammable Co      | unter Array    | (PCA0) Inter   | runt Priority ( | Control  |       |                          |

| Dito.         | This bit sets th                 |                 |                |                |                 | controll |       |                          |

|               | 0: PCA0 inter                    |                 |                |                |                 |          |       |                          |

|               | 1: PCA0 inter                    |                 |                |                |                 |          |       |                          |

|               |                                  |                 |                |                |                 |          |       |                          |

| Bit2:         | PWADC0: AI                       |                 |                |                |                 |          |       |                          |

|               | This bit sets th                 |                 |                |                |                 |          |       |                          |

|               | 0: ADC0 Win                      |                 |                |                |                 |          |       |                          |

|               | 1: ADC0 Wir                      | idow interrup   | ot set to high | priority leve  | 1.              |          |       |                          |

| Bit1:         | PSMB0: SMB                       | sus 0 Interrun  | ot Priority Co | ontrol.        |                 |          |       |                          |

| Ditti         | This bit sets th                 |                 |                |                |                 |          |       |                          |

|               | 0: SMBus inte                    | 1 *             |                | 1              |                 |          |       |                          |

|               | 1: SMBus inte                    |                 |                |                |                 |          |       |                          |

|               |                                  |                 | -              |                |                 |          |       |                          |

| Bit0:         | PSPI0: Serial                    |                 |                |                | y Control.      |          |       |                          |

|               | This bit sets th                 |                 |                |                |                 |          |       |                          |

|               | 0: SPI0 interr<br>1: SPI0 interr |                 |                |                |                 |          |       |                          |

|               | 1. SPIU interr                   | upt set to mg   | n priority le  | vel.           |                 |          |       |                          |

|               |                                  |                 |                |                |                 |          |       |                          |

### Figure 10.13. EIP1: Extended Interrupt Priority 1

#### 16.2. Operation

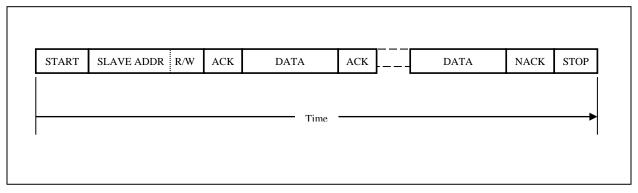

A typical SMBus transaction consists of a START condition, followed by an address byte, one or more bytes of data, and a STOP condition. The address byte and each of the data bytes are followed by an ACKNOWLEDGE bit from the receiver. The address byte consists of a 7-bit address plus a direction bit. The direction bit (R/W) occupies the least-significant bit position of the address. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation. A general call address (0x00 + R/W) is recognized by all slave devices allowing a master to address multiple slave devices simultaneously.

All transactions are initiated by the master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACKNOWLEDGE from the slave at the end of each byte. If it is a READ operation, the slave transmits the data waiting for an ACKNOWLEDGE from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 16.3 illustrates a typical SMBus transaction.

Figure 16.3. SMBus Transaction

The SMBus interface may be configured to operate as either a master or a slave. At any particular time, it will be operating in one of the following four modes:

#### 16.2.1. Master Transmitter Mode

Serial data is transmitted on SDA while the serial clock is output on SCL. The first byte transmitted contains the address of the target slave device and the data direction bit. In this case the data direction bit (R/W) will be logic 0 to indicate a "WRITE" operation. The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. To indicate the beginning and the end of the serial transfer, the master device outputs START and STOP conditions.

#### 16.2.2. Master Receiver Mode

Serial data is received on SDA while the serial clock is output on SCL. The first byte is transmitted by the master and contains the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. Serial data is then received from the slave on SDA while the master outputs the serial clock. The slave transmits one or more bytes of serial data. After each byte is received, an acknowledge bit is transmitted by the master. The master outputs START and STOP conditions to indicate the beginning and end of the serial transfer.

#### **16.2.3.** Slave Transmitter Mode

Serial data is transmitted on SDA while the serial clock is received on SCL. First, a byte is received that contains an address and data direction bit. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. If the received address matches the slave's assigned address (or a general call address is received) one or more bytes of serial data are transmitted to the master. After each byte is received, an acknowledge bit is transmitted by the master. The master outputs START and STOP conditions to indicate the beginning and end of the serial transfer.

#### 17.4. SPI Special Function Registers

The SPI is accessed and controlled through four special function registers in the system controller: SPIOCN Control Register, SPIODAT Data Register, SPIOCFG Configuration Register, and SPIOCKR Clock Rate Register. The four special function registers related to the operation of the SPI Bus are described in the following section.

| Figure 17.5.      | SPI0CFG: | SPI Cor | nfiguration | Register                              |

|-------------------|----------|---------|-------------|---------------------------------------|

| I Igui e I / ie i |          |         | mgui unon   | I I I I I I I I I I I I I I I I I I I |

| CUDITA  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                |                                                                          | R                                                                                                   | R                                         | R/W                                | R/W           | R/W     | Reset Valu         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|---------------|---------|--------------------|

| СКРНА   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BC                                                                                                               |                                                                          | BC1                                                                                                 | BC0                                       | SPIFRS2                            | SPIFRS1       | SPIFRS0 | 0000011            |

| Bit7    | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit5                                                                                                             | 5                                                                        | Bit4                                                                                                | Bit3                                      | Bit2                               | Bit1          | Bit0    | SFR Addres<br>0x9A |

| D'47.   | CKPHA: SI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                  | 1                                                                        |                                                                                                     |                                           |                                    |               |         | 0.1.711            |

| Bit7:   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                  |                                                                          |                                                                                                     |                                           |                                    |               |         |                    |

|         | This bit con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                  |                                                                          | -                                                                                                   | amiad                                     |                                    |               |         |                    |

|         | 0: Data sam<br>1: Data sam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                  |                                                                          |                                                                                                     |                                           |                                    |               |         |                    |

|         | 1. Data sam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | pied on se                                                                                                       | cond ed                                                                  | ge of SCr                                                                                           | x period.                                 |                                    |               |         |                    |

| Bit6:   | CKPOL: SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                  |                                                                          |                                                                                                     |                                           |                                    |               |         |                    |

|         | This bit con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                  |                                                                          | polarity.                                                                                           |                                           |                                    |               |         |                    |

|         | 0: SCK line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                  |                                                                          |                                                                                                     |                                           |                                    |               |         |                    |

|         | 1: SCK line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | high in id                                                                                                       | le state.                                                                |                                                                                                     |                                           |                                    |               |         |                    |

| Bits5-3 | : BC2-BC0: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SPI Bit Co                                                                                                       | unt                                                                      |                                                                                                     |                                           |                                    |               |         |                    |

| D165 5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                  |                                                                          | bits of the                                                                                         | e SPI word h                              | ave been tran                      | smitted.      |         |                    |