#### Silicon Labs - C8051F012 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 20MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT          |

| Number of I/O              | 8                                                           |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | ·                                                           |

| RAM Size                   | 256 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 4x10b; D/A 2x12b                                        |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f012 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

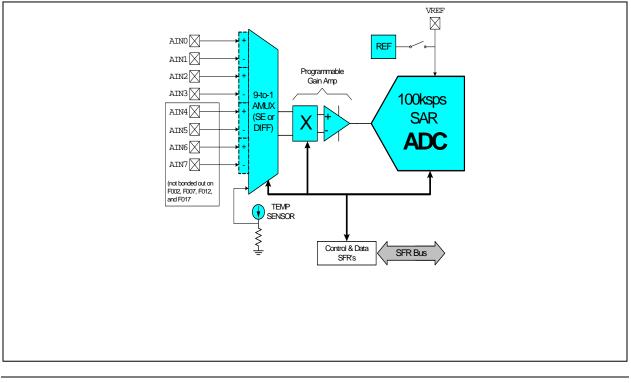

Figure 1.1. C8051F000/05/10/15 Block Diagram

### **1.5.** Programmable Counter Array

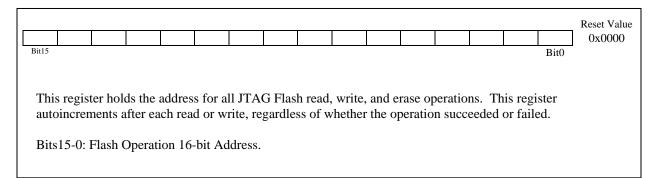

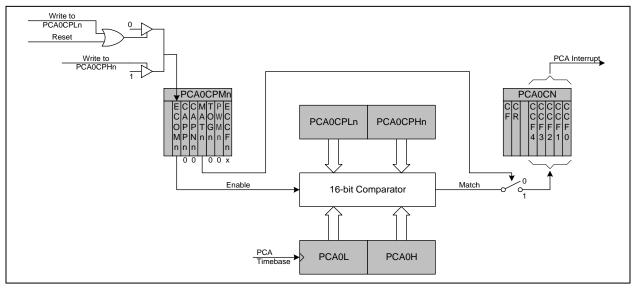

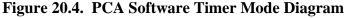

The C8051F000 MCU family has an on-board Programmable Counter/Timer Array (PCA) in addition to the four 16-bit general-purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer timebase with 5 programmable capture/compare modules. The timebase gets its clock from one of four sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflow, or an External Clock Input (ECI).

Each capture/compare module can be configured to operate in one of four modes: Edge-Triggered Capture, Software Timer, High Speed Output, or Pulse Width Modulator. The PCA Capture/Compare Module I/O and External Clock Input are routed to the MCU Port I/O via the Digital Crossbar.

### **1.6.** Serial Ports

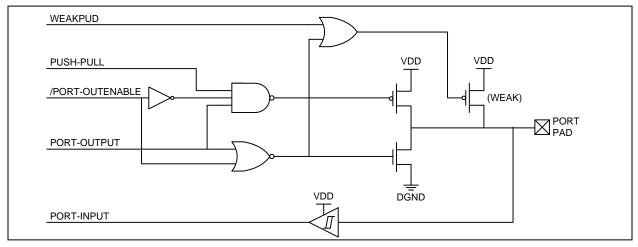

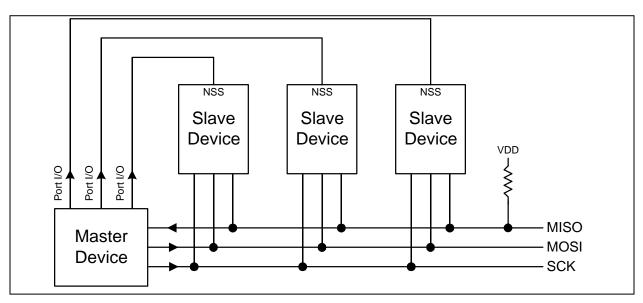

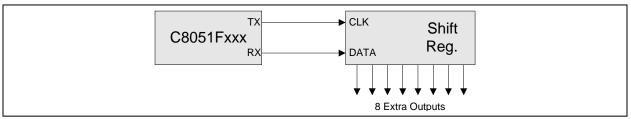

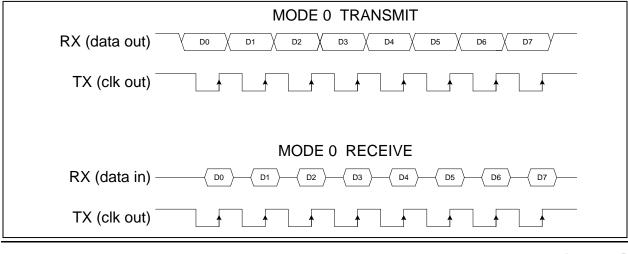

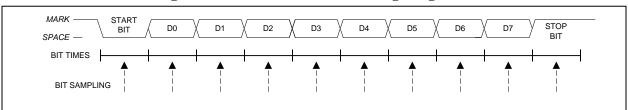

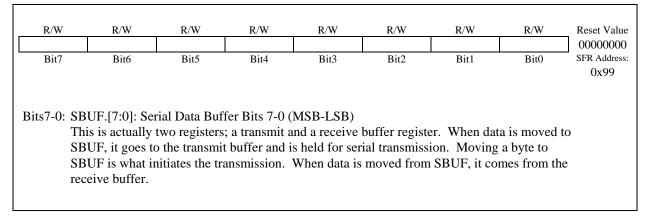

The C8051F000 MCU Family includes a Full-Duplex UART, SPI Bus, and I2C/SMBus. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little intervention by the CPU. The serial buses do not "share" resources such as timers, interrupts, or Port I/O, so any or all of the serial buses may be used together.

## **1.7.** Analog to Digital Converter

The C8051F000/1/2/5/6/7 has an on-chip 12-bit SAR ADC with a 9-channel input multiplexer and programmable gain amplifier. With a maximum throughput of 100ksps, the ADC offers true 12-bit accuracy with an INL of  $\pm$ 1LSB. The ADC in the C8051F010/1/2/5/6/7 is similar, but with 10-bit resolution. Each ADC has a maximum throughput of 100ksps. Each ADC has an INL of  $\pm$ 1LSB, offering true 12-bit accuracy with the C8051F00x, and true 10-bit accuracy with the C8051F01x. There is also an on-board 15ppm voltage reference, or an external reference may be used via the VREF pin.

The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. One input channel is tied to an internal temperature sensor, while the other eight channels are available externally. Each pair of the eight external input channels can be configured as either two single-ended inputs or a single differential input. The system controller can also put the ADC into shutdown to save power.

A programmable gain amplifier follows the analog multiplexer. The gain can be set in software from 0.5 to 16 in powers of 2. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset (in differential mode, a DAC could be used to provide the DC offset).

Conversions can be started in four ways; a software command, an overflow on Timer 2, an overflow on Timer 3, or an external signal input. This flexibility allows the start of conversion to be triggered by software events, external HW signals, or convert continuously. A completed conversion causes an interrupt, or a status bit can be polled in software to determine the end of conversion. The resulting 10 or 12-bit data word is latched into two SFRs upon completion of a conversion. The data can be right or left justified in these registers under software control.

Compare registers for the ADC data can be configured to interrupt the controller when ADC data is within a specified window. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within the specified window.

### Figure 1.10. ADC Diagram

| R/W         | R/W            | R/W           | R/W           | R/W           | R/W    | R/W    | R/W    | Reset Value  |

|-------------|----------------|---------------|---------------|---------------|--------|--------|--------|--------------|

| ADCSC2      | ADCSC1         | ADCSC0        | -             | -             | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |

| Bit7        | Bit6           | Bit5          | Bit4          | Bit3          | Bit2   | Bit1   | Bit0   | SFR Address: |

|             |                |               |               |               |        |        |        | 0xBC         |

| Bits7-5. AD | CSC2-0. AL     | C SAR Conv    | version Clock | e Period Bits |        |        |        |              |

|             |                | version Clock |               |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | version Clock | •             |               |        |        |        |              |

|             |                | Conversion C  | •             |               | )      |        |        |              |

|             |                | d = 00b; Writ |               | ,             | ,<br>, |        |        |              |

|             |                | DC Internal A |               |               |        |        |        |              |

|             | ): Gain = 1    |               | 1             |               |        |        |        |              |

| 001         | : Gain = 2     |               |               |               |        |        |        |              |

| 010         | ): $Gain = 4$  |               |               |               |        |        |        |              |

| 011         | : Gain = 8     |               |               |               |        |        |        |              |

| 10x         | : Gain = 16    |               |               |               |        |        |        |              |

| 11x         | : Gain $= 0.5$ | i             |               |               |        |        |        |              |

|             |                |               |               |               |        |        |        |              |

# Figure 5.6. ADC0CF: ADC Configuration Register (C8051F00x)

33

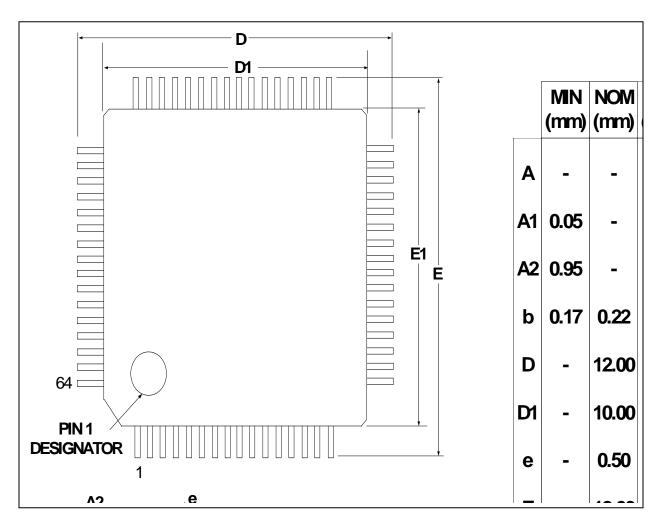

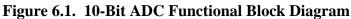

# 6. ADC (10-Bit, C8051F010/1/2/5/6/7 Only)

The ADC subsystem for the C8051F010/1/2/5/6/7 consists of a 9-channel, configurable analog multiplexer (AMUX), a programmable gain amplifier (PGA), and a 100ksps, 10-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector (see block diagram in Figure 6.1). The AMUX, PGA, Data Conversion Modes, and Window Detector are all configurable under software control via the Special Function Register's shown in Figure 6.1. The ADC subsystem (ADC, track-and-hold and PGA) is enabled only when the ADCEN bit in the ADC Control register (ADC0CN, Figure 6.7) is set to 1. The ADC subsystem is in low power shutdown when this bit is 0. The Bias Enable bit (BIASE) in the REF0CN register (see Figure 9.2) must be set to 1 in order to supply bias to the ADC.

### 6.1. Analog Multiplexer and PGA

Eight of the AMUX channels are available for external measurements while the ninth channel is internally connected to an on-board temperature sensor (temperature transfer function is shown in Figure 6.3). Note that the PGA gain is applied to the temperature sensor reading. AMUX input pairs can be programmed to operate in either the differential or single-ended mode. This allows the user to select the best measurement technique for each input channel, and even accommodates mode changes "on-the-fly". The AMUX defaults to all single-ended inputs upon reset. There are two registers associated with the AMUX: the Channel Selection register AMX0SL (Figure 6.5), and the Configuration register AMX0CF (Figure 6.4). The table in Figure 6.5 shows AMUX functionality by channel for each possible configuration. The PGA amplifies the AMUX output signal by an amount determined by the AMPGN2-0 bits in the ADC Configuration register, ADC0CF (Figure 6.6). The PGA can be software-programmed for gains of 0.5, 1, 2, 4, 8 or 16. It defaults to unity gain on reset.

| Bit7       Bit6       Bit5       Bit4       Bit3       Bit2       Bit1       Bit0         (bit addressable)       (bit addressable)       (bit addressable)       (bit addressable)         Bit7:       ADCEN: ADC Enable Bit       (bit addressable)       (bit addressable)         Bit7:       ADC Disabled. ADC is in low power shutdown.       (bit addressable)         1:       ADC Enabled. ADC is active and ready for data conversions.         Bit6:       ADCTM: ADC Track Mode Bit       (c)         (c)       When the ADC is enabled, tracking is always done unless a conversion is in process         1:       Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks         01:       Tracking started by the overflow of Timer 3 and last for 3 SAR clocks         10:       ADC tracks only when CNVSTR input is logic low         11:       Tracking started by the overflow of Timer 2 and last for 3 SAR clocks         Bit5:       ADCINT: ADC Conversion Complete Interrupt Flag         (Must be cleared by software)       0: ADC tacs completed a data conversion since the last time this flag was cleared         1:       ADC Busy generates an interrupt when enabled.       1: ADC Busy converting data         Write       0: ADC Conversion if ADSTM1-0 = 00b       0b         Bit3:-2:       ADSTM1-0: ADC Start of Conversion Mode Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset Valu |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <ul> <li>(bit addressable)</li> <li>(bit addressable)</li> <li>(bit addressable)</li> <li>(c) ADC Enabled. ADC is in low power shutdown.</li> <li>1: ADC Enabled. ADC is active and ready for data conversions.</li> <li>(b) ADC Tack Mode Bit</li> <li>(c) When the ADC is enabled, tracking is always done unless a conversion is in process</li> <li>1: Tracking befined by ADSTM1-0 bits             ADSTM1-0:             00: Track Mode Bit</li> <li>(c) When the ADC is enabled, tracking is always done unless a conversion is in process</li> <li>1: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks             01: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks             01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks             11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks             11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks             11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks         </li> <li>(Must be cleared by software)         <ul> <li>(Must be cleared by software)</li> <li>(D) ADC thas not completed a data conversion since the last time this flag was cleared</li> <li>(ADC has completed a data conversion</li> </ul> </li> <li>(Bit4: ADBUSY: ADC Busy Bit         <ul> <li>(Read)</li> <li>(C) ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>(F) ADC Busy converting data</li> <li>(F) No effect         <ul> <li>(F) Starts ADC Conversion if ADSTM1-0 = 00b</li> </ul> </li> <li>(Bits-2: ADSTM1-0: ADC Start of Conversion Mode Bits         <ul> <li>(F) ADC conversion started upon every write of 1 to ADBUSY</li> <li>(F) ADC conversion started upon every overflow of Timer 3</li> <li>(F) ADC conversion started upon every overflow of Timer 3</li> <li>(F) ADC conversion started upon every overflow of Timer 2</li> </ul> </li> <li>(Bit1: ADWINT: ADC Window Compare Interrup</li></ul></li></ul> | 0000000    |

| <ul> <li>Bit7: ADCEN: ADC Enable Bit</li> <li>0: ADC Disabled. ADC is in low power shutdown.</li> <li>1: ADC Enabled. ADC is active and ready for data conversions.</li> <li>Bit6: ADCTM: ADC Track Mode Bit</li> <li>0: When the ADC is enabled, tracking is always done unless a conversion is in process</li> <li>1: Tracking Defined by ADSTM1-0 bits<br/>ADSTM1-0:</li> <li>00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks</li> <li>01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks</li> <li>10: ADC tracks only when CNVSTR input is logic low</li> <li>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> <li>10: ADC tracks only when CNVSTR input is logic low</li> <li>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag</li> <li>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit</li> <li>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data</li> <li>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversion started upon every overflow of Timer 3</li> <li>10: ADC conversion started upon every overflow of Timer 2</li> <li>Bit1: ADC Conversion started upon every overflow of Timer 2</li> <li>Bit1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Win</li></ul>       | SFR Addres |

| <ul> <li>0: ADC Disabled. ADC is in low power shutdown.</li> <li>1: ADC Enabled. ADC is active and ready for data conversions.</li> <li>Bit6: ADCTM: ADC Track Mode Bit</li> <li>0: When the ADC is enabled, tracking is always done unless a conversion is in process <ol> <li>1: Tracking Defined by ADSTM1-0 bits</li> <li>ADSTM1-0:</li> <li>00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks</li> <li>01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks</li> <li>10: ADC tracks only when CNVSTR input is logic low</li> <li>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> </ol> </li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag (Must be cleared by software) <ol> <li>ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion</li> </ol> </li> <li>Bit4: ADBUSY: ADC Busy Bit Read <ol> <li>ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled. <ol> <li>ADC Busy converting data</li> <li>Write</li> <li>No effect</li> <li>Starts ADC Conversion if ADSTM1-0 = 00b</li> </ol> </li> <li>Bit5-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>ADC conversion started upon every write of 1 to ADBUSY</li> <li>ADC conversion started upon every overflow of Timer 3</li> <li>ADC conversion started upon every overflow of Timer 2</li> <li>Bit1: ADC conversion started upon every overflow of Timer 2</li> <li>Bit1: ADC Conversion started upon every overflow of Timer 2</li> <li>Bit1: ADC Window Compare Interrupt Flag</li> <li>(Must be cleared by software)</li> <li>ADC Conversion tatate has not occurred</li> <li>ADC Conversion tatate the on every overflow of Timer 2</li> <li>Bit1: ADC Window Comparison Data match has not occurred</li> <li>ADC Window Comparison Data match hoccurred</li> <li>C. ADC Window Comparison Data match has not occurred</li> </ol> </li> </ul>                                                                | 0xE8       |

| <ol> <li>ADC Enabled. ADC is active and ready for data conversions.</li> <li>ADCTM: ADC Track Mode Bit</li> <li>When the ADC is enabled, tracking is always done unless a conversion is in process         <ol> <li>Tracking Defined by ADSTM1-0 bits</li></ol></li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| <ol> <li>ADC Enabled. ADC is active and ready for data conversions.</li> <li>ADCTM: ADC Track Mode Bit</li> <li>When the ADC is enabled, tracking is always done unless a conversion is in process         <ol> <li>Tracking Defined by ADSTM1-0 bits</li></ol></li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| <ul> <li>Bit6: ADCTM: ADC Track Mode Bit <ul> <li>0: When the ADC is enabled, tracking is always done unless a conversion is in process</li> <li>1: Tracking Defined by ADSTM1-0 bits <ul> <li>ADSTM1-0:</li> <li>00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks</li> <li>01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks</li> <li>10: ADC tracks only when CNVSTR input is logic low</li> <li>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> </ul> </li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag <ul> <li>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion</li> </ul> </li> <li>Bit4: ADBUSY: ADC Busy Bit <ul> <li>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data</li> <li>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> </ul> </li> <li>Bit3: ADS Conversion started upon every write of 1 to ADBUSY <ul> <li>01: ADC conversion started upon every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> </ul> </li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag <ul> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> </ul> </li> <li>Bit0: ADLC Window Comparison Data match occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>1: ADL ST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right</li></ul></li></ul>  |            |

| <ul> <li>1: Tracking Defined by ADSTM1-0 bits<br/>ADSTM1-0:<br/>00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks<br/>01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks<br/>01: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks<br/>10: ADC tracks only when CNVSTR input is logic low<br/>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared<br/>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit<br/>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling<br/>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bit5-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY<br/>01: ADC conversion started upon every overflow of Timer 3<br/>10: ADC conversion started upon every overflow of Timer 3</li> <li>11: ADC conversion started upon every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred<br/>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH:ADCUL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                              |            |

| <ul> <li>1: Tracking Defined by ADSTM1-0 bits<br/>ADSTM1-0:<br/>00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks<br/>01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks<br/>10: ADC tracks only when CNVSTR input is logic low<br/>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared<br/>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit<br/>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling<br/>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bit53-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY<br/>01: ADC conversions tatted upon every write of 1 to ADBUSY<br/>01: ADC conversions tatted upon every overflow of Timer 3<br/>10: ADC conversions tatted upon every overflow of Timer 3</li> <li>10: ADC conversions tatted upon every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred<br/>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                             |            |

| <ul> <li>00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks</li> <li>01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks</li> <li>10: ADC tracks only when CNVSTR input is logic low</li> <li>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag</li> <li>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has not completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit</li> <li>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data</li> <li>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 3</li> <li>11: ADC conversions taken on every overflow of Timer 3</li> <li>12: ADC Conversions taken on every overflow of Timer 3</li> <li>13: ADC conversions taken on every overflow of Timer 3</li> <li>14: ADC conversions taken on every overflow of Timer 3</li> <li>15: ADC conversions taken on every overflow of Timer 3</li> <li>16: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag</li> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLOWINGW Comparison Data match occurred</li> <li>Bit0: ADLUST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                        |            |

| <ul> <li>01: Tracking started by the overflow of Timer 3 and last for 3 SAR clocks<br/>10: ADC tracks only when CNVSTR input is logic low<br/>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared<br/>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit<br/>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling<br/>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bit3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversion started upon every overflow of Timer 3</li> <li>10: ADC conversion started upon every overflow of Timer 3</li> <li>11: ADC conversions taken on every overflow of Timer 3</li> <li>12: ADC Conversions taken on every overflow of Timer 3</li> <li>13: ADC Conversions taken on every overflow of Timer 3</li> <li>14: ADC Conversions taken on every overflow of Timer 3</li> <li>15: ADC Conversions taken on every overflow of Timer 2</li> <li>11: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                              |            |

| <ul> <li>10: ADC tracks only when CNVSTR input is logic low <ol> <li>Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> </ol> </li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag <ul> <li>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion</li> </ul> </li> <li>Bit4: ADBUSY: ADC Busy Bit <ul> <li>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling <ul> <li>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data</li> <li>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> </ul> </li> <li>Bit3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversion started upon every rising edge of CNVSTR <ul> <li>11: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> </ul> </li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag <ul> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match cocurred</li> </ul> </li> <li>Bit0: ADLJST: ADC Left Justify Data Bit <ul> <li>0: Data in ADC0H: ADC0L Registers is right justified</li> </ul> </li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| <ul> <li>11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks</li> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag (Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bit3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 3</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag (Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH:ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| <ul> <li>Bit5: ADCINT: ADC Conversion Complete Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit<br/>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling<br/>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bit3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

| <ul> <li>(Must be cleared by software)</li> <li>0: ADC has not completed a data conversion since the last time this flag was cleared</li> <li>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit</li> <li>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data</li> <li>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADC Window Compare Interrupt Flag</li> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADC0H: ADC0L Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| <ul> <li>O: ADC has not completed a data conversion since the last time this flag was cleared <ol> <li>ADC has completed a data conversion</li> </ol> </li> <li>Bit4: ADBUSY: ADC Busy Bit <ul> <li>Read</li> <li>O: ADC Conversion complete or no valid data has been converted since a reset. The falling <ul> <li>edge of ADBUSY generates an interrupt when enabled.</li> <li>I: ADC Busy converting data</li> <li>Write</li> <li>O: No effect</li> <li>I: Starts ADC Conversion if ADSTM1-0 = 00b</li> </ul> </li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits <ul> <li>O0: ADC conversion started upon every write of 1 to ADBUSY</li> <li>O1: ADC conversions taken on every overflow of Timer 3</li> <li>IO: ADC conversions taken on every overflow of Timer 3</li> <li>IO: ADC conversions taken on every overflow of Timer 2</li> </ul> </li> <li>Bit1: ADCWindow Compare Interrupt Flag <ul> <li>(Must be cleared by software)</li> <li>O: ADC Window Comparison Data match has not occurred</li> <li>I: ADC Window Comparison Data match occurred</li> </ul> </li> <li>Bit0: ADLJST: ADC Left Justify Data Bit <ul> <li>O: Data in ADCOH: ADCOL Registers is right justified</li> </ul> </li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| <ul> <li>1: ADC has completed a data conversion</li> <li>Bit4: ADBUSY: ADC Busy Bit<br/>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling<br/>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| <ul> <li>Bit4: ADBUSY: ADC Busy Bit<br/>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling<br/>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH:ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| <ul> <li>Read</li> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversion started upon every overflow of Timer 3</li> <li>10: ADC conversion started upon every vising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag</li> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADC0H: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| <ul> <li>0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag (Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| <ul> <li>edge of ADBUSY generates an interrupt when enabled.</li> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH:ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| <ul> <li>1: ADC Busy converting data<br/>Write</li> <li>0: No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits</li> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions started upon every rising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| <ul> <li>Write <ul> <li>No effect</li> <li>1: Starts ADC Conversion if ADSTM1-0 = 00b</li> </ul> </li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits <ul> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversions started upon every rising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> </ul> </li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag <ul> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> </ul> </li> <li>Bit0: ADLJST: ADC Left Justify Data Bit <ul> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| <ul> <li>0: No effect <ol> <li>Starts ADC Conversion if ADSTM1-0 = 00b</li> </ol> </li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits <ul> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversion started upon every rising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> </ul> </li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag <ul> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> </ul> </li> <li>Bit0: ADLJST: ADC Left Justify Data Bit <ul> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| <ol> <li>Starts ADC Conversion if ADSTM1-0 = 00b</li> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits         <ul> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversion started upon every rising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> </ul> </li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag         <ul> <li>(Must be cleared by software)</li> <li>O: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>O: Data in ADCOH: ADCOL Registers is right justified</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| <ul> <li>Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits<br/>00: ADC conversion started upon every write of 1 to ADBUSY<br/>01: ADC conversions taken on every overflow of Timer 3<br/>10: ADC conversion started upon every rising edge of CNVSTR<br/>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)<br/>0: ADC Window Comparison Data match has not occurred<br/>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit<br/>0: Data in ADCOH:ADC0L Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| <ul> <li>00: ADC conversion started upon every write of 1 to ADBUSY</li> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversion started upon every rising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag (Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH: ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| <ul> <li>01: ADC conversions taken on every overflow of Timer 3</li> <li>10: ADC conversion started upon every rising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag (Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH:ADCOL Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| <ul> <li>10: ADC conversion started upon every rising edge of CNVSTR</li> <li>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag (Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADCOH:ADC0L Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| <ul> <li>11: ADC conversions taken on every overflow of Timer 2</li> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag (Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADC0H:ADC0L Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| <ul> <li>Bit1: ADWINT: ADC Window Compare Interrupt Flag<br/>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADC0H: ADC0L Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| <ul> <li>(Must be cleared by software)</li> <li>0: ADC Window Comparison Data match has not occurred</li> <li>1: ADC Window Comparison Data match occurred</li> <li>Bit0: ADLJST: ADC Left Justify Data Bit</li> <li>0: Data in ADC0H:ADC0L Registers is right justified</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |