# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b; D/A 2x12b                                            |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f016-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

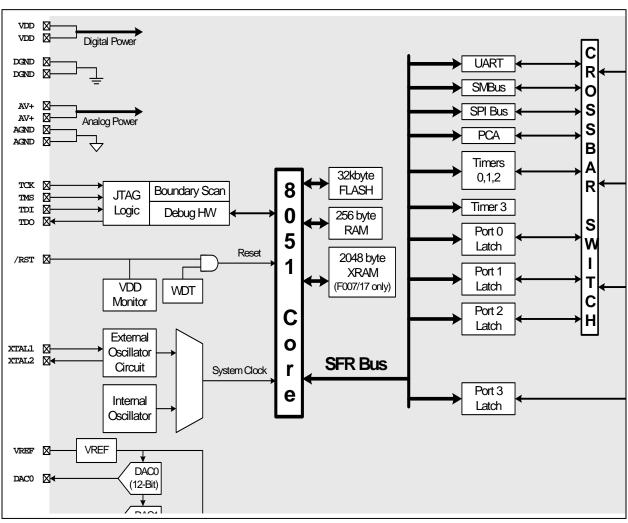

Figure 1.3. C8051F002/07/12/17 Block Diagram

## 1.3. JTAG Debug and Boundary Scan

The C8051F000 family has on-chip JTAG and debug circuitry that provide *non-intrusive, full speed, in-circuit debug using the production part installed in the end application* using the four-pin JTAG I/F. The JTAG port is fully compliant to IEEE 1149.1, providing full boundary scan for test and manufacturing purposes.

Silicon Labs' debug system supports inspection and modification of memory and registers, breakpoints, watchpoints, a stack monitor, and single stepping. No additional target RAM, program memory, timers, or communications channels are required. All the digital and analog peripherals are functional and work correctly while debugging. All the peripherals (except for the ADC) are stalled when the MCU is halted, during single stepping, or at a breakpoint in order to keep them in sync.

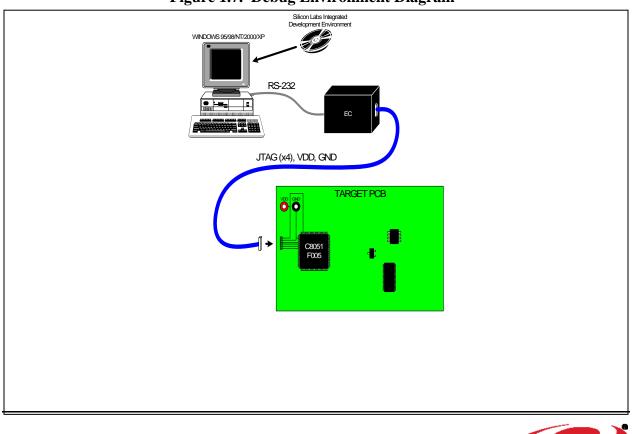

The C8051F000DK, C8051F005DK, C8051F010DK, and C8051F015DK are development kits with all the hardware and software necessary to develop application code and perform in-circuit debug with the C8051F000/1/2, F005/6/7, F010/1/2, and F015/6/7 MCUs respectively. The kit includes software with a developer's studio and debugger, an integrated 8051 assembler, and an RS-232 to JTAG protocol translator module referred to as the EC. It also has a target application board with the associated MCU installed and a large prototyping area, plus the RS-232 and JTAG cables, and wall-mount power supply. The Development Kit requires a Windows 95/98/NT/2000/XP computer with one available RS-232 serial port. As shown in Figure 1.7, the PC is connected via RS-232 to the EC. A six-inch ribbon cable connects the EC to the user's application board, picking up the four JTAG pins and VDD and GND. The EC takes its power from the application board. It requires roughly 20mA at 2.7-3.6V. For applications where there is not sufficient power available from the target board, the provided power supply can be connected directly to the EC.

This is a vastly superior configuration for developing and debugging embedded applications compared to standard MCU Emulators, which use on-board "ICE Chips" and target cables and require the MCU in the application board to be socketed. Silicon Labs' debug environment both increases ease of use and preserves the performance of the precision analog peripherals.

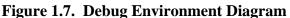

Figure 4.6. LQFP-32 Package Drawing

| R/W               | R/W             | R/W           | R/W           | R/W           | R/W    | R/W    | R/W    | Reset Value  |  |

|-------------------|-----------------|---------------|---------------|---------------|--------|--------|--------|--------------|--|

| ADCSC2            | ADCSC1          | ADCSC0        | -             | -             | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |  |

| Bit7              | Bit6            | Bit5          | Bit4          | Bit3          | Bit2   | Bit1   | Bit0   | SFR Address: |  |

|                   | 0xBC            |               |               |               |        |        |        |              |  |

| Bits7-5. AD       | CSC2-0. AL      | C SAR Conv    | version Clock | e Period Bits |        |        |        |              |  |

|                   |                 | version Clock |               |               |        |        |        |              |  |

|                   |                 | version Clock | •             |               |        |        |        |              |  |

|                   |                 | version Clock | •             |               |        |        |        |              |  |

|                   |                 | version Clock | •             |               |        |        |        |              |  |

|                   |                 | version Clock | •             |               |        |        |        |              |  |

|                   |                 | Conversion C  | •             |               | )      |        |        |              |  |

|                   |                 | d = 00b; Writ |               | ,             | ,<br>, |        |        |              |  |

|                   |                 | DC Internal A |               |               |        |        |        |              |  |

|                   | ): Gain = 1     |               | 1             |               |        |        |        |              |  |

| 001               | : Gain = 2      |               |               |               |        |        |        |              |  |

| 010               | 010: $Gain = 4$ |               |               |               |        |        |        |              |  |

| 011: Gain = 8     |                 |               |               |               |        |        |        |              |  |

| 10x: Gain = 16    |                 |               |               |               |        |        |        |              |  |

| 11x: $Gain = 0.5$ |                 |               |               |               |        |        |        |              |  |

|                   |                 |               |               |               |        |        |        |              |  |

## Figure 5.6. ADC0CF: ADC Configuration Register (C8051F00x)

33

## 5.3. ADC Programmable Window Detector

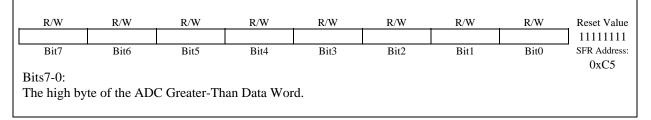

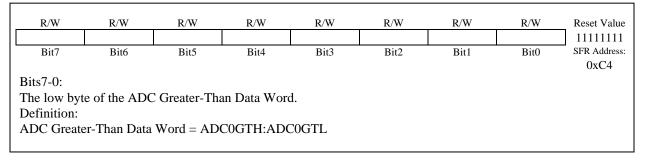

The ADC programmable window detector is very useful in many applications. It continuously compares the ADC output to user-programmed limits and notifies the system when an out-of-band condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (ADWINT in ADCOCN) can also be used in polled mode. The high and low bytes of the reference words are loaded into the ADC Greater-Than and ADC Less-Than registers (ADC0GTH, ADC0GTL, ADC0LTH, and ADC0LTL). Figure 5.14 and Figure 5.15 show example comparisons for reference. Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADC0GTx and ADC0LTx registers.

## Figure 5.10. ADC0GTH: ADC Greater-Than Data High Byte Register (C8051F00x)

## Figure 5.11. ADC0GTL: ADC Greater-Than Data Low Byte Register (C8051F00x)

### Figure 5.12. ADC0LTH: ADC Less-Than Data High Byte Register (C8051F00x)

| R/W                             | R/W                  | R/W                 | R/W                | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000000 |

|---------------------------------|----------------------|---------------------|--------------------|------|------|------|------|-------------------------|

| Bit7<br>Bits7-0:<br>The high by | Bit6<br>te of the AD | Bit5<br>C Less-Than | Bit4<br>Data Word. | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xC7    |

### Figure 5.13. ADC0LTL: ADC Less-Than Data Low Byte Register (C8051F00x)

| R/W                                                          | R/W                          | R/W | R/W | R/W | R/W | R/W | R/W | Reset Value<br>00000000 |  |

|--------------------------------------------------------------|------------------------------|-----|-----|-----|-----|-----|-----|-------------------------|--|

| Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address:<br>0xC6 |                              |     |     |     |     |     |     |                         |  |

| Definition:                                                  | re the low by<br>Гhan Data W |     |     |     |     |     |     |                         |  |

| R/W                                        | R/W           | R/W           | R/W              | R/W           | R/W    | R/W    | R/W    | Reset Value  |  |  |

|--------------------------------------------|---------------|---------------|------------------|---------------|--------|--------|--------|--------------|--|--|

| ADCSC2                                     | ADCSC1        | ADCSC0        | -                | -             | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |  |  |

| Bit7                                       | Bit6          | Bit5          | Bit4             | Bit3          | Bit2   | Bit1   | Bit0   | SFR Address: |  |  |

|                                            |               |               |                  |               |        |        |        | 0xBC         |  |  |

| Bits7-5: AD                                | CSC2-0: AD    | C SAR Conv    | version Clocl    | k Period Bits |        |        |        |              |  |  |

| 000: SAR Conversion Clock = 1 System Clock |               |               |                  |               |        |        |        |              |  |  |

| 001                                        | : SAR Conv    | version Clock | = 2 System       | Clocks        |        |        |        |              |  |  |

| 010                                        | : SAR Conv    | version Clock | = 4 System       | Clocks        |        |        |        |              |  |  |

| 011                                        | : SAR Conv    | version Clock | = 8 System       | Clocks        |        |        |        |              |  |  |

| 1xx                                        | : SAR Conv    | version Clock | = 16 System      | ns Clocks     |        |        |        |              |  |  |

| (No                                        | ote: Convers  | ion clock sho | uld be $\leq 2M$ | IHz.)         |        |        |        |              |  |  |

| Bits4-3: UN                                | USED. Rea     | d = 00b; Writ | e = don't can    | re            |        |        |        |              |  |  |

| Bits2-0: AN                                | IPGN2-0: AI   | DC Internal A | mplifier Gai     | in            |        |        |        |              |  |  |

| 000                                        | ): Gain = $1$ |               | -                |               |        |        |        |              |  |  |

| 001                                        | : Gain $= 2$  |               |                  |               |        |        |        |              |  |  |

| 010                                        | Chain = $4$   |               |                  |               |        |        |        |              |  |  |

| 011: Gain = 8                              |               |               |                  |               |        |        |        |              |  |  |

| 10x: Gain = 16                             |               |               |                  |               |        |        |        |              |  |  |

| 11x                                        | : Gain = 0.5  |               |                  |               |        |        |        |              |  |  |

|                                            |               |               |                  |               |        |        |        |              |  |  |

## Figure 6.6. ADC0CF: ADC Configuration Register (C8051F01x)

|                                                                                                 | rigure o.                                                 | o. ADCUI     | I: ADC D       | ata woru    | wisd keg | ister (Cou | SIFUIX) |              |  |  |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------|----------------|-------------|----------|------------|---------|--------------|--|--|

| R/W                                                                                             | R/W                                                       | R/W          | R/W            | R/W         | R/W      | R/W        | R/W     | Reset Value  |  |  |

|                                                                                                 |                                                           |              |                |             |          |            |         | 00000000     |  |  |

| Bit7                                                                                            | Bit6                                                      | Bit5         | Bit4           | Bit3        | Bit2     | Bit1       | Bit0    | SFR Address: |  |  |

|                                                                                                 |                                                           |              |                |             |          |            |         | 0xBF         |  |  |

|                                                                                                 |                                                           |              |                |             |          |            |         |              |  |  |

| Bits7-0: A                                                                                      | DC Data Wor                                               | d Bits       |                |             |          |            |         |              |  |  |

| E                                                                                               | or ADI IST –                                              | 1. Unner 8-h | its of the 10- | hit ADC Dat | a Word   |            |         |              |  |  |

|                                                                                                 | For ADLJST = 1: Upper 8-bits of the 10-bit ADC Data Word. |              |                |             |          |            |         |              |  |  |

| For $ADLJST = 0$ : Bits7-2 are the sign extension of Bit1. Bits 1-0 are the upper 2-bits of the |                                                           |              |                |             |          |            |         |              |  |  |

| 10                                                                                              | 10-bit ADC Data Word.                                     |              |                |             |          |            |         |              |  |  |

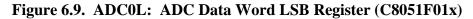

### Figure 6.8. ADC0H: ADC Data Word MSB Register (C8051F01x)

### **10.2. MEMORY ORGANIZATION**

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. There are 256 bytes of internal data memory and 64K bytes of internal program memory address space implemented within the CIP-51. The CIP-51 memory organization is shown in Figure 10.2.

#### **10.2.1. Program Memory**

The CIP-51 has a 64K-byte program memory space. The MCU implements 32896 bytes of this program memory space as in-system, reprogrammable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x807F. Note: 512 bytes (0x7E00 - 0x7FFF) of this memory are reserved for factory use and are not available for user program storage.

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to Section 11 (Flash Memory) for further details.

#### 10.2.2. Data Memory

The CIP-51 implements 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may be addressed as bytes or as 128 bit locations accessible with the direct-bit addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F will access the upper 128 bytes of data memory. Figure 10.2 illustrates the data memory organization of the CIP-51.

The C8051F005/06/07/15/16/17 also have 2048 bytes of RAM in the external data memory space of the CIP-51, accessible using the MOVX instruction. Refer to Section 12 (External RAM) for details.

#### 10.2.3. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of generalpurpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in Figure 10.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 10.2.4. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit 7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX. B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22h.3

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the user Carry flag.

#### 10.4.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

## Figure 10.9. IE: Interrupt Enable

| R/W   | R/W              | R/W           | R/W              | R/W            | R/W             | R/W           | R/W               | Reset Valu |

|-------|------------------|---------------|------------------|----------------|-----------------|---------------|-------------------|------------|

| EA    | IEGF0            | ET2           | ES               | ET1            | EX1             | ET0           | EX0               | 0000000    |

| Bit7  | Bit6             | Bit5          | Bit4             | Bit3           | Bit2            | Bit1          | Bit0              | SFR Addres |

|       |                  |               |                  |                |                 |               | (bit addressable) | 0xA8       |

|       |                  |               |                  |                |                 |               |                   |            |

| Bit7: | EA: Enable Al    | -             |                  | _              |                 |               |                   |            |

|       | This bit global  | ly enables/d  | lisables all int | errupts. It o  | verrides the in | ndividual in  | terrupt mask      |            |

|       | settings.        |               |                  |                |                 |               |                   |            |

|       | 0: Disable all i |               |                  |                | 1               |               |                   |            |

|       | 1: Enable each   | interrupt ac  | ccording to its  | s individual i | nask setting.   |               |                   |            |

| Bit6: | IEGF0: Genera    | al Purpose F  | Flag 0.          |                |                 |               |                   |            |

|       | This is a gener  |               |                  | nder softwar   | e control.      |               |                   |            |

| Bit5: | ET2: Enable T    | imer ? Inter  | rrunt            |                |                 |               |                   |            |

| DIIJ. | This bit sets th |               |                  | interrunt      |                 |               |                   |            |

|       | 0: Disable all   |               |                  | interrupt.     |                 |               |                   |            |

|       | 1: Enable inter  |               |                  | by the TF2 f   | ag (T2CON.7     | 7)            |                   |            |

|       |                  |               | 0                | - <b>J</b>     |                 | ,             |                   |            |

| Bit4: | ES: Enable Ser   |               |                  |                |                 |               |                   |            |

|       | This bit sets th |               |                  | ort (UART)     | interrupt.      |               |                   |            |

|       | 0: Disable all   |               |                  |                | (2221)          |               |                   |            |

|       | 1: Enable inter  | rrupt reques  | sts generated    | by the R1 fla  | g (SCON.0) o    | or T1 flag (S | SCON.1).          |            |

| Bit3: | ET1: Enable T    | imer 1 Inter  | rrupt.           |                |                 |               |                   |            |

|       | This bit sets th |               |                  | interrupt.     |                 |               |                   |            |

|       | 0: Disable all   |               |                  | -              |                 |               |                   |            |

|       | 1: Enable inte   | rrupt reques  | sts generated    | by the TF1 f   | lag (TCON.7)    |               |                   |            |

| Bit2: | EX1: Enable E    | External Inte | errupt 1.        |                |                 |               |                   |            |

|       | This bit sets th |               |                  | errupt 1.      |                 |               |                   |            |

|       | 0: Disable ext   | ernal interru | upt 1.           | -              |                 |               |                   |            |

|       | 1: Enable inte   | rrupt reques  | sts generated    | by the /INT1   | pin.            |               |                   |            |

| Bit1: | ET0: Enable T    | imer 0 Inter  | rrupt.           |                |                 |               |                   |            |

|       | This bit sets th |               |                  | ) interrupt.   |                 |               |                   |            |

|       | 0: Disable all   |               |                  | -              |                 |               |                   |            |

|       | 1: Enable inter  | rrupt reques  | sts generated    | by the TF0 f   | lag (TCON.5)    |               |                   |            |

| Bit0: | EX0: Enable E    | External Inte | errupt 0.        |                |                 |               |                   |            |

|       | This bit sets th |               |                  | errupt 0.      |                 |               |                   |            |

|       | 0: Disable ext   |               |                  | -              |                 |               |                   |            |

|       | 1: Enable inter  | rrupt reques  | sts generated    | by the /INTO   | pin.            |               |                   |            |

|       |                  |               |                  |                | 1               |               |                   |            |

## 15.3. General Purpose Port I/O

Each MCU has four byte-wide, bi-directional parallel ports that can be used general purpose I/O. Each port is accessed through a corresponding special function register (SFR) that is both byte addressable and bit addressable. When writing to a port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the port's input pins are returned regardless of the XBRn settings (i.e. even when the pin is assigned to another signal by the Crossbar, the Port Register can always still read its corresponding Port I/O pin). The exception to this is the execution of the *read-modify-write* instructions. The *read-modify-write* instructions when operating on a port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SET, when the destination is an individual bit in a port SFR. For these instructions, the value of the port register (not the pin) is read, modified, and written back to the SFR.

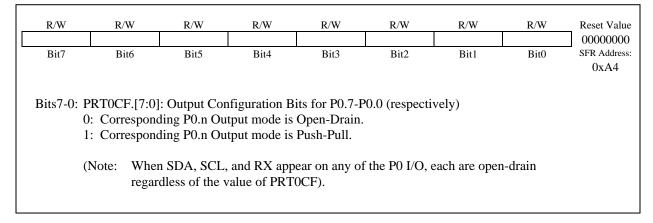

### 15.4. Configuring Ports Which are not Pinned Out

P2 and P3 are not pinned out on the F001/06/11/16. P1, P2, and P3 are not pinned out on the F002/07/12/17. These port registers (and corresponding interrupts, where applicable) are still available for software use in these reduced pin count MCUs. Whether used or not in software, it is recommended not to let these port drivers go to high impedance state. This is prevented after reset by having the weak pull-ups enabled as described in the XBR2 register. It is recommended that each output driver for ports not pinned out should be configured as push-pull using the corresponding PRTnCF register. This will inhibit a high impedance state even if the weak pull-up is disabled.

| R/W               | R/W                                                                                                                                                                     | R/W                                                  | R/W         | R/W          | R/W         | R/W             | R/W               | Reset Value |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------|--------------|-------------|-----------------|-------------------|-------------|

| P0.7              | P0.6                                                                                                                                                                    | P0.5                                                 | P0.4        | P0.3         | P0.2        | P0.1            | P0.0              | 11111111    |

| Bit7              | Bit6                                                                                                                                                                    | Bit5                                                 | Bit4        | Bit3         | Bit2        | Bit1            | Bit0              | SFR Address |

|                   |                                                                                                                                                                         |                                                      |             |              |             |                 | (bit addressable) | 0x80        |

| 0<br>1<br>(1<br>0 | <ul> <li><sup>90.</sup>[7:0]</li> <li>Write – Outpute</li> <li>Logic Low</li> <li>Logic High</li> <li>Read – Regar</li> <li>P0.n pin is</li> <li>P0.n pin is</li> </ul> | Output.<br>Output (hig<br>dless of XBI<br>logic low. | h-impedance | if correspon | ding PRT0CI | F.n bit $= 0$ ) |                   |             |

### Figure 15.6. P0: Port0 Register

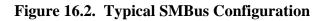

Figure 16.2 shows a typical SMBus configuration. The SMBus interface will work at any voltage between 3.0V and 5.0V and different devices on the bus may operate at different voltage levels. The SCL (serial clock) and SDA (serial data) lines are bi-directional. They must be connected to a positive power supply voltage through a pull-up resistor or similar circuit. When the bus is free, both lines are pulled high. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus will not exceed 300ns and 1000ns, respectively.

### **16.1.** Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The *I*<sup>2</sup>*C*-bus and how to use it (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification -- Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification -- Version 1.1, SBS Implementers Forum.

| Figure 16.4. SMB0CN: SMB | us Control Register |

|--------------------------|---------------------|

|--------------------------|---------------------|

| R             | R/W                            | R/W           | R/W           | R/W            | R/W             | R/W             | R/W               | Reset Value |

|---------------|--------------------------------|---------------|---------------|----------------|-----------------|-----------------|-------------------|-------------|

| BUSY          | ENSMB                          | STA           | STO           | SI             | AA              | FTE             | TOE               | 0000000     |

| Bit7          | Bit6                           | Bit5          | Bit4          | Bit3           | Bit2            | Bit1            | Bit0              | SFR Address |

|               |                                |               |               |                |                 |                 | (bit addressable) | 0xC0        |

| Bit7:         | BUSY: Busy S                   | tatus Flao    |               |                |                 |                 |                   |             |

| Dit/.         | 0: SMBus is fro                |               |               |                |                 |                 |                   |             |

|               | 1: SMBus is bu                 | isy           |               |                |                 |                 |                   |             |

| Bit6:         | ENSMB: SMB                     | us Enable.    |               |                |                 |                 |                   |             |

|               | This bit enable                | s/disables th | ne SMBus ser  | ial interface. |                 |                 |                   |             |

|               | 0: SMBus disa                  | bled.         |               |                |                 |                 |                   |             |

|               | 1: SMBus enab                  | oled.         |               |                |                 |                 |                   |             |

| Bit5:         | STA: SMBus S                   | Start Flag.   |               |                |                 |                 |                   |             |

|               | 0: No START                    | condition is  | transmitted.  |                |                 |                 |                   |             |

|               | 1: When operation              | ting as a ma  | ster, a STAR  | T condition    | is transmitted  | l if the bus is | free. (If the     |             |

|               | bus is not free,               | the START     | is transmitte | d after a ST   | OP is receive   | d.) If STA is   | s set after one   |             |

|               | or more bytes h                | nave been tr  | ansmitted or  | received and   | before a STO    | OP is receive   | ed, a repeated    |             |

|               | START condit                   | ion is transr | nitted. STO   | should be ex   | plicitly cleare | ed before set   | ting STA to       |             |

|               | logic 1.                       |               |               |                |                 |                 |                   |             |

| Bit4:         | STO: SMBus S                   |               |               |                |                 |                 |                   |             |

|               | 0: No STOP co                  |               |               |                |                 |                 |                   |             |

|               | 1: Setting STO                 |               |               |                |                 |                 |                   |             |

|               | condition is rec               |               |               |                |                 |                 |                   |             |

|               | STOP conditio                  |               |               |                |                 |                 | le, setting the   |             |

|               | STO flag cause                 |               |               | a STOP con     | dition was re   | eceived.        |                   |             |

| Bit3:         | SI: SMBus Ser                  | 1             | 0             |                |                 |                 |                   |             |

|               | This bit is set b              | •             |               | -              |                 |                 |                   |             |

|               | 0xF8 does not                  |               |               |                |                 |                 |                   |             |

|               | the CPU to vec                 |               |               |                |                 | oit is not auto | matically         |             |

|               | cleared by hard                |               |               |                | e.              |                 |                   |             |

| Bit2:         | AA: SMBus A                    |               | 0 0           |                |                 |                 |                   |             |

|               | This bit defines               | s the type of | facknowledg   | e returned du  | iring the acki  | nowledge cy     | cle on the        |             |

|               | SCL line.                      | 1 1 1 4       |               |                |                 |                 |                   |             |

|               | 0: A "not ackne                |               |               |                |                 |                 |                   |             |

| D'.1          | 1: An "acknow                  | -             |               | A) is returne  | d during the a  | acknowledge     | e cycle.          |             |

| Bit1:         | FTE: SMBus F                   |               |               |                |                 |                 |                   |             |

|               | 0: No timeout                  |               |               | 1 1            | C 11 /1 C       |                 |                   |             |

| <b>D</b> '40. | 1: Timeout wh                  | -             |               | as limit spec  | ified by the S  | MB0CR val       | ue.               |             |

| Bit0:         | TOE: SMBus T                   |               |               |                |                 |                 |                   |             |

|               | 0: No timeout<br>1: Timeout wh |               |               | . 1::          | ° 11 m          | 2 . 6 1 1 .     | 1                 |             |

|               |                                |               |               |                |                 |                 |                   |             |

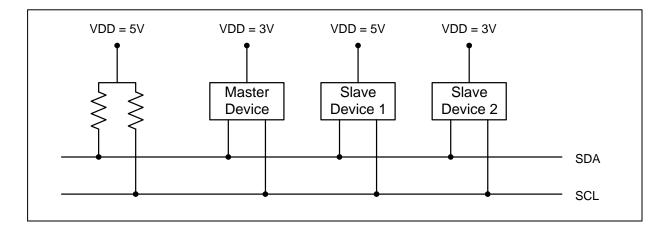

## **18. UART**

The UART is a serial port capable of asynchronous transmission. The UART can function in full duplex mode. In all modes, receive data is buffered in a holding register. This allows the UART to start reception of a second incoming data byte before software has finished reading the previous data byte.

The UART has an associated Serial Control Register (SCON) and a Serial Data Buffer (SBUF) in the SFRs. The single SBUF location provides access to both transmit and receive registers. Reads access the Receive register and writes access the Transmit register automatically.

The UART is capable of generating interrupts if enabled. The UART has two sources of interrupts: a Transmit Interrupt flag, TI (SCON.1) set when transmission of a data byte is complete, and a Receive Interrupt flag, RI (SCON.0) set when reception of a data byte is complete. The UART interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software. This allows software to determine the cause of the UART interrupt (transmit complete or receive complete).

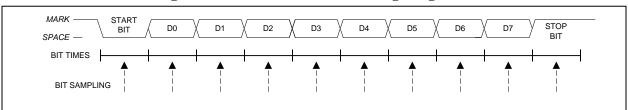

Mode 1 provides standard asynchronous, full duplex communication using a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit (see the timing diagram in Figure 18.4). Data are transmitted from the TX pin and received at the RX pin (see the interconnection diagram in Figure 18.5). On receive, the eight data bits are stored in SBUF and the stop bit goes into RB8 (SCON.2).

Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit (SCON.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF receive register if the following conditions are met: RI must be logic 0, and if SM2 is logic 1, the stop bit must be logic 1.

If these conditions are met, the eight bits of data are stored in SBUF, the stop bit is stored in RB8, and the RI flag is set. If these conditions are not met, SBUF and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI is set.

Figure 18.4. UART Mode 1 Timing Diagram

The baud rate generated in Mode 1 is a function of timer overflow. The UART can use Timer 1 operating in 8-bit *Counter/Timer with Auto-Reload Mode*, or Timer 2 operating in *Baud Rate Generator Mode* to generate the baud rate (note that the TX and RX clock sources are selected separately). On each timer overflow event (a rollover from all ones (0xFF for Timer 1, 0xFFFF for Timer 2) to zero), a clock is sent to the baud rate logic.

When Timer 1 is selected as a baud rate source, the SMOD bit (PCON.7) selects whether or not to divide the Timer 1 overflow rate by two. On reset, the SMOD bit is logic 0, thus selecting the lower speed baud rate by default. The SMOD bit affects the baud rate generated by Timer 1 as follows:

Mode 1 Baud Rate =  $(1/32) * T1_OVERFLOWRATE$  (when the SMOD bit is set to logic 0). Mode 1 Baud Rate =  $(1/16) * T1_OVERFLOWRATE$  (when the SMOD bit is set to logic 1).

When Timer 2 is selected as a baud rate source, the baud rate generated by Timer 2 is as follows:

Mode 1 Baud Rate =  $(1 / 16) * T2_OVERFLOWRATE$ .

The Timer 1 overflow rate is determined by the Timer 1 clock source (T1CLK) and reload value (TH1). The frequency of T1CLK can be selected as SYSCLK, SYSCLK/12, or an external clock source. The Timer 1 overflow rate can be calculated as follows:

$$T1_OVERFLOWRATE = T1CLK / (256 - TH1).$$

For example, assume TMOD = 0x20. If T1M (CKCON.4) is logic 1, then the above equation becomes:

$T1_OVERFLOWRATE = (SYSCLK) / (256 - TH1).$

If T1M (CKCON.4) is logic 0, then the above equation becomes:

$T1_OVERFLOWRATE = (SYSCLK/12) / (256 - TH1).$

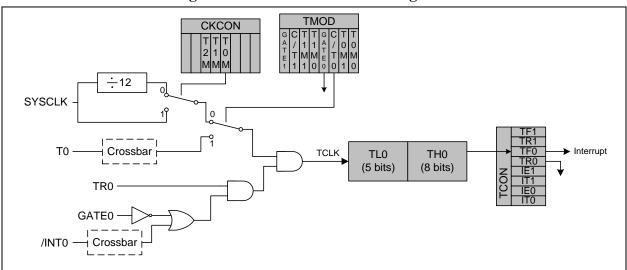

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is 0 or the input signal /INT0 is logic-level one. Setting GATE0 to logic 1 allows the timer to be controlled by the external input signal /INT0, facilitating pulse width measurements.

| TR0   | GATE0     | /INT0 | <b>Counter/Timer</b> |

|-------|-----------|-------|----------------------|

| 0     | X         | Х     | Disabled             |

| 1     | 0         | Х     | Enabled              |

| 1     | 1         | 0     | Disabled             |

| 1     | 1         | 1     | Enabled              |

| X = D | on't Care |       |                      |

Setting TR0 does not reset the timer register. The timer register should be initialized to the desired value before enabling the timer.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0.

Figure 19.1. T0 Mode 0 Block Diagram

#### 19.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

### 20.1. Capture/Compare Modules

Each module can be configured to operate independently in one of four operation modes: Edge-triggered Capture, Software Timer, High Speed Output, or Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

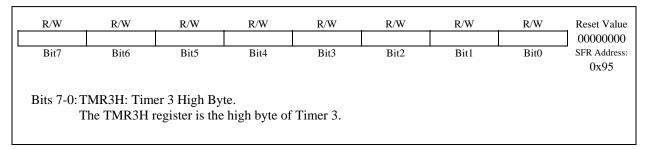

Table 20.1 summarizes the bit settings in the PCA0CPMn registers used to place the PCA capture/compare modules into different operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note: PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit (IE.7) and the EPCA0 bit (EIE1.3) to logic 1. See Figure 20.2 for details on the PCA interrupt configuration.

|      |      |      |     | 0   | 6   |      |                                            |

|------|------|------|-----|-----|-----|------|--------------------------------------------|

| ECOM | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                             |

| Х    | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge on CEXn |

| Х    | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on      |

0

0

0

1

Х

Х

Х

Х

0

1

1

Х

0

0

1

0

CEXn

Software Timer

High Speed Output

Pulse Width Modulator

Capture triggered by transition on CEXn

| Table 20.1. | PCA0CPM Register     | • Settings for PCA | Canture/Com | nare Modules |

|-------------|----------------------|--------------------|-------------|--------------|

|             | I CHUCI III REGISTEI | beenings for I Ch  | Capture Com | part mounts  |

X = Don't Care

1

0

0

0

1

0

0

0

Х

1

1

1

155

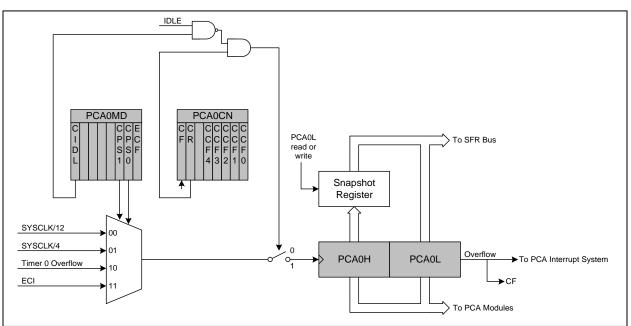

### 20.2. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H at the same time. By reading the PCA0L Register first, this allows the PCA0H value to be held (at the time PCA0L was read) until the user reads the PCA0H Register. Reading PCA0H or PCA0L does not disturb the counter operation. The CPS1 and CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 20.2.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. (Note: PCA0 interrupts must be globally enabled before CF interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit (IE.7) and the EPCA0 bit in EIE1 to logic 1.) Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the microcontroller core is in Idle mode.

| CPS1 C | PS0 | Timebase                                                              |

|--------|-----|-----------------------------------------------------------------------|

| 0      | 0   | System clock divided by 12                                            |

| 0      | 1   | System clock divided by 4                                             |

| 1      | 0   | Timer 0 overflow                                                      |

| 1      | 1   | High-to-low transitions on ECI (max rate = system clock divided by 4) |

Table 20.2.

PCA Timebase Input Options

### Figure 20.7. PCA Counter/Timer Block Diagram

## 21. JTAG (IEEE 1149.1)

Each MCU has an on-chip JTAG interface and logic to support boundary scan for production and in-system testing, Flash read and write operations, and non-intrusive in-circuit debug. The JTAG interface is fully compliant with the IEEE 1149.1 specification. Refer to this specification for detailed descriptions of the Test Interface and Boundary-Scan Architecture. Access of the JTAG Instruction Register (IR) and Data Registers (DR) are as described in the Test Access Port and Operation of the IEEE 1149.1 specification.

The JTAG interface is via four dedicated pins on the MCU, which are TCK, TMS, TDI, and TDO. These pins are all 5V tolerant.

Through the 16-bit JTAG Instruction Register (IR), any of the eight instructions shown in Figure 21.1 can be commanded. There are three Data Registers (DR's) associated with JTAG Boundary-Scan, and four associated with Flash read/write operations on the MCU.

|          |               |            |         |         |         |        |         |          |          |          |         | 0x0004  |

|----------|---------------|------------|---------|---------|---------|--------|---------|----------|----------|----------|---------|---------|

| Bit15    |               |            |         |         |         |        |         |          |          |          | Bit0    | •       |

|          |               |            |         |         |         |        |         |          |          |          |         |         |

|          |               |            |         |         |         |        |         |          |          |          |         |         |

|          |               |            |         |         |         |        |         |          |          |          |         |         |

| IR value | Instruction   | Descriptio | on      |         |         |        |         |          |          |          |         |         |

| 0x0000   | EXTEST        | Selects th | e Boun  | dary D  | Data Re | gister | for co  | ntrol a  | nd obs   | ervabi   | lity of | all     |

|          |               | device pir | is      | -       |         | -      |         |          |          |          | -       |         |

| 0x0002   | SAMPLE/       | Selects th | e Boun  | dary D  | Data Re | gister | for ob  | servab   | ility aı | nd pres  | setting | the     |

|          | PRELOAD       | scan-path  | latches | 5       |         | -      |         |          | •        | -        | -       |         |

| 0x0004   | IDCODE        | Selects de | vice II | ) Regi  | ster    |        |         |          |          |          |         |         |

| 0xFFFF   | BYPASS        | Selects By | pass I  | Data Re | egister |        |         |          |          |          |         |         |

| 0x0082   | Flash Control | Selects FI | LASHC   | CON R   | egister | to con | ntrol h | ow the   | interf   | ace log  | gic res | onds to |

|          |               | reads and  | writes  | to the  | FLAS    | HDAT   | Regis   | ter      |          |          |         |         |

| 0x0083   | Flash Data    | Selects FI | LASHI   | DAT R   | egister | for re | ads an  | d write  | es to th | e Flas   | h mem   | ory     |

| 0x0084   | Flash Address | Selects FI | LASHA   | ADR R   | egister | which  | n holds | s the ad | ldress   | of all l | Flash r | ead,    |

|          |               | write, and | erase   | operati | ons     |        |         |          |          |          |         |         |

| 0x0085   | Flash Scale   | Selects FI | LASHS   | CL Re   | egister | which  | contro  | ols the  | presca   | ler use  | ed to g | enerate |

|          |               | timing sig | nals fo | r Flash | n opera | tions  |         |          | -        |          |         |         |

|          | •             |            |         |         | •       |        |         |          |          |          |         |         |

| Figure 21.1. IR: JTAG Instruction Register |

|--------------------------------------------|

|--------------------------------------------|

## 21.3. Debug Support

Each MCU has on-chip JTAG and debug circuitry that provide *non-intrusive, full speed, in-circuit debug using the production part installed in the end application* using the four pin JTAG I/F. Silicon Labs' debug system supports inspection and modification of memory and registers, setting breakpoints, watchpoints, single stepping, and run and halt commands. No additional target RAM, program memory, or communications channels are required. All the digital and analog peripherals are functional and work correctly (remain in sync) while debugging. The WDT is disabled when the MCU is halted during single stepping or at a breakpoint.

The C8051F000DK, C8051F005DK, C8051F010DK, and C8051F015DK are development kits with all the hardware and software necessary to develop application code and perform in-circuit debugging with each MCU in the C8051F000 family. Each kit includes an Integrated Development Environment (IDE) which has a debugger and integrated 8051 assembler. It has an RS-232 to JTAG protocol translator module referred to as the EC. There is also a target application board with a C8051F000, F005, F010, or F015 installed and with a large prototyping area. The kit also includes RS-232 and JTAG cables, and wall-mount power supply.