#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Discontinued at Digi-Key                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SPI, UART, USB                        |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                         |

| Number of I/O              | 55                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 80K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-64-19                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4400f100f256abxqsa1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### XMC4400 Data Sheet

Revision History: V1.2 2015-12

| IVE AISIOII | Thistory. V1.2 2013-12                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous    |                                                                                                                                                                  |

| V1.1 2014   |                                                                                                                                                                  |

| V1.0 2013   |                                                                                                                                                                  |

| V0.6 2012   |                                                                                                                                                                  |

| Page        | Subjects                                                                                                                                                         |

| 12          | Added a section listing the packages of the different markings.                                                                                                  |

| 14          | Added BA marking variant.                                                                                                                                        |

| 37          | Added footnote explaining minimum $V_{\rm BAT}$ requirements to start the hibernate domain and/or oscillation of a crystal on RTC_XTAL.                          |

| 38          | Changed pull device definition to System Requirement (SR) to reflect that the specified currents are defined by the characteristics of the external load/driver. |

| 38          | Added information that PORST Pull-up is identical to the pull-up on standard I/O pins.                                                                           |

| 45          | Updated $C_{\text{AINSW}}$ , $C_{\text{AINTOT}}$ and $R_{\text{AIN}}$ parameters with improved values.                                                           |

| 59          | Added footnote on test configuration for LPAC measurement.                                                                                                       |

| 61          | Corrected parameter name of of USB pull device (upstream port receiving) definition according to USB standard (referenced to DM instead of DP)                   |

| 66          | Relaxed RTC_XTAL $V_{\rm PPX}$ parameter value and changed it to a system requirement.                                                                           |

| 70          | Added footnote on current consumption by enabling of $f_{CCU}$ .                                                                                                 |

| 71          | Added Flash endurance parameter for 64 Kbytes Physical Sector PS4 $N_{\rm EPS4}$ for devices with BA marking.                                                    |

| many        | Added PG-TQFP-64-19 and PG-LQFP-100-25 package information.                                                                                                      |

| 97, 100     | Added tables describing the differences between PG-LQFP-100-11 to PG-LQFP-100-25 as well as PG-LQFP-64-19 to PG-TQFP-64-19 packages.                             |

| 102         | Updated to JEDEC standard J-STD-020D for the moisture sensitivity level and added solder temperature parameter according to the same standard.                   |

| -           |                                                                                                                                                                  |

### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG. ARM<sup>®</sup>, ARM Powered<sup>®</sup>, Cortex<sup>®</sup>, Thumb<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

### **General Device Information**

# 2.2.1 Package Pin Summary

The following general scheme is used to describe each pin:

### Table 9 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad<br>Type | Notes |

|----------|-----------|-----------|-----------------|-------|

| Name     | Ν         | Ax        | <br>A2          |       |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the dedicated pins (i.e. PORST) and supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type (A1, A1+, A2, special=special pad, In=input pad, AN/DIG\_IN=analog and digital input, Power=power supply). Details about the pad properties are defined in the Electrical Parameters.

In the "Notes", special information to the respective pin/function is given, i.e. deviations from the default configuration after reset. Per default the regular Port pins are configured as direct input with no internal pull device active.

| Function | LQFP-100 | LQFP-64<br>TQFP-64 | Pad Type | Notes                                                                                                                |

|----------|----------|--------------------|----------|----------------------------------------------------------------------------------------------------------------------|

| P0.0     | 2        | 2                  | A1+      |                                                                                                                      |

| P0.1     | 1        | 1                  | A1+      |                                                                                                                      |

| P0.2     | 100      | 64                 | A2       |                                                                                                                      |

| P0.3     | 99       | 63                 | A2       |                                                                                                                      |

| P0.4     | 98       | 62                 | A2       |                                                                                                                      |

| P0.5     | 97       | 61                 | A2       |                                                                                                                      |

| P0.6     | 96       | 60                 | A2       |                                                                                                                      |

| P0.7     | 89       | 58                 | A2       | After a system reset, via<br>HWSEL this pin selects the<br>DB.TDI function.                                          |

| P0.8     | 88       | 57                 | A2       | After a system reset, via<br><u>HWSEL</u> this pin selects the<br>DB.TRST function, with a<br>weak pull-down active. |

| P0.9     | 4        | 4                  | A2       |                                                                                                                      |

| P0.10    | 3        | 3                  | A1+      |                                                                                                                      |

### Table 10 Package Pin Mapping

### **General Device Information**

| Table 10 | Package Pin Mapping (cont'd) |                    |                   |       |  |  |  |  |  |  |

|----------|------------------------------|--------------------|-------------------|-------|--|--|--|--|--|--|

| Function | LQFP-100                     | LQFP-64<br>TQFP-64 | Pad Type          | Notes |  |  |  |  |  |  |

| P3.0     | 7                            | -                  | A2                |       |  |  |  |  |  |  |

| P3.1     | 6                            | -                  | A2                |       |  |  |  |  |  |  |

| P3.2     | 5                            | -                  | A2                |       |  |  |  |  |  |  |

| P3.3     | 93                           | -                  | A1+               |       |  |  |  |  |  |  |

| P3.4     | 92                           | -                  | A1+               |       |  |  |  |  |  |  |

| P3.5     | 91                           | -                  | A2                |       |  |  |  |  |  |  |

| P3.6     | 90                           | -                  | A2                |       |  |  |  |  |  |  |

| P4.0     | 85                           | -                  | A2                |       |  |  |  |  |  |  |

| P4.1     | 84                           | -                  | A2                |       |  |  |  |  |  |  |

| P5.0     | 58                           | -                  | A1+               |       |  |  |  |  |  |  |

| P5.1     | 57                           | -                  | A1+               |       |  |  |  |  |  |  |

| P5.2     | 56                           | -                  | A1+               |       |  |  |  |  |  |  |

| P5.7     | 55                           | -                  | A1+               |       |  |  |  |  |  |  |

| P14.0    | 31                           | 20                 | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.1    | 30                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.2    | 29                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.3    | 28                           | 19                 | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.4    | 27                           | 18                 | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.5    | 26                           | 17                 | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.6    | 25                           | 16                 | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.7    | 24                           | 15                 | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.8    | 37                           | 24                 | AN/DAC/DIG_I<br>N |       |  |  |  |  |  |  |

| P14.9    | 36                           | 23                 | AN/DAC/DIG_I<br>N |       |  |  |  |  |  |  |

| P14.12   | 23                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.13   | 22                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.14   | 21                           | 14                 | AN/DIG_IN         |       |  |  |  |  |  |  |

| P14.15   | 20                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P15.2    | 19                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P15.3    | 18                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P15.8    | 39                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

| P15.9    | 38                           | -                  | AN/DIG_IN         |       |  |  |  |  |  |  |

#### Table 10 Deekege Din Menning (cont'd)

### Table 12 Port I/O Functions (cont'd)

Data Sheet

| Function  | unction Output |                      |      | Input |                  |                  |               |                |                |                |                    |       |        |                 |

|-----------|----------------|----------------------|------|-------|------------------|------------------|---------------|----------------|----------------|----------------|--------------------|-------|--------|-----------------|

|           | ALT1           | ALT2                 | ALT3 | ALT4  | HWO0             | HWI0             | Input         | Input          | Input          | Input          | Input              | Input | Input  | Input           |

| P14.9     |                |                      |      |       | DAC.<br>OUT_1    |                  |               | VADC.<br>G1CH1 |                | VADC.<br>G3CH3 | ETH0.<br>RXD1C     |       |        |                 |

| P14.12    |                |                      |      |       |                  |                  |               | VADC.<br>G1CH4 |                |                |                    |       |        |                 |

| P14.13    |                |                      |      |       |                  |                  |               | VADC.<br>G1CH5 |                |                |                    |       |        |                 |

| P14.14    |                |                      |      |       |                  |                  |               | VADC.<br>G1CH6 |                |                |                    |       | G1ORC6 |                 |

| P14.15    |                |                      |      |       |                  |                  |               | VADC.<br>G1CH7 |                |                |                    |       | G1ORC7 |                 |

| P15.2     |                |                      |      |       |                  |                  |               |                | VADC.<br>G2CH2 |                |                    |       |        |                 |

| P15.3     |                |                      |      |       |                  |                  |               |                | VADC.<br>G2CH3 |                |                    |       |        |                 |

| P15.8     |                |                      |      |       |                  |                  |               |                |                | VADC.<br>G3CH0 | ETH0.<br>CLK_RMIIC |       |        | ETH0.<br>CLKRXC |

| P15.9     |                |                      |      |       |                  |                  |               |                |                | VADC.<br>G3CH1 | ETH0.<br>CRS_DVC   |       |        | ETH0.<br>RXDVC  |

| USB_DP    |                |                      |      |       |                  |                  |               |                |                |                |                    |       |        |                 |

| USB_DM    |                |                      |      |       |                  |                  |               |                |                |                |                    |       |        |                 |

| HIB_IO_0  | HIBOUT         | WWDT.<br>SERVICE_OUT |      |       |                  |                  | WAKEUPA       |                |                |                |                    |       |        |                 |

| HIB_IO_1  | HIBOUT         | WWDT.<br>SERVICE_OUT |      |       |                  |                  | WAKEUPB       |                |                |                |                    |       |        |                 |

| тск       |                |                      |      |       |                  | DB.TCK/<br>SWCLK |               |                |                |                |                    |       |        |                 |

| TMS       |                |                      |      |       | DB.TMS/<br>SWDIO |                  |               |                |                |                |                    |       |        |                 |

| PORST     |                |                      |      |       |                  |                  |               |                |                |                |                    |       |        |                 |

| XTAL1     |                |                      |      |       |                  |                  | U0C0.<br>DX0F | U0C1.<br>DX0F  | U1C0.<br>DX0F  | U1C1.<br>DX0F  |                    |       |        |                 |

| XTAL2     |                |                      |      |       |                  |                  |               |                |                |                |                    |       |        |                 |

| RTC_XTAL1 |                |                      |      |       |                  |                  |               |                | ERU0.<br>1B1   |                |                    |       |        |                 |

| RTC_XTAL2 |                |                      |      |       |                  |                  |               |                |                |                |                    |       |        |                 |

XMC4400 XMC4000 Family

The XMC4400 has a common ground concept, all  $V_{\rm SS}$ ,  $V_{\rm SSA}$  and  $V_{\rm SSO}$  pins share the same ground potential. In packages with an exposed die pad it must be connected to the common ground as well.

$V_{\rm AGND}$  is the low potential to the analog reference  $V_{\rm AREF}$ . Depending on the application it can share the common ground or have a different potential. In devices with shared  $V_{\rm DDA}/V_{\rm AREF}$  and  $V_{\rm SSA}/V_{\rm AGND}$  pins the reference is tied to the supply. Some analog channels can optionally serve as "Alternate Reference"; further details on this operating mode are described in the Reference Manual.

When  $V_{\text{DDP}}$  is supplied,  $V_{\text{BAT}}$  must be supplied as well. If no other supply source (e.g. battery) is connected to  $V_{\text{BAT}}$ , the  $V_{\text{BAT}}$  pin can also be connected directly to  $V_{\text{DDP}}$ .

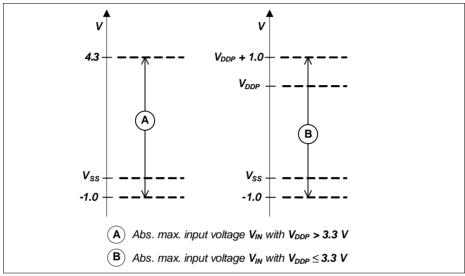

**Figure 8** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

Figure 8 Absolute Maximum Input Voltage Ranges

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 14 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload parameters, then the parameters functionality of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

| Table 14 | Overload Parameters |

|----------|---------------------|

|          |                     |

| Parameter                                                                  | Symbol              |      | Value     | s  | Unit | Note /                                                        |  |

|----------------------------------------------------------------------------|---------------------|------|-----------|----|------|---------------------------------------------------------------|--|

|                                                                            |                     | Min. | Min. Typ. |    |      | Test Condition                                                |  |

| Input current on any port pin during overload condition                    | I <sub>OV</sub> SR  | -5   | -         | 5  | mA   |                                                               |  |

| Absolute sum of all input circuit currents for one port                    | I <sub>OVG</sub> SI | २ –  | -         | 20 | mA   | $\Sigma  I_{\rm OVx} $ , for all $I_{\rm OVx} < 0 \ {\rm mA}$ |  |

| group during overload condition <sup>1)</sup>                              |                     | -    | -         | 20 | mA   | $\Sigma  I_{OVx} $ , for all $I_{OVx} > 0 \text{ mA}$         |  |

| Absolute sum of all input<br>circuit currents during<br>overload condition | I <sub>OVS</sub> SI | ₹ –  | -         | 80 | mA   | ΣI <sub>OVG</sub>                                             |  |

1) The port groups are defined in **Table 17**.

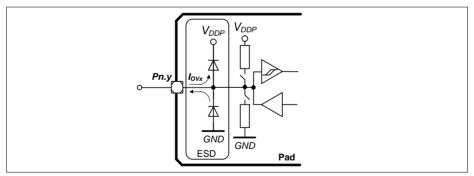

**Figure 9** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\text{DDP}}$  and ground are a simplified representation of these ESD protection structures.

### Figure 9 Input Overload Current via ESD structures

Table 15 and Table 16 list input voltages that can be reached under overload conditions.

Note that the absolute maximum input voltages as defined in the Absolute Maximum Ratings must not be exceeded during overload.

# 3.2 DC Parameters

# 3.2.1 Input/Output Pins

The digital input stage of the shared analog/digital input pins is identical to the input stage of the standard digital input/output pins.

The Pull-up on the PORST pin is identical to the Pull-up on the standard digital input/output pins.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                | Symbol                   | Va                          | alues | Unit | Note / Test Condition                                   |

|----------------------------------------------------------|--------------------------|-----------------------------|-------|------|---------------------------------------------------------|

|                                                          |                          | Min.                        | Max.  |      |                                                         |

| Pin capacitance (digital inputs/outputs)                 | C <sub>IO</sub> CC       | -                           | 10    | pF   |                                                         |

| Pull-down current                                        | $ I_{PDL} $              | 150                         | -     | μA   | $^{1)}V_{\rm IN} \ge 0.6 \times V_{\rm DDP}$            |

|                                                          | CC                       | _                           | 10    | μΑ   | $^{2)}V_{\mathrm{IN}} \leq 0.36 	imes V_{\mathrm{DDP}}$ |

| Pull-Up current                                          | $ I_{\rm PUH} $          | _                           | 10    | μA   | $^{2)}V_{\rm IN} \ge 0.6 	imes V_{\rm DDP}$             |

|                                                          | SR                       | 100                         | -     | μΑ   | $^{1)}V_{\rm IN} \leq 0.36 \times V_{\rm DDP}$          |

| Input Hysteresis for pads of all A classes <sup>3)</sup> | <i>HYSA</i><br>SR        | $0.1 \times V_{\text{DDP}}$ | -     | V    |                                                         |

| PORST spike filter<br>always blocked pulse<br>duration   | t <sub>SF1</sub> CC      | -                           | 10    | ns   |                                                         |

| PORST spike filter<br>pass-through pulse<br>duration     | t <sub>SF2</sub> CC      | 100                         | -     | ns   |                                                         |

| PORST pull-down current                                  | I <sub>PPD</sub>  <br>CC | 13                          | -     | mA   | V <sub>IN</sub> = 1.0 V                                 |

### Table 20 Standard Pad Parameters

Current required to override the pull device with the opposite logic level ("force current").

With active pull device, at load currents between force and keep current the input state is undefined.

Load current at which the pull device still maintains the valid logic level ("keep current").

With active pull device, at load currents between force and keep current the input state is undefined.

Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

38

### Table 22 Standard Pads Class\_A1+

| Parameter            | Symbol               | Va                     | lues | Unit | Note /<br>Test Condition                                                |  |

|----------------------|----------------------|------------------------|------|------|-------------------------------------------------------------------------|--|

|                      |                      | Min.                   | Max. |      |                                                                         |  |

| Output high voltage, | V <sub>OHA1+</sub>   | V <sub>DDP</sub> - 0.4 | -    | V    | <i>I</i> <sub>OH</sub> ≥ -400 μA                                        |  |

| $POD^{1)} = weak$    | CC                   | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -500 μA                                        |  |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | I <sub>OH</sub> ≥ -1.4 mA                                               |  |

| $POD^{1)} = medium$  |                      | 2.4                    | -    | V    | I <sub>OH</sub> ≥ -2 mA                                                 |  |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | $I_{\rm OH} \ge$ -1.4 mA                                                |  |

| $POD^{1)} = strong$  |                      | 2.4                    | _    | V    | $I_{\rm OH} \ge$ -2 mA                                                  |  |

| Output low voltage   | $V_{\rm OLA1+}$ CC   | _                      | 0.4  | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak                   |  |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium                |  |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = strong                |  |

| Fall time            | t <sub>FA1+</sub> CC | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |  |

|                      |                      | -                      | 50   | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium                      |  |

|                      |                      | _                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |  |

|                      |                      | _                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft; |  |

| Rise time            | t <sub>RA1+</sub> CC | -                      | 150  | ns   | $C_{\rm L}$ = 20 pF;<br>POD <sup>1)</sup> = weak                        |  |

|                      |                      | -                      | 50   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium                  |  |

|                      |                      | -                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |  |

|                      |                      | -                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft  |  |

1) POD = Pin Out Driver

| Parameter                                          | Symbol                   | Va                     | lues                   | Unit | Note /<br>Test Condition $0 \ V \le V_{IN} \le V_{BAT}$               |  |

|----------------------------------------------------|--------------------------|------------------------|------------------------|------|-----------------------------------------------------------------------|--|

|                                                    |                          | Min.                   | Max.                   |      |                                                                       |  |

| Input leakage current                              | I <sub>OZHIB</sub><br>CC | -500                   | 500                    | nA   |                                                                       |  |

| Input high voltage                                 | V <sub>IHHIB</sub><br>SR | $0.6 	imes V_{BAT}$    | V <sub>BAT</sub> + 0.3 | V    | max. 3.6 V                                                            |  |

| Input low voltage                                  | $V_{\rm ILHIB}$ SR       | -0.3                   | $0.36 	imes V_{BAT}$   | V    |                                                                       |  |

| Input Hysteresis for                               | HYSHIB<br>CC             | $0.1 	imes V_{BAT}$    | -                      | V    | $V_{BAT} \ge 3.13 \ V$                                                |  |

| HIB_IO pins <sup>1)</sup>                          |                          | $0.06 \times V_{BAT}$  | -                      | V    | $V_{\rm BAT}$ < 3.13 V                                                |  |

| Output high voltage,<br>POD <sup>1)</sup> = medium | V <sub>OHHIB</sub><br>CC | V <sub>BAT</sub> - 0.4 | -                      | V    | $I_{\rm OH}$ $\geq$ -1.4 mA                                           |  |

| Output low voltage                                 | V <sub>OLHIB</sub><br>CC | -                      | 0.4                    | V    | $I_{\rm OL} \le 2 \ {\rm mA}$                                         |  |

| Fall time                                          | t <sub>FHIB</sub> CC     | -                      | 50                     | ns   | $V_{\text{BAT}} \ge 3.13 \text{ V}$<br>$C_{\text{L}} = 50 \text{ pF}$ |  |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF                         |  |

| Rise time                                          | t <sub>RHIB</sub> CC     | -                      | 50                     | ns   | $V_{\rm BAT} \ge 3.13 \ { m V}$<br>$C_{\rm L}$ = 50 pF                |  |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF                         |  |

### Table 24 HIB\_IO Class\_A1 special Pads

1) Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

# 3.2.2 Analog to Digital Converters (ADCx)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                                    | Symbol                     |                            | Values | 5                                    | Unit | Note /                                                                                                        |  |

|------------------------------------------------------------------------------|----------------------------|----------------------------|--------|--------------------------------------|------|---------------------------------------------------------------------------------------------------------------|--|

|                                                                              |                            | Min.                       | Тур.   | Typ. Max.                            |      | Test Condition                                                                                                |  |

| Analog reference voltage <sup>5)</sup>                                       | $V_{AREF}$ SR              | V <sub>AGND</sub><br>+ 1   | -      | $V_{\rm DDA}^{}+$ 0.05 <sup>1)</sup> | V    |                                                                                                               |  |

| Analog reference ground <sup>5)</sup>                                        | $V_{ m AGND}$ SR           | V <sub>SSM</sub> -<br>0.05 | -      | V <sub>AREF</sub> -<br>1             | V    |                                                                                                               |  |

| Analog reference voltage<br>range <sup>2)5)</sup>                            | $V_{AREF}$ - $V_{AGND}$ SR | 1                          | -      | V <sub>DDA</sub> + 0.1               | V    |                                                                                                               |  |

| Analog input voltage                                                         | $V_{\rm AIN}~{\rm SR}$     | $V_{\rm AGND}$             | -      | $V_{DDA}$                            | V    |                                                                                                               |  |

| Input leakage at analog inputs <sup>3)</sup>                                 | I <sub>OZ1</sub> CC        | -100                       | -      | 200                                  | nA   | $0.03 	imes V_{ m DDA} < V_{ m AIN} < 0.97 	imes V_{ m DI}$ A                                                 |  |

|                                                                              |                            | -500                       | -      | 100                                  | nA   | $\begin{array}{l} 0 \ V \leq V_{AIN} \leq 0.03 \\ \times \ V_{DDA} \end{array}$                               |  |

|                                                                              |                            | -100                       | -      | 500                                  | nA   | $\begin{array}{l} \textbf{0.97} \times V_{\text{DDA}} \\ \leq V_{\text{AIN}} \leq V_{\text{DDA}} \end{array}$ |  |

| Input leakage current at VAREF                                               | I <sub>OZ2</sub> CC        | -1                         | -      | 1                                    | μA   | $0 V \le V_{AREF} \le V_{DDA}$                                                                                |  |

| Input leakage current at VAGND                                               | I <sub>OZ3</sub> CC        | -1                         | -      | 1                                    | μA   | $\begin{array}{l} 0 \ V \leq V_{AGND} \\ \leq V_{DDA} \end{array}$                                            |  |

| Internal ADC clock                                                           | $f_{\sf ADCI}\sf CC$       | 2                          | -      | 30                                   | MHz  | $V_{\rm DDA}$ = 3.3 V                                                                                         |  |

| Switched capacitance at the analog voltage inputs <sup>4)</sup>              | C <sub>AINSW</sub><br>CC   | -                          | 4      | 6.5                                  | pF   |                                                                                                               |  |

| Total capacitance of an analog input                                         | $C_{AINTOT}$ CC            | -                          | 12     | 20                                   | pF   |                                                                                                               |  |

| Switched capacitance at the positive reference voltage input <sup>5)6)</sup> | C <sub>AREFSW</sub><br>CC  | -                          | 15     | 30                                   | pF   |                                                                                                               |  |

| Total capacitance of the voltage reference inputs <sup>5)</sup>              | $C_{AREFTOT}$ CC           | -                          | 20     | 40                                   | pF   |                                                                                                               |  |

| Table 25 | ADC Parameters | (Operating Conditions apply) |  |

|----------|----------------|------------------------------|--|

|----------|----------------|------------------------------|--|

| Parameter                                                                 | Symbol                                                          |           | Value | s     | Unit | Note /                                                                                    |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------|-----------|-------|-------|------|-------------------------------------------------------------------------------------------|--|

|                                                                           |                                                                 | Min. Typ. |       | Max.  | _    | Test Condition                                                                            |  |

| Total Unadjusted Error                                                    | TUE CC                                                          | -4        | -     | 4     | LSB  | 12-bit resolution <sup>7)</sup> ;                                                         |  |

| Differential Non-Linearity<br>Error <sup>8)</sup>                         | EA <sub>DNL</sub><br>CC                                         | -3        | -     | 3     | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$<br>$V_{\text{AREF}} = V_{\text{DDA}},$                  |  |

| Gain Error <sup>8)</sup>                                                  | EA <sub>GAIN</sub><br>CC                                        | -4        | -     | 4     | LSB  | dedicated pins for $V_{\text{DDA}}$ and $V_{\text{AREF}}$                                 |  |

| Integral Non-Linearity <sup>8)</sup>                                      | EAINLCC                                                         | -3        | -     | 3     | LSB  |                                                                                           |  |

| Offset Error <sup>8)</sup>                                                | EA <sub>OFF</sub><br>CC                                         | -4        | -     | 4     | LSB  |                                                                                           |  |

| Total Unadjusted Error                                                    | TUE CC                                                          | -6        | -     | 6     | LSB  | 12-bit resolution <sup>7)</sup> ;                                                         |  |

| Differential Non-Linearity<br>Error <sup>8)</sup>                         | EA <sub>DNL</sub><br>CC                                         | -4.5      | -     | 4.5   | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$<br>$V_{\text{AREF}} = V_{\text{DDA}},$                  |  |

| Gain Error <sup>8)</sup>                                                  | EA <sub>GAIN</sub><br>CC                                        | -6        | -     | 6     | LSB  | shared pin for $V_{\text{DDA}}$ and $V_{\text{AREF}}$ (PG-LQFP-64)                        |  |

| Integral Non-Linearity <sup>8)</sup>                                      | EAINLCC                                                         | -4.5      | -     | 4.5   | LSB  |                                                                                           |  |

| Offset Error <sup>8)</sup>                                                | EA <sub>OFF</sub><br>CC                                         | -6        | -     | 6     | LSB  |                                                                                           |  |

| Worst case ADC $V_{\text{DDA}}$ power supply current per active converter | I <sub>DDAA</sub><br>CC                                         | _         | 1.5   | 2     | mA   | during conversion<br>$V_{\text{DDP}} = 3.6 \text{ V},$<br>$T_{\text{J}} = 150 \text{ °C}$ |  |

| Charge consumption on $V_{\text{AREF}}$ per conversion <sup>5)</sup>      | $\begin{array}{c} Q_{\mathrm{CONV}} \\ \mathrm{CC} \end{array}$ | -         | 30    | -     | рС   | $0 V \le V_{AREF} \le V_{DDA}^{9)}$                                                       |  |

| ON resistance of the analog input path                                    | R <sub>AIN</sub> CC                                             | -         | 700   | 1 200 | Ohm  |                                                                                           |  |

| ON resistance for the ADC test (pull down for AIN7)                       | R <sub>AIN7T</sub><br>CC                                        | 180       | 550   | 900   | Ohm  |                                                                                           |  |

| Resistance of the reference voltage input path                            | R <sub>AREF</sub><br>CC                                         | _         | 700   | 1 700 | Ohm  |                                                                                           |  |

### Table 25 ADC Parameters (Operating Conditions apply)

1) A running conversion may become imprecise in case the normal conditions are violated (voltage overshoot).

If the analog reference voltage is below V<sub>DDA</sub>, then the ADC converter errors increase. If the reference voltage is reduced by the factor k (k<1), TUE, DNL, INL, Gain, and Offset errors increase also by the factor 1/k.</li>

3) The leakage current definition is a continuous function, as shown in figure ADCx Analog Inputs Leakage. The numerical values defined determine the characteristic points of the given continuous linear approximation they do not define step function (see Figure 14).

46

### 3.2.5.3 Clocks

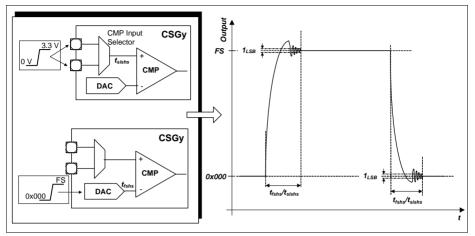

### **HRPWM DAC Conversion Clock**

The DAC conversion clock can be generated internally or it can be controlled via a HRPWM module pin.

| Table 31 External DAC conversion trigger operating conditions |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Parameter | Symbol                  |                                   | Values | Unit             | Note / |                    |

|-----------|-------------------------|-----------------------------------|--------|------------------|--------|--------------------|

|           |                         | Min.                              | Тур.   | Max.             |        | Test Con<br>dition |

| Frequency | $f_{\rm etrg}$ SR       | _                                 | -      | 30 <sup>2)</sup> | MHz    |                    |

| ON time   | t <sub>onetrg</sub> SR  | 2T <sub>ccu</sub> <sup>1)2)</sup> | -      | -                | ns     |                    |

| OFF time  | t <sub>offetrg</sub> SR | 2T <sub>ccu</sub> <sup>1)2)</sup> | -      | -                | ns     |                    |

1) 50% duty cycle is not obligatory

2) Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

### CSG External Clock

It is possible to select an external source, that can be used as a clock for the slope generation, HRPWMx.ECLKy. This clock is synchronized internally with the module clock and therefore the external clock needs to meet the criterion described on Table 32.

| Parameter                                                   | Symbol                  |                        | Values | 5                      | Unit | Note /                                                     |  |

|-------------------------------------------------------------|-------------------------|------------------------|--------|------------------------|------|------------------------------------------------------------|--|

|                                                             |                         | Min.                   | Тур.   | Max.                   |      | Test Condition                                             |  |

| Input frequency                                             | $f_{\rm OSC}{\rm SR}$   | 4                      | -      | 40                     | MHz  | Direct Input Mode<br>selected                              |  |

|                                                             |                         | 4                      | -      | 25                     | MHz  | External Crystal<br>Mode selected                          |  |

| Oscillator start-up time <sup>1)2)</sup>                    | t <sub>OSCS</sub><br>CC | _                      | -      | 10                     | ms   |                                                            |  |

| Input voltage at XTAL1                                      | V <sub>IX</sub> SR      | -0.5                   | -      | V <sub>DDP</sub> + 0.5 | V    |                                                            |  |

| Input amplitude (peak-<br>to-peak) at XTAL1 <sup>2)3)</sup> | $V_{\rm PPX}{\rm SR}$   | $0.4 	imes V_{ m DDP}$ | -      | V <sub>DDP</sub> + 1.0 | V    |                                                            |  |

| Input high voltage at XTAL1 <sup>4)</sup>                   | $V_{\rm IHBX} {\rm SR}$ | 1.0                    | -      | V <sub>DDP</sub> + 0.5 | V    |                                                            |  |

| Input low voltage at XTAL1 <sup>4)</sup>                    | $V_{\rm ILBX}{ m SR}$   | -0.5                   | -      | 0.4                    | V    |                                                            |  |

| Input leakage current at XTAL1                              | I <sub>ILX1</sub> CC    | -100                   | -      | 100                    | nA   | Oscillator power<br>down<br>0 V $\leq V_{IX} \leq V_{DDP}$ |  |

### Table 37 OSC\_XTAL Parameters

t<sub>OSCS</sub> is defined from the moment the oscillator is enabled wih SCU\_OSCHPCTRL.MODE until the oscillations reach an amplitude at XTAL1 of 0.4 \* V<sub>DDP</sub>.

2) The external oscillator circuitry must be optimized by the customer and checked for negative resistance and amplitude as recommended and specified by crystal suppliers.

3) If the shaper unit is enabled and not bypassed.

4) If the shaper unit is bypassed, dedicated DC-thresholds have to be met.

### Table 41 Flash Memory Parameters

| Parameter                                                                 | Symbol                  |           | Values | 5    | Unit   | Note /<br>Test Condition                                                              |  |

|---------------------------------------------------------------------------|-------------------------|-----------|--------|------|--------|---------------------------------------------------------------------------------------|--|

|                                                                           |                         | Min.      | Тур.   | Max. |        |                                                                                       |  |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC     | 20        | -      | -    | years  | Max. 4<br>erase/program<br>cycles per UCB                                             |  |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub><br>CC | PS4 10000 |        | -    | cycles | BA-marking<br>devices only!<br>Cycling<br>distributed over<br>life time <sup>5)</sup> |  |

1) In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

2) The following formula applies to the wait state configuration: FCON.WSPFLASH × (1 /  $f_{CPU}$ )  $\geq t_a$ .

3) Storage and inactive time included.

4) Values given are valid for an average weighted junction temperature of  $T_{\rm J}$  = 110°C.

5) Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see the Reference Manual.

# 3.3.11 Ethernet Interface (ETH) Characteristics

For proper operation of the Ethernet Interface it is required that  $f_{SYS} \ge 100 \text{ MHz}$ .

Note: These parameters are not subject to production test, but verified by design and/or characterization.

# 3.3.11.1 ETH Measurement Reference Points

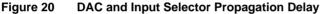

Figure 39 ETH Measurement Reference Points

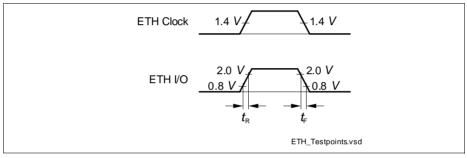

# 3.3.11.2 ETH Management Signal Parameters (ETH\_MDC, ETH\_MDIO)

| Parameter                    |                       | Symbol |      | Values | 5    | Unit | Note /                 |

|------------------------------|-----------------------|--------|------|--------|------|------|------------------------|

|                              |                       |        | Min. | Тур.   | Max. |      | Test Conditi<br>on     |

| ETH_MDC period               | <i>t</i> <sub>1</sub> | CC     | 400  | -      | -    | ns   | C <sub>L</sub> = 25 pF |

| ETH_MDC high time            | <i>t</i> <sub>2</sub> | CC     | 160  | -      | -    | ns   |                        |

| ETH_MDC low time             | t <sub>3</sub>        | CC     | 160  | -      | -    | ns   |                        |

| ETH_MDIO setup time (output) | <i>t</i> <sub>4</sub> | CC     | 10   | -      | -    | ns   |                        |

| ETH_MDIO hold time (output)  | $t_5$                 | CC     | 10   | -      | -    | ns   |                        |

| ETH_MDIO data valid (input)  | $t_6$                 | SR     | 0    | -      | 300  | ns   |                        |

### Table 58 ETH Management Signal Timing Parameters

Figure 40 ETH Management Signal Timing

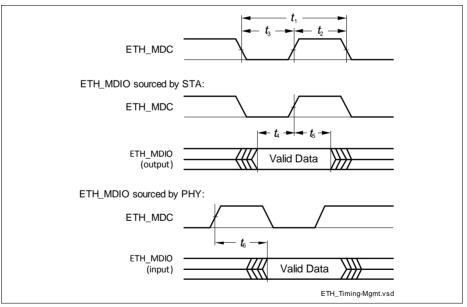

# 3.3.11.3 ETH RMII Parameters

In the following, the parameters of the RMII (Reduced Media Independent Interface) are described.

| Table 59         ETH RMII Signal Timing Parameters |

|----------------------------------------------------|

|----------------------------------------------------|

| Parameter                                      |                        | Symbol |      | Value | S    | Unit | Note /                            |

|------------------------------------------------|------------------------|--------|------|-------|------|------|-----------------------------------|

|                                                |                        |        | Min. | Тур.  | Max. |      | Test Condit<br>ion                |

| ETH_RMII_REF_CL clock period                   | <i>t</i> <sub>13</sub> | SR     | 20   | -     | _    | ns   | C <sub>L</sub> = 25 pF;<br>50 ppm |

| ETH_RMII_REF_CL clock high time                | t <sub>14</sub>        | SR     | 7    | -     | 13   | ns   | C <sub>L</sub> = 25 pF            |

| ETH_RMII_REF_CL clock low time                 | t <sub>15</sub>        | SR     | 7    | -     | 13   | ns   | -                                 |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS setup time  | t <sub>16</sub>        | SR     | 4    | _     | _    | ns   |                                   |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS hold time   | t <sub>17</sub>        | SR     | 2    | -     | -    | ns   |                                   |

| ETH_RMII_TXD[1:0],<br>ETH_RMII_TXEN data valid | t <sub>18</sub>        | СС     | 4    | -     | 15   | ns   |                                   |

Figure 41 ETH RMII Signal Timing

# XMC4400 XMC4000 Family

### Package and Reliability

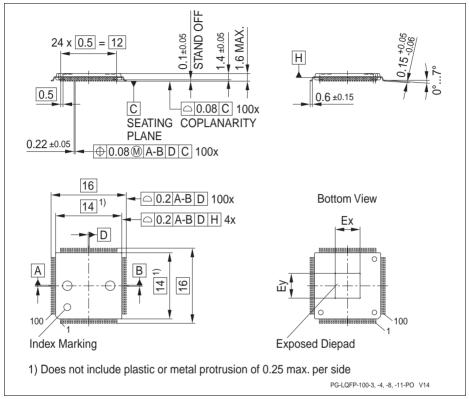

Figure 42 PG-LQFP-100-11 (Plastic Green Low Profile Quad Flat Package)

# XMC4400 XMC4000 Family

### Package and Reliability

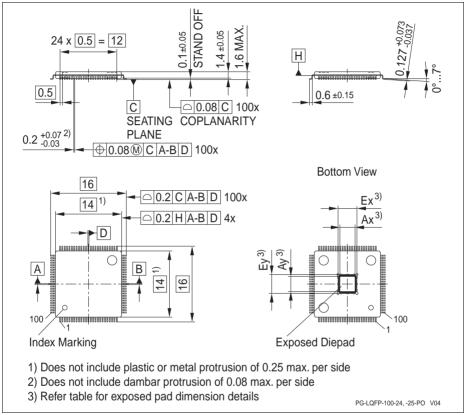

Figure 43 PG-LQFP-100-25 (Plastic Green Low Profile Quad Flat Package)