Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SPI, UART, USB                        |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                         |

| Number of I/O              | 55                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 80K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-100-11                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4400f100k256baxuma2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XMC4400

Microcontroller Series for Industrial Applications

XMC4000 Family

ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit processor core

Data Sheet V1.2 2015-12

## Microcontrollers

CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM, Limited.

Synopsys<sup>™</sup> is a trademark of Synopsys, Inc.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### About this Document

## About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC4400 series devices.

The document describes the characteristics of a superset of the XMC4400 series devices. For simplicity, the various device types are referred to by the collective term XMC4400 throughout this manual.

#### XMC4000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

## Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc4000 to get access to the latest versions of those documents.

#### **Summary of Features**

## 1 Summary of Features

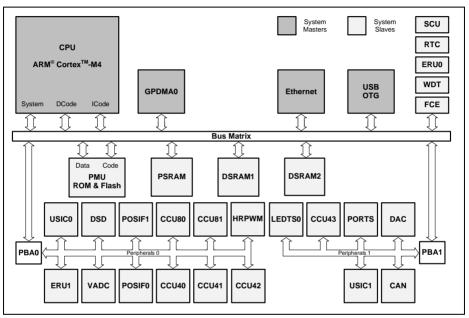

The XMC4400 devices are members of the XMC4000 Family of microcontrollers based on the ARM Cortex-M4 processor core. The XMC4000 is a family of high performance and energy efficient microcontrollers optimized for Industrial Connectivity, Industrial Control, Power Conversion, Sense & Control.

Figure 1 System Block Diagram

#### **CPU Subsystem**

- CPU Core

- High Performance 32-bit ARM Cortex-M4 CPU

- 16-bit and 32-bit Thumb2 instruction set

- DSP/MAC instructions

- System timer (SysTick) for Operating System support

- Floating Point Unit

- Memory Protection Unit

- Nested Vectored Interrupt Controller

- One General Purpose DMA with up-to 8 channels

- Event Request Unit (ERU) for programmable processing of external and internal service requests

- Flexible CRC Engine (FCE) for multiple bit error detection

Data Sheet

## XMC4400 XMC4000 Family

#### **General Device Information**

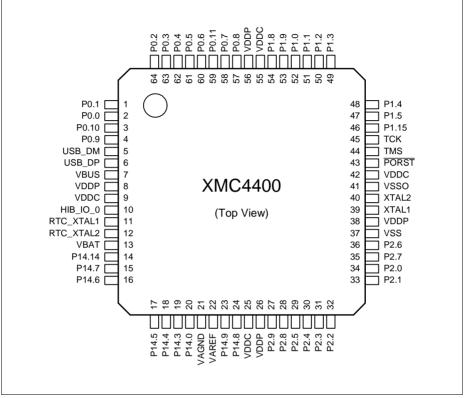

Figure 5 XMC4400 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

#### **General Device Information**

### 2.2.1 Package Pin Summary

The following general scheme is used to describe each pin:

#### Table 9 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad<br>Type | Notes |

|----------|-----------|-----------|-----------------|-------|

| Name     | Ν         | Ax        | <br>A2          |       |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the dedicated pins (i.e. PORST) and supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type (A1, A1+, A2, special=special pad, In=input pad, AN/DIG\_IN=analog and digital input, Power=power supply). Details about the pad properties are defined in the Electrical Parameters.

In the "Notes", special information to the respective pin/function is given, i.e. deviations from the default configuration after reset. Per default the regular Port pins are configured as direct input with no internal pull device active.

| Function | LQFP-100 | LQFP-64<br>TQFP-64 | Pad Type | Notes                                                                                                                |

|----------|----------|--------------------|----------|----------------------------------------------------------------------------------------------------------------------|

| P0.0     | 2        | 2                  | A1+      |                                                                                                                      |

| P0.1     | 1        | 1                  | A1+      |                                                                                                                      |

| P0.2     | 100      | 64                 | A2       |                                                                                                                      |

| P0.3     | 99       | 63                 | A2       |                                                                                                                      |

| P0.4     | 98       | 62                 | A2       |                                                                                                                      |

| P0.5     | 97       | 61                 | A2       |                                                                                                                      |

| P0.6     | 96       | 60                 | A2       |                                                                                                                      |

| P0.7     | 89       | 58                 | A2       | After a system reset, via<br>HWSEL this pin selects the<br>DB.TDI function.                                          |

| P0.8     | 88       | 57                 | A2       | After a system reset, via<br><u>HWSEL</u> this pin selects the<br>DB.TRST function, with a<br>weak pull-down active. |

| P0.9     | 4        | 4                  | A2       |                                                                                                                      |

| P0.10    | 3        | 3                  | A1+      |                                                                                                                      |

#### Table 10 Package Pin Mapping

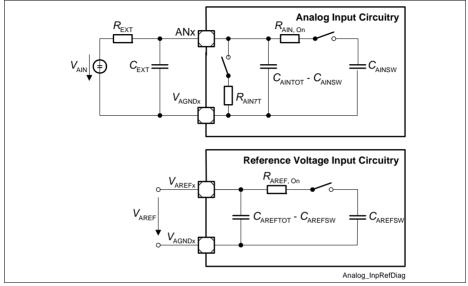

The power-up calibration of the ADC requires a maximum number of 4 352  $f_{ADCI}$  cycles.

Figure 13 ADCx Input Circuits

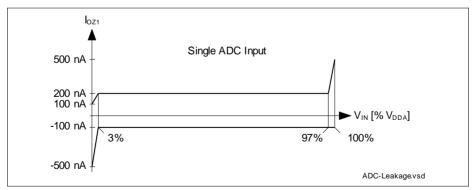

Figure 14 ADCx Analog Input Leakage Current

#### **Conversion Time**

| Table 26 | <b>Conversion Time</b> (Operating Conditions apply) |

|----------|-----------------------------------------------------|

|----------|-----------------------------------------------------|

| Parameter          | Syr            | nbol | Values                                                      | Unit | Note                                                                                             |

|--------------------|----------------|------|-------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------|

| Conversion<br>time | t <sub>C</sub> |      | $2 \times T_{ADC}$ +<br>(2 + N + STC + PC +DM) × $T_{ADCI}$ |      | N = 8, 10, 12 for<br>N-bit conversion<br>$T_{ADC} = 1 / f_{PERIPH}$<br>$T_{ADCI} = 1 / f_{ADCI}$ |

- STC defines additional clock cycles to extend the sample time

- · PC adds two cycles if post-calibration is enabled

- DM adds one cycle for an extended conversion time of the MSB

#### **Conversion Time Examples**

System assumptions:

$f_{ADC}$  = 120 MHz i.e.  $t_{ADC}$  = 8.33 ns, DIVA = 3,  $f_{ADCI}$  = 30 MHz i.e.  $t_{ADCI}$  = 33.3 ns According to the given formulas the following minimum conversion times can be achieved (STC = 0, DM = 0):

12-bit post-calibrated conversion (PC = 2):

$t_{CN12C} = (2 + 12 + 2) \times t_{ADCI} + 2 \times t_{ADC} = 16 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 550 \text{ ns}$

12-bit uncalibrated conversion:

$t_{\text{CN12}} = (2 + 12) \times t_{\text{ADCI}} + 2 \times t_{\text{ADC}} = 14 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 483 \text{ ns}$ 10-bit uncalibrated conversion:

$t_{CN10} = (2 + 10) \times t_{ADCI} + 2 \times t_{ADC} = 12 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 417 \text{ ns}$ 8-bit uncalibrated:

$t_{CN8} = (2 + 8) \times t_{ADCI} + 2 \times t_{ADC} = 10 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 350 \text{ ns}$

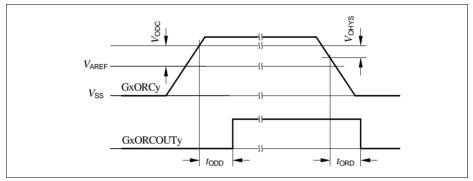

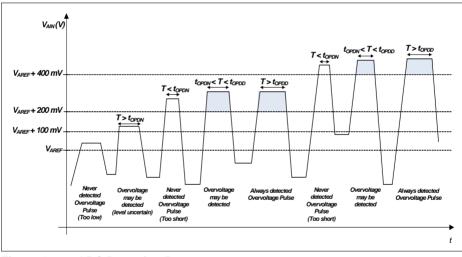

## 3.2.4 Out-of-Range Comparator (ORC)

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{AIN}$ ) above the analog reference<sup>1</sup> ( $V_{AREF}$ ) on selected input pins (GxORCy) and generates a service request trigger (GxORCOUTy).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The parameters in Table 28 apply for the maximum reference voltage  $V_{\text{AREF}} = V_{\text{DDA}} + 50 \text{ mV}.$

| Parameter                 | Symb              | ol |      | Values | 5                | Unit | Note / Test Condition                                 |

|---------------------------|-------------------|----|------|--------|------------------|------|-------------------------------------------------------|

|                           |                   |    | Min. | Тур.   | Max.             | 1    |                                                       |

| DC Switching Level        | $V_{\rm ODC}$     | CC | 100  | 125    | 200              | mV   | $V_{\text{AIN}} \ge V_{\text{AREF}} + V_{\text{ODC}}$ |

| Hysteresis                | $V_{\rm OHYS}$    | CC | 50   | -      | V <sub>ODC</sub> | mV   |                                                       |

| Detection Delay of a      | t <sub>ODD</sub>  | СС | 55   | -      | 450              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

| persistent<br>Overvoltage |                   |    | 45   | -      | 105              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |

| Always detected           | t <sub>OPDD</sub> | СС | 440  | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

| Overvoltage Pulse         |                   |    | 90   | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |

| Never detected            | t <sub>OPDN</sub> | СС | -    | -      | 49               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

| Overvoltage Pulse         |                   |    | -    | -      | 30               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |

| Release Delay             | t <sub>ORD</sub>  | СС | 65   | -      | 105              | ns   | $V_{AIN} \leq V_{AREF}$                               |

| Enable Delay              | t <sub>OED</sub>  | CC | -    | 100    | 200              | ns   |                                                       |

#### Table 28 ORC Parameters (Operating Conditions apply)

<sup>1)</sup> Always the standard VADC reference, alternate references do not apply to the ORC.

Figure 16 GxORCOUTy Trigger Generation

Figure 17 ORC Detection Ranges

### 3.2.7 Die Temperature Sensor

The Die Temperature Sensor (DTS) measures the junction temperature  $T_{1}$ .

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                         | Symbol Values       |    | S    | Unit | Note / |    |                                                                                    |

|---------------------------------------------------|---------------------|----|------|------|--------|----|------------------------------------------------------------------------------------|

|                                                   |                     |    | Min. | Тур. | Max.   |    | Test Condition                                                                     |

| Temperature sensor range                          | $T_{\rm SR}$        | SR | -40  | -    | 150    | °C |                                                                                    |

| Linearity Error<br>(to the below defined formula) | $\Delta T_{\rm LE}$ | СС | -    | ±1   | -      | °C | per $\Delta T_{\rm J} \leq 30  {\rm °C}$                                           |

| Offset Error                                      | $\Delta T_{\rm OE}$ | СС | -    | ±6   | -      | °C | $\Delta T_{\rm OE} = T_{\rm J} - T_{\rm DTS}$ $V_{\rm DDP} \le 3.3 \ {\rm V}^{1)}$ |

| Measurement time                                  | t <sub>M</sub>      | СС | -    | -    | 100    | μS |                                                                                    |

| Start-up time after reset inactive                | t <sub>TSST</sub>   | SR | _    | -    | 10     | μS |                                                                                    |

Table 34

Die Temperature Sensor Parameters

1) At  $V_{\text{DDP max}}$  = 3.63 V the typical offset error increases by an additional  $\Delta T_{\text{OE}}$  = ±1 °C.

The following formula calculates the temperature measured by the DTS in [°C] from the RESULT bit field of the DTSSTAT register.

Temperature  $T_{\text{DTS}}$  = (RESULT - 605) / 2.05 [°C]

This formula and the values defined in **Table 34** apply with the following calibration values:

- DTSCON.BGTRIM = 8<sub>H</sub>

- DTSCON.REFTRIM = 4<sub>H</sub>

## 3.2.8 USB OTG Interface DC Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification and the OTG Specification Rev. 1.3. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                            | Symbol                     |      | Values | 5    | Unit | Note /                                                   |

|--------------------------------------|----------------------------|------|--------|------|------|----------------------------------------------------------|

|                                      |                            | Min. | Тур.   | Max. |      | Test Condition                                           |

| VBUS input voltage range             | V <sub>IN</sub> CC         | 0.0  | -      | 5.25 | V    |                                                          |

| A-device VBUS valid threshold        | V <sub>B1</sub> CC         | 4.4  | -      | -    | V    |                                                          |

| A-device session valid threshold     | V <sub>B2</sub> CC         | 0.8  | -      | 2.0  | V    |                                                          |

| B-device session valid threshold     | V <sub>B3</sub> CC         | 0.8  | -      | 4.0  | V    |                                                          |

| B-device session end threshold       | V <sub>B4</sub> CC         | 0.2  | -      | 0.8  | V    |                                                          |

| VBUS input resistance to ground      | R <sub>VBUS_IN</sub><br>CC | 40   | -      | 100  | kOhm |                                                          |

| B-device VBUS pull-<br>up resistor   | R <sub>VBUS_PU</sub><br>CC | 281  | -      | -    | Ohm  | Pull-up voltage = 3.0 V                                  |

| B-device VBUS pull-<br>down resistor | R <sub>VBUS_PD</sub><br>CC | 656  | -      | -    | Ohm  |                                                          |

| USB.ID pull-up<br>resistor           | R <sub>UID_PU</sub><br>CC  | 14   | -      | 25   | kOhm |                                                          |

| VBUS input current                   | I <sub>VBUS_IN</sub><br>CC | _    | -      | 150  | μΑ   | $0 V \le V_{IN} \le 5.25 V$ :<br>T <sub>AVG</sub> = 1 ms |

#### Table 35 USB OTG VBUS and ID Parameters (Operating Conditions apply)

| Condition                                           | s apply)            |       |     |        |       |      |                                  |

|-----------------------------------------------------|---------------------|-------|-----|--------|-------|------|----------------------------------|

| Parameter                                           | Symbo               | I     | 1   | Values | 5     | Unit | Note /                           |

|                                                     |                     | Mi    | in. | Тур.   | Max.  |      | Test Condition                   |

| Input low voltage                                   | V <sub>IL</sub> S   | R –   |     | -      | 0.8   | V    |                                  |

| Input high voltage<br>(driven)                      | V <sub>IH</sub> S   | R 2.0 | 0   | -      | -     | V    |                                  |

| Input high voltage<br>(floating) <sup>1)</sup>      | V <sub>IHZ</sub> SI | R 2.1 | 7   | -      | 3.6   | V    |                                  |

| Differential input sensitivity                      | V <sub>DIS</sub> C  | C 0.2 | 2   | -      | _     | V    |                                  |

| Differential common mode range                      | V <sub>CM</sub> C   | C 0.8 | 8   | -      | 2.5   | V    |                                  |

| Output low voltage                                  | V <sub>OL</sub> C   | C 0.0 | 0   | -      | 0.3   | V    | 1.5 kOhm pull-<br>up to 3.6 V    |

| Output high voltage                                 | V <sub>OH</sub> C   | C 2.8 | 8   | -      | 3.6   | V    | 15 kOhm pull-<br>down to 0 V     |

| DP pull-up resistor (idle bus)                      | R <sub>PUI</sub> C  | C 90  | 00  | -      | 1 575 | Ohm  |                                  |

| DP pull-up resistor<br>(upstream port<br>receiving) | R <sub>PUA</sub> C  | C 1 4 | 425 | -      | 3 090 | Ohm  |                                  |

| DP, DM pull-down resistor                           | R <sub>PD</sub> CO  | C 14  | .25 | -      | 24.8  | kOhm |                                  |

| Input impedance DP,<br>DM                           | Z <sub>INP</sub> C  | C 30  | 00  | -      | -     | kOhm | $0 \ V \leq V_{IN} \leq V_{DDP}$ |

| Driver output resistance<br>DP, DM                  | Z <sub>DRV</sub> C  | C 28  | }   | -      | 44    | Ohm  |                                  |

## Table 36 USB OTG Data Line (USB\_DP, USB\_DM) Parameters (Operating Conditions apply)

Measured at A-connector with 1.5 kOhm ± 5% to 3.3 V ± 0.3 V connected to USB\_DP or USB\_DM and at Bconnector with 15 kOhm ± 5% to ground connected to USB\_DP and USB\_DM.

| Parameter                                      | Symb             | ol |      | Values | 5    | Unit   | Note /                                                                     |

|------------------------------------------------|------------------|----|------|--------|------|--------|----------------------------------------------------------------------------|

|                                                |                  |    | Min. | Тур.   | Max. |        | Test Condition                                                             |

| Power Dissipation                              | $P_{DISS}$       | СС | -    | -      | 1    | W      | V <sub>DDP</sub> = 3.6 V,<br>T <sub>J</sub> = 150 °C                       |

| Wake-up time from Sleep to Active mode         | t <sub>SSA</sub> | СС | -    | 6      | -    | cycles |                                                                            |

| Wake-up time from Deep<br>Sleep to Active mode |                  |    | -    | -      | -    | ms     | Defined by the<br>wake-up of the<br>Flash module,<br>see<br>Section 3.2.11 |

| Wake-up time from<br>Hibernate mode            |                  |    | _    | -      | -    | ms     | Wake-up via<br>power-on reset<br>event, see<br>Section 3.3.2               |

#### Table 39 Power Supply Parameters

1) CPU executing code from Flash, all peripherals idle.

2) CPU executing code from Flash. Ethernet, USB and CCU clock off.

3) CPU in sleep, all peripherals idle, Flash in Active mode.

- 4) CPU in sleep, Flash in Active mode.

- 5) CPU in sleep, peripherals disabled, after wake-up code execution from RAM.

- 6) To wake-up the Flash from its Sleep mode,  $f_{CPU} \ge 1$  MHz is required.

- 7) OSC\_ULP operating with external crystal on RTC\_XTAL

- 8) OSC\_ULP off, Hibernate domain operating with OSC\_SI clock

- 9) Test Power Loop: f<sub>SYS</sub> = 120 MHz, CPU executing benchmark code from Flash, all CCUs in 100kHz timer mode, all ADC groups in continuous conversion mode, USICs as SPI in internal loop-back mode, CAN in 500kHz internal loop-back mode, interrupt triggered DMA block transfers to parity protected RAMs and FCE, DTS measurements and FPU calculations.

The power consumption of each customer application will most probably be lower than this value, but must be evaluated separately.

- 10)  $I_{\text{DDP}}$  decreases typically by 5 mA when  $f_{\text{SYS}}$  decreases by 10 MHz, at constant  $T_{\text{J}}$

- 11) Sum of currents of all active converters (ADC and DAC)

#### Table 41 Flash Memory Parameters

| Parameter                                                                 | Symbol Values           |       |      |      | Unit   | Note /                                                                                |

|---------------------------------------------------------------------------|-------------------------|-------|------|------|--------|---------------------------------------------------------------------------------------|

|                                                                           |                         | Min.  | Тур. | Max. |        | Test Condition                                                                        |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC     | 20    | -    | -    | years  | Max. 4<br>erase/program<br>cycles per UCB                                             |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub><br>CC | 10000 | -    | -    | cycles | BA-marking<br>devices only!<br>Cycling<br>distributed over<br>life time <sup>5)</sup> |

1) In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

2) The following formula applies to the wait state configuration: FCON.WSPFLASH × (1 /  $f_{CPU}$ )  $\geq t_a$ .

3) Storage and inactive time included.

4) Values given are valid for an average weighted junction temperature of  $T_{\rm J}$  = 110°C.

5) Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see the Reference Manual.

## 3.3.9 Peripheral Timing

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

- Note: Operating conditions apply.

## 3.3.9.1 Delta-Sigma Demodulator Digital Interface Timing

The following parameters are applicable for the digital interface of the Delta-Sigma Demodulator (DSD).

The data timing is relative to the active clock edge. Depending on the operation mode of the connected modulator that can be the rising and falling clock edge.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Symbol                |    | ,                          | Values |      | Unit | Note /                                |

|------------------------------------------------|-----------------------|----|----------------------------|--------|------|------|---------------------------------------|

|                                                |                       |    | Min.                       | Тур.   | Max. |      | Test Condition                        |

| MCLK period in master mode                     | <i>t</i> <sub>1</sub> | СС | 33.3                       | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{1}$ |

| MCLK high time in master mode                  | <i>t</i> <sub>2</sub> | СС | 9                          | -      | -    | ns   | $t_2 > t_{\text{PERIPH}}^{1)}$        |

| MCLK low time in master mode                   | <i>t</i> <sub>3</sub> | СС | 9                          | -      | -    | ns   | $t_3 > t_{\text{PERIPH}}^{1)}$        |

| MCLK period in slave mode                      | <i>t</i> <sub>1</sub> | SR | 33.3                       | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{1}$ |

| MCLK high time in slave mode                   | <i>t</i> <sub>2</sub> | SR | t <sub>PERIPH</sub>        | -      | -    | ns   | 1)                                    |

| MCLK low time in slave mode                    | <i>t</i> <sub>3</sub> | SR | t <sub>PERIPH</sub>        | -      | -    | ns   | 1)                                    |

| DIN input setup time to the active clock edge  | <i>t</i> <sub>4</sub> | SR | $t_{\text{PERIPH}}$ + 4    | -      | -    | ns   | 1)                                    |

| DIN input hold time from the active clock edge | <i>t</i> <sub>5</sub> | SR | t <sub>PERIPH</sub><br>+ 3 | -      | -    | ns   | 1)                                    |

84

| Table 50 | DSD Interface Timing Parameters |

|----------|---------------------------------|

|----------|---------------------------------|

1)  $t_{\text{PERIPH}} = 1 / f_{\text{PERIPH}}$

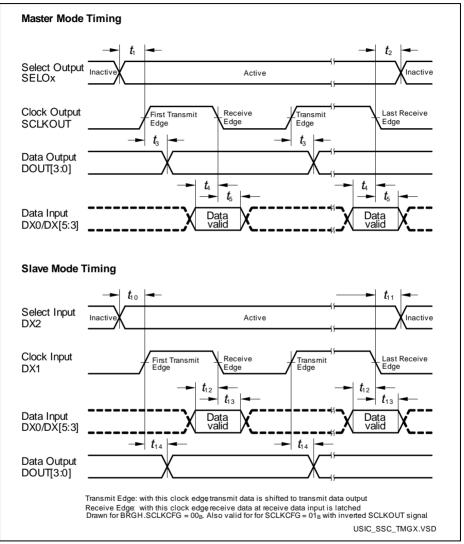

Figure 34 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration, for which the slave select signal is low-active, and the serial clock signal is not shifted and not inverted.

## 3.3.9.3 Inter-IC (IIC) Interface Timing

The following parameters are applicable for a USIC channel operated in IIC mode. *Note: Operating Conditions apply.*

| Table 53 | USIC IIC | Standard | Mode | Timing <sup>1)</sup> |

|----------|----------|----------|------|----------------------|

|----------|----------|----------|------|----------------------|

| Parameter                                              | Symbol                   | Values |      |      | Unit | Note /         |

|--------------------------------------------------------|--------------------------|--------|------|------|------|----------------|

|                                                        |                          | Min.   | Тур. | Max. |      | Test Condition |

| Fall time of both SDA and SCL                          | t <sub>1</sub><br>CC/SR  | -      | -    | 300  | ns   |                |

| Rise time of both SDA and SCL                          | t <sub>2</sub><br>CC/SR  | -      | -    | 1000 | ns   |                |

| Data hold time                                         | t <sub>3</sub><br>CC/SR  | 0      | -    | -    | μs   |                |

| Data set-up time                                       | t <sub>4</sub><br>CC/SR  | 250    | -    | -    | ns   |                |

| LOW period of SCL clock                                | t <sub>5</sub><br>CC/SR  | 4.7    | -    | -    | μs   |                |

| HIGH period of SCL clock                               | t <sub>6</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Hold time for (repeated)<br>START condition            | t <sub>7</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Set-up time for repeated START condition               | t <sub>8</sub><br>CC/SR  | 4.7    | -    | -    | μs   |                |

| Set-up time for STOP condition                         | t <sub>9</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Bus free time between a<br>STOP and START<br>condition | t <sub>10</sub><br>CC/SR | 4.7    | -    | -    | μs   |                |

| Capacitive load for each bus line                      | $C_{\rm b}{\rm SR}$      | -      | -    | 400  | pF   |                |

Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

## XMC4400 XMC4000 Family

#### Package and Reliability

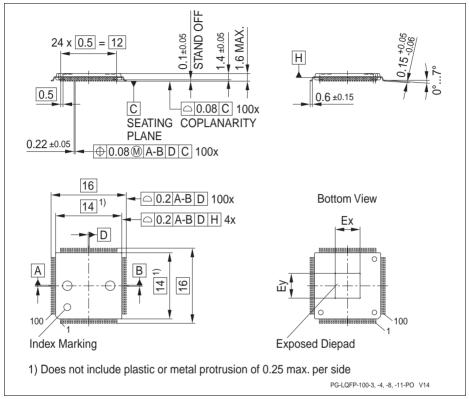

Figure 42 PG-LQFP-100-11 (Plastic Green Low Profile Quad Flat Package)

## XMC4400 XMC4000 Family

#### Package and Reliability

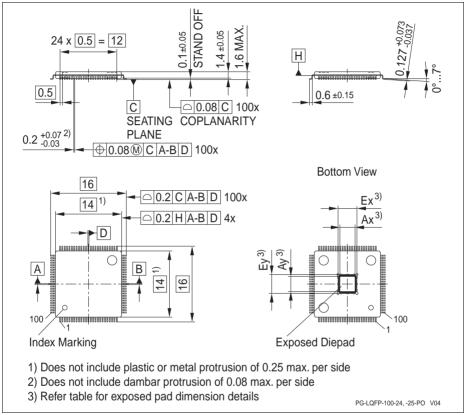

Figure 43 PG-LQFP-100-25 (Plastic Green Low Profile Quad Flat Package)