Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SPI, UART, USB                        |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                         |

| Number of I/O              | 55                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 80K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-100-11                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4400f100k512baxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Summary of Features**

## 1.3 Package Variants

Different markings of the XMC4400 use different package variants. Details of those packages are given in the **Package Parameters** section of the Data Sheet.

## Table 2 XMC4400 Package Variants

| Package Variant | Marking                  | Package        |

|-----------------|--------------------------|----------------|

| XMC4400-F100    | EES-AA, ES-AA, ES-AB, AB | PG-LQFP-100-11 |

| XMC4400-F64     |                          | PG-LQFP-64-19  |

| XMC4400-F100    | BA                       | PG-LQFP-100-25 |

| XMC4400-F64     |                          | PG-TQFP-64-19  |

## 1.4 Device Type Features

The following table lists the available features per device type.

| Derivative <sup>1)</sup> | LEDTS Intf. | ETH<br>Intf. | USB<br>Intf. | USIC<br>Chan. | MultiCAN<br>Nodes, MO |

|--------------------------|-------------|--------------|--------------|---------------|-----------------------|

| XMC4400-F100x512         | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4400-F64x512          | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4400-F100x256         | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4400-F64x256          | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4402-F100x256         | 1           | -            | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4402-F64x256          | 1           | -            | 1            | 2 x 2         | N0, N1<br>MO[063]     |

### Table 3 Features of XMC4400 Device Types

1) x is a placeholder for the supported temperature range.

### **General Device Information**

# 2 General Device Information

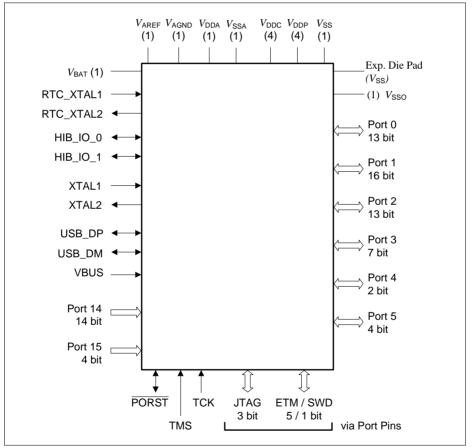

This section summarizes the logic symbols and package pin configurations with a detailed list of the functional I/O mapping.

## 2.1 Logic Symbols

Figure 2 XMC4400 Logic Symbol PG-LQFP-100

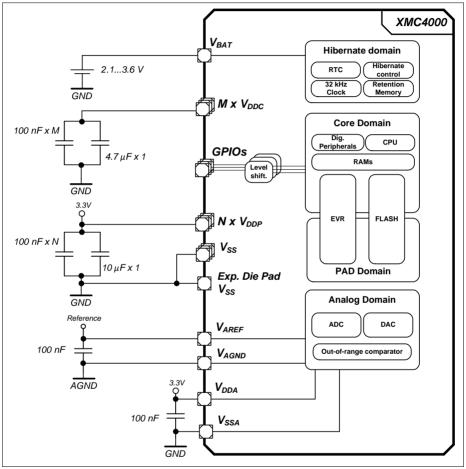

## 2.3 Power Connection Scheme

Figure 7. shows a reference power connection scheme for the XMC4400.

Figure 7 Power Connection Scheme

Every power supply pin needs to be connected. Different pins of the same supply need also to be externally connected. As example, all  $V_{\rm DDP}$  pins must be connected externally to one  $V_{\rm DDP}$  net. In this reference scheme one 100 nF capacitor is connected at each supply pin against  $V_{\rm SS}$ . An additional 10 µF capacitor is connected to the  $V_{\rm DDP}$  nets and an additional 4.7µF capacitor to the  $V_{\rm DDC}$  nets.

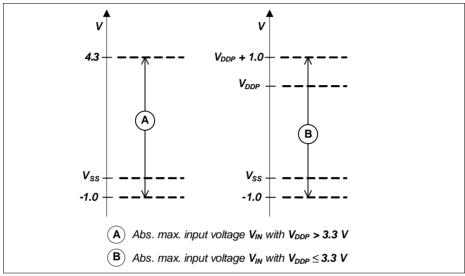

**Figure 8** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

Figure 8 Absolute Maximum Input Voltage Ranges

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 14 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload parameters, then the parameters functionality of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

## 3.1.5 Operating Conditions

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the XMC4400. All parameters specified in the following tables refer to these operating conditions, unless noted otherwise.

| Parameter                                                                | Symbol                     |                    | Values | 5                  | Unit | Note /<br>Test Condition                                                            |

|--------------------------------------------------------------------------|----------------------------|--------------------|--------|--------------------|------|-------------------------------------------------------------------------------------|

|                                                                          |                            | Min.               | Тур.   | Max.               |      |                                                                                     |

| Ambient Temperature                                                      | T <sub>A</sub> SR          | -40                | -      | 85                 | °C   | Temp. Range F                                                                       |

|                                                                          |                            | -40                | -      | 125                | °C   | Temp. Range K                                                                       |

| Digital supply voltage                                                   | $V_{\rm DDP}{\rm SR}$      | 3.13 <sup>1)</sup> | 3.3    | 3.63 <sup>2)</sup> | V    |                                                                                     |

| Core Supply Voltage                                                      | V <sub>DDC</sub><br>CC     | _1)                | 1.3    | -                  | V    | Generated internally                                                                |

| Digital ground voltage                                                   | $V_{\rm SS}$ SR            | 0                  | -      | -                  | V    |                                                                                     |

| ADC analog supply voltage                                                | $V_{\rm DDA}{\rm SR}$      | 3.0                | 3.3    | 3.6 <sup>2)</sup>  | V    |                                                                                     |

| Analog ground voltage for $V_{\rm DDA}$                                  | $V_{\rm SSA}{ m SR}$       | -0.1               | 0      | 0.1                | V    |                                                                                     |

| Battery Supply Voltage for Hibernate Domain <sup>3)</sup>                | $V_{\rm BAT}{ m SR}$       | 1.95 <sup>4)</sup> | -      | 3.63               | V    | When $V_{\text{DDP}}$ is<br>supplied $V_{\text{BAT}}$<br>has to be<br>supplied too. |

| System Frequency                                                         | $f_{\rm SYS}~{\rm SR}$     | -                  | -      | 120                | MHz  |                                                                                     |

| Short circuit current of digital outputs                                 | I <sub>SC</sub> SR         | -5                 | -      | 5                  | mA   |                                                                                     |

| Absolute sum of short<br>circuit currents per pin<br>group <sup>5)</sup> | $\Sigma I_{SC_{PG}}$<br>SR | _                  | -      | 20                 | mA   |                                                                                     |

| Absolute sum of short<br>circuit currents of the<br>device               | $\Sigma I_{SC_D}$<br>SR    | _                  | -      | 100                | mA   |                                                                                     |

| Table 19 Operating Conditions Parameters | Table 19 | Operating Conditions Parameters |

|------------------------------------------|----------|---------------------------------|

|------------------------------------------|----------|---------------------------------|

1) See also the Supply Monitoring thresholds, **Section 3.3.2**.

2) Voltage overshoot to 4.0 V is permissible at Power-Up and  $\overrightarrow{\text{PORST}}$  low, provided the pulse duration is less than 100  $\mu$ s and the cumulated sum of the pulses does not exceed 1 h over lifetime.

3) Different limits apply for LPAC operation, Section 3.2.6

4) To start the hibernate domain it is required that V<sub>BAT</sub> ≥ 2.1 V, for a reliable start of the oscillation of RTC\_XTAL in crystal mode it is required that V<sub>BAT</sub> ≥ 3.0 V.

37

5) The port groups are defined in Table 17.

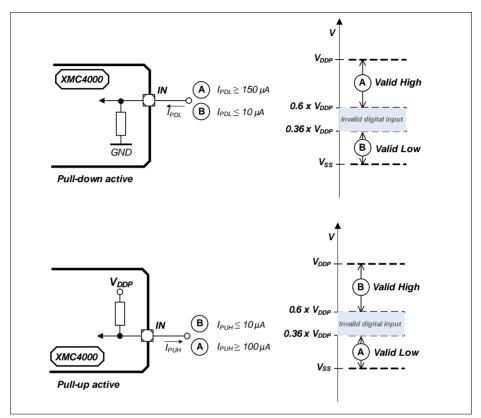

### Figure 11 Pull Device Input Characteristics

Figure 11 visualizes the input characteristics with an active internal pull device:

- in the cases "A" the internal pull device is overridden by a strong external driver;

- in the cases "B" the internal pull device defines the input logical state against a weak external load.

## Table 23 Standard Pads Class\_A2

| Parameter | Symbol              |      | Values | Unit | Note /                                                     |

|-----------|---------------------|------|--------|------|------------------------------------------------------------|

|           |                     | Min. | Max.   |      | Test Condition                                             |

| Fall time | t <sub>FA2</sub> CC | -    | 150    | ns   | $C_{L} = 20 \text{ pF};$<br>POD = weak                     |

|           |                     | -    | 50     | ns   | $C_{L} = 50 \text{ pF};$<br>POD = medium                   |

|           |                     | -    | 3.7    | ns   | $C_{L} = 50 \text{ pF};$<br>POD = strong;<br>edge = sharp  |

|           |                     | -    | 7      | ns   | $C_{L} = 50 \text{ pF};$<br>POD = strong;<br>edge = medium |

|           |                     | _    | 16     | ns   | $C_{L} = 50 \text{ pF};$<br>POD = strong;<br>edge = soft   |

| Rise time | t <sub>RA2</sub> CC | -    | 150    | ns   | $C_{L} = 20 \text{ pF};$<br>POD = weak                     |

|           |                     | -    | 50     | ns   | $C_{L} = 50 \text{ pF};$<br>POD = medium                   |

|           |                     | -    | 3.7    | ns   | $C_{L} = 50 \text{ pF};$<br>POD = strong;<br>edge = sharp  |

|           |                     | -    | 7.0    | ns   | $C_{L} = 50 \text{ pF};$<br>POD = strong;<br>edge = medium |

|           |                     | -    | 16     | ns   | $C_{L} = 50 \text{ pF};$<br>POD = strong;<br>edge = soft   |

The power-up calibration of the ADC requires a maximum number of 4 352  $f_{ADCI}$  cycles.

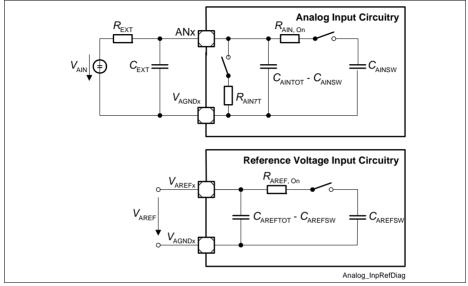

Figure 13 ADCx Input Circuits

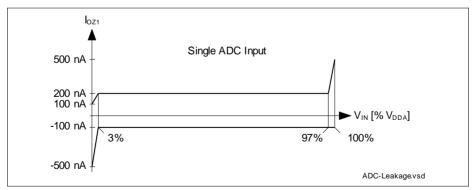

Figure 14 ADCx Analog Input Leakage Current

## 3.2.4 Out-of-Range Comparator (ORC)

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{AIN}$ ) above the analog reference<sup>1</sup> ( $V_{AREF}$ ) on selected input pins (GxORCy) and generates a service request trigger (GxORCOUTy).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The parameters in Table 28 apply for the maximum reference voltage  $V_{\text{AREF}} = V_{\text{DDA}} + 50 \text{ mV}.$

| Parameter                 | Symbol            |    |      | Values | 5                | Unit | Note / Test Condition                                 |

|---------------------------|-------------------|----|------|--------|------------------|------|-------------------------------------------------------|

|                           |                   |    | Min. | Тур.   | Max.             | 1    |                                                       |

| DC Switching Level        | $V_{\rm ODC}$     | CC | 100  | 125    | 200              | mV   | $V_{\text{AIN}} \ge V_{\text{AREF}} + V_{\text{ODC}}$ |

| Hysteresis                | $V_{\rm OHYS}$    | CC | 50   | -      | V <sub>ODC</sub> | mV   |                                                       |

| Detection Delay of a      | t <sub>ODD</sub>  | СС | 55   | -      | 450              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

| persistent<br>Overvoltage |                   |    | 45   | -      | 105              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |

| Always detected           | t <sub>OPDD</sub> | СС | 440  | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

| Overvoltage Pulse         |                   |    | 90   | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |

| Never detected            | t <sub>OPDN</sub> | СС | -    | -      | 49               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

| Overvoltage Pulse         |                   |    | -    | -      | 30               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |

| Release Delay             | t <sub>ORD</sub>  | СС | 65   | -      | 105              | ns   | $V_{AIN} \leq V_{AREF}$                               |

| Enable Delay              | t <sub>OED</sub>  | CC | -    | 100    | 200              | ns   |                                                       |

## Table 28 ORC Parameters (Operating Conditions apply)

<sup>1)</sup> Always the standard VADC reference, alternate references do not apply to the ORC.

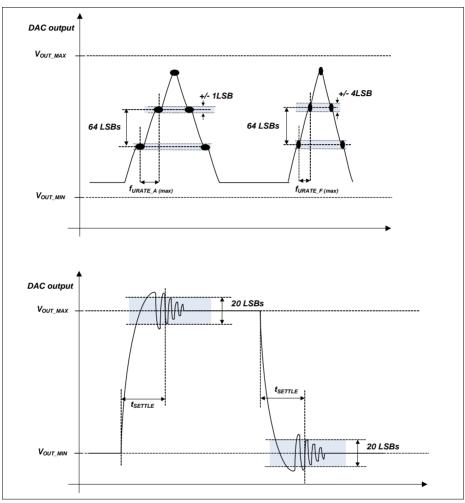

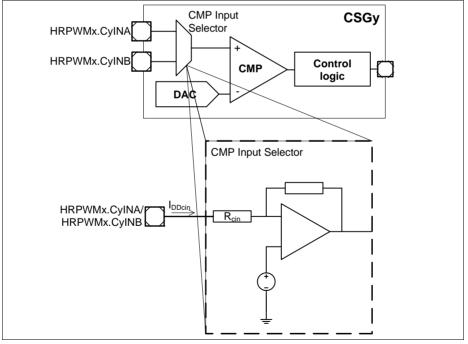

| Table 30 | CMP and 10-bit DAC characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|          | (cont'd)                                                        |

| Parameter                                     | Symbol                    |                             | Value | s         | Unit | Note /<br>Test Condition |

|-----------------------------------------------|---------------------------|-----------------------------|-------|-----------|------|--------------------------|

|                                               |                           | Min.                        | Тур.  | Max.      |      |                          |

| CSG Output Jitter                             | D <sub>CSG</sub><br>CC    | -                           | -     | 1         | clk  |                          |

| Bias startup time                             | t <sub>start</sub> CC     | -                           | -     | 98        | us   |                          |

| Bias supply current                           | I <sub>DDbias</sub><br>CC | -                           | -     | 400       | μA   |                          |

| CSGy startup time                             | t <sub>CSGS</sub><br>CC   | -                           | -     | 2         | μS   |                          |

| Input operation current <sup>1)</sup>         |                           | -10                         | -     | 33        | μA   | See Figure 19            |

| High Speed Mode                               |                           | 1                           |       |           | -1   | 1                        |

| DAC output voltage range                      | $V_{\text{DOUT}}$         | $V_{\rm SS}$                | -     | $V_{DDP}$ | V    |                          |

| DAC propagation delay -<br>Full scale         | t <sub>FShs</sub><br>CC   | -                           | -     | 80        | ns   | See Figure 20            |

| Input Selector propagation delay - Full scale | t <sub>Dhs</sub> CC       | -                           | -     | 100       | ns   | See Figure 20            |

| Comparator bandwidth                          | t <sub>Dhs</sub> CC       | 20                          | -     | -         | ns   |                          |

| DAC CLK frequency                             | $f_{\rm clk}~{\rm SR}$    | -                           | -     | 30        | MHz  |                          |

| Supply current                                | I <sub>DDhs</sub><br>CC   | -                           | -     | 940       | μA   |                          |

| Low Speed Mode                                |                           | *                           |       |           |      | 1                        |

| DAC output voltage range                      | V <sub>DOUT</sub><br>CC   | $0.1 	imes V_{ m DDP}^{2)}$ | -     | $V_{DDP}$ | V    |                          |

| DAC propagation delay -<br>Full Scale         | t <sub>FSIs</sub> CC      | -                           | -     | 160       | ns   | See Figure 20            |

| Input Selector propagation delay - Full Scale | t <sub>Dls</sub> CC       | -                           | -     | 200       | ns   | See Figure 20            |

| Comparator bandwidth                          | t <sub>DIs</sub> CC       | 20                          | -     | -         | ns   |                          |

| DAC CLK frequency                             | $f_{\rm clk}$ SR          | _                           | -     | 30        | MHz  |                          |

| Supply current                                | I <sub>DDIs</sub><br>CC   | -                           | -     | 300       | μA   |                          |

| 4) Tradical in a standard and D               |                           |                             |       | 1         |      |                          |

1) Typical input resistance  $R_{CIN} = 100$ kOhm.

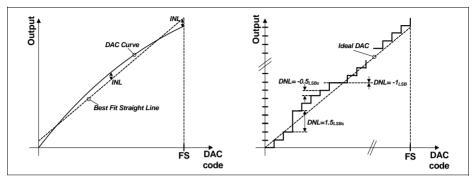

2) The INL error increases for DAC output voltages below this limit.

Figure 19 Input operation current

## **Peripheral Idle Currents**

Test conditions:

- f<sub>svs</sub> and derived clocks at 120 MHz

- V<sub>DDP</sub> = 3.3 V, T<sub>a</sub> =25 °C

- all peripherals are held in reset (see the PRSTAT registers in the Reset Control Unit of the SCU)

- the peripheral clocks are disabled (see CGATSTAT registers in the Clock Control Unit of the SCU

- no I/O activity

- the given values are a result of differential measurements with asserted and deasserted peripheral reset and enabled clock of the peripheral under test

The tested peripheral is left in the state after the peripheral reset is deasserted, no further initialisation or configuration is done. E.g. no timer is running in the CCUs, no communication active in the USICs, etc.

| Parameter                                     | Symbol              |      | Values |      | Unit | Note /         |

|-----------------------------------------------|---------------------|------|--------|------|------|----------------|

|                                               |                     | Min. | Тур.   | Max. |      | Test Condition |

| PORTS<br>ETH<br>USB<br>FCE<br>WDT<br>POSIFx   | I <sub>PER</sub> CC | -    | ≤ 0.3  | _    | mA   |                |

| MultiCAN<br>ERU<br>LEDTSCU0<br>CCU4x<br>CCU8x |                     | -    | ≤ 1.0  | _    |      |                |

| DAC (digital) <sup>1)</sup>                   |                     | -    | 1.3    | -    |      |                |

| USICx                                         | 1                   | -    | 3.0    | -    | 1    |                |

| DSD<br>VADC (digital) <sup>1)</sup>           |                     | -    | 4.5    | -    |      |                |

| DMAx                                          | 1                   | -    | 6.0    | -    | 1    |                |

## Table 40Peripheral Idle Currents

1) The current consumption of the analog components are given in the dedicated Data Sheet sections of the respective peripheral.

#### Table 41 Flash Memory Parameters

| Parameter                                                                 | Symbol Values           |       |      | Unit | Note / |                                                                                       |

|---------------------------------------------------------------------------|-------------------------|-------|------|------|--------|---------------------------------------------------------------------------------------|

|                                                                           |                         | Min.  | Тур. | Max. |        | Test Condition                                                                        |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC     | 20    | -    | -    | years  | Max. 4<br>erase/program<br>cycles per UCB                                             |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub><br>CC | 10000 | -    | -    | cycles | BA-marking<br>devices only!<br>Cycling<br>distributed over<br>life time <sup>5)</sup> |

1) In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

2) The following formula applies to the wait state configuration: FCON.WSPFLASH × (1 /  $f_{CPU}$ )  $\geq t_a$ .

3) Storage and inactive time included.

4) Values given are valid for an average weighted junction temperature of  $T_{\rm J}$  = 110°C.

5) Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see the Reference Manual.

## 3.3.5 Internal Clock Source Characteristics

### Fast Internal Clock Source

| Parameter         | Symbol                         |      | Value | S    | Unit | Note /                                                                              |

|-------------------|--------------------------------|------|-------|------|------|-------------------------------------------------------------------------------------|

|                   |                                | Min. | Тур.  | Max. |      | Test Condition                                                                      |

| Nominal frequency | $f_{\rm OFINC}$                | -    | 36.5  | -    | MHz  | not calibrated                                                                      |

|                   | CC                             | -    | 24    | -    | MHz  | calibrated                                                                          |

| Accuracy          | <i>∆f</i> <sub>OFI</sub><br>CC | -0.5 | -     | 0.5  | %    | automatic<br>calibration <sup>1)2)</sup>                                            |

|                   |                                | -15  | -     | 15   | %    | factory<br>calibration,<br>$V_{\text{DDP}} = 3.3 \text{ V}$                         |

|                   |                                | -25  | -     | 25   | %    | no calibration,<br>$V_{\text{DDP}}$ = 3.3 V                                         |

|                   |                                | -7   | -     | 7    | %    | Variation over<br>voltage range <sup>3)</sup><br>$3.13 V \le V_{DDP} \le$<br>3.63 V |

| Start-up time     | t <sub>OFIS</sub> CC           | -    | 50    | -    | μS   |                                                                                     |

## Table 45 Fast Internal Clock Parameters

1) Error in addition to the accuracy of the reference clock.

2) Automatic calibration compensates variations of the temperature and in the  $V_{\rm DDP}$  supply voltage.

3) Deviations from the nominal  $V_{\text{DDP}}$  voltage induce an additional error to the uncalibrated and/or factory calibrated oscillator frequency.

## 3.3.6 JTAG Interface Timing

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Note: Operating conditions apply.

| Parameter                                                          | Symbol                 |    |      | Values | 5    | Unit | Note /                 |

|--------------------------------------------------------------------|------------------------|----|------|--------|------|------|------------------------|

|                                                                    |                        |    | Min. | Тур.   | Max. |      | Test Condition         |

| TCK clock period                                                   | <i>t</i> <sub>1</sub>  | SR | 25   | -      | -    | ns   |                        |

| TCK high time                                                      | $t_2$                  | SR | 10   | -      | -    | ns   |                        |

| TCK low time                                                       | $t_3$                  | SR | 10   | -      | -    | ns   |                        |

| TCK clock rise time                                                | $t_4$                  | SR | -    | _      | 4    | ns   |                        |

| TCK clock fall time                                                | $t_5$                  | SR | -    | -      | 4    | ns   |                        |

| TDI/TMS setup<br>to TCK rising edge                                | t <sub>6</sub>         | SR | 6    | -      | -    | ns   |                        |

| TDI/TMS hold<br>after TCK rising edge                              | <i>t</i> <sub>7</sub>  | SR | 6    | -      | -    | ns   |                        |

| TDO valid after TCK falling edge <sup>1)</sup> (propagation delay) | t <sub>8</sub>         | CC | -    | _      | 13   | ns   | C <sub>L</sub> = 50 pF |

|                                                                    |                        |    | 3    | _      | -    | ns   | C <sub>L</sub> = 20 pF |

| TDO hold after TCK falling edge <sup>1)</sup>                      | t <sub>18</sub>        | CC | 2    | -      | -    | ns   |                        |

| TDO high imped. to valid from TCK falling edge <sup>1)2)</sup>     | t <sub>9</sub>         | СС | -    | -      | 14   | ns   | C <sub>L</sub> = 50 pF |

| TDO valid to high imped.<br>from TCK falling edge <sup>1)</sup>    | <i>t</i> <sub>10</sub> | СС | -    | -      | 13.5 | ns   | C <sub>L</sub> = 50 pF |

Table 47 JTAG Interface Timing Parameters

1) The falling edge on TCK is used to generate the TDO timing.

2) The setup time for TDO is given implicitly by the TCK cycle time.

## 3.3.9 Peripheral Timing

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

- Note: Operating conditions apply.

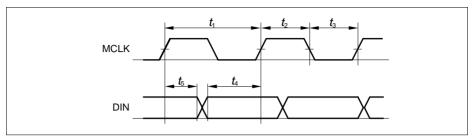

## 3.3.9.1 Delta-Sigma Demodulator Digital Interface Timing

The following parameters are applicable for the digital interface of the Delta-Sigma Demodulator (DSD).

The data timing is relative to the active clock edge. Depending on the operation mode of the connected modulator that can be the rising and falling clock edge.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Symbol                |    | ,                       | Values | ;    | Unit | Note /                                |

|------------------------------------------------|-----------------------|----|-------------------------|--------|------|------|---------------------------------------|

|                                                |                       |    | Min.                    | Тур.   | Max. | -    | Test Condition                        |

| MCLK period in master mode                     | t <sub>1</sub>        | CC | 33.3                    | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{1}$ |

| MCLK high time in master mode                  | <i>t</i> <sub>2</sub> | СС | 9                       | -      | -    | ns   | $t_2 > t_{\text{PERIPH}}^{1)}$        |

| MCLK low time in master mode                   | <i>t</i> <sub>3</sub> | СС | 9                       | -      | -    | ns   | $t_3 > t_{\text{PERIPH}}^{1)}$        |

| MCLK period in slave mode                      | t <sub>1</sub>        | SR | 33.3                    | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{1}$ |

| MCLK high time in slave mode                   | <i>t</i> <sub>2</sub> | SR | t <sub>PERIPH</sub>     | -      | -    | ns   | 1)                                    |

| MCLK low time in slave mode                    | <i>t</i> <sub>3</sub> | SR | t <sub>PERIPH</sub>     | -      | -    | ns   | 1)                                    |

| DIN input setup time to the active clock edge  | <i>t</i> <sub>4</sub> | SR | $t_{\text{PERIPH}}$ + 4 | -      | -    | ns   | 1)                                    |

| DIN input hold time from the active clock edge | t <sub>5</sub>        | SR | $t_{\text{PERIPH}}$ + 3 | -      | -    | ns   | 1)                                    |

84

| Table 50 | DSD Interface Timing Parameters |

|----------|---------------------------------|

|----------|---------------------------------|

1)  $t_{\text{PERIPH}} = 1 / f_{\text{PERIPH}}$

Figure 33 DSD Data Timing

## 3.3.9.2 Synchronous Serial Interface (USIC SSC) Timing

The following parameters are applicable for a USIC channel operated in SSC mode. *Note: Operating Conditions apply.*

| Parameter                                                               | Symbol              |                                         | Value | S    | Unit | Note /<br>Test Condition |

|-------------------------------------------------------------------------|---------------------|-----------------------------------------|-------|------|------|--------------------------|

|                                                                         |                     | Min.                                    | Тур.  | Max. |      |                          |

| SCLKOUT master clock period                                             | t <sub>CLK</sub> CC | 33.3                                    | -     | -    | ns   |                          |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC   | t <sub>SYS</sub> -<br>6.5 <sup>1)</sup> | -     | -    | ns   |                          |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC   | t <sub>SYS</sub> -<br>8.5 <sup>1)</sup> | -     | -    | ns   |                          |

| Data output DOUT[3:0] valid time                                        | t <sub>3</sub> CC   | -6                                      | -     | 8    | ns   |                          |

| Receive data input<br>DX0/DX[5:3] setup time to<br>SCLKOUT receive edge | t <sub>4</sub> SR   | 23                                      | -     | -    | ns   |                          |

| Data input DX0/DX[5:3]<br>hold time from SCLKOUT<br>receive edge        | t <sub>5</sub> SR   | 1                                       | _     | -    | ns   |                          |

## Table 51 USIC SSC Master Mode Timing

1)  $t_{SYS} = 1 / f_{PB}$

## Table 52 USIC SSC Slave Mode Timing

| 6                                                                                         |                  |      |      |        |      |      |                |  |

|-------------------------------------------------------------------------------------------|------------------|------|------|--------|------|------|----------------|--|

| Parameter                                                                                 |                  | nbol |      | Values | S    | Unit | Note /         |  |

|                                                                                           |                  |      | Min. | Тур.   | Max. |      | Test Condition |  |

| DX1 slave clock period                                                                    | t <sub>CLK</sub> | SR   | 66.6 | -      | -    | ns   |                |  |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>               | t <sub>10</sub>  | SR   | 3    | -      | -    | ns   |                |  |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup>         | t <sub>11</sub>  | SR   | 4    | -      | -    | ns   |                |  |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | t <sub>12</sub>  | SR   | 6    | -      | -    | ns   |                |  |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | t <sub>13</sub>  | SR   | 4    | -      | -    | ns   |                |  |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub>  | СС   | 0    | -      | 24   | ns   |                |  |

These input timing are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

### Package and Reliability

# 4 Package and Reliability

The XMC4400 is a member of the XMC4000 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Die Pad may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.

## 4.1 Package Parameters

Table 60 provides the thermal characteristics of the packages used in XMC4400.

| Parameter                                                               | Symbol             | Lim  | it Values                          | Unit | Package Types                |  |

|-------------------------------------------------------------------------|--------------------|------|------------------------------------|------|------------------------------|--|

|                                                                         |                    | Min. | Max.                               |      |                              |  |

| Exposed Die Pad<br>dimensions (including U-<br>Groove where applicable) | Ex × Ey<br>CC      | -    | 7.0 	imes 7.0                      | mm   | PG-LQFP-100-11               |  |

|                                                                         |                    | -    | 7.0 	imes 7.0                      | mm   | PG-LQFP-100-25               |  |

|                                                                         |                    | -    | $\textbf{5.8} \times \textbf{5.8}$ | mm   | PG-LQFP-64-19                |  |

|                                                                         |                    | -    | 5.7 	imes 5.7                      | mm   | PG-TQFP-64-19                |  |

| Exposed Die Pad<br>dimensions excluding U-<br>Groove                    | Ax × Ay<br>CC      | -    | 6.2 × 6.2                          | mm   | PG-LQFP-100-25               |  |

| Thermal resistance Junction-Ambient $T_{\rm J} \leq 150~{\rm °C}$       | $R_{\Theta JA}$ CC | -    | 20.5                               | K/W  | PG-LQFP-100-11 <sup>1)</sup> |  |

|                                                                         |                    | -    | 20.0                               | K/W  | PG-LQFP-100-25 <sup>1)</sup> |  |

|                                                                         |                    | -    | 30.0                               | K/W  | PG-LQFP-64-19 <sup>1)</sup>  |  |

|                                                                         |                    | -    | 22.5                               | K/W  | PG-TQFP-64-19 <sup>1)</sup>  |  |

Table 60

Thermal Characteristics of the Packages

1) Device mounted on a 4-layer JEDEC board (JESD 51-7) with thermal vias; exposed pad soldered.

Note: For electrical reasons, it is required to connect the exposed pad to the board ground  $V_{SS}$ , independent of EMC and thermal requirements.

## 4.1.1 Thermal Considerations

When operating the XMC4400 in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.