#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SPI, UART, USB                       |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| Number of I/O              | 31                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 80K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters            | A/D 14x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-64-19                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4400f64k512baxqma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### XMC4400 Data Sheet

Revision History: V1.2 2015-12

| IVE AISIOII | Thistory. V1.2 2013-12                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous    |                                                                                                                                                                  |

| V1.1 2014   |                                                                                                                                                                  |

| V1.0 2013   |                                                                                                                                                                  |

| V0.6 2012   |                                                                                                                                                                  |

| Page        | Subjects                                                                                                                                                         |

| 12          | Added a section listing the packages of the different markings.                                                                                                  |

| 14          | Added BA marking variant.                                                                                                                                        |

| 37          | Added footnote explaining minimum $V_{\rm BAT}$ requirements to start the hibernate domain and/or oscillation of a crystal on RTC_XTAL.                          |

| 38          | Changed pull device definition to System Requirement (SR) to reflect that the specified currents are defined by the characteristics of the external load/driver. |

| 38          | Added information that PORST Pull-up is identical to the pull-up on standard I/O pins.                                                                           |

| 45          | Updated $C_{\text{AINSW}}$ , $C_{\text{AINTOT}}$ and $R_{\text{AIN}}$ parameters with improved values.                                                           |

| 59          | Added footnote on test configuration for LPAC measurement.                                                                                                       |

| 61          | Corrected parameter name of of USB pull device (upstream port receiving) definition according to USB standard (referenced to DM instead of DP)                   |

| 66          | Relaxed RTC_XTAL $V_{\rm PPX}$ parameter value and changed it to a system requirement.                                                                           |

| 70          | Added footnote on current consumption by enabling of $f_{CCU}$ .                                                                                                 |

| 71          | Added Flash endurance parameter for 64 Kbytes Physical Sector PS4 $N_{\rm EPS4}$ for devices with BA marking.                                                    |

| many        | Added PG-TQFP-64-19 and PG-LQFP-100-25 package information.                                                                                                      |

| 97, 100     | Added tables describing the differences between PG-LQFP-100-11 to PG-LQFP-100-25 as well as PG-LQFP-64-19 to PG-TQFP-64-19 packages.                             |

| 102         | Updated to JEDEC standard J-STD-020D for the moisture sensitivity level and added solder temperature parameter according to the same standard.                   |

| -           |                                                                                                                                                                  |

## Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG. ARM<sup>®</sup>, ARM Powered<sup>®</sup>, Cortex<sup>®</sup>, Thumb<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM, Limited.

Synopsys<sup>™</sup> is a trademark of Synopsys, Inc.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### Summary of Features

## **On-Chip Memories**

- 16 KB on-chip boot ROM

- 16 KB on-chip high-speed program memory

- 32 KB on-chip high speed data memory

- 32 KB on-chip high-speed communication memory

- 512 KB on-chip Flash Memory with 4 KB instruction cache

## **Communication Peripherals**

- Ethernet MAC module capable of 10/100 Mbit/s transfer rates

- Universal Serial Bus, USB 2.0 host, Full-Speed OTG, with integrated PHY

- Controller Area Network interface (MultiCAN), Full-CAN/Basic-CAN with two nodes, 64 message objects (MO), data rate up to 1MBit/s

- Four Universal Serial Interface Channels (USIC), providing four serial channels, usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- LED and Touch-Sense Controller (LEDTS) for Human-Machine interface

## **Analog Frontend Peripherals**

- Four Analog-Digital Converters (VADC) of 12-bit resolution, 8 channels each, with input out-of-range comparators

- Delta Sigma Demodulator with four channels, digital input stage for A/D signal conversion

- Digital-Analog Converter (DAC) with two channels of 12-bit resolution

## **Industrial Control Peripherals**

- Two Capture/Compare Units 8 (CCU8) for motor control and power conversion

- Four Capture/Compare Units 4 (CCU4) for use as general purpose timers

- Four High Resoultion PWM (HRPWM) channels

- Two Position Interfaces (POSIF) for servo motor positioning

- Window Watchdog Timer (WDT) for safety sensitive applications

- Die Temperature Sensor (DTS)

- · Real Time Clock module with alarm support

- System Control Unit (SCU) for system configuration and control

## Input/Output Lines

- Programmable port driver control module (PORTS)

- Individual bit addressability

- Tri-stated in input mode

- Push/pull or open drain output mode

- Boundary scan test support over JTAG interface

## XMC4400 XMC4000 Family

#### **General Device Information**

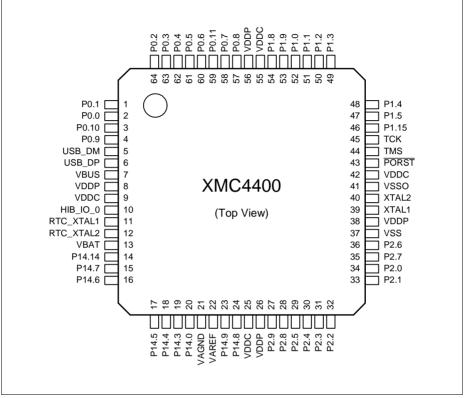

Figure 5 XMC4400 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

## 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                              | Symbol                                 |    |      | Va   | lues                                  | Unit | Note /                |  |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----|------|------|---------------------------------------|------|-----------------------|--|

|                                                                                                                        |                                        |    | Min. | Тур. | Max.                                  |      | Test Con<br>dition    |  |

| Storage temperature                                                                                                    | $T_{\rm ST}$                           | SR | -65  | -    | 150                                   | °C   | -                     |  |

| Junction temperature                                                                                                   | TJ                                     | SR | -40  | _    | 150                                   | °C   | -                     |  |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}$                                                        | $V_{DDP}$                              | SR | -    | -    | 4.3                                   | V    | -                     |  |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                            | V <sub>IN</sub>                        | SR | -1.0 | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |  |

| Voltage on any analog input pin with respect to $V_{\text{AGND}}$                                                      | $V_{\mathrm{AIN}} \ V_{\mathrm{AREF}}$ | SR | -1.0 | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |  |

| Input current on any pin<br>during overload condition                                                                  | I <sub>IN</sub>                        | SR | -10  | -    | +10                                   | mA   |                       |  |

| Absolute maximum sum of all<br>input circuit currents for one<br>port group during overload<br>condition <sup>1)</sup> | $\Sigma I_{\rm IN}$                    | SR | -25  | -    | +25                                   | mA   |                       |  |

| Absolute maximum sum of all input circuit currents during overload condition                                           | $\Sigma I_{\rm IN}$                    | SR | -100 | _    | +100                                  | mA   |                       |  |

#### Table 13 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 17**.

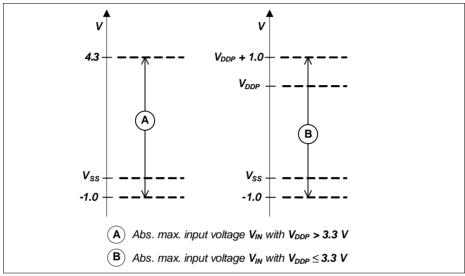

**Figure 8** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

Figure 8 Absolute Maximum Input Voltage Ranges

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 14 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload parameters, then the parameters functionality of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

### Table 22 Standard Pads Class\_A1+

| Parameter            | Symbol               | Va                     | lues | Unit | Note /                                                                  |  |

|----------------------|----------------------|------------------------|------|------|-------------------------------------------------------------------------|--|

|                      |                      | Min.                   | Max. |      | Test Condition                                                          |  |

| Output high voltage, | V <sub>OHA1+</sub>   | V <sub>DDP</sub> - 0.4 | -    | V    | <i>I</i> <sub>OH</sub> ≥ -400 μA                                        |  |

| $POD^{1)} = weak$    | CC                   | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -500 μA                                        |  |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | I <sub>OH</sub> ≥ -1.4 mA                                               |  |

| $POD^{1)} = medium$  |                      | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -2 mA                                          |  |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | $I_{\rm OH} \ge$ -1.4 mA                                                |  |

| $POD^{1)} = strong$  |                      | 2.4                    | _    | V    | $I_{\rm OH} \ge$ -2 mA                                                  |  |

| Output low voltage   | $V_{\rm OLA1+}$ CC   | _                      | 0.4  | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak                   |  |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium                |  |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = strong                |  |

| Fall time            | t <sub>FA1+</sub> CC | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |  |

|                      |                      | -                      | 50   | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium                      |  |

|                      |                      | _                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |  |

|                      |                      | _                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft; |  |

| Rise time            | t <sub>RA1+</sub> CC | -                      | 150  | ns   | $C_{\rm L}$ = 20 pF;<br>POD <sup>1)</sup> = weak                        |  |

|                      |                      | -                      | 50   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium                  |  |

|                      |                      | -                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |  |

|                      |                      | -                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft  |  |

1) POD = Pin Out Driver

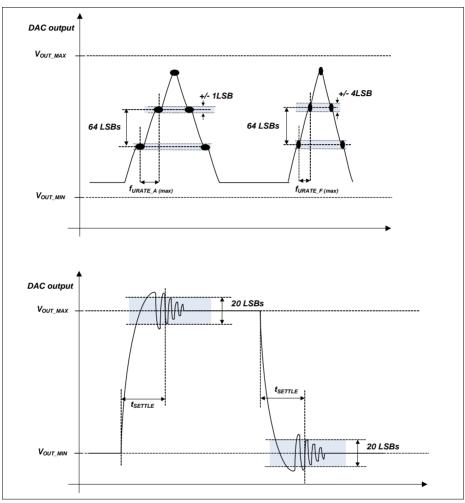

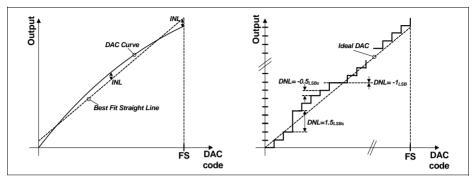

## 3.2.3 Digital to Analog Converters (DACx)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                | Symbol                    |                   |      | Values | 5    | Unit          | Note /                                                                            |  |

|------------------------------------------|---------------------------|-------------------|------|--------|------|---------------|-----------------------------------------------------------------------------------|--|

|                                          |                           |                   | Min. | Тур.   | Max. |               | Test Condition                                                                    |  |

| RMS supply current                       | I <sub>DD</sub>           | CC                | -    | 2.5    | 4    | mA            | per active DAC<br>channel,<br>without load<br>currents of DAC<br>outputs          |  |

| Resolution                               | RES                       | CC                | -    | 12     | -    | Bit           |                                                                                   |  |

| Update rate                              | furate.                   | _ <sub>A</sub> CC | _    |        | 2    | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 1LSB accuracy     |  |

| Update rate                              | furate.                   | _F CC             | _    |        | 5    | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 4 LSB accuracy    |  |

| Settling time                            | t <sub>settle</sub>       | CC                | -    | 1      | 2    | μs            | at full scale jump,<br>output voltage<br>reaches target<br>value ± 20 LSB         |  |

| Slew rate                                | SR                        | CC                | 2    | 5      | -    | V/µs          |                                                                                   |  |

| Minimum output<br>voltage                | V <sub>OUT_</sub> N<br>CC | MIN               | -    | 0.3    | -    | V             | code value<br>unsigned: 000 <sub>H</sub> ;<br>signed: 800 <sub>H</sub>            |  |

| Maximum output<br>voltage                | V <sub>OUT_</sub> M<br>CC | мах               | -    | 2.5    | -    | V             | code value<br>unsigned: FFF <sub>H</sub> ;<br>signed: 7FF <sub>H</sub>            |  |

| Integral non-<br>linearity <sup>1)</sup> | INL                       | CC                | -5.5 | ±2.5   | 5.5  | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm,} \\ C_L \leq 50 \text{ pF} \end{array}$ |  |

| Differential non-<br>linearity           | DNL                       | CC                | -2   | ±1     | 2    | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm,} \\ C_L \leq 50 \text{ pF} \end{array}$ |  |

| Table 27 DAC Parameters | (Operating Conditions apply) |

|-------------------------|------------------------------|

|-------------------------|------------------------------|

## 3.2.4 Out-of-Range Comparator (ORC)

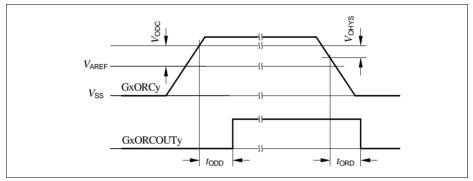

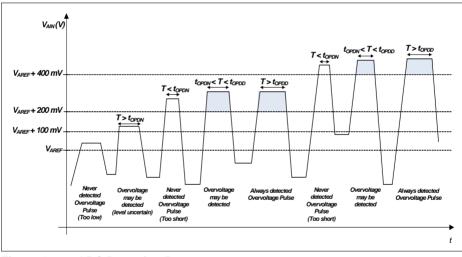

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{AIN}$ ) above the analog reference<sup>1</sup> ( $V_{AREF}$ ) on selected input pins (GxORCy) and generates a service request trigger (GxORCOUTy).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The parameters in Table 28 apply for the maximum reference voltage  $V_{\text{AREF}} = V_{\text{DDA}} + 50 \text{ mV}.$

| Parameter                 | Symbol            |    |      | Values | 5                | Unit | Note / Test Condition                                 |  |

|---------------------------|-------------------|----|------|--------|------------------|------|-------------------------------------------------------|--|

|                           |                   |    | Min. | Тур.   | Max.             | 1    |                                                       |  |

| DC Switching Level        | $V_{\rm ODC}$     | CC | 100  | 125    | 200              | mV   | $V_{\text{AIN}} \ge V_{\text{AREF}} + V_{\text{ODC}}$ |  |

| Hysteresis                | $V_{\rm OHYS}$    | CC | 50   | -      | V <sub>ODC</sub> | mV   |                                                       |  |

| Detection Delay of a      | t <sub>ODD</sub>  | CC | 55   | -      | 450              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |  |

| persistent<br>Overvoltage |                   |    | 45   | -      | 105              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |  |

| Always detected           | t <sub>OPDD</sub> | СС | 440  | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |  |

| Overvoltage Pulse         |                   |    | 90   | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |  |

| Never detected            | t <sub>OPDN</sub> | СС | -    | -      | 49               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |  |

| Overvoltage Pulse         |                   |    | -    | -      | 30               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |  |

| Release Delay             | t <sub>ORD</sub>  | СС | 65   | -      | 105              | ns   | $V_{AIN} \leq V_{AREF}$                               |  |

| Enable Delay              | t <sub>OED</sub>  | CC | -    | 100    | 200              | ns   |                                                       |  |

## Table 28 ORC Parameters (Operating Conditions apply)

<sup>1)</sup> Always the standard VADC reference, alternate references do not apply to the ORC.

Figure 16 GxORCOUTy Trigger Generation

Figure 17 ORC Detection Ranges

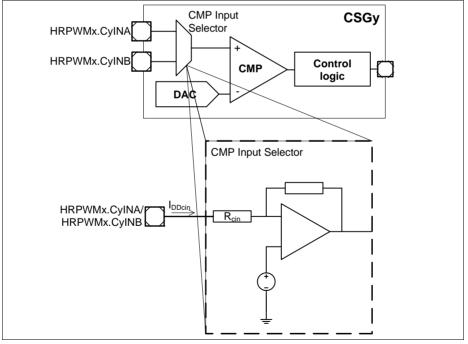

| Table 30 | CMP and 10-bit DAC characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|          | (cont'd)                                                        |

| Parameter                                     | Symbol                    |                             | Value | s         | Unit | Note /<br>Test Conditior |

|-----------------------------------------------|---------------------------|-----------------------------|-------|-----------|------|--------------------------|

|                                               |                           | Min.                        | Тур.  | Max.      |      |                          |

| CSG Output Jitter                             | D <sub>CSG</sub><br>CC    | -                           | -     | 1         | clk  |                          |

| Bias startup time                             | t <sub>start</sub> CC     | -                           | -     | 98        | us   |                          |

| Bias supply current                           | I <sub>DDbias</sub><br>CC | -                           | -     | 400       | μA   |                          |

| CSGy startup time                             | t <sub>CSGS</sub><br>CC   | -                           | -     | 2         | μS   |                          |

| Input operation current <sup>1)</sup>         |                           | -10                         | -     | 33        | μA   | See Figure 19            |

| High Speed Mode                               |                           | 1                           |       |           | -1   | 1                        |

| DAC output voltage range                      | $V_{\text{DOUT}}$         | $V_{\rm SS}$                | -     | $V_{DDP}$ | V    |                          |

| DAC propagation delay -<br>Full scale         | t <sub>FShs</sub><br>CC   | -                           | -     | 80        | ns   | See Figure 20            |

| Input Selector propagation delay - Full scale | t <sub>Dhs</sub> CC       | -                           | -     | 100       | ns   | See Figure 20            |

| Comparator bandwidth                          | t <sub>Dhs</sub> CC       | 20                          | -     | -         | ns   |                          |

| DAC CLK frequency                             | $f_{\rm clk}~{\rm SR}$    | -                           | -     | 30        | MHz  |                          |

| Supply current                                | I <sub>DDhs</sub><br>CC   | -                           | -     | 940       | μA   |                          |

| Low Speed Mode                                |                           | *                           |       |           |      | 1                        |

| DAC output voltage range                      | V <sub>DOUT</sub><br>CC   | $0.1 	imes V_{ m DDP}^{2)}$ | -     | $V_{DDP}$ | V    |                          |

| DAC propagation delay -<br>Full Scale         | t <sub>FSIs</sub> CC      | -                           | -     | 160       | ns   | See Figure 20            |

| Input Selector propagation delay - Full Scale | t <sub>Dls</sub> CC       | -                           | -     | 200       | ns   | See Figure 20            |

| Comparator bandwidth                          | t <sub>DIs</sub> CC       | 20                          | -     | -         | ns   |                          |

| DAC CLK frequency                             | $f_{\rm clk}$ SR          | _                           | -     | 30        | MHz  |                          |

| Supply current                                | I <sub>DDIs</sub><br>CC   | -                           | -     | 300       | μA   |                          |

| 4) Transaction of a sister of D               |                           |                             |       | 1         |      |                          |

1) Typical input resistance  $R_{CIN} = 100$ kOhm.

2) The INL error increases for DAC output voltages below this limit.

Figure 19 Input operation current

| Parameter | Symbol                  |                                           | Value | Unit              | Note / |                                       |

|-----------|-------------------------|-------------------------------------------|-------|-------------------|--------|---------------------------------------|

|           |                         | Min.                                      | Тур.  | Max.              |        | Test Con<br>dition                    |

| Frequency | $f_{eclk}$ SR           | -                                         | -     | $f_{\rm hrpwm}/4$ | MHz    |                                       |

| ON time   | t <sub>oneclk</sub> SR  | $2T_{\rm ccu}^{(1)2)}$                    | -     | -                 | ns     |                                       |

| OFF time  | t <sub>offeclk</sub> SR | 2 <i>T</i> <sub>ccu</sub> <sup>1)2)</sup> | -     | -                 | ns     | Only the<br>rising<br>edge is<br>used |

### Table 32 External clock operating conditions

1) 50% duty cycle is not obligatory

2) Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

## 3.2.6 Low Power Analog Comparator (LPAC)

The Low Power Analog Comparator (LPAC) triggers a wake-up event from Hibernate state or an interrupt trigger during normal operation. It does so by comparing  $V_{\rm BAT}$  or another external sensor voltage  $V_{\rm LPS}$  with a pre-programmed threshold voltage.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                             | Symbol                   | ymbol Values |       |      |    | Note /                                     |

|-------------------------------------------------------|--------------------------|--------------|-------|------|----|--------------------------------------------|

|                                                       |                          | Min.         | Тур.  | Max. |    | Test Condition                             |

| $V_{\rm BAT}$ supply voltage range for LPAC operation | $V_{\rm BAT}~{ m SR}$    | 2.1          | -     | 3.6  | V  |                                            |

| Sensor voltage range                                  | V <sub>LPCS</sub><br>CC  | 0            | -     | 1.2  | V  |                                            |

| Threshold step size                                   | $V_{\rm th}$ CC          | -            | 18.75 | _    | mV |                                            |

| Threshold trigger accuracy                            | $\Delta V_{\rm th}$ CC   | -            | -     | ±10  | %  | for $V_{\rm th}$ > 0.4 V                   |

| Conversion time                                       | t <sub>LPCC</sub> CC     | -            | -     | 250  | μS |                                            |

| Average current consumption over time                 | I <sub>LPCAC</sub><br>CC | -            | -     | 15   | μA | conversion<br>interval 10 ms <sup>1)</sup> |

| Current consumption during conversion                 | $I_{\rm LPCC}  {\rm CC}$ | -            | 150   | -    | μA | 1)                                         |

Table 33Low Power Analog Comparator Parameters

1) Single channel conversion, measuring  $V_{\text{BAT}}$  = 3.3 V, 8 cycles settling time

| Parameter                                                          | Symbol                  |                      | Values |                        | Unit | Note /<br>Test Condition                                 |  |

|--------------------------------------------------------------------|-------------------------|----------------------|--------|------------------------|------|----------------------------------------------------------|--|

|                                                                    |                         | Min.                 | Тур.   | Max.                   |      |                                                          |  |

| Input frequency                                                    | $f_{\rm OSC}$ SR        | -                    | 32.768 | -                      | kHz  |                                                          |  |

| Oscillator start-up<br>time <sup>1)2)3)</sup>                      | t <sub>oscs</sub><br>CC | -                    | -      | 5                      | S    |                                                          |  |

| Input voltage at<br>RTC_XTAL1                                      | $V_{\rm IX}$ SR         | -0.3                 | -      | V <sub>BAT</sub> + 0.3 | V    |                                                          |  |

| Input amplitude (peak-<br>to-peak) at<br>RTC_XTAL1 <sup>2)4)</sup> | $V_{PPX}SR$             | 0.4                  | -      | -                      | V    |                                                          |  |

| Input high voltage at<br>RTC_XTAL1 <sup>5)</sup>                   | $V_{\rm IHBX} {\rm SR}$ | $0.6 \times V_{BAT}$ | -      | V <sub>BAT</sub> + 0.3 | V    |                                                          |  |

| Input low voltage at<br>RTC_XTAL1 <sup>5)</sup>                    | $V_{\rm ILBX}{\rm SR}$  |                      | -      | $0.36 	imes V_{BAT}$   | V    |                                                          |  |

| Input Hysteresis for<br>RTC_XTAL1 <sup>5)6)</sup>                  | V <sub>HYSX</sub><br>CC | $0.1 	imes V_{BAT}$  |        | -                      | V    | $3.0 \text{ V} \le V_{\text{BAT}} < 3.6 \text{ V}$       |  |

|                                                                    |                         | $0.03 	imes V_{BAT}$ |        | -                      | V    | $V_{\rm BAT}$ < 3.0 V                                    |  |

| Input leakage current at RTC_XTAL1                                 | I <sub>ILX1</sub> CC    | -100                 | -      | 100                    | nA   | Oscillator power<br>down<br>$0 V \le V_{IX} \le V_{BAT}$ |  |

### Table 38 RTC\_XTAL Parameters

t<sub>OSCS</sub> is defined from the moment the oscillator is enabled by the user with SCU\_OSCULCTRL.MODE until the oscillations reach an amplitude at RTC\_XTAL1 of 400 mV.

The external oscillator circuitry must be optimized by the customer and checked for negative resistance and amplitude as recommended and specified by crystal suppliers.

- 3) For a reliable start of the oscillation in crystal mode it is required that  $V_{BAT} \ge 3.0$  V. A running oscillation is maintained across the full  $V_{BAT}$  voltage range.

- 4) If the shaper unit is enabled and not bypassed.

- 5) If the shaper unit is bypassed, dedicated DC-thresholds have to be met.

- 6) Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

## 3.3.5 Internal Clock Source Characteristics

### Fast Internal Clock Source

| Parameter         | Symbol                         |      | Values | 5    | Unit | Note /<br>Test Condition                                                            |  |

|-------------------|--------------------------------|------|--------|------|------|-------------------------------------------------------------------------------------|--|

|                   |                                | Min. | Тур.   | Max. |      |                                                                                     |  |

| Nominal frequency | $f_{\rm OFINC}$                | -    | 36.5   | _    | MHz  | not calibrated                                                                      |  |

|                   | CC                             | -    | 24     | _    | MHz  | calibrated                                                                          |  |

| Accuracy          | <i>∆f</i> <sub>OFI</sub><br>CC | -0.5 | -      | 0.5  | %    | automatic<br>calibration <sup>1)2)</sup>                                            |  |

|                   |                                | -15  | -      | 15   | %    | factory<br>calibration,<br>$V_{\text{DDP}} = 3.3 \text{ V}$                         |  |

|                   |                                | -25  | -      | 25   | %    | no calibration,<br>$V_{\text{DDP}}$ = 3.3 V                                         |  |

|                   |                                | -7   | -      | 7    | %    | Variation over<br>voltage range <sup>3)</sup><br>$3.13 V \le V_{DDP} \le$<br>3.63 V |  |

| Start-up time     | t <sub>OFIS</sub> CC           | -    | 50     | _    | μS   |                                                                                     |  |

## Table 45 Fast Internal Clock Parameters

1) Error in addition to the accuracy of the reference clock.

2) Automatic calibration compensates variations of the temperature and in the  $V_{\rm DDP}$  supply voltage.

3) Deviations from the nominal  $V_{\text{DDP}}$  voltage induce an additional error to the uncalibrated and/or factory calibrated oscillator frequency.

## 3.3.9 Peripheral Timing

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

- Note: Operating conditions apply.

## 3.3.9.1 Delta-Sigma Demodulator Digital Interface Timing

The following parameters are applicable for the digital interface of the Delta-Sigma Demodulator (DSD).

The data timing is relative to the active clock edge. Depending on the operation mode of the connected modulator that can be the rising and falling clock edge.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Symbol                |    | ,                          | Values |      | Unit | Note /                                |  |

|------------------------------------------------|-----------------------|----|----------------------------|--------|------|------|---------------------------------------|--|

|                                                |                       |    | Min.                       | Тур.   | Max. |      | Test Condition                        |  |

| MCLK period in master mode                     | <i>t</i> <sub>1</sub> | СС | 33.3                       | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{1}$ |  |

| MCLK high time in master mode                  | <i>t</i> <sub>2</sub> | СС | 9                          | -      | -    | ns   | $t_2 > t_{\text{PERIPH}}^{(1)}$       |  |

| MCLK low time in master mode                   | <i>t</i> <sub>3</sub> | СС | 9                          | -      | -    | ns   | $t_3 > t_{\text{PERIPH}}^{1)}$        |  |

| MCLK period in slave mode                      | <i>t</i> <sub>1</sub> | SR | 33.3                       | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{1}$ |  |

| MCLK high time in slave mode                   | <i>t</i> <sub>2</sub> | SR | t <sub>PERIPH</sub>        | -      | -    | ns   | 1)                                    |  |

| MCLK low time in slave mode                    | <i>t</i> <sub>3</sub> | SR | t <sub>PERIPH</sub>        | -      | -    | ns   | 1)                                    |  |

| DIN input setup time to the active clock edge  | <i>t</i> <sub>4</sub> | SR | $t_{\text{PERIPH}}$ + 4    | -      | -    | ns   | 1)                                    |  |

| DIN input hold time from the active clock edge | <i>t</i> <sub>5</sub> | SR | t <sub>PERIPH</sub><br>+ 3 | -      | -    | ns   | 1)                                    |  |

84

| Table 50 | DSD Interface Timing Parameters |

|----------|---------------------------------|

|----------|---------------------------------|

1)  $t_{\text{PERIPH}} = 1 / f_{\text{PERIPH}}$

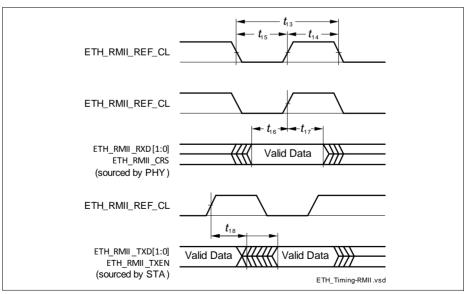

## 3.3.11.3 ETH RMII Parameters

In the following, the parameters of the RMII (Reduced Media Independent Interface) are described.

| Table 59         ETH RMII Signal Timing Parameters |

|----------------------------------------------------|

|----------------------------------------------------|

| Parameter                                      |                 | Symbol |      | Values |      |    | Note /                            |  |

|------------------------------------------------|-----------------|--------|------|--------|------|----|-----------------------------------|--|

|                                                |                 |        | Min. | Тур.   | Max. |    | Test Condit<br>ion                |  |

| ETH_RMII_REF_CL clock period                   | t <sub>13</sub> | SR     | 20   | -      | _    | ns | C <sub>L</sub> = 25 pF;<br>50 ppm |  |

| ETH_RMII_REF_CL clock high time                | t <sub>14</sub> | SR     | 7    | -      | 13   | ns | C <sub>L</sub> = 25 pF            |  |

| ETH_RMII_REF_CL clock low time                 | t <sub>15</sub> | SR     | 7    | -      | 13   | ns |                                   |  |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS setup time  | t <sub>16</sub> | SR     | 4    | _      | _    | ns |                                   |  |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS hold time   | t <sub>17</sub> | SR     | 2    | -      | -    | ns | -                                 |  |

| ETH_RMII_TXD[1:0],<br>ETH_RMII_TXEN data valid | t <sub>18</sub> | CC     | 4    | -      | 15   | ns |                                   |  |

Figure 41 ETH RMII Signal Timing

## Package and Reliability

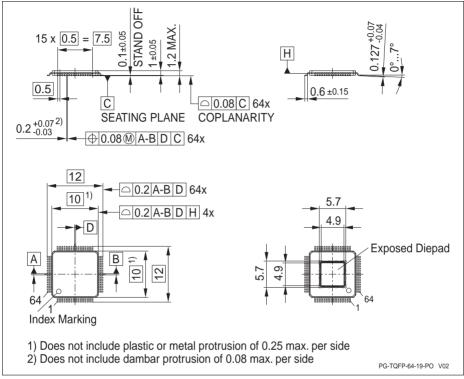

Figure 45 PG-TQFP-64-19 (Plastic Green Low Profile Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages