Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4402f100f256abxqma1 |

|----------------------------|-----------------------------------------------------------------------------------|

| Supplier Device Package    | PG-LQFP-100-11                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                              |

| Mounting Type              | Surface Mount                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Oscillator Type            | Internal                                                                          |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                             |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                     |

| RAM Size                   | 80K x 8                                                                           |

| EEPROM Size                | -                                                                                 |

| Program Memory Type        | FLASH                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Number of I/O              | 55                                                                                |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |

| Speed                      | 120MHz                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                |

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Product Status             | Discontinued at Digi-Key                                                          |

| Details                    |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 3.3.4    | Phase Locked Loop (PLL) Characteristics                | 77 |

|----------|--------------------------------------------------------|----|

| 3.3.5    | Internal Clock Source Characteristics                  | 78 |

| 3.3.6    | JTAG Interface Timing                                  | 80 |

| 3.3.7    | Serial Wire Debug Port (SW-DP) Timing                  | 82 |

| 3.3.8    | Embedded Trace Macro Cell (ETM) Timing                 | 83 |

| 3.3.9    | Peripheral Timing                                      |    |

| 3.3.9.1  | Delta-Sigma Demodulator Digital Interface Timing       | 84 |

| 3.3.9.2  | Synchronous Serial Interface (USIC SSC) Timing         | 85 |

| 3.3.9.3  | Inter-IC (IIC) Interface Timing                        | 88 |

| 3.3.9.4  | Inter-IC Sound (IIS) Interface Timing                  | 90 |

| 3.3.10   | USB Interface Characteristics                          |    |

| 3.3.11   | Ethernet Interface (ETH) Characteristics               | 93 |

| 3.3.11.1 | ETH Measurement Reference Points 9                     |    |

| 3.3.11.2 | ETH Management Signal Parameters (ETH_MDC, ETH_MDIO) 9 |    |

| 3.3.11.3 | ETH RMII Parameters                                    | 95 |

| 4        | Package and Reliability                                | 96 |

| 4.1      | Package Parameters                                     |    |

| 4.1.1    | Thermal Considerations                                 | 96 |

| 4.2      | Package Outlines                                       | 97 |

| 5        | Quality Declarations                                   | 02 |

## **Summary of Features**

## **On-Chip Memories**

- 16 KB on-chip boot ROM

- 16 KB on-chip high-speed program memory

- 32 KB on-chip high speed data memory

- 32 KB on-chip high-speed communication memory

- 512 KB on-chip Flash Memory with 4 KB instruction cache

## **Communication Peripherals**

- Ethernet MAC module capable of 10/100 Mbit/s transfer rates

- Universal Serial Bus, USB 2.0 host, Full-Speed OTG, with integrated PHY

- Controller Area Network interface (MultiCAN), Full-CAN/Basic-CAN with two nodes, 64 message objects (MO), data rate up to 1MBit/s

- Four Universal Serial Interface Channels (USIC), providing four serial channels, usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- LED and Touch-Sense Controller (LEDTS) for Human-Machine interface

## **Analog Frontend Peripherals**

- Four Analog-Digital Converters (VADC) of 12-bit resolution, 8 channels each, with input out-of-range comparators

- Delta Sigma Demodulator with four channels, digital input stage for A/D signal conversion

- Digital-Analog Converter (DAC) with two channels of 12-bit resolution

## **Industrial Control Peripherals**

- Two Capture/Compare Units 8 (CCU8) for motor control and power conversion

- Four Capture/Compare Units 4 (CCU4) for use as general purpose timers

- Four High Resoultion PWM (HRPWM) channels

- Two Position Interfaces (POSIF) for servo motor positioning

- Window Watchdog Timer (WDT) for safety sensitive applications

- Die Temperature Sensor (DTS)

- Real Time Clock module with alarm support

- System Control Unit (SCU) for system configuration and control

### Input/Output Lines

- Programmable port driver control module (PORTS)

- Individual bit addressability

- · Tri-stated in input mode

- · Push/pull or open drain output mode

- Boundary scan test support over JTAG interface

# **Summary of Features**

Table 4 Features of XMC4400 Device Types

| Derivative <sup>1)</sup> | ADC<br>Chan. | DSD<br>Chan. | DAC<br>Chan. | CCU4<br>Slice | CCU8<br>Slice | POSIF<br>Intf. | HRPWM<br>Intf. |

|--------------------------|--------------|--------------|--------------|---------------|---------------|----------------|----------------|

| XMC4400-F100x512         | 24           | 4            | 2            | 4 x 4         | 2 x 4         | 2              | 1              |

| XMC4400-F64x512          | 14           | 4            | 2            | 4 x 4         | 2 x 4         | 2              | 1              |

| XMC4400-F100x256         | 24           | 4            | 2            | 4 x 4         | 2 x 4         | 2              | 1              |

| XMC4400-F64x256          | 14           | 4            | 2            | 4 x 4         | 2 x 4         | 2              | 1              |

| XMC4402-F100x256         | 24           | 4            | 2            | 4 x 4         | 2 x 4         | 2              | 1              |

| XMC4402-F64x256          | 14           | 4            | 2            | 4 x 4         | 2 x 4         | 2              | 1              |

<sup>1)</sup> x is a placeholder for the supported temperature range.

## 1.5 Definition of Feature Variants

The XMC4400 types are offered with several memory sizes and number of available VADC channels. **Table 5** describes the location of the available Flash memory, **Table 6** describes the location of the available SRAMs, **Table 7** the available VADC channels.

Table 5 Flash Memory Ranges

| Total Flash Size | Cached Range                                       | <b>Uncached Range</b>                              |

|------------------|----------------------------------------------------|----------------------------------------------------|

| 256 Kbytes       | 0800 0000 <sub>H</sub> –<br>0803 FFFF <sub>H</sub> | 0C00 0000 <sub>H</sub> -<br>0C03 FFFF <sub>H</sub> |

| 512 Kbytes       | 0800 0000 <sub>H</sub> –<br>0807 FFFF <sub>H</sub> | 0C00 0000 <sub>H</sub> -<br>0C07 FFFF <sub>H</sub> |

Table 6 SRAM Memory Ranges

| Total SRAM Size | Program SRAM             | System Data SRAM         | Communication Data SRAM  |

|-----------------|--------------------------|--------------------------|--------------------------|

| 80 Kbytes       | 1FFF C000 <sub>H</sub> – | 2000 0000 <sub>H</sub> – | 2000 8000 <sub>H</sub> – |

|                 | 1FFF FFFF <sub>H</sub>   | 2000 7FFF <sub>H</sub>   | 2000 FFFF <sub>H</sub>   |

# **Summary of Features**

Table 7 ADC Channels<sup>1)</sup>

| Package     | VADC G0        | VADC G1               | VADC G2  | VADC G3  |

|-------------|----------------|-----------------------|----------|----------|

| PG-LQFP-100 | CH0CH7         | CH0CH7                | CH0CH3   | CH0CH3   |

| PG-LQFP-64  | CH0,<br>CH3CH7 | CH0, CH1,<br>CH3, CH6 | CH0, CH1 | CH2, CH3 |

Some pins in a package may be connected to more than one channel. For the detailed mapping see the Port I/O Function table.

# 1.6 Identification Registers

The identification registers allow software to identify the marking.

Table 8 XMC4400 Identification Registers

| Register Name | Value                  | Marking       |

|---------------|------------------------|---------------|

| SCU_IDCHIP    | 0004 4001 <sub>H</sub> | EES-AA, ES-AA |

| SCU_IDCHIP    | 0004 4002 <sub>H</sub> | ES-AB, AB     |

| SCU_IDCHIP    | 0004 4003 <sub>H</sub> | ВА            |

| JTAG IDCODE   | 101D C083 <sub>H</sub> | EES-AA, ES-AA |

| JTAG IDCODE   | 201D C083 <sub>H</sub> | ES-AB, AB     |

| JTAG IDCODE   | 301D C083 <sub>H</sub> | ВА            |

### **General Device Information**

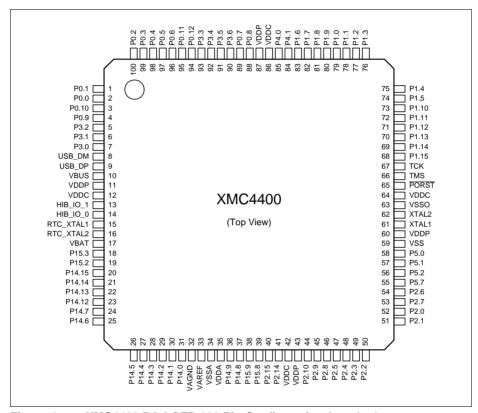

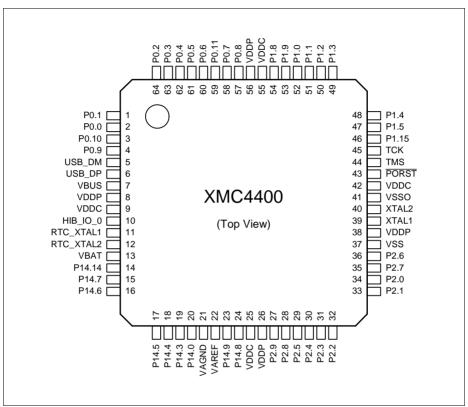

# 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the different packages.

Figure 4 XMC4400 PG-LQFP-100 Pin Configuration (top view)

### **General Device Information**

Figure 5 XMC4400 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

## 3.2 DC Parameters

# 3.2.1 Input/Output Pins

The digital input stage of the shared analog/digital input pins is identical to the input stage of the standard digital input/output pins.

The Pull-up on the PORST pin is identical to the Pull-up on the standard digital input/output pins.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 20 Standard Pad Parameters

| Parameter                                                | Symbol              | Va                               | alues | Unit | Note / Test Condition                  |

|----------------------------------------------------------|---------------------|----------------------------------|-------|------|----------------------------------------|

|                                                          |                     | Min.                             | Max.  |      |                                        |

| Pin capacitance (digital inputs/outputs)                 | $C_{IO}CC$          | _                                | 10    | pF   |                                        |

| Pull-down current                                        | $ I_{PDL} $         | 150                              | _     | μΑ   | $^{1)}V_{IN} \geq 0.6 	imes V_{DDP}$   |

|                                                          | CC                  | _                                | 10    | μΑ   | $^{2)}V_{IN} \leq 0.36 \times V_{DDP}$ |

| Pull-Up current                                          | $ I_{\rm PUH} $ SR  | _                                | 10    | μΑ   | $^{2)}V_{IN} \geq 0.6 	imes V_{DDP}$   |

|                                                          |                     | 100                              | _     | μΑ   | $^{1)}V_{IN} \leq 0.36 \times V_{DDP}$ |

| Input Hysteresis for pads of all A classes <sup>3)</sup> | HYSA<br>SR          | 0.1 ×<br><i>V</i> <sub>DDP</sub> | _     | V    |                                        |

| PORST spike filter always blocked pulse duration         | t <sub>SF1</sub> CC | _                                | 10    | ns   |                                        |

| PORST spike filter pass-through pulse duration           | t <sub>SF2</sub> CC | 100                              | -     | ns   |                                        |

| PORST pull-down current                                  | $ I_{PPD} $ CC      | 13                               | _     | mA   | V <sub>IN</sub> = 1.0 V                |

Current required to override the pull device with the opposite logic level ("force current").

With active pull device, at load currents between force and keep current the input state is undefined.

Load current at which the pull device still maintains the valid logic level ("keep current").

With active pull device, at load currents between force and keep current the input state is undefined.

<sup>3)</sup> Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

#### **Conversion Time**

Table 26

Conversion Time (Operating Conditions apply)

| Parameter       | Syn     | nbol | Values                                                         | Unit | Note                                                                                                         |

|-----------------|---------|------|----------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------|

| Conversion time | $t_{C}$ |      | $2 \times T_{ADC}$ + $(2 + N + STC + PC + DM) \times T_{ADCI}$ |      | N = 8, 10, 12 for<br>N-bit conversion<br>$T_{\rm ADC} = 1/f_{\rm PERIPH}$<br>$T_{\rm ADCI} = 1/f_{\rm ADCI}$ |

- STC defines additional clock cycles to extend the sample time

- PC adds two cycles if post-calibration is enabled

- DM adds one cycle for an extended conversion time of the MSB

## **Conversion Time Examples**

System assumptions:

$$f_{ADC}$$

= 120 MHz i.e.  $t_{ADC}$  = 8.33 ns, DIVA = 3,  $f_{ADCI}$  = 30 MHz i.e.  $t_{ADCI}$  = 33.3 ns

According to the given formulas the following minimum conversion times can be achieved (STC = 0, DM = 0):

12-bit post-calibrated conversion (PC = 2):

$$t_{\text{CN12C}} = (2 + 12 + 2) \times t_{\text{ADCI}} + 2 \times t_{\text{ADC}} = 16 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 550 \text{ ns}$$

12-bit uncalibrated conversion:

$$t_{\text{CN12}}$$

= (2 + 12) ×  $t_{\text{ADCI}}$  + 2 ×  $t_{\text{ADC}}$  = 14 × 33.3 ns + 2 × 8.33 ns = 483 ns

10-bit uncalibrated conversion:

$$t_{\text{CN10}} = (2 + 10) \times t_{\text{ADCI}} + 2 \times t_{\text{ADC}} = 12 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 417 \text{ ns}$$

8-bit uncalibrated:

$$t_{\text{CN8}} = (2 + 8) \times t_{\text{ADCI}} + 2 \times t_{\text{ADC}} = 10 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 350 \text{ ns}$$

Table 27 DAC Parameters (Operating Conditions apply) (cont'd)

| Parameter                       | Symbo                | Symbol          |      | Values |      |      | Note /                                                  |  |

|---------------------------------|----------------------|-----------------|------|--------|------|------|---------------------------------------------------------|--|

|                                 |                      |                 | Min. | Тур.   | Max. |      | Test Condition                                          |  |

| Offset error                    | $ED_{OFF}$           | CC              |      | ±20    |      | mV   |                                                         |  |

| Gain error                      | $ED_{G\_IN}$         | CC              | -5   | 0      | 5    | %    |                                                         |  |

| Startup time                    | t <sub>STARTU</sub>  | <sub>P</sub> CC | _    | 15     | 30   | μS   | time from output<br>enabling till code<br>valid ±16 LSB |  |

| 3dB Bandwidth of Output Buffer  | $f_{C1}$             | CC              | 2.5  | 5      | _    | MHz  | verified by design                                      |  |

| Output sourcing current         | I <sub>OUT_SO</sub>  | URCE            | _    | -30    | _    | mA   |                                                         |  |

| Output sinking current          | I <sub>OUT_SIN</sub> | ١K              | _    | 0.6    | _    | mA   |                                                         |  |

| Output resistance               | $R_{OUT}$            | CC              | -    | 50     | -    | Ohm  |                                                         |  |

| Load resistance                 | $R_{L}$              | SR              | 5    | -      | -    | kOhm |                                                         |  |

| Load capacitance                | $C_{L}$              | SR              | -    | _      | 50   | pF   |                                                         |  |

| Signal-to-Noise<br>Ratio        | SNR                  | СС              | _    | 70     | -    | dB   | examination<br>bandwidth < 25 kHz                       |  |

| Total Harmonic<br>Distortion    | THD                  | CC              | _    | 70     | _    | dB   | examination<br>bandwidth < 25 kHz                       |  |

| Power Supply<br>Rejection Ratio | PSRR                 | CC              | _    | 56     | _    | dB   | to $V_{\rm DDA}$ verified by design                     |  |

<sup>1)</sup> According to best straight line method.

### **Conversion Calculation**

Unsigned:

$\mathsf{DACxDATA} = 4095 \times (V_\mathsf{OUT} - V_\mathsf{OUT\_MIN}) \, / \, (V_\mathsf{OUT\_MAX} - V_\mathsf{OUT\_MIN})$

Signed:

$\mathsf{DACxDATA} = 4095 \times (V_\mathsf{OUT} - V_\mathsf{OUT\_MIN}) \, / \, (V_\mathsf{OUT\_MAX} - V_\mathsf{OUT\_MIN}) \, - \, 2048$

# 3.2.4 Out-of-Range Comparator (ORC)

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{\text{AIN}}$ ) above the analog reference<sup>1)</sup> ( $V_{\text{AREF}}$ ) on selected input pins (GxORCy) and generates a service request trigger (GxORCOUTy).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The parameters in Table 28 apply for the maximum reference voltage  $V_{\rm AREF} = V_{\rm DDA} + 50$  mV.

Table 28

ORC Parameters (Operating Conditions apply)

| Parameter                 | Symbol        |    |      | Values | i                | Unit | Note / Test Condition             |

|---------------------------|---------------|----|------|--------|------------------|------|-----------------------------------|

|                           |               |    | Min. | Тур.   | Max.             |      |                                   |

| DC Switching Level        | $V_{ODC}$     | CC | 100  | 125    | 200              | mV   | $V_{AIN} \geq V_{AREF} + V_{ODC}$ |

| Hysteresis                | $V_{OHYS}$    | CC | 50   | _      | $V_{\text{ODC}}$ | mV   |                                   |

| Detection Delay of a      | $t_{ODD}$     | CC | 55   | _      | 450              | ns   | $V_{AIN} \geq V_{AREF}$ + 200 mV  |

| persistent<br>Overvoltage |               |    | 45   | -      | 105              | ns   | $V_{AIN} \geq V_{AREF}$ + 400 mV  |

| Always detected           | $t_{OPDD}$    | CC | 440  | _      | -                | ns   | $V_{AIN} \geq V_{AREF}$ + 200 mV  |

| Overvoltage Pulse         |               |    | 90   | _      | -                | ns   | $V_{AIN} \geq V_{AREF}$ + 400 mV  |

| Never detected            | $t_{OPDN}$    | CC | _    | _      | 49               | ns   | $V_{AIN} \geq V_{AREF}$ + 200 mV  |

| Overvoltage Pulse         |               |    | _    | _      | 30               | ns   | $V_{AIN} \geq V_{AREF}$ + 400 mV  |

| Release Delay             | $t_{ORD}$     | CC | 65   | _      | 105              | ns   | $V_{AIN} \leq V_{AREF}$           |

| Enable Delay              | $t_{\sf OED}$ | CC | _    | 100    | 200              | ns   |                                   |

<sup>1)</sup> Always the standard VADC reference, alternate references do not apply to the ORC.

# 3.2.5 High Resolution PWM (HRPWM)

The following chapters describe the operating conditions, characteristics and timing requirements, for all the components inside the HRPWM module. Each description is given for just one sub unit, e.g., one CSG or one HRC.

All the timing information is related to the module clock,  $f_{\text{hrown}}$ .

Note: These parameters are not subject to production test, but verified by design and/or characterization.

#### 3.2.5.1 HRC characteristics

Table 29 summarizes the characteristics of the HRC units.

Table 29

HRC characteristics (Operating Conditions apply)

| Parameter                                 | Symbol                | Values |      |      | Values Unit |                |  | Unit | Note / |

|-------------------------------------------|-----------------------|--------|------|------|-------------|----------------|--|------|--------|

|                                           |                       | Min.   | Тур. | Max. |             | Test Condition |  |      |        |

| High resolution step size <sup>1)2)</sup> | t <sub>HRS</sub> CC   | _      | 150  | _    | ps          |                |  |      |        |

| Startup time (after reset release)        | t <sub>start</sub> CC | _      | _    | 2    | μS          |                |  |      |        |

<sup>1)</sup> The step size for clock frequencies equal to 180, 120 and 80 MHz is 150 ps.

## 3.2.5.2 CMP and 10-bit DAC characteristics

The **Table 30** summarizes the characteristics of the CSG unit.

The specified characteristics require that the setup of the HRPWM follows the initialization sequence as documented in the Reference Manual.

Table 30 CMP and 10-bit DAC characteristics (Operating Conditions apply)

| Parameter                     | Symbol    |      | Values | S    | Unit | Note /                                  |

|-------------------------------|-----------|------|--------|------|------|-----------------------------------------|

|                               |           | Min. | Тур.   | Max. |      | Test Condition                          |

| DAC Resolution                | RES<br>CC |      | 10     |      | bits |                                         |

| DAC differential nonlinearity | DNL<br>CC | -1   | _      | 1.5  | LSB  | Monotonic<br>behavior,<br>See Figure 18 |

| DAC integral nonlinearity     | INL CC    | -3   | -      | 3    | LSB  | See Figure 18                           |

<sup>2)</sup> The step size for clock frequencies different from 180, 120 and 80 MHz but within the range from 180 to 64 MHz can be between 118 to 180 ps (fixed over process and operating conditions)

Table 36 USB OTG Data Line (USB\_DP, USB\_DM) Parameters (Operating Conditions apply)

| Parameter                                           | Symbol              |       | Values | S     | Unit | Note /                         |

|-----------------------------------------------------|---------------------|-------|--------|-------|------|--------------------------------|

|                                                     |                     | Min.  | Тур.   | Max.  |      | Test Condition                 |

| Input low voltage                                   | $V_{IL}$ SR         | _     | _      | 0.8   | V    |                                |

| Input high voltage (driven)                         | V <sub>IH</sub> SR  | 2.0   | _      | -     | V    |                                |

| Input high voltage (floating) 1)                    | $V_{IHZ}$ SR        | 2.7   | _      | 3.6   | V    |                                |

| Differential input sensitivity                      | $V_{DIS}$ CC        | 0.2   | _      | _     | V    |                                |

| Differential common mode range                      | $V_{CM}$ CC         | 0.8   | _      | 2.5   | V    |                                |

| Output low voltage                                  | $V_{OL}$ CC         | 0.0   | _      | 0.3   | V    | 1.5 kOhm pull-<br>up to 3.6 V  |

| Output high voltage                                 | $V_{OH}$ CC         | 2.8   | _      | 3.6   | V    | 15 kOhm pull-<br>down to 0 V   |

| DP pull-up resistor (idle bus)                      | $R_{PUI}$ CC        | 900   | _      | 1 575 | Ohm  |                                |

| DP pull-up resistor<br>(upstream port<br>receiving) | R <sub>PUA</sub> CC | 1 425 | _      | 3 090 | Ohm  |                                |

| DP, DM pull-down resistor                           | R <sub>PD</sub> CC  | 14.25 | _      | 24.8  | kOhm |                                |

| Input impedance DP,<br>DM                           | $Z_{INP}$ CC        | 300   | _      | -     | kOhm | $0 \ V \le V_{IN} \le V_{DDP}$ |

| Driver output resistance DP, DM                     | $Z_{DRV}$ CC        | 28    | _      | 44    | Ohm  |                                |

<sup>1)</sup> Measured at A-connector with 1.5 kOhm ± 5% to 3.3 V ± 0.3 V connected to USB\_DP or USB\_DM and at B-connector with 15 kOhm ± 5% to ground connected to USB\_DP and USB\_DM.

## **Peripheral Idle Currents**

#### Test conditions:

- f<sub>svs</sub> and derived clocks at 120 MHz

- $V_{\text{DDP}} = 3.3 \text{ V}, T_{\text{a}} = 25 \text{ °C}$

- all peripherals are held in reset (see the PRSTAT registers in the Reset Control Unit of the SCU)

- the peripheral clocks are disabled (see CGATSTAT registers in the Clock Control Unit of the SCU

- no I/O activity

- the given values are a result of differential measurements with asserted and deasserted peripheral reset and enabled clock of the peripheral under test

The tested peripheral is left in the state after the peripheral reset is deasserted, no further initialisation or configuration is done. E.g. no timer is running in the CCUs, no communication active in the USICs, etc.

Table 40 Peripheral Idle Currents

| Parameter                           | Symbol              |      | Values |      | Unit | Note /         |

|-------------------------------------|---------------------|------|--------|------|------|----------------|

|                                     |                     | Min. | Тур.   | Max. |      | Test Condition |

| PORTS ETH USB FCE WDT POSIFx        | I <sub>PER</sub> CC | -    | ≤ 0.3  | -    | mA   |                |

| MultiCAN ERU LEDTSCU0 CCU4x CCU8x   |                     | _    | ≤ 1.0  | -    |      |                |

| DAC (digital) <sup>1)</sup>         |                     | _    | 1.3    | _    |      |                |

| USICx                               |                     | _    | 3.0    | _    |      |                |

| DSD<br>VADC (digital) <sup>1)</sup> |                     | -    | 4.5    | -    |      |                |

| DMAx                                |                     | _    | 6.0    | _    |      |                |

The current consumption of the analog components are given in the dedicated Data Sheet sections of the respective peripheral.

Table 41 Flash Memory Parameters

| Parameter                                                                 | Symbol               |       | Values | 3    | Unit   | Note /<br>Test Condition                                                              |

|---------------------------------------------------------------------------|----------------------|-------|--------|------|--------|---------------------------------------------------------------------------------------|

|                                                                           |                      | Min.  | Тур.   | Max. |        |                                                                                       |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC  | 20    | -      | -    | years  | Max. 4<br>erase/program<br>cycles per UCB                                             |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub> CC | 10000 | _      | -    | cycles | BA-marking<br>devices only!<br>Cycling<br>distributed over<br>life time <sup>5)</sup> |

In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

<sup>2)</sup> The following formula applies to the wait state configuration: FCON.WSPFLASH  $\times$  (1 /  $f_{CPU}$ )  $\geq t_a$ .

<sup>3)</sup> Storage and inactive time included.

<sup>4)</sup> Values given are valid for an average weighted junction temperature of  $T_J = 110$  °C.

Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see

the Reference Manual.

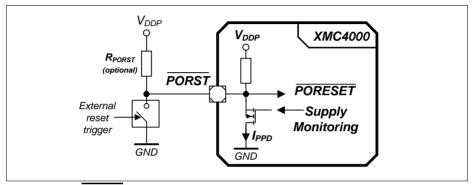

# 3.3.2 Power-Up and Supply Monitoring

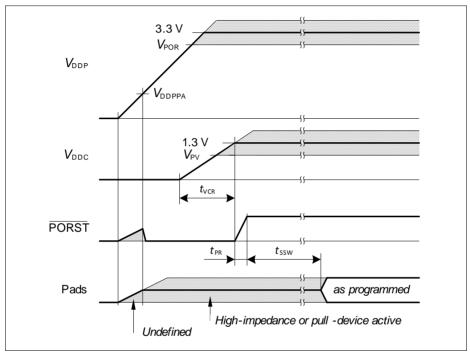

$\overline{ extsf{PORST}}$  is always asserted when  $V_{ extsf{DDP}}$  and/or  $V_{ extsf{DDC}}$  violate the respective thresholds.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Figure 26 PORST Circuit

Table 42 Supply Monitoring Parameters

| Parameter                                                       | Symbol              |                    | Value | s                  | Unit | Note /<br>Test Condition                                                                  |

|-----------------------------------------------------------------|---------------------|--------------------|-------|--------------------|------|-------------------------------------------------------------------------------------------|

|                                                                 |                     | Min.               | Тур.  | Max.               |      |                                                                                           |

| Digital supply voltage reset threshold                          | $V_{POR}$ CC        | 2.79 <sup>1)</sup> | -     | 3.05 <sup>2)</sup> | V    | 3)                                                                                        |

| Core supply voltage reset threshold                             | $V_{\sf PV}$ CC     | _                  | -     | 1.17               | V    |                                                                                           |

| $V_{ m DDP}$ voltage to ensure defined pad states               | $V_{DDPPA}$ CC      | _                  | 1.0   | -                  | V    |                                                                                           |

| PORST rise time                                                 | $t_{PR}$ SR         | _                  | _     | 2                  | μS   |                                                                                           |

| Startup time from power-on reset with code execution from Flash | t <sub>SSW</sub> CC | -                  | 2.5   | 3.5                | ms   | Time to the first user code instruction                                                   |

| $\overline{V_{	extsf{DDC}}}$ ramp up time                       | t <sub>VCR</sub> CC | _                  | 550   | _                  | μѕ   | Ramp up after power-on or after a reset triggered by a violation of $V_{POR}$ or $V_{PV}$ |

<sup>1)</sup> Minimum threshold for reset assertion.

- 2) Maximum threshold for reset deassertion.

- 3) The  $V_{\text{DDP}}$  monitoring has a typical hysteresis of  $V_{\text{PORHYS}}$  = 180 mV.

Figure 27 Power-Up Behavior

# 3.3.3 Power Sequencing

While starting up and shutting down as well as when switching power modes of the system it is important to limit the current load steps. A typical cause for such load steps is changing the CPU frequency  $f_{\rm CPU}$ . Load steps exceeding the below defined values may cause a power on reset triggered by the supply monitor.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

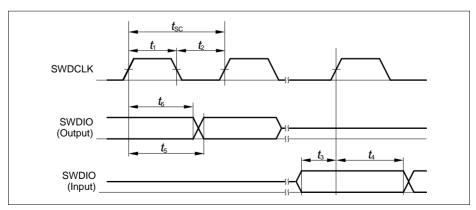

# 3.3.7 Serial Wire Debug Port (SW-DP) Timing

The following parameters are applicable for communication through the SW-DP interface.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Note: Operating conditions apply.

Table 48

SWD Interface Timing Parameters (Operating Conditions apply)

|                                                |                       |    | -      | •    |        |      |                        |

|------------------------------------------------|-----------------------|----|--------|------|--------|------|------------------------|

| Parameter                                      | Symbol                |    | Values |      |        | Unit | Note /                 |

|                                                |                       |    | Min.   | Тур. | Max.   |      | Test Condition         |

| SWDCLK clock period                            | $t_{SC}$              | SR | 25     | _    | _      | ns   | C <sub>L</sub> = 30 pF |

|                                                |                       |    | 40     | _    | _      | ns   | C <sub>L</sub> = 50 pF |

| SWDCLK high time                               | $t_1$                 | SR | 10     | _    | 500000 | ns   |                        |

| SWDCLK low time                                | $t_2$                 | SR | 10     | _    | 500000 | ns   |                        |

| SWDIO input setup to SWDCLK rising edge        | <i>t</i> <sub>3</sub> | SR | 6      | -    | _      | ns   |                        |

| SWDIO input hold after SWDCLK rising edge      | <i>t</i> <sub>4</sub> | SR | 6      | -    | _      | ns   |                        |

| SWDIO output valid time                        | $t_5$                 | CC | _      | _    | 17     | ns   | C <sub>L</sub> = 50 pF |

| after SWDCLK rising edge                       |                       |    | _      | _    | 13     | ns   | C <sub>L</sub> = 30 pF |

| SWDIO output hold time from SWDCLK rising edge | <i>t</i> <sub>6</sub> | CC | 3      | -    | _      | ns   |                        |

Figure 30 SWD Timing

Subject to Agreement on the Use of Product Information

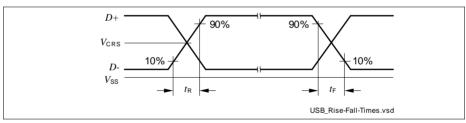

## 3.3.10 USB Interface Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification and the OTG Specification Rev. 1.3. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

**Table 57** USB Timing Parameters (operating conditions apply)

| Parameter               | Symbol                |    | Values |      |        | Unit | Note /                 |

|-------------------------|-----------------------|----|--------|------|--------|------|------------------------|

|                         |                       |    | Min.   | Тур. | Max.   |      | Test Condition         |

| Rise time               | $t_{R}$               | CC | 4      | _    | 20     | ns   | C <sub>L</sub> = 50 pF |

| Fall time               | $t_{F}$               | CC | 4      | _    | 20     | ns   | C <sub>L</sub> = 50 pF |

| Rise/Fall time matching | $t_{\rm R}/t_{\rm F}$ | CC | 90     | -    | 111.11 | %    | C <sub>L</sub> = 50 pF |

| Crossover voltage       | $V_{CRS}$             | CC | 1.3    | _    | 2.0    | V    | C <sub>L</sub> = 50 pF |

Figure 38 USB Signal Timing

# Package and Reliability

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\rm \Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IOSYAT}) \times R_{\Theta IA}$

The internal power consumption is defined as

$P_{\mathsf{INT}} = V_{\mathsf{DDP}} \times I_{\mathsf{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} - V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\mathsf{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- · Reduce the system frequency

- · Reduce the number of output pins

- · Reduce the load on active output drivers

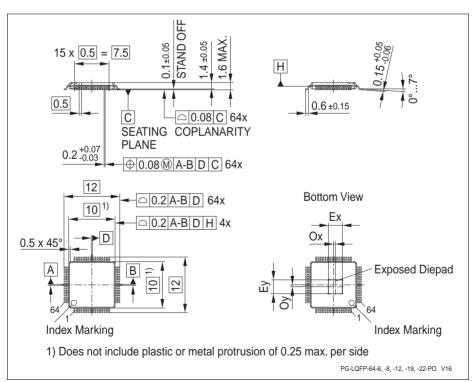

# 4.2 Package Outlines

The availability of different packages for different devices types is listed in **Table 1**, specific packages for different device markings are listed in **Table 2**.

The exposed die pad dimensions are listed in Table 60.

Table 61 Differences PG-LQFP-100-11 to PG-LQFP-100-24

| Change                                                | PG-LQFP-100-11                            | PG-LQFP-100-25                               |

|-------------------------------------------------------|-------------------------------------------|----------------------------------------------|

| Thermal Resistance Junction Ambient $(R_{\Theta JA})$ | 20.5 K/W                                  | 20.0 K/W                                     |

| Lead Width                                            |                                           | 0.2 <sup>+0.07</sup> <sub>-0.03</sub> mm     |

| Lead Thickness                                        | 0.15 <sup>+0.05</sup> <sub>-0.06</sub> mm | 0.127 <sup>+0.073</sup> <sub>-0.037</sub> mm |

| Exposed Die Pad outer dimensions                      | 7.0 mm × 7.0 mm                           | 7.0 mm × 7.0 mm                              |

| Exposed Die Pad U-<br>Groove inner dimensions         | n.a.                                      | 6.2 mm × 6.2 mm                              |

## Package and Reliability

Table 62 Differences PG-LQFP-64-19 to PG-TQFP-64-19

| Change                                                | PG-LQFP-64-19                             | PG-TQFP-64-19                              |

|-------------------------------------------------------|-------------------------------------------|--------------------------------------------|

| Thermal Resistance Junction Ambient $(R_{\Theta JA})$ | 30.0 K/W                                  | 22.5 K/W                                   |

| Package thickness                                     | 1.4 <sup>±0.05</sup> mm                   | 1.0 <sup>±0.05</sup> mm                    |

|                                                       | 1.6 mm MAX                                | 1.2 mm MAX                                 |

| Lead Width                                            | 0.22 <sup>±0.05</sup> mm                  | 0.2 <sup>+0.07</sup> <sub>-0.03</sub> mm   |

| Lead Thickness                                        | 0.15 <sup>+0.05</sup> <sub>-0.06</sub> mm | 0.127 <sup>+0.07</sup> <sub>-0.04</sub> mm |

| Exposed Die Pad outer dimensions                      | 5.8 mm × 5.8 mm                           | 5.7 mm × 5.7 mm                            |

| Exposed Die Pad U-<br>Groove inner dimensions         | n.a.                                      | 4.9 mm × 4.9 mm                            |

Figure 44 PG-LQFP-64-19 (Plastic Green Low Profile Quad Flat Package)