Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessorARM® Cortex®-M4Core Size32-Bit Single-CoreSpeed120MHzConnectivityCANbus, I²C, LINbus, SPI, UART/USART, USBConnectivityCANbus, I²C, LED, POR, PWM, WDTNumber of I/O55Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-ARAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSurper Converters100-LQFP Exposed Pad | Details                    |                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed120MHzConnectivityCANbus, I²C, LINbus, SPI, UART/USART, USBPeripheralsDMA, I²S, LED, POR, PWM, WDTNumber of I/O55Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bDoperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSurface NamePG-LQFP-100-25                                                            | Product Status             | Active                                                                            |

| Speed120MHzConnectivityCANbus, I²C, LINbus, SPI, UART/USART, USBPeripheralsDMA, I²S, LED, POR, PWM, WDTNumber of I/O55Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bDocillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                       | Core Processor             | ARM® Cortex®-M4                                                                   |

| ConnectivityCANbus, I°C, LINbus, SPI, UART/USART, USBPeripheralsDMA, I°S, LED, POR, PWM, WDTNumber of I/O55Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadConverter PackagePG-LQFP-100-25                                                                               | Core Size                  | 32-Bit Single-Core                                                                |

| PeripheralsDMA, I2S, LED, POR, PWM, WDTNumber of I/O55Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bDoccillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                      | Speed                      | 120MHz                                                                            |

| Number of I/O55Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                                                              | Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                            |

| Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Package / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                                                                                                       | Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                         |

| Program Memory TypeFLASHEEPROM Size-RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                                                                                                                | Number of I/O              | 55                                                                                |

| EEPROM Size-RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bData ConvertersA/D 24x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                                                                                                    | Program Memory Size        | 256КВ (256К х 8)                                                                  |

| RAM Size80K x 8Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bDscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                                                                                                                                                    | Program Memory Type        | FLASH                                                                             |

| Voltage - Supply (Vcc/Vdd)3.13V ~ 3.63VData ConvertersA/D 24x12b; D/A 2x12bDoscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                                                                                                                                                                  | EEPROM Size                | -                                                                                 |

| Data ConvertersA/D 24x12b; D/A 2x12bDscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-25                                                                                                                                                                                                                                                                                          | RAM Size                   | 80K x 8                                                                           |

| Dscillator Type     Internal       Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     100-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-100-25                                                                                                                                                                                                                                                                         | Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                     |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     100-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-100-25                                                                                                                                                                                                                                                                                                            | Data Converters            | A/D 24x12b; D/A 2x12b                                                             |

| Mounting Type     Surface Mount       Package / Case     100-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-100-25                                                                                                                                                                                                                                                                                                                                                               | Oscillator Type            | Internal                                                                          |

| Package / Case 100-LQFP Exposed Pad Supplier Device Package PG-LQFP-100-25                                                                                                                                                                                                                                                                                                                                                                                                                   | Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Supplier Device Package PG-LQFP-100-25                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Mounting Type              | Surface Mount                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Package / Case             | 100-LQFP Exposed Pad                                                              |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xmc4402f100k256baxqma1                                                                                                                                                                                                                                                                                                                                                                                               | Supplier Device Package    | PG-LQFP-100-25                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4402f100k256baxqma1 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### XMC4400 Data Sheet

Revision History: V1.2 2015-12

| IVE AISIOII | Thistory. V1.2 2013-12                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous    |                                                                                                                                                                  |

| V1.1 2014   |                                                                                                                                                                  |

| V1.0 2013   |                                                                                                                                                                  |

| V0.6 2012   |                                                                                                                                                                  |

| Page        | Subjects                                                                                                                                                         |

| 12          | Added a section listing the packages of the different markings.                                                                                                  |

| 14          | Added BA marking variant.                                                                                                                                        |

| 37          | Added footnote explaining minimum $V_{\rm BAT}$ requirements to start the hibernate domain and/or oscillation of a crystal on RTC_XTAL.                          |

| 38          | Changed pull device definition to System Requirement (SR) to reflect that the specified currents are defined by the characteristics of the external load/driver. |

| 38          | Added information that PORST Pull-up is identical to the pull-up on standard I/O pins.                                                                           |

| 45          | Updated $C_{\text{AINSW}}$ , $C_{\text{AINTOT}}$ and $R_{\text{AIN}}$ parameters with improved values.                                                           |

| 59          | Added footnote on test configuration for LPAC measurement.                                                                                                       |

| 61          | Corrected parameter name of of USB pull device (upstream port receiving) definition according to USB standard (referenced to DM instead of DP)                   |

| 66          | Relaxed RTC_XTAL $V_{\rm PPX}$ parameter value and changed it to a system requirement.                                                                           |

| 70          | Added footnote on current consumption by enabling of $f_{CCU}$ .                                                                                                 |

| 71          | Added Flash endurance parameter for 64 Kbytes Physical Sector PS4 $N_{\rm EPS4}$ for devices with BA marking.                                                    |

| many        | Added PG-TQFP-64-19 and PG-LQFP-100-25 package information.                                                                                                      |

| 97, 100     | Added tables describing the differences between PG-LQFP-100-11 to PG-LQFP-100-25 as well as PG-LQFP-64-19 to PG-TQFP-64-19 packages.                             |

| 102         | Updated to JEDEC standard J-STD-020D for the moisture sensitivity level and added solder temperature parameter according to the same standard.                   |

| -           |                                                                                                                                                                  |

## Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG. ARM<sup>®</sup>, ARM Powered<sup>®</sup>, Cortex<sup>®</sup>, Thumb<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

#### Summary of Features

## **On-Chip Memories**

- 16 KB on-chip boot ROM

- 16 KB on-chip high-speed program memory

- 32 KB on-chip high speed data memory

- 32 KB on-chip high-speed communication memory

- 512 KB on-chip Flash Memory with 4 KB instruction cache

## **Communication Peripherals**

- Ethernet MAC module capable of 10/100 Mbit/s transfer rates

- Universal Serial Bus, USB 2.0 host, Full-Speed OTG, with integrated PHY

- Controller Area Network interface (MultiCAN), Full-CAN/Basic-CAN with two nodes, 64 message objects (MO), data rate up to 1MBit/s

- Four Universal Serial Interface Channels (USIC), providing four serial channels, usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- LED and Touch-Sense Controller (LEDTS) for Human-Machine interface

## **Analog Frontend Peripherals**

- Four Analog-Digital Converters (VADC) of 12-bit resolution, 8 channels each, with input out-of-range comparators

- Delta Sigma Demodulator with four channels, digital input stage for A/D signal conversion

- Digital-Analog Converter (DAC) with two channels of 12-bit resolution

## **Industrial Control Peripherals**

- Two Capture/Compare Units 8 (CCU8) for motor control and power conversion

- Four Capture/Compare Units 4 (CCU4) for use as general purpose timers

- Four High Resoultion PWM (HRPWM) channels

- Two Position Interfaces (POSIF) for servo motor positioning

- Window Watchdog Timer (WDT) for safety sensitive applications

- Die Temperature Sensor (DTS)

- · Real Time Clock module with alarm support

- System Control Unit (SCU) for system configuration and control

## Input/Output Lines

- Programmable port driver control module (PORTS)

- Individual bit addressability

- Tri-stated in input mode

- Push/pull or open drain output mode

- Boundary scan test support over JTAG interface

#### **Summary of Features**

# **On-Chip Debug Support**

- Full support for debug features: 8 breakpoints, CoreSight, trace

- Various interfaces: ARM-JTAG, SWD, single wire trace

# 1.1 Ordering Information

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. The code "XMC4<DDD>-<Z><PPP><T><FFFF>" identifies:

- <DDD> the derivatives function set

- <Z> the package variant

- E: LFBGA

- F: LQFP

- Q: VQFN

- <PPP> package pin count

- <T> the temperature range:

- F: -40°C to 85°C

- K: -40°C to 125°C

- <FFFF> the Flash memory size.

For ordering codes for the XMC4400 please contact your sales representative or local distributor.

This document describes several derivatives of the XMC4400 series, some descriptions may not apply to a specific product. Please see **Table 1**.

For simplicity the term XMC4400 is used for all derivatives throughout this document.

## 1.2 Device Types

These device types are available and can be ordered through Infineon's direct and/or distribution channels.

| Derivative <sup>1)</sup> | Package                  | Flash Kbytes | SRAM<br>Kbytes |  |  |  |  |  |

|--------------------------|--------------------------|--------------|----------------|--|--|--|--|--|

| XMC4400-F100x512         | PG-LQFP-100              | 512          | 80             |  |  |  |  |  |

| XMC4400-F64x512          | PG-yQFP-64 <sup>2)</sup> | 512          | 80             |  |  |  |  |  |

| XMC4400-F100x256         | PG-LQFP-100              | 256          | 80             |  |  |  |  |  |

| XMC4400-F64x256          | PG-yQFP-64 <sup>2)</sup> | 256          | 80             |  |  |  |  |  |

| XMC4402-F100x256         | PG-LQFP-100              | 256          | 80             |  |  |  |  |  |

| XMC4402-F64x256          | PG-yQFP-64 <sup>2)</sup> | 256          | 80             |  |  |  |  |  |

|                          |                          |              |                |  |  |  |  |  |

#### Table 1 Synopsis of XMC4400 Device Types

1) x is a placeholder for the supported temperature range.

2) y is a placeholder for the QFP package variant, LQFP or TQFP depending on the stepping, see Section 1.3.

#### **Summary of Features**

## 1.3 Package Variants

Different markings of the XMC4400 use different package variants. Details of those packages are given in the **Package Parameters** section of the Data Sheet.

### Table 2 XMC4400 Package Variants

| Package Variant | Marking                  | Package        |

|-----------------|--------------------------|----------------|

| XMC4400-F100    | EES-AA, ES-AA, ES-AB, AB | PG-LQFP-100-11 |

| XMC4400-F64     |                          | PG-LQFP-64-19  |

| XMC4400-F100    | BA                       | PG-LQFP-100-25 |

| XMC4400-F64     |                          | PG-TQFP-64-19  |

## 1.4 Device Type Features

The following table lists the available features per device type.

| Derivative <sup>1)</sup> | LEDTS Intf. | ETH<br>Intf. | USB<br>Intf. | USIC<br>Chan. | MultiCAN<br>Nodes, MO |

|--------------------------|-------------|--------------|--------------|---------------|-----------------------|

| XMC4400-F100x512         | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4400-F64x512          | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4400-F100x256         | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4400-F64x256          | 1           | RMII         | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4402-F100x256         | 1           | -            | 1            | 2 x 2         | N0, N1<br>MO[063]     |

| XMC4402-F64x256          | 1           | -            | 1            | 2 x 2         | N0, N1<br>MO[063]     |

#### Table 3 Features of XMC4400 Device Types

1) x is a placeholder for the supported temperature range.

# 2 General Device Information

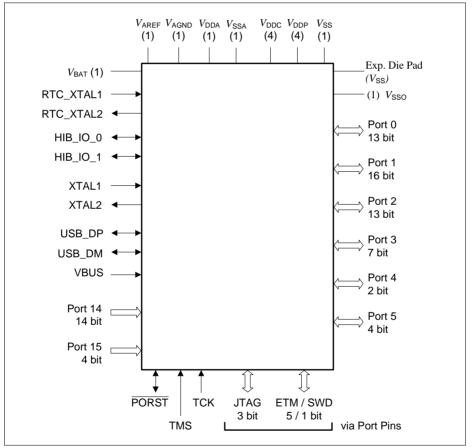

This section summarizes the logic symbols and package pin configurations with a detailed list of the functional I/O mapping.

# 2.1 Logic Symbols

Figure 2 XMC4400 Logic Symbol PG-LQFP-100

# 2.2.1 Package Pin Summary

The following general scheme is used to describe each pin:

## Table 9 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad<br>Type | Notes |

|----------|-----------|-----------|-----------------|-------|

| Name     | Ν         | Ax        | <br>A2          |       |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the dedicated pins (i.e. PORST) and supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type (A1, A1+, A2, special=special pad, In=input pad, AN/DIG\_IN=analog and digital input, Power=power supply). Details about the pad properties are defined in the Electrical Parameters.

In the "Notes", special information to the respective pin/function is given, i.e. deviations from the default configuration after reset. Per default the regular Port pins are configured as direct input with no internal pull device active.

| Function | LQFP-100 | LQFP-64<br>TQFP-64 | Pad Type | Notes                                                                                                                |

|----------|----------|--------------------|----------|----------------------------------------------------------------------------------------------------------------------|

| P0.0     | 2        | 2                  | A1+      |                                                                                                                      |

| P0.1     | 1        | 1                  | A1+      |                                                                                                                      |

| P0.2     | 100      | 64                 | A2       |                                                                                                                      |

| P0.3     | 99       | 63                 | A2       |                                                                                                                      |

| P0.4     | 98       | 62                 | A2       |                                                                                                                      |

| P0.5     | 97       | 61                 | A2       |                                                                                                                      |

| P0.6     | 96       | 60                 | A2       |                                                                                                                      |

| P0.7     | 89       | 58                 | A2       | After a system reset, via<br>HWSEL this pin selects the<br>DB.TDI function.                                          |

| P0.8     | 88       | 57                 | A2       | After a system reset, via<br><u>HWSEL</u> this pin selects the<br>DB.TRST function, with a<br>weak pull-down active. |

| P0.9     | 4        | 4                  | A2       |                                                                                                                      |

| P0.10    | 3        | 3                  | A1+      |                                                                                                                      |

## Table 10 Package Pin Mapping

| Table 10  | Package Pin Mapping (cont'd) |                    |            |                                                                                                                                                                                              |  |  |  |  |  |

|-----------|------------------------------|--------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Function  | LQFP-100                     | LQFP-64<br>TQFP-64 | Pad Type   | Notes                                                                                                                                                                                        |  |  |  |  |  |

| USB_DP    | 9                            | 6                  | special    |                                                                                                                                                                                              |  |  |  |  |  |

| USB_DM    | 8                            | 5                  | special    |                                                                                                                                                                                              |  |  |  |  |  |

| HIB_IO_0  | 14                           | 10                 | A1 special | At the first power-up and with<br>every reset of the hibernate<br>domain this pin is configured<br>as open-drain output and<br>drives "0".<br>As output the medium driver<br>mode is active. |  |  |  |  |  |

| HIB_IO_1  | 13                           | -                  | A1 special | At the first power-up and with<br>every reset of the hibernate<br>domain this pin is configured<br>as input with no pull device<br>active.<br>As output the medium driver<br>mode is active. |  |  |  |  |  |

| ТСК       | 67                           | 45                 | A1         | Weak pull-down active.                                                                                                                                                                       |  |  |  |  |  |

| TMS       | 66                           | 44                 | A1+        | Weak pull-up active.<br>As output the strong-soft<br>driver mode is active.                                                                                                                  |  |  |  |  |  |

| PORST     | 65                           | 43                 | special    | Strong pull-down controlled<br>by EVR.<br>Weak pull-up active while<br>strong pull-down is not<br>active.                                                                                    |  |  |  |  |  |

| XTAL1     | 61                           | 39                 | clock_IN   |                                                                                                                                                                                              |  |  |  |  |  |

| XTAL2     | 62                           | 40                 | clock_O    |                                                                                                                                                                                              |  |  |  |  |  |

| RTC_XTAL1 | 15                           | 11                 | clock_IN   |                                                                                                                                                                                              |  |  |  |  |  |

| RTC_XTAL2 | 16                           | 12                 | clock_O    |                                                                                                                                                                                              |  |  |  |  |  |

| VBAT      | 17                           | 13                 | Power      | When VDDP is supplied<br>VBAT has to be supplied as<br>well.                                                                                                                                 |  |  |  |  |  |

| VBUS      | 10                           | 7                  | special    |                                                                                                                                                                                              |  |  |  |  |  |

| VAREF     | 33                           | -                  | AN_Ref     |                                                                                                                                                                                              |  |  |  |  |  |

| VAGND     | 32                           | -                  | AN_Ref     |                                                                                                                                                                                              |  |  |  |  |  |

| VDDA      | 35                           | -                  | AN_Power   |                                                                                                                                                                                              |  |  |  |  |  |

#### Table 10 Deekege Din Menning (cont'd)

# 2.2.2 Port I/O Functions

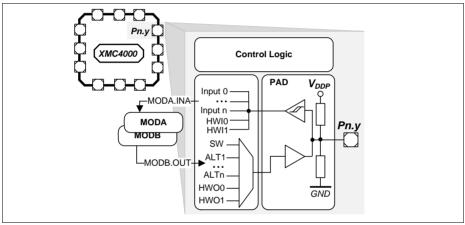

The following general scheme is used to describe each PORT pin:

### Table 11 Port I/O Function Description

| Function | Outputs  |          |          | Inputs   |          |          |  |

|----------|----------|----------|----------|----------|----------|----------|--|

|          | ALT1     | ALTn     | HWO0     | HWI0     | Input    | Input    |  |

| P0.0     |          | MODA.OUT | MODB.OUT | MODB.INA | MODC.INA |          |  |

| Pn.y     | MODA.OUT |          |          |          | MODA.INA | MODC.INB |  |

## Figure 6 Simplified Port Structure

Pn.y is the port pin name, defining the control and data bits/registers associated with it. As GPIO, the port is under software control. Its input value is read via Pn\_IN.y, Pn\_OUT defines the output value.

Up to four alternate output functions (ALT1/2/3/4) can be mapped to a single port pin, selected by Pn\_IOCR.PC. The output value is directly driven by the respective module, with the pin characteristics controlled by the port registers (within the limits of the connected pad).

The port pin input can be connected to multiple peripherals. Most peripherals have an input multiplexer to select between different possible input sources.

The input path is also active while the pin is configured as output. This allows to feedback an output to on-chip resources without wasting an additional external pin.

By Pn\_HWSEL it is possible to select between different hardware "masters" (HWO0/HWI0). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers.

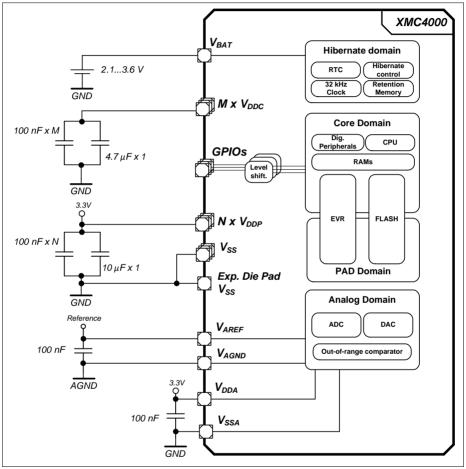

# 2.3 Power Connection Scheme

Figure 7. shows a reference power connection scheme for the XMC4400.

Figure 7 Power Connection Scheme

Every power supply pin needs to be connected. Different pins of the same supply need also to be externally connected. As example, all  $V_{\rm DDP}$  pins must be connected externally to one  $V_{\rm DDP}$  net. In this reference scheme one 100 nF capacitor is connected at each supply pin against  $V_{\rm SS}$ . An additional 10 µF capacitor is connected to the  $V_{\rm DDP}$  nets and an additional 4.7µF capacitor to the  $V_{\rm DDC}$  nets.

# 3 Electrical Parameters

# 3.1 General Parameters

## 3.1.1 Parameter Interpretation

The parameters listed in this section partly represent the characteristics of the XMC4400 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are marked with an two-letter abbreviation in column "Symbol":

• CC

Such parameters indicate Controller Characteristics, which are a distinctive feature of the XMC4400 and must be regarded for system design.

• SR

Such parameters indicate **S**ystem **R**equirements, which must be provided by the application system in which the XMC4400 is designed in.

# 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                              | Symbol                                 |    |      | Values |                                       |    | Note /                |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----|------|--------|---------------------------------------|----|-----------------------|

|                                                                                                                        |                                        |    | Min. | Тур.   | Max.                                  |    | Test Con<br>dition    |

| Storage temperature                                                                                                    | $T_{\rm ST}$                           | SR | -65  | -      | 150                                   | °C | -                     |

| Junction temperature                                                                                                   | TJ                                     | SR | -40  | _      | 150                                   | °C | -                     |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}$                                                        | $V_{DDP}$                              | SR | -    | -      | 4.3                                   | V  | -                     |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                            | V <sub>IN</sub>                        | SR | -1.0 | -      | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V  | whichever<br>is lower |

| Voltage on any analog input pin with respect to $V_{\text{AGND}}$                                                      | $V_{\mathrm{AIN}} \ V_{\mathrm{AREF}}$ | SR | -1.0 | -      | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V  | whichever<br>is lower |

| Input current on any pin<br>during overload condition                                                                  | I <sub>IN</sub>                        | SR | -10  | -      | +10                                   | mA |                       |

| Absolute maximum sum of all<br>input circuit currents for one<br>port group during overload<br>condition <sup>1)</sup> | $\Sigma I_{\rm IN}$                    | SR | -25  | -      | +25                                   | mA |                       |

| Absolute maximum sum of all input circuit currents during overload condition                                           | $\Sigma I_{\rm IN}$                    | SR | -100 | _      | +100                                  | mA |                       |

#### Table 13 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 17**.

#### Table 22 Standard Pads Class\_A1+

| Parameter            | Symbol               | Va                     | lues | Unit | Note /                                                                  |  |

|----------------------|----------------------|------------------------|------|------|-------------------------------------------------------------------------|--|

|                      |                      | Min.                   | Max. |      | Test Condition                                                          |  |

| Output high voltage, | V <sub>OHA1+</sub>   | V <sub>DDP</sub> - 0.4 | -    | V    | <i>I</i> <sub>OH</sub> ≥ -400 μA                                        |  |

| $POD^{1)} = weak$    | CC                   | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -500 μA                                        |  |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | I <sub>OH</sub> ≥ -1.4 mA                                               |  |

| $POD^{1)} = medium$  |                      | 2.4                    | -    | V    | I <sub>OH</sub> ≥ -2 mA                                                 |  |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | $I_{\rm OH} \ge$ -1.4 mA                                                |  |

| $POD^{1)} = strong$  |                      | 2.4                    | _    | V    | $I_{\rm OH} \ge$ -2 mA                                                  |  |

| Output low voltage   | $V_{\rm OLA1+}$ CC   | _                      | 0.4  | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak                   |  |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium                |  |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = strong                |  |

| Fall time            | t <sub>FA1+</sub> CC | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |  |

|                      |                      | -                      | 50   | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium                      |  |

|                      |                      | _                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |  |

|                      |                      | _                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft; |  |

| Rise time            | t <sub>RA1+</sub> CC | -                      | 150  | ns   | $C_{\rm L}$ = 20 pF;<br>POD <sup>1)</sup> = weak                        |  |

|                      |                      | -                      | 50   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium                  |  |

|                      |                      | -                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |  |

|                      |                      | -                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft  |  |

1) POD = Pin Out Driver

# 3.2.10 Power Supply Current

The total power supply current defined below consists of a leakage and a switching component.

Application relevant values are typically lower than those given in the following tables, and depend on the customer's system operating conditions (e.g. thermal connection or used application configurations).

If not stated otherwise, the operating conditions for the parameters in the following table are:

$V_{\rm DDP}$  = 3.3 V,  $T_{\rm A}$  = 25 °C

| Parameter                                                    | Symbol            |    |      | Values |      |    | Note /          |  |

|--------------------------------------------------------------|-------------------|----|------|--------|------|----|-----------------|--|

|                                                              |                   |    | Min. | Тур.   | Max. |    | Test Condition  |  |

| Active supply current <sup>1)</sup>                          | $I_{\rm DDPA}$    | CC | -    | 113    | -    | mA | 120 / 120 / 120 |  |

| Peripherals enabled                                          |                   |    | -    | 102    | -    |    | 120 / 60 / 60   |  |

| Frequency:<br>$f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz            |                   |    | -    | 82     | -    |    | 60 / 60 / 120   |  |

| JCPU' JPERIPH' JCCU III IVII IZ                              |                   |    | -    | 61     | -    |    | 24 / 24 / 24    |  |

|                                                              |                   |    | -    | 51     | -    |    | 1/1/1           |  |

| Active supply current                                        | I <sub>DDPA</sub> | CC | -    | 53     | -    | mA | 120 / 120 / 120 |  |

| Code execution from RAM<br>Flash in Sleep mode<br>Frequency: |                   |    | -    | 50     | -    |    | 120 / 60 / 60   |  |

| $f_{\rm CPU}/f_{\rm PERIPH}/f_{\rm CCU}$ in MHz              |                   |    |      |        |      |    |                 |  |

| Active supply current <sup>2)</sup>                          | $I_{\rm DDPA}$    | СС | -    | 80     | -    | mA | 120 / 120 / 120 |  |

| Peripherals disabled                                         |                   |    | -    | 80     | -    |    | 120 / 60 / 60   |  |

| Frequency: $f_{CPU}/f_{PERIPH}$ in MHz                       |                   |    | -    | 65     | -    |    | 60 / 60 / 120   |  |

| JCPUTJPERIPH                                                 |                   |    | -    | 55     | -    |    | 24 / 24 / 24    |  |

|                                                              |                   |    | _    | 50     | -    |    | 1/1/1           |  |

## Table 39 Power Supply Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Symbol           |    |      | Values | 5    | Unit   | Note /<br>Test Condition                                                   |

|------------------------------------------------|------------------|----|------|--------|------|--------|----------------------------------------------------------------------------|

|                                                |                  |    | Min. | Тур.   | Max. |        |                                                                            |

| Power Dissipation                              | $P_{DISS}$       | СС | -    | -      | 1    | W      | V <sub>DDP</sub> = 3.6 V,<br>T <sub>J</sub> = 150 °C                       |

| Wake-up time from Sleep to Active mode         | t <sub>SSA</sub> | СС | -    | 6      | -    | cycles |                                                                            |

| Wake-up time from Deep<br>Sleep to Active mode |                  |    | -    | -      | -    | ms     | Defined by the<br>wake-up of the<br>Flash module,<br>see<br>Section 3.2.11 |

| Wake-up time from<br>Hibernate mode            |                  |    | _    | -      | -    | ms     | Wake-up via<br>power-on reset<br>event, see<br>Section 3.3.2               |

#### Table 39 Power Supply Parameters

1) CPU executing code from Flash, all peripherals idle.

2) CPU executing code from Flash. Ethernet, USB and CCU clock off.

3) CPU in sleep, all peripherals idle, Flash in Active mode.

- 4) CPU in sleep, Flash in Active mode.

- 5) CPU in sleep, peripherals disabled, after wake-up code execution from RAM.

- 6) To wake-up the Flash from its Sleep mode,  $f_{CPU} \ge 1$  MHz is required.

- 7) OSC\_ULP operating with external crystal on RTC\_XTAL

- 8) OSC\_ULP off, Hibernate domain operating with OSC\_SI clock

- 9) Test Power Loop: f<sub>SYS</sub> = 120 MHz, CPU executing benchmark code from Flash, all CCUs in 100kHz timer mode, all ADC groups in continuous conversion mode, USICs as SPI in internal loop-back mode, CAN in 500kHz internal loop-back mode, interrupt triggered DMA block transfers to parity protected RAMs and FCE, DTS measurements and FPU calculations.

The power consumption of each customer application will most probably be lower than this value, but must be evaluated separately.

- 10)  $I_{\text{DDP}}$  decreases typically by 5 mA when  $f_{\text{SYS}}$  decreases by 10 MHz, at constant  $T_{\text{J}}$

- 11) Sum of currents of all active converters (ADC and DAC)

## **Peripheral Idle Currents**

Test conditions:

- f<sub>svs</sub> and derived clocks at 120 MHz

- V<sub>DDP</sub> = 3.3 V, T<sub>a</sub> =25 °C

- all peripherals are held in reset (see the PRSTAT registers in the Reset Control Unit of the SCU)

- the peripheral clocks are disabled (see CGATSTAT registers in the Clock Control Unit of the SCU

- no I/O activity

- the given values are a result of differential measurements with asserted and deasserted peripheral reset and enabled clock of the peripheral under test

The tested peripheral is left in the state after the peripheral reset is deasserted, no further initialisation or configuration is done. E.g. no timer is running in the CCUs, no communication active in the USICs, etc.

| Parameter                                     | Symbol              |      | Values |      | Unit | Note /         |

|-----------------------------------------------|---------------------|------|--------|------|------|----------------|

|                                               |                     | Min. | Тур.   | Max. |      | Test Condition |

| PORTS<br>ETH<br>USB<br>FCE<br>WDT<br>POSIFx   | I <sub>PER</sub> CC | -    | ≤ 0.3  | _    | mA   |                |

| MultiCAN<br>ERU<br>LEDTSCU0<br>CCU4x<br>CCU8x |                     | -    | ≤ 1.0  | _    |      |                |

| DAC (digital) <sup>1)</sup>                   |                     | -    | 1.3    | -    |      |                |

| USICx                                         | 1                   | -    | 3.0    | -    | 1    |                |

| DSD<br>VADC (digital) <sup>1)</sup>           |                     | -    | 4.5    | -    |      |                |

| DMAx                                          | 1                   | -    | 6.0    | -    | 1    |                |

## Table 40Peripheral Idle Currents

1) The current consumption of the analog components are given in the dedicated Data Sheet sections of the respective peripheral.

## 3.3 AC Parameters

## 3.3.1 Testing Waveforms

Figure 24 Testing Waveform, Output Delay

Figure 25 Testing Waveform, Output High Impedance

# 3.3.4 Phase Locked Loop (PLL) Characteristics

## Main and USB PLL

## Table 44PLL Parameters

| Parameter                | Symbol                  |      | Values | S    | Unit | Note /                                                                      |

|--------------------------|-------------------------|------|--------|------|------|-----------------------------------------------------------------------------|

|                          |                         | Min. | Тур.   | Max. |      | Test Condition                                                              |

| Accumulated Jitter       | D <sub>P</sub> CC       | -    | -      | ±5   | ns   | accumulated<br>over 300 cycles<br>$f_{SYS}$ = 120 MHz                       |

| Duty Cycle <sup>1)</sup> | D <sub>DC</sub> CC      | 46   | 50     | 54   | %    | Low pulse to<br>total period,<br>assuming an<br>ideal input clock<br>source |

| PLL base frequency       | $f_{PLLBASE}$ CC        | 30   | -      | 140  | MHz  |                                                                             |

| VCO input frequency      | $f_{\sf REF}\sf CC$     | 4    | -      | 16   | MHz  |                                                                             |

| VCO frequency range      | $f_{\rm VCO}  {\rm CC}$ | 260  | -      | 520  | MHz  |                                                                             |

| PLL lock-in time         | t <sub>L</sub> CC       | -    | -      | 400  | μS   |                                                                             |

1) 50% for even K2 divider values, 50±(10/K2) for odd K2 divider values.

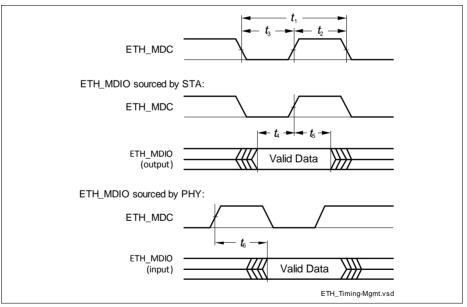

# 3.3.11.2 ETH Management Signal Parameters (ETH\_MDC, ETH\_MDIO)

| Parameter                    | Symbol                |    |      | Values | 5    | Unit | Note /                 |

|------------------------------|-----------------------|----|------|--------|------|------|------------------------|

|                              |                       |    | Min. | Тур.   | Max. |      | Test Conditi<br>on     |

| ETH_MDC period               | <i>t</i> <sub>1</sub> | СС | 400  | -      | -    | ns   | C <sub>L</sub> = 25 pF |

| ETH_MDC high time            | <i>t</i> <sub>2</sub> | СС | 160  | -      | -    | ns   |                        |

| ETH_MDC low time             | $t_3$                 | CC | 160  | -      | -    | ns   |                        |

| ETH_MDIO setup time (output) | <i>t</i> <sub>4</sub> | СС | 10   | -      | -    | ns   |                        |

| ETH_MDIO hold time (output)  | $t_5$                 | СС | 10   | -      | -    | ns   |                        |

| ETH_MDIO data valid (input)  | $t_6$                 | SR | 0    | -      | 300  | ns   | ]                      |

#### Table 58 ETH Management Signal Timing Parameters

Figure 40 ETH Management Signal Timing

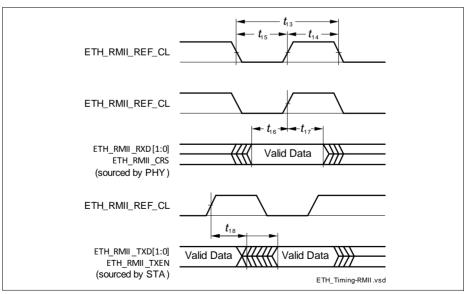

## 3.3.11.3 ETH RMII Parameters

In the following, the parameters of the RMII (Reduced Media Independent Interface) are described.

| Table 59         ETH RMII Signal Timing Parameters |

|----------------------------------------------------|

|----------------------------------------------------|

| Parameter                                      |                        | Symbol |      | Value | S    | Unit | Note /                            |

|------------------------------------------------|------------------------|--------|------|-------|------|------|-----------------------------------|

|                                                |                        |        | Min. | Тур.  | Max. |      | Test Condit<br>ion                |

| ETH_RMII_REF_CL clock period                   | <i>t</i> <sub>13</sub> | SR     | 20   | -     | _    | ns   | C <sub>L</sub> = 25 pF;<br>50 ppm |

| ETH_RMII_REF_CL clock high time                | t <sub>14</sub>        | SR     | 7    | -     | 13   | ns   | C <sub>L</sub> = 25 pF            |

| ETH_RMII_REF_CL clock low time                 | t <sub>15</sub>        | SR     | 7    | -     | 13   | ns   |                                   |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS setup time  | t <sub>16</sub>        | SR     | 4    | _     | _    | ns   |                                   |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS hold time   | t <sub>17</sub>        | SR     | 2    | -     | -    | ns   |                                   |

| ETH_RMII_TXD[1:0],<br>ETH_RMII_TXEN data valid | t <sub>18</sub>        | СС     | 4    | -     | 15   | ns   |                                   |

Figure 41 ETH RMII Signal Timing

## Package and Reliability

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta JA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}}-V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

# 4.2 Package Outlines

The availability of different packages for different devices types is listed in **Table 1**, specific packages for different device markings are listed in **Table 2**.

The exposed die pad dimensions are listed in Table 60.

| Change                                                  | PG-LQFP-100-11                 | PG-LQFP-100-25                         |

|---------------------------------------------------------|--------------------------------|----------------------------------------|

| Thermal Resistance Junction Ambient ( $R_{\Theta JA}$ ) | 20.5 K/W                       | 20.0 K/W                               |

| Lead Width                                              | 0.22 <sup>±0.05</sup> mm       | 0.2 <sup>+0.07</sup> -0.03 mm          |

| Lead Thickness                                          | 0.15 <sup>+0.05</sup> -0.06 mm | 0.127 <sup>+0.073</sup> -0.037 mm      |

| Exposed Die Pad outer dimensions                        | 7.0 mm × 7.0 mm                | $7.0 \text{ mm} \times 7.0 \text{ mm}$ |

| Exposed Die Pad U-<br>Groove inner dimensions           | n.a.                           | 6.2 mm × 6.2 mm                        |

Table 61 Differences PG-LQFP-100-11 to PG-LQFP-100-24