#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 1 1 1 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                         |

| Core Processor             | ARM® Cortex®-M4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                           |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| Number of I/O              | 31                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 80K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters            | A/D 14x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-64-19                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4402f64k256abxqsa1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2015-12 Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **General Device Information**

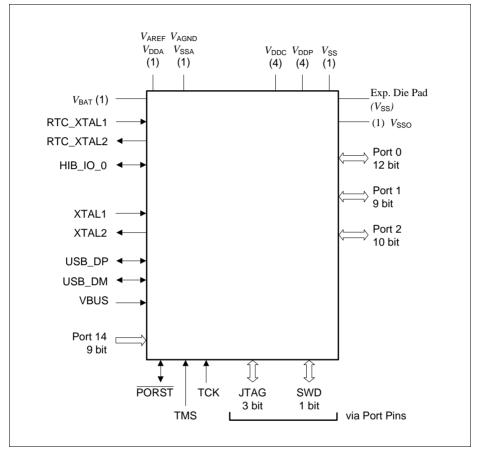

Figure 3 XMC4400 Logic Symbol PG-LQFP-64 and PG-TQFP-64

#### **General Device Information**

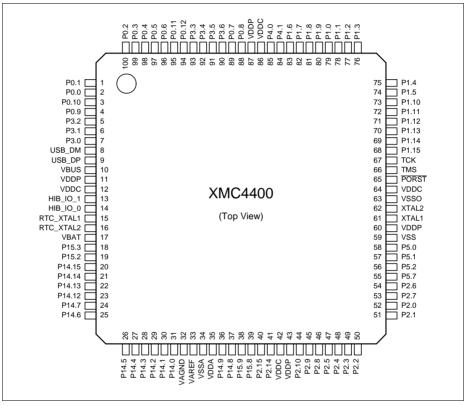

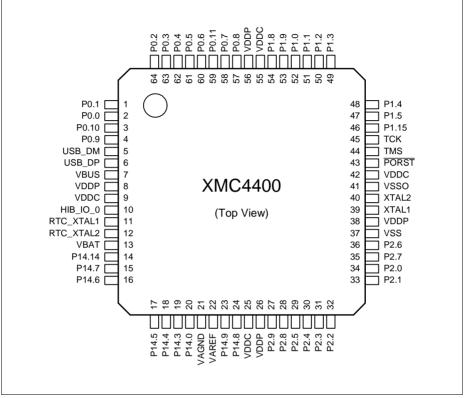

## 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the different packages.

Figure 4 XMC4400 PG-LQFP-100 Pin Configuration (top view)

### XMC4400 XMC4000 Family

#### **General Device Information**

Figure 5 XMC4400 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

#### **General Device Information**

### 2.2.1 Package Pin Summary

The following general scheme is used to describe each pin:

### Table 9 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad<br>Type | Notes |

|----------|-----------|-----------|-----------------|-------|

| Name     | Ν         | Ax        | <br>A2          |       |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the dedicated pins (i.e. PORST) and supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type (A1, A1+, A2, special=special pad, In=input pad, AN/DIG\_IN=analog and digital input, Power=power supply). Details about the pad properties are defined in the Electrical Parameters.

In the "Notes", special information to the respective pin/function is given, i.e. deviations from the default configuration after reset. Per default the regular Port pins are configured as direct input with no internal pull device active.

| Function | LQFP-100 | LQFP-64<br>TQFP-64 | Pad Type | Notes                                                                                                                |

|----------|----------|--------------------|----------|----------------------------------------------------------------------------------------------------------------------|

| P0.0     | 2        | 2                  | A1+      |                                                                                                                      |

| P0.1     | 1        | 1                  | A1+      |                                                                                                                      |

| P0.2     | 100      | 64                 | A2       |                                                                                                                      |

| P0.3     | 99       | 63                 | A2       |                                                                                                                      |

| P0.4     | 98       | 62                 | A2       |                                                                                                                      |

| P0.5     | 97       | 61                 | A2       |                                                                                                                      |

| P0.6     | 96       | 60                 | A2       |                                                                                                                      |

| P0.7     | 89       | 58                 | A2       | After a system reset, via<br>HWSEL this pin selects the<br>DB.TDI function.                                          |

| P0.8     | 88       | 57                 | A2       | After a system reset, via<br><u>HWSEL</u> this pin selects the<br>DB.TRST function, with a<br>weak pull-down active. |

| P0.9     | 4        | 4                  | A2       |                                                                                                                      |

| P0.10    | 3        | 3                  | A1+      |                                                                                                                      |

### Table 10 Package Pin Mapping

#### Table 12 Port I/O Functions (cont'd)

Data Sheet

| Function  | n Output |                      |      |      |                  | Input            |               |                |                |                |                    |       |        |                 |

|-----------|----------|----------------------|------|------|------------------|------------------|---------------|----------------|----------------|----------------|--------------------|-------|--------|-----------------|

|           | ALT1     | ALT2                 | ALT3 | ALT4 | HWO0             | HWI0             | Input         | Input          | Input          | Input          | Input              | Input | Input  | Input           |

| P14.9     |          |                      |      |      | DAC.<br>OUT_1    |                  |               | VADC.<br>G1CH1 |                | VADC.<br>G3CH3 | ETH0.<br>RXD1C     |       |        |                 |

| P14.12    |          |                      |      |      |                  |                  |               | VADC.<br>G1CH4 |                |                |                    |       |        |                 |

| P14.13    |          |                      |      |      |                  |                  |               | VADC.<br>G1CH5 |                |                |                    |       |        |                 |

| P14.14    |          |                      |      |      |                  |                  |               | VADC.<br>G1CH6 |                |                |                    |       | G1ORC6 |                 |

| P14.15    |          |                      |      |      |                  |                  |               | VADC.<br>G1CH7 |                |                |                    |       | G1ORC7 |                 |

| P15.2     |          |                      |      |      |                  |                  |               |                | VADC.<br>G2CH2 |                |                    |       |        |                 |

| P15.3     |          |                      |      |      |                  |                  |               |                | VADC.<br>G2CH3 |                |                    |       |        |                 |

| P15.8     |          |                      |      |      |                  |                  |               |                |                | VADC.<br>G3CH0 | ETH0.<br>CLK_RMIIC |       |        | ETH0.<br>CLKRXC |

| P15.9     |          |                      |      |      |                  |                  |               |                |                | VADC.<br>G3CH1 | ETH0.<br>CRS_DVC   |       |        | ETH0.<br>RXDVC  |

| USB_DP    |          |                      |      |      |                  |                  |               |                |                |                |                    |       |        |                 |

| USB_DM    |          |                      |      |      |                  |                  |               |                |                |                |                    |       |        |                 |

| HIB_IO_0  | HIBOUT   | WWDT.<br>SERVICE_OUT |      |      |                  |                  | WAKEUPA       |                |                |                |                    |       |        |                 |

| HIB_IO_1  | HIBOUT   | WWDT.<br>SERVICE_OUT |      |      |                  |                  | WAKEUPB       |                |                |                |                    |       |        |                 |

| тск       |          |                      |      |      |                  | DB.TCK/<br>SWCLK |               |                |                |                |                    |       |        |                 |

| TMS       |          |                      |      |      | DB.TMS/<br>SWDIO |                  |               |                |                |                |                    |       |        |                 |

| PORST     |          |                      |      |      |                  |                  |               |                |                |                |                    |       |        |                 |

| XTAL1     |          |                      |      |      |                  |                  | U0C0.<br>DX0F | U0C1.<br>DX0F  | U1C0.<br>DX0F  | U1C1.<br>DX0F  |                    |       |        |                 |

| XTAL2     |          |                      |      |      |                  |                  |               |                |                |                |                    |       |        |                 |

| RTC_XTAL1 |          |                      |      |      |                  |                  |               |                | ERU0.<br>1B1   |                |                    |       |        |                 |

| RTC_XTAL2 |          |                      |      |      |                  |                  |               |                |                |                |                    |       |        |                 |

XMC4400 XMC4000 Family

The XMC4400 has a common ground concept, all  $V_{\rm SS}$ ,  $V_{\rm SSA}$  and  $V_{\rm SSO}$  pins share the same ground potential. In packages with an exposed die pad it must be connected to the common ground as well.

$V_{\rm AGND}$  is the low potential to the analog reference  $V_{\rm AREF}$ . Depending on the application it can share the common ground or have a different potential. In devices with shared  $V_{\rm DDA}/V_{\rm AREF}$  and  $V_{\rm SSA}/V_{\rm AGND}$  pins the reference is tied to the supply. Some analog channels can optionally serve as "Alternate Reference"; further details on this operating mode are described in the Reference Manual.

When  $V_{\text{DDP}}$  is supplied,  $V_{\text{BAT}}$  must be supplied as well. If no other supply source (e.g. battery) is connected to  $V_{\text{BAT}}$ , the  $V_{\text{BAT}}$  pin can also be connected directly to  $V_{\text{DDP}}$ .

### Table 21 Standard Pads Class\_A1

| Parameter                                          | Symbol                  | Va                     | lues                         | Unit | Note /                                                   |

|----------------------------------------------------|-------------------------|------------------------|------------------------------|------|----------------------------------------------------------|

|                                                    |                         | Min.                   | Max.                         |      | Test Condition                                           |

| Input leakage current                              | I <sub>OZA1</sub> CC    | -500                   | 500                          | nA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$     |

| Input high voltage                                 | $V_{\rm IHA1}~{\rm SR}$ | $0.6 	imes V_{ m DDP}$ | $V_{\text{DDP}}$ + 0.3       | V    | max. 3.6 V                                               |

| Input low voltage                                  | $V_{\rm ILA1}{\rm SR}$  | -0.3                   | $0.36 \times V_{\text{DDF}}$ | . V  |                                                          |

| Output high voltage,                               | $V_{OHA1}$              | V <sub>DDP</sub> - 0.4 | -                            | V    | $I_{OH} \ge$ -400 $\mu$ A                                |

| $POD^{1)} = weak$                                  | CC                      | 2.4                    | -                            | V    | $I_{OH} \ge$ -500 $\mu$ A                                |

| Output high voltage,<br>POD <sup>1)</sup> = medium | _                       | V <sub>DDP</sub> - 0.4 | -                            | V    | $I_{\rm OH} \ge$ -1.4 mA                                 |

|                                                    |                         | 2.4                    | -                            | V    | $I_{OH} \ge -2 \text{ mA}$                               |

| Output low voltage                                 | V <sub>OLA1</sub><br>CC | -                      | 0.4                          | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak    |

|                                                    |                         | _                      | 0.4                          | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium |

| Fall time                                          | t <sub>FA1</sub> CC     | _                      | 150                          | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak     |

|                                                    |                         | -                      | 50                           | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium       |

| Rise time                                          | t <sub>RA1</sub> CC     | -                      | 150                          | ns   | $C_{\rm L}$ = 20 pF;<br>POD <sup>1)</sup> = weak         |

|                                                    |                         | -                      | 50                           | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium   |

1) POD = Pin Out Driver

### Table 22 Standard Pads Class\_A1+

| Parameter             | Symbol                | Values<br>Min. Max.      |  | Unit                    | Note /         |                                                      |

|-----------------------|-----------------------|--------------------------|--|-------------------------|----------------|------------------------------------------------------|

|                       |                       |                          |  |                         | Test Condition |                                                      |

| Input leakage current | I <sub>OZA1+</sub> CC | -1                       |  | 1                       | μΑ             | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$ |

| Input high voltage    | $V_{\rm IHA1+}\rm SR$ | $0.6 \times V_{\rm DDP}$ |  | $V_{\text{DDP}}$ + 0.3  | V              | max. 3.6 V                                           |

| Input low voltage     | $V_{\rm ILA1+}\rm SR$ | -0.3                     |  | $0.36 	imes V_{ m DDP}$ | V              |                                                      |

| Parameter                                          | Symbol                   | Va                     | lues                   | Unit | Note /<br>Test Condition                                              |  |

|----------------------------------------------------|--------------------------|------------------------|------------------------|------|-----------------------------------------------------------------------|--|

|                                                    |                          | Min.                   | Max.                   |      |                                                                       |  |

| Input leakage current                              | I <sub>OZHIB</sub><br>CC | -500                   | 500                    | nA   | $0 \ V \le V_{IN} \le V_{BAT}$                                        |  |

| Input high voltage                                 | V <sub>IHHIB</sub><br>SR | $0.6 	imes V_{BAT}$    | V <sub>BAT</sub> + 0.3 | V    | max. 3.6 V                                                            |  |

| Input low voltage                                  | $V_{\rm ILHIB}$ SR       | -0.3                   | $0.36 	imes V_{BAT}$   | V    |                                                                       |  |

| Input Hysteresis for<br>HIB_IO pins <sup>1)</sup>  | <i>HYSHIB</i><br>CC      | $0.1 	imes V_{BAT}$    | -                      | V    | $V_{BAT} \ge 3.13 \ V$                                                |  |

|                                                    |                          | $0.06 \times V_{BAT}$  | -                      | V    | $V_{\rm BAT}$ < 3.13 V                                                |  |

| Output high voltage,<br>POD <sup>1)</sup> = medium | V <sub>OHHIB</sub><br>CC | V <sub>BAT</sub> - 0.4 | -                      | V    | $I_{\rm OH}$ $\geq$ -1.4 mA                                           |  |

| Output low voltage                                 | V <sub>OLHIB</sub><br>CC | -                      | 0.4                    | V    | $I_{\rm OL} \le 2 \ {\rm mA}$                                         |  |

| Fall time                                          | t <sub>FHIB</sub> CC     | -                      | 50                     | ns   | $V_{\text{BAT}} \ge 3.13 \text{ V}$<br>$C_{\text{L}} = 50 \text{ pF}$ |  |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF                         |  |

| Rise time                                          | t <sub>RHIB</sub> CC     | -                      | 50                     | ns   | $V_{\rm BAT} \ge 3.13 \ { m V}$<br>$C_{\rm L}$ = 50 pF                |  |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF                         |  |

### Table 24 HIB\_IO Class\_A1 special Pads

1) Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

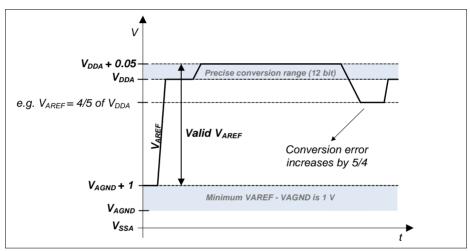

## 3.2.2 Analog to Digital Converters (ADCx)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                                    | Symbol                     |                            | Values | 5                                    | Unit | Note /                                                                                                        |

|------------------------------------------------------------------------------|----------------------------|----------------------------|--------|--------------------------------------|------|---------------------------------------------------------------------------------------------------------------|

|                                                                              |                            | Min.                       | Тур.   | Max.                                 |      | Test Condition                                                                                                |

| Analog reference voltage <sup>5)</sup>                                       | $V_{AREF}$ SR              | V <sub>AGND</sub><br>+ 1   | -      | $V_{\rm DDA}^{}+$ 0.05 <sup>1)</sup> | V    |                                                                                                               |

| Analog reference ground <sup>5)</sup>                                        | $V_{AGND}$ SR              | V <sub>SSM</sub> -<br>0.05 | -      | V <sub>AREF</sub> -<br>1             | V    |                                                                                                               |

| Analog reference voltage<br>range <sup>2)5)</sup>                            | $V_{AREF}$ - $V_{AGND}$ SR | 1                          | -      | V <sub>DDA</sub> + 0.1               | V    |                                                                                                               |

| Analog input voltage                                                         | $V_{\rm AIN}~{\rm SR}$     | $V_{\rm AGND}$             | -      | $V_{DDA}$                            | V    |                                                                                                               |

| Input leakage at analog inputs <sup>3)</sup>                                 | I <sub>OZ1</sub> CC        | -100                       | -      | 200                                  | nA   | $0.03 	imes V_{ m DDA} < V_{ m AIN} < 0.97 	imes V_{ m DI}$ A                                                 |

|                                                                              |                            | -500                       | -      | 100                                  | nA   | $\begin{array}{l} 0 \ V \leq V_{AIN} \leq 0.03 \\ \times \ V_{DDA} \end{array}$                               |

|                                                                              |                            | -100                       | -      | 500                                  | nA   | $\begin{array}{l} \textbf{0.97} \times V_{\text{DDA}} \\ \leq V_{\text{AIN}} \leq V_{\text{DDA}} \end{array}$ |

| Input leakage current at VAREF                                               | I <sub>OZ2</sub> CC        | -1                         | -      | 1                                    | μA   | $0 V \le V_{AREF} \le V_{DDA}$                                                                                |

| Input leakage current at VAGND                                               | I <sub>OZ3</sub> CC        | -1                         | -      | 1                                    | μA   | $\begin{array}{l} 0 \ V \leq V_{AGND} \\ \leq V_{DDA} \end{array}$                                            |

| Internal ADC clock                                                           | $f_{\sf ADCI}\sf CC$       | 2                          | -      | 30                                   | MHz  | $V_{\rm DDA}$ = 3.3 V                                                                                         |

| Switched capacitance at the analog voltage inputs <sup>4)</sup>              | C <sub>AINSW</sub><br>CC   | -                          | 4      | 6.5                                  | pF   |                                                                                                               |

| Total capacitance of an analog input                                         | $C_{AINTOT}$ CC            | -                          | 12     | 20                                   | pF   |                                                                                                               |

| Switched capacitance at the positive reference voltage input <sup>5)6)</sup> | C <sub>AREFSW</sub><br>CC  | -                          | 15     | 30                                   | pF   |                                                                                                               |

| Total capacitance of the voltage reference inputs <sup>5)</sup>              | $C_{AREFTOT}$ CC           | -                          | 20     | 40                                   | pF   |                                                                                                               |

| Table 25 | ADC Parameters | (Operating Conditions apply) |  |

|----------|----------------|------------------------------|--|

|----------|----------------|------------------------------|--|

- 4) The sampling capacity of the conversion C-network is pre-charged to V<sub>AREF</sub>/2 before the sampling moment. Because of the parasitic elements, the voltage measured at AINx can deviate from V<sub>AREF</sub>/2.

- 5) Applies to AINx, when used as alternate reference input.

- 6) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead, smaller capacitances are successively switched to the reference voltage.

- For 10-bit conversions, the errors are reduced to 1/4; for 8-bit conversions, the errors are reduced to 1/16. Never less than ±1 LSB.

- 8) The sum of DNL/INL/GAIN/OFF errors does not exceed the related total unadjusted error TUE.

- 9) The resulting current for a conversion can be calculated with  $I_{AREF} = Q_{CONV} / t_c$ . The fastest 12-bit post-calibrated conversion of  $t_c = 550$  ns results in a typical average current of  $I_{AREF} = 54.5 \ \mu$ A.

Figure 12 VADC Reference Voltage Range

| Parameter | Symbol                  |                                           | Value | Unit              | Note / |                                       |

|-----------|-------------------------|-------------------------------------------|-------|-------------------|--------|---------------------------------------|

|           |                         | Min.                                      | Тур.  | Max.              |        | Test Con<br>dition                    |

| Frequency | $f_{eclk}$ SR           | -                                         | -     | $f_{\rm hrpwm}/4$ | MHz    |                                       |

| ON time   | t <sub>oneclk</sub> SR  | $2T_{\rm ccu}^{1)2)}$                     | -     | -                 | ns     |                                       |

| OFF time  | t <sub>offeclk</sub> SR | 2 <i>T</i> <sub>ccu</sub> <sup>1)2)</sup> | -     | -                 | ns     | Only the<br>rising<br>edge is<br>used |

### Table 32 External clock operating conditions

1) 50% duty cycle is not obligatory

2) Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

## 3.2.6 Low Power Analog Comparator (LPAC)

The Low Power Analog Comparator (LPAC) triggers a wake-up event from Hibernate state or an interrupt trigger during normal operation. It does so by comparing  $V_{\rm BAT}$  or another external sensor voltage  $V_{\rm LPS}$  with a pre-programmed threshold voltage.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                             | Symbol                   |      | Values |      | Unit |                                            |  |

|-------------------------------------------------------|--------------------------|------|--------|------|------|--------------------------------------------|--|

|                                                       |                          | Min. | Тур.   | Max. |      | Test Condition                             |  |

| $V_{\rm BAT}$ supply voltage range for LPAC operation | $V_{\rm BAT}~{ m SR}$    | 2.1  | -      | 3.6  | V    |                                            |  |

| Sensor voltage range                                  | V <sub>LPCS</sub><br>CC  | 0    | -      | 1.2  | V    |                                            |  |

| Threshold step size                                   | $V_{\rm th}$ CC          | -    | 18.75  | _    | mV   |                                            |  |

| Threshold trigger accuracy                            | $\Delta V_{\rm th}$ CC   | -    | -      | ±10  | %    | for $V_{\rm th}$ > 0.4 V                   |  |

| Conversion time                                       | t <sub>LPCC</sub> CC     | -    | -      | 250  | μS   |                                            |  |

| Average current consumption over time                 | I <sub>LPCAC</sub><br>CC | -    | -      | 15   | μA   | conversion<br>interval 10 ms <sup>1)</sup> |  |

| Current consumption during conversion                 | $I_{\rm LPCC}  {\rm CC}$ | -    | 150    | -    | μA   | 1)                                         |  |

Table 33Low Power Analog Comparator Parameters

1) Single channel conversion, measuring  $V_{\text{BAT}}$  = 3.3 V, 8 cycles settling time

## 3.2.8 USB OTG Interface DC Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification and the OTG Specification Rev. 1.3. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                            | Symbol                     |      | Values | 5    | Unit | Note /                                                   |  |

|--------------------------------------|----------------------------|------|--------|------|------|----------------------------------------------------------|--|

|                                      |                            | Min. | Тур.   | Max. |      | Test Condition                                           |  |

| VBUS input voltage range             | V <sub>IN</sub> CC         | 0.0  | -      | 5.25 | V    |                                                          |  |

| A-device VBUS valid threshold        | V <sub>B1</sub> CC         | 4.4  | -      | -    | V    |                                                          |  |

| A-device session valid threshold     | V <sub>B2</sub> CC         | 0.8  | -      | 2.0  | V    |                                                          |  |

| B-device session valid threshold     | V <sub>B3</sub> CC         | 0.8  | -      | 4.0  | V    |                                                          |  |

| B-device session end threshold       | V <sub>B4</sub> CC         | 0.2  | -      | 0.8  | V    |                                                          |  |

| VBUS input resistance to ground      | R <sub>VBUS_IN</sub><br>CC | 40   | -      | 100  | kOhm |                                                          |  |

| B-device VBUS pull-<br>up resistor   | R <sub>VBUS_PU</sub><br>CC | 281  | -      | -    | Ohm  | Pull-up voltage = 3.0 V                                  |  |

| B-device VBUS pull-<br>down resistor | R <sub>VBUS_PD</sub><br>CC | 656  | -      | -    | Ohm  |                                                          |  |

| USB.ID pull-up<br>resistor           | R <sub>UID_PU</sub><br>CC  | 14   | -      | 25   | kOhm |                                                          |  |

| VBUS input current                   | I <sub>VBUS_IN</sub><br>CC | _    | -      | 150  | μΑ   | $0 V \le V_{IN} \le 5.25 V$ :<br>T <sub>AVG</sub> = 1 ms |  |

#### Table 35 USB OTG VBUS and ID Parameters (Operating Conditions apply)

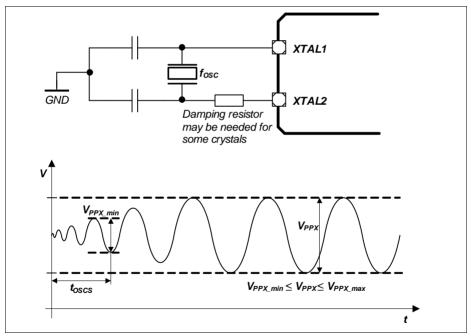

### 3.2.9 Oscillator Pins

- Note: It is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimal parameters for the oscillator operation. Please refer to the limits specified by the crystal or ceramic resonator supplier.

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

The oscillator pins can be operated with an external crystal (see Figure 21) or in direct input mode (see Figure 22).

Figure 21 Oscillator in Crystal Mode

| Parameter                                                   | Symbol                  | Values                      |      |                        | Unit | Note /                                                     |

|-------------------------------------------------------------|-------------------------|-----------------------------|------|------------------------|------|------------------------------------------------------------|

|                                                             |                         | Min.                        | Тур. | Max.                   |      | Test Condition                                             |

| Input frequency                                             | $f_{\rm OSC}{\rm SR}$   | 4                           | -    | 40                     | MHz  | Direct Input Mode<br>selected                              |

|                                                             |                         | 4                           | -    | 25                     | MHz  | External Crystal<br>Mode selected                          |

| Oscillator start-up time <sup>1)2)</sup>                    | t <sub>OSCS</sub><br>CC | _                           | -    | 10                     | ms   |                                                            |

| Input voltage at XTAL1                                      | V <sub>IX</sub> SR      | -0.5                        | -    | V <sub>DDP</sub> + 0.5 | V    |                                                            |

| Input amplitude (peak-<br>to-peak) at XTAL1 <sup>2)3)</sup> | $V_{\rm PPX}{\rm SR}$   | $0.4 \times V_{\text{DDP}}$ | -    | V <sub>DDP</sub> + 1.0 | V    |                                                            |

| Input high voltage at XTAL1 <sup>4)</sup>                   | $V_{\rm IHBX} {\rm SR}$ | 1.0                         | -    | V <sub>DDP</sub> + 0.5 | V    |                                                            |

| Input low voltage at XTAL1 <sup>4)</sup>                    | $V_{\rm ILBX}{ m SR}$   | -0.5                        | -    | 0.4                    | V    |                                                            |

| Input leakage current at XTAL1                              | I <sub>ILX1</sub> CC    | -100                        | -    | 100                    | nA   | Oscillator power<br>down<br>0 V $\leq V_{IX} \leq V_{DDP}$ |

#### Table 37 OSC\_XTAL Parameters

t<sub>OSCS</sub> is defined from the moment the oscillator is enabled wih SCU\_OSCHPCTRL.MODE until the oscillations reach an amplitude at XTAL1 of 0.4 \* V<sub>DDP</sub>.

2) The external oscillator circuitry must be optimized by the customer and checked for negative resistance and amplitude as recommended and specified by crystal suppliers.

3) If the shaper unit is enabled and not bypassed.

4) If the shaper unit is bypassed, dedicated DC-thresholds have to be met.

#### Table 41 Flash Memory Parameters

| Parameter                                                                 | Symbol                  | Values |      |      | Unit   | Note /                                                                                |

|---------------------------------------------------------------------------|-------------------------|--------|------|------|--------|---------------------------------------------------------------------------------------|

|                                                                           |                         | Min.   | Тур. | Max. |        | Test Condition                                                                        |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC     | 20     | -    | -    | years  | Max. 4<br>erase/program<br>cycles per UCB                                             |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub><br>CC | 10000  | -    | -    | cycles | BA-marking<br>devices only!<br>Cycling<br>distributed over<br>life time <sup>5)</sup> |

1) In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

2) The following formula applies to the wait state configuration: FCON.WSPFLASH × (1 /  $f_{CPU}$ )  $\geq t_a$ .

3) Storage and inactive time included.

4) Values given are valid for an average weighted junction temperature of  $T_{\rm J}$  = 110°C.

5) Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see the Reference Manual.

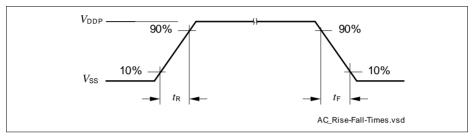

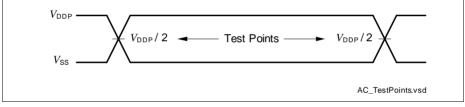

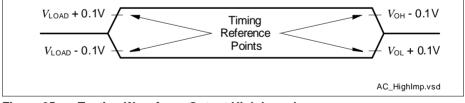

### 3.3 AC Parameters

### 3.3.1 Testing Waveforms

Figure 24 Testing Waveform, Output Delay

Figure 25 Testing Waveform, Output High Impedance

### 3.3.6 JTAG Interface Timing

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Note: Operating conditions apply.

| Parameter                                                          | Symbol                 |    | Values    |   |      | Unit | Note /                 |

|--------------------------------------------------------------------|------------------------|----|-----------|---|------|------|------------------------|

|                                                                    |                        |    | Min. Typ. |   | Max. | 1    | Test Condition         |

| TCK clock period                                                   | <i>t</i> <sub>1</sub>  | SR | 25        | - | -    | ns   |                        |

| TCK high time                                                      | $t_2$                  | SR | 10        | - | -    | ns   |                        |

| TCK low time                                                       | $t_3$                  | SR | 10        | - | -    | ns   |                        |

| TCK clock rise time                                                | $t_4$                  | SR | -         | _ | 4    | ns   |                        |

| TCK clock fall time                                                | $t_5$                  | SR | -         | - | 4    | ns   |                        |

| TDI/TMS setup<br>to TCK rising edge                                | t <sub>6</sub>         | SR | 6         | - | -    | ns   |                        |

| TDI/TMS hold<br>after TCK rising edge                              | <i>t</i> <sub>7</sub>  | SR | 6         | - | -    | ns   |                        |

| TDO valid after TCK falling edge <sup>1)</sup> (propagation delay) | <i>t</i> <sub>8</sub>  | СС | -         | _ | 13   | ns   | C <sub>L</sub> = 50 pF |

|                                                                    |                        |    | 3         | _ | _    | ns   | C <sub>L</sub> = 20 pF |

| TDO hold after TCK falling edge <sup>1)</sup>                      | t <sub>18</sub>        | CC | 2         | - | -    | ns   |                        |

| TDO high imped. to valid from TCK falling edge <sup>1)2)</sup>     | t <sub>9</sub>         | СС | -         | - | 14   | ns   | C <sub>L</sub> = 50 pF |

| TDO valid to high imped.<br>from TCK falling edge <sup>1)</sup>    | <i>t</i> <sub>10</sub> | СС | -         | - | 13.5 | ns   | C <sub>L</sub> = 50 pF |

Table 47 JTAG Interface Timing Parameters

1) The falling edge on TCK is used to generate the TDO timing.

2) The setup time for TDO is given implicitly by the TCK cycle time.

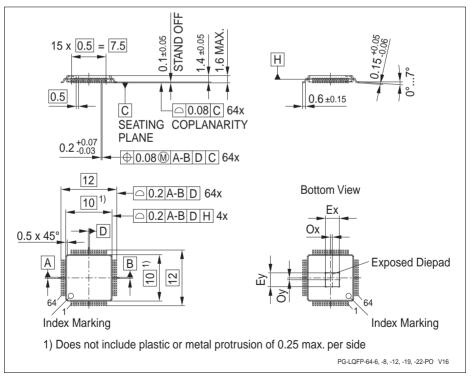

### Package and Reliability

| Change                                                     | PG-LQFP-64-19                  | PG-TQFP-64-19                   |  |  |

|------------------------------------------------------------|--------------------------------|---------------------------------|--|--|

| Thermal Resistance<br>Junction Ambient ( $R_{\Theta JA}$ ) | 30.0 K/W                       | 22.5 K/W                        |  |  |

| Package thickness                                          | 1.4 <sup>±0.05</sup> mm        | 1.0 <sup>±0.05</sup> mm         |  |  |

|                                                            | 1.6 mm MAX                     | 1.2 mm MAX                      |  |  |

| Lead Width                                                 | 0.22 <sup>±0.05</sup> mm       | 0.2 <sup>+0.07</sup> -0.03 mm   |  |  |

| Lead Thickness                                             | 0.15 <sup>+0.05</sup> -0.06 mm | 0.127 <sup>+0.07</sup> -0.04 mm |  |  |

| Exposed Die Pad outer<br>dimensions                        | 5.8 mm × 5.8 mm                | 5.7 mm × 5.7 mm                 |  |  |

| Exposed Die Pad U-<br>Groove inner dimensions              | n.a.                           | 4.9 mm × 4.9 mm                 |  |  |

Figure 44 PG-LQFP-64-19 (Plastic Green Low Profile Quad Flat Package)

#### **Quality Declarations**

# 5 Quality Declarations

The qualification of the XMC4400 is executed according to the JEDEC standard JESD47H.

Note: For automotive applications refer to the Infineon automotive microcontrollers.

| Parameter                                                        | Symbol                 | Values |      |       | Unit | Note /                                                        |  |

|------------------------------------------------------------------|------------------------|--------|------|-------|------|---------------------------------------------------------------|--|

|                                                                  |                        | Min.   | Тур. | Max.  |      | Test Condition                                                |  |

| Operation lifetime                                               | t <sub>OP</sub> CC     | 20     | -    | -     | а    | $T_{\rm J} \le 109^{\circ}{\rm C},$<br>device permanent<br>on |  |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)     | $V_{\rm HBM}$ SR       | -      | -    | 2 000 | V    | EIA/JESD22-<br>A114-B                                         |  |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) | V <sub>CDM</sub><br>SR | _      | -    | 500   | V    | Conforming to<br>JESD22-C101-C                                |  |

| Moisture sensitivity level                                       | MSL<br>CC              | -      | -    | 3     | -    | JEDEC<br>J-STD-020D                                           |  |

| Soldering temperature                                            | $T_{\rm SDR}$<br>SR    | _      | -    | 260   | °C   | Profile according<br>to JEDEC<br>J-STD-020D                   |  |

### Table 63Quality Parameters