Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                            |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 33MHz                                                                          |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SSU, UART/USART                          |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 48K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b; D/A 2x8b                                                           |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 120-LQFP                                                                       |

| Supplier Device Package    | 120-LQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r4f24248nvfpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 11.4.6 Phase Counting Mode                                                 | 771   |

|-------|----------------------------------------------------------------------------|-------|

| 11.5  | Interrupt Sources                                                          | 779   |

| 11.6  | DTC Activation                                                             | 783   |

| 11.7  | DMAC Activation                                                            | 783   |

| 11.8  | A/D Converter Activation                                                   | 783   |

| 11.9  | Operation Timing                                                           | 784   |

|       | 11.9.1 Input/Output Timing                                                 |       |

|       | 11.9.2 Interrupt Signal Timing                                             | 789   |

| 11.10 | Usage Notes                                                                | 793   |

|       | 11.10.1 Module Stop Function Setting                                       | 793   |

|       | 11.10.2 Input Clock Restrictions                                           |       |

|       | 11.10.3 Caution on Cycle Setting                                           | 794   |

|       | 11.10.4 Contention between TCNT Write and Clear Operations                 |       |

|       | 11.10.5 Contention between TCNT Write and Increment Operations             |       |

|       | 11.10.6 Contention between TGR Write and Compare Match                     | 796   |

|       | 11.10.7 Contention between Buffer Register Write and Compare Match         | 797   |

|       | 11.10.8 Contention between TGR Read and Input Capture                      | 798   |

|       | 11.10.9 Contention between TGR Write and Input Capture                     | 799   |

|       | 11.10.10 Contention between Buffer Register Write and Input Capture        | 800   |

|       | 11.10.11 Contention between Overflow/Underflow and Counter Clearing        | 801   |

|       | 11.10.12 Contention between TCNT Write and Overflow/Underflow              | 802   |

|       | 11.10.13 Multiplexing of I/O Pins                                          | 802   |

|       | 11.10.14 Interrupts and Module Stop Mode                                   | 802   |

| Secti | on 12 Programmable Pulse Generator (PPG)                                   | . 803 |

| 12.1  | Features                                                                   |       |

| 12.2  | Input/Output Pins                                                          | 805   |

| 12.3  | Register Descriptions                                                      | 806   |

|       | 12.3.1 Next Data Enable Registers H, L (NDERH, NDERL)                      | 807   |

|       | 12.3.2 Output Data Registers H, L (PODRH, PODRL)                           | 808   |

|       | 12.3.3 Next Data Registers H, L (NDRH, NDRL)                               | 809   |

|       | 12.3.4 PPG Output Control Register (PCR)                                   | 812   |

|       | 12.3.5 PPG Output Mode Register (PMR)                                      | 813   |

| 12.4  | Operation                                                                  | 815   |

|       | 12.4.1 Output Timing                                                       | 816   |

|       | 12.4.2 Sample Setup Procedure for Normal Pulse Output                      | 817   |

|       | 12.4.3 Example of Normal Pulse Output (Example of Five-Phase Pulse Output) |       |

|       | 12.4.4 Non-Overlapping Pulse Output.                                       |       |

|       | 12.4.5 Sample Setup Procedure for Non-Overlapping Pulse Output             |       |

|       |                                                                            |       |

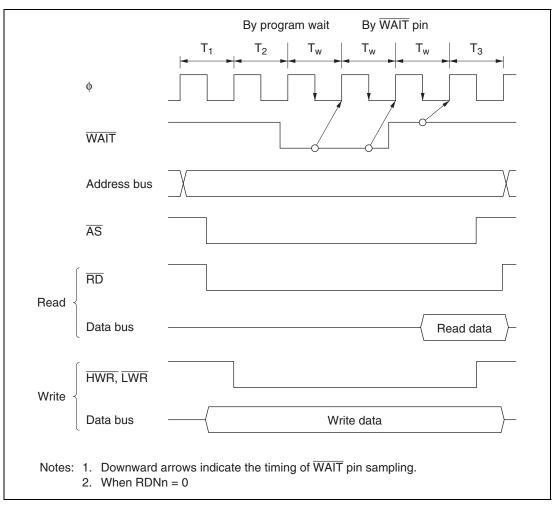

Figure 6.18 Example of Wait State Insertion Timing

### 6.5.5 Read Strobe (RD) Timing

The read strobe  $(\overline{RD})$  timing can be changed for individual areas by setting bits RDN7 to RDN0 to 1 in RDNCR. Figure 6.19 shows an example of the timing when the read strobe timing is changed in basic bus 3-state access space.

When the DMAC or EXDMAC is used in single address mode, note that if the  $\overline{RD}$  timing is changed by setting RDNn to 1, the  $\overline{RD}$  timing will change relative to the rise of  $\overline{DACK}$  or  $\overline{EDACK}$ .

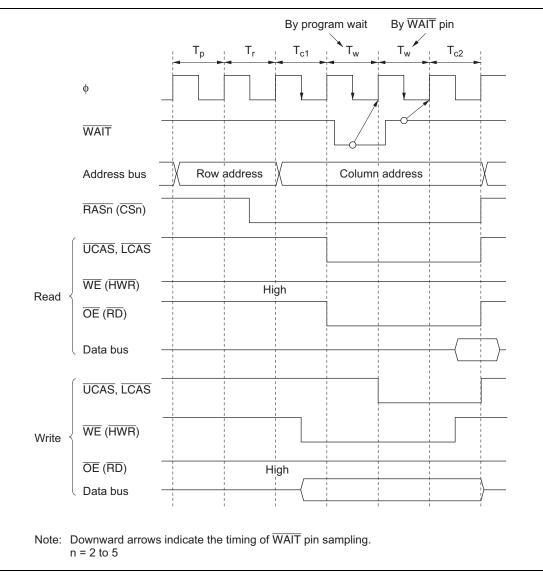

Figure 6.38 Example of Wait State Insertion Timing (2-State Column Address Output)

#### 6.8.12 Burst Operation

With synchronous DRAM, in addition to full access (normal access) in which data is accessed by outputting a row address for each access, burst access is also provided which can be used when making consecutive accesses to the same row address. This access enables fast access of data by simply changing the column address after the row address has been output. Burst access can be selected by setting the BE bit to 1 in DRAMCR.

DQM has the 2-cycle latency when synchronous DRAM is read. Therefore, the DQM signal cannot be specified to the Tc2 cycle data output if the Tc1 cycle is executed for second or following column address when the CAS latency is set to 1 to issue the READ command. Do not set the BE bit to 1 when synchronous DRAM of CAS latency 1 is connected.

#### (1) Burst Access Operation Timing

Figure 6.64 shows the operation timing for burst access. When there are consecutive access cycles for continuous synchronous DRAM space, the column address output cycles continue as long as the row address is the same for consecutive access cycles. The row address used for the comparison is set with bits MXC2 to MXC0 in DRAMCR.

## 6.10.2 Pin States in Idle Cycle

Table 6.13 shows the pin states in an idle cycle.

#### Table 6.13 Pin States in Idle Cycle

| Pins                                    | Pin State                         |

|-----------------------------------------|-----------------------------------|

| A23 to A0                               | Contents of following bus cycle   |

| D15 to D0                               | High impedance                    |

| $\overline{\text{CSn}}$ (n = 7 to 0)    | High* <sup>1</sup> * <sup>2</sup> |

| UCAS, LCAS                              | High* <sup>2</sup>                |

| AS/AH                                   | High                              |

| RD                                      | High                              |

| ŌĒ                                      | High                              |

| HWR, LWR                                | High                              |

| DACKn (n = 1, 0)                        | High                              |

| $\overline{\text{EDACKn}}$ (n = 3 to 0) | High                              |

Notes: 1. Remains low in DRAM space RAS down mode.

2. Remains low in a DRAM space refresh cycle.

## 6.15 Usage Notes

#### 6.15.1 External Bus Release Function and All-Module-Clocks-Stopped Mode

In this LSI, if the ACSE bit is set to 1 in MSTPCR, and then a SLEEP instruction is executed with the setting for all peripheral module clocks to be stopped (MSTPCR = H'FFFF, EXMSTPCR = H'FFFF) or for operation of the 8-bit timer module alone (MSTPCR = H'FFFE, EXMSTPCR = H'FFFF), and a transition is made to the sleep state, the all-module-clocks-stopped mode is entered in which the clock is also stopped for the bus controller and I/O ports. In this state, the external bus release function is halted. To use the external bus release function in sleep mode, the ACSE bit in MSTPCR must be cleared to 0. Conversely, if a SLEEP instruction to place the chip in all-module-clocks-stopped mode is executed in the external bus released state, the transition to all-module-clocks-stopped mode is deferred and performed until after the bus is recovered.

#### 6.15.2 External Bus Release Function and Software Standby

In this LSI, internal bus master operation does not stop even while the bus is released, as long as the program is running in on-chip ROM, etc., and no external access occurs. If a SLEEP instruction to place the chip in software standby mode is executed while the external bus is released, the transition to software standby mode is deferred and performed after the bus is recovered.

Also, since clock oscillation halts in software standby mode, if BREQ goes low in this mode, indicating an external bus release request, the request cannot be answered until the chip has recovered from the software standby state.

#### 6.15.3 External Bus Release Function and CBR Refreshing/Auto Refreshing

CBR refreshing<sup>\*1</sup>/auto refreshing<sup>\*2</sup> cannot be executed while the external bus is released. Setting the BREQOE bit to 1 in BCR beforehand enables the  $\overline{BREQO}$  signal to be output when a CBR refresh<sup>\*1</sup>/auto refresh<sup>\*2</sup> request is issued.

- Notes: 1. The auto refresh control function is not supported by the H8S/2426 Group and H8S/2424 Group.

- 2. The CBR refreshing control is not supported by the 5-V version.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DAT1     | 0             | R/W | Destination Address Update Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6   | DAT0     | 0             | R/W | These bits specify incrementing/decrementing of<br>the transfer destination address (EDDAR). When<br>an external device with DACK is designated as the<br>transfer destination in single address mode, the<br>specification by these bits is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |               |     | 0x: Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          |               |     | 10: Incremented (+1 in byte transfer, +2 in word transfer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          |               |     | <ol> <li>Decremented (-1 in byte transfer, -2 in word transfer)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | DARIE    | 0             | R/W | Destination Address Repeat Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |               |     | When this bit is set to 1, in the event of destination<br>address repeat area overflow the IRF bit is set to 1<br>and the EDA bit cleared to 0 in EDMDR, and<br>transfer is terminated. If the EDIE bit in EDMDR is<br>1 when the IRF bit in EDMDR is set to 1, an<br>interrupt request is sent to the CPU. When used<br>together with block transfer mode, a destination<br>address repeat interrupt is requested at the end of<br>a block-size transfer. If the EDA bit is set to 1 in<br>EDMDR for the channel on which transfer is<br>terminated by a destination address repeat<br>interrupt, transfer can be resumed from the state<br>in which it ended. If a destination address repeat<br>area has not been designated, this bit is ignored. |

|     |          |               |     | 0: Destination address repeat interrupt is not<br>requested                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |               |     | 1: When destination address repeat area overflow occurs, the IRF bit in EDMDR is set to 1 and an interrupt is requested                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# 8.5 Interrupt Sources

EXDMAC interrupt sources are a transfer end indicated by the transfer counter, and repeat area overflow interrupts. Table 8.4 shows the interrupt sources and their priority order.

| Interrupt | Interrupt source                                     | Interrupt Priority |

|-----------|------------------------------------------------------|--------------------|

| EXDMTEND2 | Transfer end indicated by channel 2 transfer counter | High               |

|           | Channel 2 source address repeat area overflow        | 1                  |

|           | Channel 2 destination address repeat area overflow   |                    |

| EXDMTEND3 | Transfer end indicated by channel 3 transfer counter | -                  |

|           | Channel 3 source address repeat area overflow        |                    |

|           | Channel 3 destination address repeat area overflow   | Low                |

## Table 8.4 Interrupt Sources and Priority Order

Interrupt sources can be enabled or disabled by means of the EDIE bit in EDMDR for the relevant channel, and can be sent to the interrupt controller independently. The relative priority order of the channels is determined by the interrupt controller (see table 8.4).

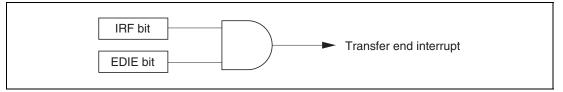

Figure 8.45 shows the transfer end interrupt logic. A transfer end interrupt is generated whenever the EDIE bit is set to 1 while the IRF bit is set to 1 in EDMDR.

Figure 8.45 Transfer End Interrupt Logic

Interrupt source settings are made individually with the interrupt enable bits in the registers for the relevant channels. The transfer counter's transfer end interrupt is enabled or disabled by means of the TCEIE bit in EDMDR, the source address register repeat area overflow interrupt by means of the SARIE bit in EDACR, and the destination address register repeat area overflow interrupt by means of the DARIE bit in EDACR. When an interrupt source occurs while the corresponding interrupt enable bit is set to 1, the IRF bit in EDMDR is set to 1. The IRF bit is set by all interrupt sources indiscriminately.

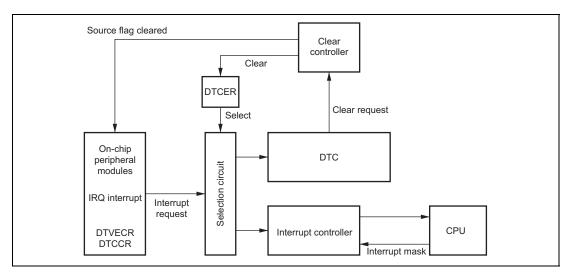

Figure 9.2 Block Diagram of DTC Activation Source Control

|        |                                                                          |                                                                                           |                        | Mo                                                          |                             | ode 3, 7                | Schmitt-                             | Input Pull-                                                                                  | Open Drain                                                                                      |                                |

|--------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------|-----------------------------|-------------------------|--------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|

| Port   | Description                                                              | Mode 1                                                                                    | Mode 2                 | Mode 4                                                      | EXPE = 1                    | EXPE = 0                | triggered<br>input Pin* <sup>3</sup> | up MOS<br>Capability                                                                         | Output<br>Capability                                                                            | 5-V<br>Tolerance* <sup>2</sup> |

| Port F | General I/O port<br>also functioning                                     |                                                                                           |                        |                                                             |                             | PF7/¢                   | _                                    | _                                                                                            | —                                                                                               | —                              |

|        | ass interrupt<br>inputs, bus<br>control signal<br>I/Os,<br>SSU I/Os, and |                                                                                           | PF6/AS/AH              |                                                             |                             |                         |                                      |                                                                                              | All output<br>pin<br>functions<br>other than<br>AS and AH                                       |                                |

|        | A/D converter<br>inputs                                                  | RD                                                                                        | RD                     |                                                             |                             |                         |                                      | All output<br>pin<br>functions<br>other than<br>RD                                           |                                                                                                 |                                |

|        |                                                                          | HWR                                                                                       |                        |                                                             |                             | PF4                     |                                      |                                                                                              | All output<br>pin<br>functions<br>other than<br>HWR                                             |                                |

|        |                                                                          | PF3/LWR/SSO0-C                                                                            |                        |                                                             |                             | PF3/SSO0-C              |                                      |                                                                                              | All output<br>pin<br>functions<br>other than<br>LWR                                             |                                |

|        |                                                                          | PF2/LCA                                                                                   | 5 <sup>*²</sup> /DQML* | DQML*'/IRQ15-A/SSI0-C PF2/IRQ15-A/ IRQ15-A<br>SSI0-C f<br>f |                             |                         |                                      | All output<br>pin<br>functions<br>other than<br>LCAS <sup>*2</sup> and<br>DQML <sup>*1</sup> |                                                                                                 |                                |

|        |                                                                          | PF1/UCAS* <sup>2</sup> /DQMU* <sup>1</sup> /IRQ14-A/SSCK0-C<br>PF0/WAIT-A/ADTRG0-B/SCS0-C |                        |                                                             | SSCK0-C                     | PF1/IRQ14-A/<br>SSCK0-C | ÎRQ14-A                              |                                                                                              | All output<br>pin<br>functions<br>other than<br>UCAS* <sup>2</sup><br>and<br>DQMU* <sup>1</sup> |                                |

|        |                                                                          |                                                                                           |                        |                                                             | PF0/<br>ADTRG0-B/<br>SCS0-C | _                       |                                      | All output<br>pin<br>functions                                                               |                                                                                                 |                                |

#### 10.1.5 Pin Functions

Port 1 pins also function as the pins for PPG outputs, TPU I/Os, EXDMAC I/Os (H8S/2426 Group, H8S/2426R Group), SSU I/Os, and DMAC I/Os (H8S/2424 Group). The correspondence between the register specification and the pin functions is shown below.

#### (1) Pin Functions of H8S/2426 Group and H8S/2426R Group

#### • P17/PO15/TIOCB2/TCLKD/EDRAK3/SCS0-A

The pin function is switched as shown below according to the combination of the operating mode, bit EXPE, TPU channel 2 settings (by bits MD3 to MD0 in TMDR\_2, bits IOB3 to IOB0 in TIOR\_2, and bits CCLR1 and CCLR0 in TCR\_2), bits TPSC2 to TPSC0 in TCR\_0 and TCR\_5, bit NDER15 in NDERH of the PPG, bit EDRAKE in EDMDR\_3 of the EXDMAC, bits MSS, CSS1, and CSS0 in SSCRH and bit SSUMS in SSCRL of the SSU, bits SCS0S1 and SCS0S0 in PFCR5, and bit P17DDR.

| SSU settings           |                    | (1) in table below |                |                |                  |                                              |                                            | (3) in<br>table<br>below                      |

|------------------------|--------------------|--------------------|----------------|----------------|------------------|----------------------------------------------|--------------------------------------------|-----------------------------------------------|

| EDRAKE                 |                    | 0                  |                |                | 1                |                                              |                                            |                                               |

| TPU channel 2 settings | (1) in table below | (2) in table below |                |                |                  |                                              |                                            |                                               |

| P17DDR                 | _                  | 0                  | 1              | 1              | —                | 0* <sup>6</sup>                              | 0* <sup>6</sup>                            | —                                             |

| NDER15                 | —                  |                    | 0              | 1              |                  |                                              |                                            |                                               |

| Pin function           | TIOCB2<br>output   | P17<br>input       | P17<br>output  | PO15<br>output | EDRAK3<br>output | SCS0-A<br>input* <sup>3</sup> * <sup>7</sup> | SCS0-A<br>I/O* <sup>5</sup> * <sup>7</sup> | SCS0-A<br>output* <sup>4</sup> * <sup>7</sup> |

|                        |                    |                    | TIOCB2 input*1 |                |                  |                                              |                                            |                                               |

|                        |                    | тс                 | LKD input      | *2             |                  |                                              |                                            |                                               |

• Modes 1, 2, and 4 Modes 3 and 7 (EXPE = 1)

#### • P14/PO12/TIOCA1/SSO0-A

The pin function is switched as shown below according to the combination of the TPU channel 1 settings (by bits MD3 to MD0 in TMDR\_1, bits IOA3 to IOA0 in TIOR\_1, and bits CCLR1 and CCLR0 in TCR\_1), bit NDER12 in NDERH of the PPG, bits MSS and BIDE in SSCRH, bit SSUMS in SSCRL, and bits TE and RE in SSER of the SSU, bits SSO0S1 and SSO0S0 in PFCR5, and bit P14DDR.

| SSU settings           |                       | (1) in tab   | (2) in table<br>below | (3) in table<br>below |                                              |                                               |  |

|------------------------|-----------------------|--------------|-----------------------|-----------------------|----------------------------------------------|-----------------------------------------------|--|

| TPU channel 1 settings | (1) in table<br>below | (2)          | ) in table belo       | _                     | _                                            |                                               |  |

| P14DDR                 | _                     | 0            | 1                     | 1                     | 0*5                                          |                                               |  |

| NDER12                 | _                     |              | 0                     | 1                     |                                              |                                               |  |

| Pin function           | TIOCA1<br>output      | P14<br>input | P14<br>output         | PO12<br>output        | SSO0-A<br>input* <sup>3</sup> * <sup>6</sup> | SSO0-A<br>output* <sup>4</sup> * <sup>6</sup> |  |

|                        |                       | Т            | IOCA1 input           |                       |                                              |                                               |  |

| TPU channel 1 settings | (2)                          | (1)                                   | (2)    | (1)                                | (1)                     | (2)  |

|------------------------|------------------------------|---------------------------------------|--------|------------------------------------|-------------------------|------|

| MD3 to MD0             | B'000                        | 00, B'01xx                            | B'001x | B'0010                             | B'                      | 0011 |

| IOA3 to IOA0           | B'0000,<br>B'0100,<br>B'1xxx | B'0001 to B'0011,<br>B'0101 to B'0111 | B'xx00 | Other than<br>B'xx00               | Other than B'xx00       |      |

| CCLR1,<br>CCLR0        | _                            |                                       |        |                                    | Other<br>than B'01      | B'01 |

| Output<br>function     |                              | Output compare<br>output              |        | PWM* <sup>2</sup> mode<br>1 output | PWM<br>mode 2<br>output | —    |

[Legend]

#### x: Don't care

Notes: 1. TIOCA1 input when MD3 to MD0 = B'0000 or B'01xx and IOA3 to IOA0 = B'10xx.

- 2. TIOCB1 output disabled.

- 3. When using as SSO0-A input, set SSO0S1 and SSO0S0 in PFCR5 to B'00 before other register setting.

- 4. When using as SSO0-A output, set SSO0S1 and SSO0S0 in PFCR5 to B'00 before other register setting.

- 5. P14DDR = 0 when the SSU pin is used as input.

- Do not set up for SSU unless SSO0S1 and SSO0S0 = B'00 in PFCR5. Use as I/O port or TPU pin.

#### • P21/IRQ9-B/PO1-A/TIOCB3-A

The pin function is switched as shown below according to the combination of the TPU channel 3 settings (by bits MD3 to MD0 in TMDR\_3, bits IOB3 to IOB0 in TIORH\_3, and bits CCLR2 to CCLR0 in TCR\_3), bit NDER1 in NDERL of the PPG, bits PPGS and TPUS in PFCR3, bit P21DDR, and bit ITS9 in ITSR of the interrupt controller.

| TPU channel 3 settings | (1) in table<br>below | (2) in table below                          |                |  |  |  |  |  |

|------------------------|-----------------------|---------------------------------------------|----------------|--|--|--|--|--|

| P21DDR                 | —                     | 0                                           | 1              |  |  |  |  |  |

| NDER1                  | —                     | —                                           | 0 1            |  |  |  |  |  |

| Pin function           | TIOCB3-A              | P21 input P21 output PO1-A output*          |                |  |  |  |  |  |

|                        | output* <sup>4</sup>  | TIOCB3-A input* <sup>1</sup> * <sup>4</sup> |                |  |  |  |  |  |

|                        |                       | IRQ9-B int                                  | errupt input*2 |  |  |  |  |  |

Notes: 1. TIOCB3-A input when MD3 to MD0 = B'0000 and IOB3 to IOB0 = B'10xx.

- 2. IRQ9-B input when the ITS9 bit in ITSR is 1.

- 3. When using as PO1-A output, set PPGS in PFCR3 to 0 before other register setting.

- 4. When using as TIOCB3-A input/output, set TPUS in PFCR3 to 0 before other register setting.

| TPU channel 3 settings | (2)                          | (1)                                         | (2)    | (2)    | (1)                  | (2)   |  |

|------------------------|------------------------------|---------------------------------------------|--------|--------|----------------------|-------|--|

| MD3 to MD0             | B'C                          | 000                                         | B'0010 |        | B'0011               |       |  |

| IOB3 to IOB0           | B'0000,<br>B'0100,<br>B'1xxx | B'0001 to<br>B'0011,<br>B'0101 to<br>B'0111 | _      | B'xx00 | Other than B'xx00    |       |  |

| CCLR2 to<br>CCLR0      | —                            | —                                           | —      | _      | Other than<br>B'010  | B'010 |  |

| Output function        | _                            | Output<br>compare<br>output                 |        |        | PWM mode<br>2 output | —     |  |

[Legend]

x: Don't care

#### • PA3/A19/SCK4-B

The pin function is switched as shown below according to the combination of the operating mode, bit EXPE, bit  $C/\overline{A}$  in SMR\_4 and bits CKE0 and CKE1 in SCR\_4 of the SCI, bit A19E in PFCR1, bit SCK4S in PFCR4, and bit PA3DDR.

| Operating<br>mode | 1, 2          |              | 4             |                   |                   |                  |                         |   |  |

|-------------------|---------------|--------------|---------------|-------------------|-------------------|------------------|-------------------------|---|--|

| EXPE              |               |              |               |                   | _                 |                  |                         |   |  |

| A19E              |               |              | 0 1           |                   |                   |                  |                         |   |  |

| CKE1              |               |              | 0 1           |                   |                   |                  | _                       | _ |  |

| C/A               |               |              | 0             |                   | 1                 | _                | _                       | _ |  |

| CKE0              |               | (            | )             | 1                 | —                 | _                | _                       | _ |  |

| PA3DDR            |               | 0            | 1             | —                 | _                 | _                | 0 1                     |   |  |

| Pin function      | A19<br>output | PA3<br>input | PA3<br>output | SCK4-B<br>output* | SCK4-B<br>output* | SCK4-B<br>input* | PA3 A19<br>input output |   |  |

| Operating<br>mode | 3, 7         |               |                   |   |                  |              |               |                   |                   |                  |              |               |

|-------------------|--------------|---------------|-------------------|---|------------------|--------------|---------------|-------------------|-------------------|------------------|--------------|---------------|

| EXPE              | 0 1          |               |                   |   |                  |              |               |                   |                   |                  |              |               |

| A19E              | _            |               |                   |   |                  | 0            |               |                   |                   |                  | 1            |               |

| CKE1              |              |               | 0                 |   | 1                |              | 0 1           |                   |                   |                  | —            |               |

| C/Ā               |              | 0             |                   | 1 | —                | 0            |               |                   | 1                 | _                | -            | _             |

| CKE0              |              | 0             | 1                 | _ | —                | 0 1          |               | _                 | _                 |                  | _            |               |

| PA3DDR            | 0            | 1             | _                 | _ | —                | 0            | 1             | _                 | _                 | _                | 0            | 1             |

| Pin function      | PA3<br>input | PA3<br>output | SCK4-B<br>output* |   | SCK4-B<br>input* | PA3<br>input | PA3<br>output | SCK4-B<br>output* | SCK4-B<br>output* | SCK4-B<br>input* | PA3<br>input | A19<br>output |

Note: \* When using as SCK4-B input/output, set SCK4S in PFCR4 to 1 before other register setting.

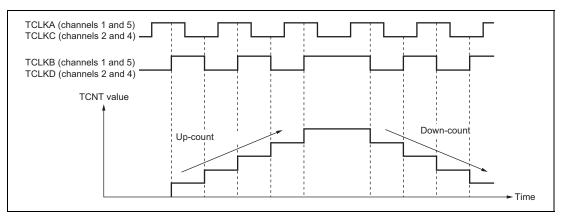

#### d. Phase counting mode 4

Figure 11.29 shows an example of phase counting mode 4 operation, and table 11.36 summarizes the TCNT up/down-count conditions.

#### Table 11.36 Up/Down-Count Conditions in Phase Counting Mode 4

| TCLKA (Channels 1 and 5)<br>TCLKC (Channels 2 and 4)<br>TCLKE (Channels 7 and 11)<br>TCLKG (Channels 8 and 10) | TCLKB (Channels 1 and 5)<br>TCLKD (Channels 2 and 4)<br>TCLKF (Channels 7 and 11)<br>TCLKH (Channels 8 and 10) | Operation  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------|

| High level                                                                                                     |                                                                                                                | Up-count   |

| Low level                                                                                                      |                                                                                                                |            |

|                                                                                                                | Low level                                                                                                      | Don't care |

|                                                                                                                | High level                                                                                                     |            |

| High level                                                                                                     |                                                                                                                | Down-count |

| Low level                                                                                                      |                                                                                                                |            |

|                                                                                                                | High level                                                                                                     | Don't care |

| <b>▼</b> _                                                                                                     | Low level                                                                                                      |            |

#### [Legend]

F: Rising edge

: Falling edge

| Bit<br>Rate | 8 |     |   | 10  |   | 16  |   | 20  |   | 25  |   | 30  |   | 33  |

|-------------|---|-----|---|-----|---|-----|---|-----|---|-----|---|-----|---|-----|

| (bit/s)     | n | Ν   | n | Ν   | n | Ν   | n | Ν   | n | Ν   | n | Ν   | n | Ν   |

| 110         |   |     |   |     |   |     |   |     |   |     |   |     |   |     |

| 250         | 3 | 124 | _ | _   | 3 | 249 |   |     |   |     |   |     |   |     |

| 500         | 2 | 249 | _ |     | 3 | 124 | _ |     |   |     | 3 | 233 |   |     |

| 1 k         | 2 | 124 |   | _   | 2 | 249 | _ | _   | 3 | 97  | 3 | 116 | 3 | 128 |

| 2.5 k       | 1 | 199 | 1 | 249 | 2 | 99  | 2 | 124 | 2 | 155 | 2 | 187 | 2 | 205 |

| 5 k         | 1 | 99  | 1 | 124 | 1 | 199 | 1 | 249 | 2 | 77  | 2 | 93  | 2 | 102 |

| 10 k        | 0 | 199 | 0 | 249 | 1 | 99  | 1 | 124 | 1 | 155 | 1 | 187 | 1 | 205 |

| 25 k        | 0 | 79  | 0 | 99  | 0 | 159 | 0 | 199 | 0 | 249 | 1 | 74  | 1 | 82  |

| 50 k        | 0 | 39  | 0 | 49  | 0 | 79  | 0 | 99  | 0 | 124 | 0 | 149 | 0 | 164 |

| 100 k       | 0 | 19  | 0 | 24  | 0 | 39  | 0 | 49  | 0 | 62  | 0 | 74  | 0 | 82  |

| 250 k       | 0 | 7   | 0 | 9   | 0 | 15  | 0 | 19  | 0 | 24  | 0 | 29  | 0 | 32  |

| 500 k       | 0 | 3   | 0 | 4   | 0 | 7   | 0 | 9   |   |     | 0 | 14  | _ | _   |

| 1 M         | 0 | 1   |   |     | 0 | 3   | 0 | 4   |   |     | _ | _   | _ | _   |

| 2.5 M       |   |     | 0 | 0*  |   |     | 0 | 1   |   |     | 0 | 2   | _ | —   |

| 5 M         |   |     |   |     |   |     | 0 | 0*  | _ | _   | _ | _   | _ | _   |

|             |   |     |   |     |   |     |   |     |   |     |   |     |   |     |

**Operating Frequency**  $\phi$  **(MHz)**

### Table 15.6 BRR Settings for Various Bit Rates (Clocked Synchronous Mode)

[Legend]

Blank: Cannot be set.

—: Can be set, but there will be a degree of error.

\*: Continuous transfer is not possible.

### Table 15.7 Maximum Bit Rate with External Clock Input (Clocked Synchronous Mode)

| φ (MHz) | External Input<br>Clock (MHz) | Maximum Bit<br>Rate (bit/s) | φ (MHz) | External Input<br>Clock (MHz) | Maximum Bit<br>Rate (bit/s) |

|---------|-------------------------------|-----------------------------|---------|-------------------------------|-----------------------------|

| 8       | 1.3333                        | 1333333.3                   | 18      | 3.0000                        | 300000.0                    |

| 10      | 1.6667                        | 1666666.7                   | 20      | 3.3333                        | 3333333.3                   |

| 12      | 2.0000                        | 2000000.0                   | 25      | 4.1667                        | 4166666.7                   |

| 14      | 2.3333                        | 2333333.3                   | 30      | 5.0000                        | 500000.0                    |

| 16      | 2.6667                        | 2666666.7                   | 33      | 5.5000                        | 5500000.0                   |

## 16.4.5 Slave Receive Operation

In slave receive mode, the master device outputs the transmit clock and transmit data, and the slave device returns an acknowledge signal. The reception procedure and operations in slave receive mode are described below.

- 1. Set the ICE bit in ICCRA to 1. Set the MLS and WAIT bits in ICMR and the CKS3 to CKS0 bits in ICCRA to 1. (Initial setting) Set the MST and TRS bits in ICCRA to select slave receive mode, and wait until the slave address matches.

- 2. When the slave address matches in the first frame following detection of the start condition, the slave device outputs the level specified by ACKBT in ICIER to SDA, at the rise of the 9th clock pulse. At the same time, RDRF in ICSR is set to read ICDRR (dummy read) and RDRF is cleared. (Since the read data show the slave address and  $R/\overline{W}$ , it is not used.)

- 3. Clear RDRF after reading ICDRR every time RDRF is set. If 8th receive clock pulse falls while RDRF is 1, SCL is fixed low until ICDRR is read. The change of the acknowledge before reading ICDRR, to be returned to the master device, is reflected to the next transmit frame.

- 4. The last byte data is read by reading ICDRR.

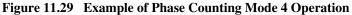

Figure 25.31 DMAC and EXDMAC Single Address Transfer Timing: Two-State Access

|                      |                                                                                                                 | Symbol                                                                                                                                                 | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Max.                                                   | Unit                                                    | <b>Test Conditions</b>                                  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|--|

| SCS hold time        | Master                                                                                                          | t <sub>LAG</sub>                                                                                                                                       | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                      | t <sub>cyc</sub>                                        | Figures 25.86 to                                        |  |

|                      | Slave                                                                                                           | -                                                                                                                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                      | _                                                       |                                                         |  |

| Data output delay    | Master                                                                                                          | t <sub>op</sub>                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                     | ns                                                      |                                                         |  |

| time                 | Slave                                                                                                           | —                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                     | _                                                       |                                                         |  |

| Data output hold     | Master                                                                                                          | t <sub>он</sub>                                                                                                                                        | -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                      | ns                                                      |                                                         |  |

| time                 | Slave                                                                                                           | -                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                      |                                                         |                                                         |  |

| Continuous           | Master                                                                                                          | t <sub>TD</sub>                                                                                                                                        | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                      | t <sub>cyc</sub>                                        | _                                                       |  |

| transmit delay time  | Slave                                                                                                           | _                                                                                                                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                      | -                                                       |                                                         |  |

| Slave access time    | t <sub>sa</sub>                                                                                                 | _                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>cyc</sub>                                       | Figures 25.88                                           |                                                         |  |

| Slave out release ti | t <sub>rel</sub>                                                                                                |                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>cyc</sub>                                       | and 25.89                                               |                                                         |  |

|                      | Data output delay<br>time<br>Data output hold<br>time<br>Continuous<br>transmit delay time<br>Slave access time | MaterData output delay<br>timeMasterData output hold<br>timeMasterData output hold<br>timeMasterSlaveSlaveContinuous<br>transmit delay timeMasterSlave | $\begin{tabular}{ c c c c c }\hline \hline SCS hold time & \underline{Master} & t_{\tiny LAG} \\\hline \hline Slave & \\\hline \hline Data output delay time & \underline{Master} & t_{\tiny OD} \\\hline \hline Data output hold & \underline{Master} & t_{\tiny OH} \\\hline \hline Data output hold & \underline{Master} & t_{\tiny OH} \\\hline \hline Continuous & \underline{Master} & t_{\tiny TD} \\\hline \hline Continuous & \underline{Master} & t_{\tiny Slave} \\\hline \hline Slave access time & t_{\tiny SA} \\\hline \hline Slave & t_{\tiny SA} \\\hline \hline \end{array}$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |

Note \* SSU: Synchronous serial communication unit

#### 25.5.4 A/D Conversion Characteristics

#### Table 25.48 A/D Conversion Characteristics

Conditions:  $V_{cc} = 4.5 \text{ V}$  to 5.5 V,  $AV_{cc} = 4.5 \text{ V}$  to 5.5 V,  $V_{ref} = 4.5 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 \text{ V}$ ,  $\phi = 8 \text{ MHz}$  to 33 MHz

| Item                                | Min. | Тур. | Max. | Unit |

|-------------------------------------|------|------|------|------|

| Resolution                          | 10   | 10   | 10   | Bit  |

| Conversion time                     | 2.5* | _    | _    | μs   |

| Analog input capacitance            | —    | —    | 15   | pF   |

| Permissible signal source impedance | —    | —    | 5    | kΩ   |

| Nonlinearity error                  | _    | _    | ±3.5 | LSB  |

| Offset error                        | _    | —    | ±3.5 | LSB  |

| Full-scale error                    | _    | —    | ±3.5 | LSB  |

| Quantization error                  | _    | —    | ±0.5 | LSB  |

| Absolute accuracy                   | _    | _    | ±4.0 | LSB  |

Note: \* For 40 states at ADCLK = 16 MHz.

##

# 0

| Offset error                | 1018 |

|-----------------------------|------|

| On-board programming        | 1084 |

| Open-drain control register | 507  |

| Operation field             |      |

| Output trigger              |      |

| Overflow                    |      |

| Overrun error               |      |

| OVI                         |      |

| OVI0                        |      |

| OVI1                        |      |

|                             |      |

# P

| Package dimensions               | 1356     |

|----------------------------------|----------|

| Parity error                     |          |

| Phase counting mode              |          |

| PLL circuit                      | 1138     |

| Port function control register 2 | 696      |

| Port register                    | 507      |

| Product code lineup              |          |

| Program counter (PC)             |          |

| Program-counter relative         |          |

| Programmable pulse generator     |          |

| Programmer mode                  | 1130     |

| Pull-up MOS control register     | 507      |

| Pulse output                     | 838, 839 |

| PWM modes                        |          |

|                                  |          |

# Q

| Quantization error |  |

|--------------------|--|

| C                  |  |

# R

| RAM                                    | 1075 |

|----------------------------------------|------|

| Read strobe ( $\overline{RD}$ ) timing |      |

| Register addresses                     |      |

| Register bits                          |      |

| Register direct                        |      |

| Register Field                         |      |

| Register indirect                      |      |

| Register indirect with displacement    |      |

| Register indirect with post-increment. |      |

| Register indirect with pre-decrement   |      |

| Register information                   |      |

| Register states in each operating      |      |

| mode                                   | 1199 |

| Registers                              |      |

| ABWCR                                  | 156  |

| ADCSR                                  | 999  |

| ASTCR                                  | 156  |

| BCR                                    | 168  |

| BROMCR                                 | 167  |

| BRR                                    | 889  |

| CRA                                    | 480  |

| CRB                                    | 480  |

| CSACR                                  | 165  |

| DACR                                   | 1030 |

| DADR                                   | 1030 |

| DAR                                    | 480  |

| DMABCR                                 | 331  |

| DMACR                                  | 323  |

| DMATCR                                 | 344  |

| DMAWER                                 | 342  |

| DRACCR                                 | 179  |

| DRAMCR                                 | 171  |

| DTCER                                  | 481  |

| DTVECR                                 | 481  |

| EDACR                                  | 418  |