Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

|                            |                                                                        |

| Product Status             | Discontinued at Digi-Key                                               |

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                             |

| Number of I/O              | 50                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                           |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-TQFP                                                                |

| Supplier Device Package    | 64-TQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg332f512-qfp64 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

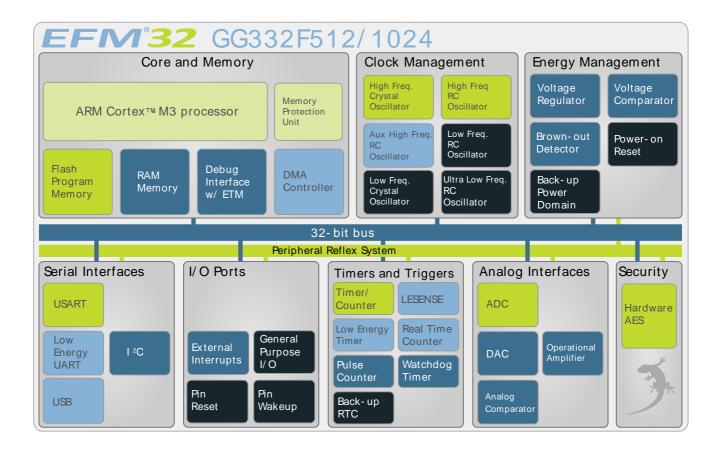

# 2 System Summary

## 2.1 System Introduction

The EFM32 MCUs are the world's most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM Cortex-M3, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32GG microcontroller is well suited for any battery operated application as well as other systems requiring high performance and low-energy consumption. This section gives a short introduction to each of the modules in general terms and also shows a summary of the configuration for the EFM32GG332 devices. For a complete feature set and in-depth information on the modules, the reader is referred to the *EFM32GG Reference Manual*.

A block diagram of the EFM32GG332 is shown in Figure 2.1 (p. 3).

Figure 2.1. Block Diagram

### 2.1.1 ARM Cortex-M3 Core

The ARM Cortex-M3 includes a 32-bit RISC processor which can achieve as much as 1.25 Dhrystone MIPS/MHz. A Memory Protection Unit with support for up to 8 memory segments is included, as well as a Wake-up Interrupt Controller handling interrupts triggered while the CPU is asleep. The EFM32 implementation of the Cortex-M3 is described in detail in *EFM32 Cortex-M3 Reference Manual*.

## 2.1.2 Debug Interface (DBG)

This device includes hardware debug support through a 2-pin serial-wire debug interface and an Embedded Trace Module (ETM) for data/instruction tracing. In addition there is also a 1-wire Serial Wire Viewer pin which can be used to output profiling information, data trace and software-generated messages.

available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

### 2.1.26 Backup Power Domain

The backup power domain is a separate power domain containing a Backup Real Time Counter, BURTC, and a set of retention registers, available in all energy modes. This power domain can be configured to automatically change power source to a backup battery when the main power drains out. The backup power domain enables the EFM32GG332 to keep track of time and retain data, even if the main power source should drain out.

### 2.1.27 Advanced Encryption Standard Accelerator (AES)

The AES accelerator performs AES encryption and decryption with 128-bit or 256-bit keys. Encrypting or decrypting one 128-bit data block takes 52 HFCORECLK cycles with 128-bit keys and 75 HFCORECLK cycles with 256-bit keys. The AES module is an AHB slave which enables efficient access to the data and key registers. All write accesses to the AES module must be 32-bit operations, i.e. 8- or 16-bit operations are not supported.

### 2.1.28 General Purpose Input/Output (GPIO)

In the EFM32GG332, there are 50 General Purpose Input/Output (GPIO) pins, which are divided into ports with up to 16 pins each. These pins can individually be configured as either an output or input. More advanced configurations like open-drain, filtering and drive strength can also be configured individually for the pins. The GPIO pins can also be overridden by peripheral pin connections, like Timer PWM outputs or USART communication, which can be routed to several locations on the device. The GPIO supports up to 16 asynchronous external pin interrupts, which enables interrupts from any pin on the device. Also, the input value of a pin can be routed through the Peripheral Reflex System to other peripherals.

## 2.2 Configuration Summary

The features of the EFM32GG332 is a subset of the feature set described in the EFM32GG Reference Manual. Table 2.1 (p. 7) describes device specific implementation of the features.

Table 2.1. Configuration Summary

| Module    | Configuration      | Pin Connections                                                                    |  |  |

|-----------|--------------------|------------------------------------------------------------------------------------|--|--|

| Cortex-M3 | Full configuration | NA                                                                                 |  |  |

| DBG       | Full configuration | DBG_SWCLK, DBG_SWDIO,<br>DBG_SWO                                                   |  |  |

| MSC       | Full configuration | NA                                                                                 |  |  |

| DMA       | Full configuration | NA                                                                                 |  |  |

| RMU       | Full configuration | NA                                                                                 |  |  |

| EMU       | Full configuration | NA                                                                                 |  |  |

| CMU       | Full configuration | CMU_OUT0, CMU_OUT1                                                                 |  |  |

| WDOG      | Full configuration | NA                                                                                 |  |  |

| PRS       | Full configuration | NA                                                                                 |  |  |

| USB       | Full configuration | USB_VBUS, USB_VBUSEN,<br>USB_VREGI, USB_VREGO, USB_DM,<br>USB_DMPU, USB_DP, USB_ID |  |  |

### Table 3.5. Power Management

| Symbol                   | Parameter                                                                   | Condition                                                               | Min  | Тур  | Max  | Unit |

|--------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| M                        | BOD threshold on                                                            | ЕМО                                                                     | 1.74 |      | 1.96 | V    |

| V <sub>BODextthr</sub> - | falling external sup-<br>ply voltage                                        | EM2                                                                     | 1.74 |      | 1.98 | V    |

| V <sub>BODintthr</sub> - | BOD threshold on<br>falling internally reg-<br>ulated supply volt-<br>age   |                                                                         | 1.57 |      | 1.70 | V    |

| V <sub>BODextthr+</sub>  | BOD threshold on rising external supply voltage                             |                                                                         |      | 1.85 | 1.98 | V    |

| V <sub>PORthr+</sub>     | Power-on Reset<br>(POR) threshold on<br>rising external sup-<br>ply voltage |                                                                         |      |      | 1.98 | V    |

| t <sub>RESET</sub>       | Delay from reset<br>is released until<br>program execution<br>starts        | Applies to Power-on Reset,<br>Brown-out Reset and pin reset.            |      | 163  |      | μѕ   |

| C <sub>DECOUPLE</sub>    | Voltage regulator decoupling capacitor.                                     | X5R capacitor recommended.<br>Apply between DECOUPLE pin<br>and GROUND  |      | 1    |      | μF   |

| C <sub>USB_VREGO</sub>   | USB voltage regulator out decoupling capacitor.                             | X5R capacitor recommended.<br>Apply between USB_VREGO<br>pin and GROUND |      | 1    |      | μF   |

| C <sub>USB_VREGI</sub>   | USB voltage regulator in decoupling capacitor.                              | X5R capacitor recommended.<br>Apply between USB_VREGI<br>pin and GROUND |      | 4.7  |      | μF   |

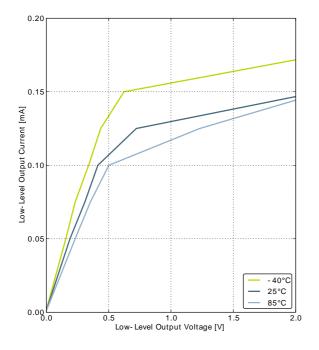

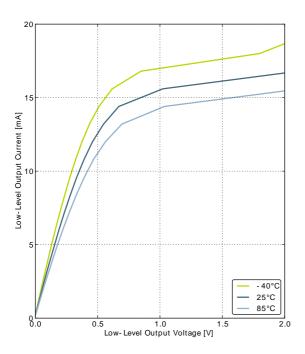

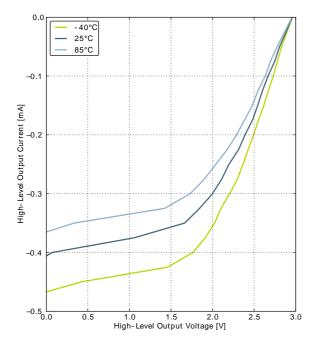

Figure 3.4. Typical Low-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

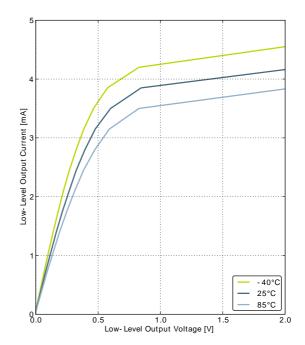

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

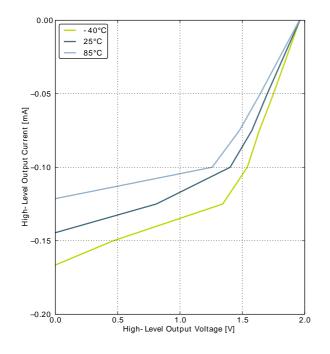

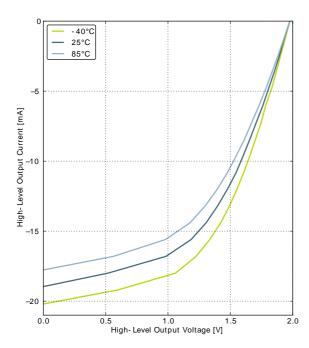

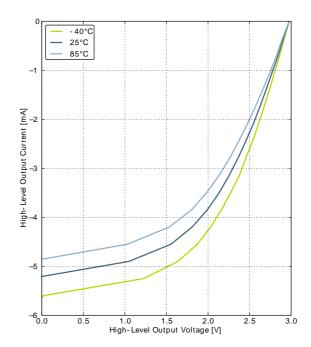

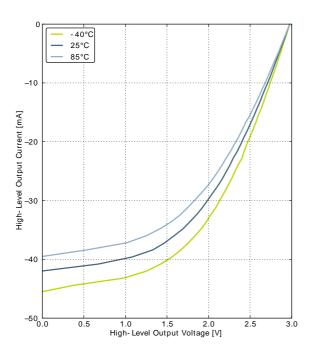

Figure 3.5. Typical High-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

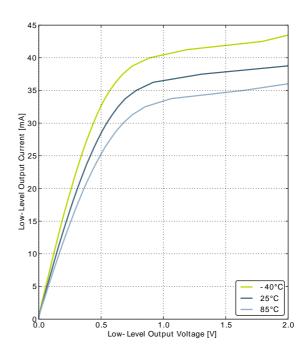

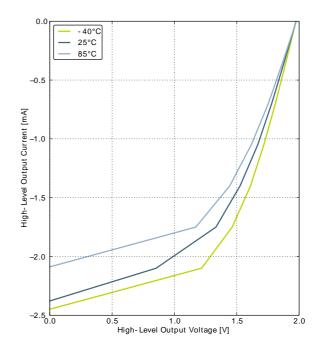

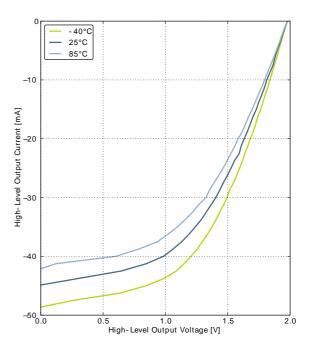

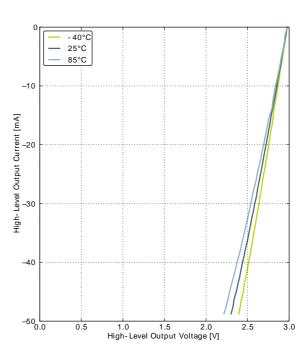

Figure 3.7. Typical High-Level Output Current, 3V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

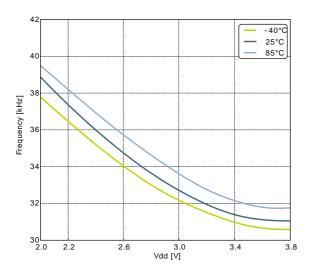

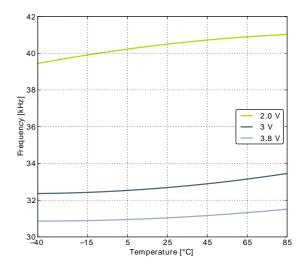

### 3.9.3 LFRCO

Table 3.10. LFRCO

| Symbol                          | Parameter                                                                       | Condition | Min   | Тур    | Max   | Unit |

|---------------------------------|---------------------------------------------------------------------------------|-----------|-------|--------|-------|------|

| f <sub>LFRCO</sub>              | Oscillation frequen-<br>cy , V <sub>DD</sub> = 3.0 V,<br>T <sub>AMB</sub> =25°C |           | 31.29 | 32.768 | 34.28 | kHz  |

| t <sub>LFRCO</sub>              | Startup time not including software calibration                                 |           |       | 150    |       | μs   |

| I <sub>LFRCO</sub>              | Current consumption                                                             |           |       | 300    | 900   | nA   |

| TUNESTEP <sub>L</sub> .<br>FRCO | Frequency step<br>for LSB change in<br>TUNING value                             |           |       | 1.5    |       | %    |

Figure 3.10. Calibrated LFRCO Frequency vs Temperature and Supply Voltage

### 3.9.4 HFRCO

Table 3.11. HFRCO

| Symbol                      | Parameter                                            | Condition                   | Min               | Тур               | Max               | Unit   |

|-----------------------------|------------------------------------------------------|-----------------------------|-------------------|-------------------|-------------------|--------|

|                             |                                                      | 28 MHz frequency band       | 27.5              | 28.0              | 28.5              | MHz    |

|                             |                                                      | 21 MHz frequency band       | 20.6              | 21.0              | 21.4              | MHz    |

| f                           | Oscillation frequen-<br>cy, V <sub>DD</sub> = 3.0 V, | 14 MHz frequency band       | 13.7              | 14.0              | 14.3              | MHz    |

| † <sub>HFRCO</sub>          | T <sub>AMB</sub> =25°C                               | 11 MHz frequency band       | 10.8              | 11.0              | 11.2              | MHz    |

|                             |                                                      | 7 MHz frequency band        | 6.48 <sup>1</sup> | 6.60 <sup>1</sup> | 6.72 <sup>1</sup> | MHz    |

|                             |                                                      | 1 MHz frequency band        | 1.15 <sup>2</sup> | 1.20 <sup>2</sup> | 1.25 <sup>2</sup> | MHz    |

|                             | Settling time after start-up                         | f <sub>HFRCO</sub> = 14 MHz |                   | 0.6               |                   | Cycles |

| <sup>t</sup> HFRCO_settling | Settling time after band switch                      |                             |                   | 25                |                   | Cycles |

| Symbol               | Parameter                                          | Condition                                                            | Min | Тур | Max | Unit |

|----------------------|----------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, internal 1.25V reference       |     | 62  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, internal 2.5V reference        |     | 63  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference      |     | 67  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, internal 1.25V reference       |     | 63  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, internal 2.5V reference        |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, 5V reference                   |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, V <sub>DD</sub> reference      | 63  | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference    |     | 70  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, single<br>ended, internal 1.25V refer-<br>ence |     | 58  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, single ended, internal 2.5V reference          |     | 62  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, single ended, V <sub>DD</sub> reference        |     | 64  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differential, internal 1.25V reference         |     | 60  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differential, internal 2.5V reference          |     | 64  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differential, 5V reference                     |     | 54  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differential, V <sub>DD</sub> reference        |     | 66  |     | dB   |

| SINAD <sub>ADC</sub> | SIgnal-to-Noise<br>And Distortion-ratio<br>(SINAD) | 1 MSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference      |     | 68  |     | dB   |

|                      | (0.1.1.2)                                          | 200 kSamples/s, 12 bit, single ended, internal 1.25V reference       |     | 61  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, internal 2.5V reference        |     | 65  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference      |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, internal 1.25V reference       |     | 63  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, internal 2.5V reference        |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, 5V reference                   |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, V <sub>DD</sub> reference      | 62  | 65  |     | dB   |

| Symbol                 | Parameter                                              | Condition                                                            | Min                 | Тур   | Max | Unit                |

|------------------------|--------------------------------------------------------|----------------------------------------------------------------------|---------------------|-------|-----|---------------------|

|                        |                                                        | 200 kSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference    |                     | 69    |     | dB                  |

|                        |                                                        | 1 MSamples/s, 12 bit, single<br>ended, internal 1.25V refer-<br>ence |                     | 64    |     | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, single ended, internal 2.5V reference          |                     | 76    |     | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, single ended, V <sub>DD</sub> reference        |                     | 73    |     | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differential, internal 1.25V reference         |                     | 66    |     | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differential, internal 2.5V reference          |                     | 77    |     | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differential, V <sub>DD</sub> reference        |                     | 76    |     | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference      |                     | 75    |     | dBc                 |

| SFDR <sub>ADC</sub>    | Spurious-Free Dy-<br>namic Range (SF-                  | 1 MSamples/s, 12 bit, differential, 5V reference                     |                     | 69    |     | dBc                 |

| GI DIVADC              | DR)                                                    | 200 kSamples/s, 12 bit, single ended, internal 1.25V reference       |                     | 75    |     | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, single ended, internal 2.5V reference        |                     | 75    |     | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference      |                     | 76    |     | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, internal 1.25V reference       |                     | 79    |     | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, internal 2.5V reference        |                     | 79    |     | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, 5V reference                   |                     | 78    |     | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, V <sub>DD</sub> reference      | 68                  | 79    |     | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference    |                     | 79    |     | dBc                 |

| V <sub>ADCOFFSET</sub> | Offset voltage                                         | After calibration, single ended                                      |                     | 0.3   |     | mV                  |

| - ADCOFFSET            | - Chica Foliago                                        | After calibration, differential                                      | -3                  | 0.3   | 3   | mV                  |

|                        |                                                        |                                                                      |                     | -1.92 |     | mV/°C               |

| TGRAD <sub>ADCTH</sub> | Thermometer out-<br>put gradient                       |                                                                      |                     | -6.3  |     | ADC<br>Codes/<br>°C |

| DNL <sub>ADC</sub>     | Differential non-lin-<br>earity (DNL)                  | V <sub>DD</sub> = 3.0 V, external 2.5V reference                     | -1                  | ±0.7  | 4   | LSB                 |

| INL <sub>ADC</sub>     | Integral non-linear-<br>ity (INL), End point<br>method |                                                                      | ±1.2                |       |     | LSB                 |

| MC <sub>ADC</sub>      | No missing codes                                       |                                                                      | 11.999 <sup>1</sup> | 12    |     | bits                |

| Symbol                    | Parameter                     | Condition                                                                            | Min             | Тур  | Max                  | Unit              |

|---------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----------------|------|----------------------|-------------------|

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1, Unity<br>Gain                             |                 | 13   | 17                   | μА                |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 101  |                      | dB                |

| G <sub>OL</sub>           | Open Loop Gain                | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 98   |                      | dB                |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 91   |                      | dB                |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 6.1  |                      | MHz               |

| GBW <sub>OPAMP</sub>      | Gain Bandwidth<br>Product     | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 1.8  |                      | MHz               |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.25 |                      | MHz               |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0, C <sub>L</sub> =75<br>pF                  |                 | 64   |                      | 0                 |

| PM <sub>OPAMP</sub>       | Phase Margin                  | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1, C <sub>L</sub> =75<br>pF                  |                 | 58   |                      | 0                 |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1, C <sub>L</sub> =75<br>pF                  |                 | 58   |                      | 0                 |

| R <sub>INPUT</sub>        | Input Resistance              |                                                                                      |                 | 100  |                      | Mohm              |

| R <sub>LOAD</sub>         | Load Resistance               |                                                                                      | 200             |      |                      | Ohm               |

| I <sub>LOAD_DC</sub>      | DC Load Current               |                                                                                      |                 |      | 11                   | mA                |

| Viviput                   | Input Voltage                 | OPAxHCMDIS=0                                                                         | V <sub>SS</sub> |      | V <sub>DD</sub>      | V                 |

| V <sub>INPUT</sub>        | input voltage                 | OPAxHCMDIS=1                                                                         | V <sub>SS</sub> |      | V <sub>DD</sub> -1.2 | V                 |

| V <sub>OUTPUT</sub>       | Output Voltage                |                                                                                      | V <sub>SS</sub> |      | $V_{DD}$             | V                 |

| V <sub>OFFSET</sub>       | Input Offset Voltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD,<br/>OPAxHCMDIS=0</v<sub></v<sub>     | -13             | 0    | 11                   | mV                |

| VOFFSET                   | input Onset Voltage           | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD-1.2,<br/>OPAxHCMDIS=1</v<sub></v<sub> |                 | 1    |                      | mV                |

| V <sub>OFFSET_DRIFT</sub> | Input Offset Voltage<br>Drift |                                                                                      |                 |      | 0.02                 | mV/°C             |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 3.2  |                      | V/µs              |

| SR <sub>OPAMP</sub>       | Slew Rate                     | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.8  |                      | V/µs              |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.1  |                      | V/µs              |

| N                         | Voltage Nain-                 | V <sub>out</sub> =1V, RESSEL=0,<br>0.1 Hz <f<10 khz,="" opax-<br="">HCMDIS=0</f<10>  |                 | 101  |                      | μV <sub>RMS</sub> |

| N <sub>OPAMP</sub>        | Voltage Noise                 | V <sub>out</sub> =1V, RESSEL=0,<br>0.1 Hz <f<10 khz,="" opax-<br="">HCMDIS=1</f<10>  |                 | 141  |                      | μV <sub>RMS</sub> |

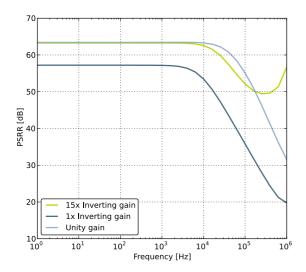

Figure 3.27. OPAMP Negative Power Supply Rejection Ratio

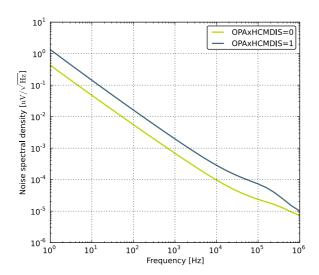

Figure 3.28. OPAMP Voltage Noise Spectral Density (Unity Gain) Vout=1V

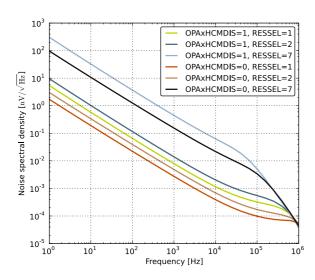

Figure 3.29. OPAMP Voltage Noise Spectral Density (Non-Unity Gain)

| 30 PD2 ADC0_CH2 TI  31 PD3 ADC0_CH3 OPAMP_N2  32 PD4 ADC0_CH4 OPAMP_P2  33 PD5 ADC0_CH5 OPAMP_OUT2 #0  34 PD6 ADC0_CH6 LET TI | Timers  IM0_CC1 #3  IM0_CC2 #3            | USB_DMPU #0 US1_CLK #1  US1_CS #1  LEU0_TX #0 | DBG_SWO #3 ETM_TD1 #0/2                                   |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 31 PD3 ADC0_CH3 TI  32 PD4 ADC0_CH4 OPAMP_P2  33 PD5 ADC0_CH5 OPAMP_OUT2 #0  34 PD6 ADC0_CH6 TI                               |                                           | US1_CLK #1 US1_CS #1                          | ETM_TD1 #0/2                                              |

| 31 PD3 OPAMP_N2  32 PD4 ADC0_CH4 OPAMP_P2  33 PD5 ADC0_CH5 OPAMP_OUT2 #0  34 PD6 ADC0_CH6 OPAMP_P1                            | IM0_CC2 #3                                | _                                             |                                                           |

| 32 PD4 OPAMP_P2  33 PD5 ADC0_CH5 OPAMP_OUT2 #0  34 PD6 ADC0_CH6 OPAMP_P1  TI                                                  |                                           | LEU0_TX #0                                    | ETM TD0 "0"                                               |

| 33                                                                                                                            |                                           |                                               | ETM_TD2 #0/2                                              |

| 34 PD6 ADCU_CH6 TI                                                                                                            |                                           | LEU0_RX #0                                    | ETM_TD3 #0/2                                              |

|                                                                                                                               | TIM0_OUT0 #0<br>IM1_CC0 #4<br>NT0_S0IN #3 | US1_RX #2<br>I2C0_SDA #1                      | LES_ALTEX0 #0<br>ACMP0_O #2<br>ETM_TD0 #0                 |

| 35 PD7 ADCU_CH7 TI                                                                                                            | IM0_OUT1 #0<br>IM1_CC1 #4<br>NT0_S1IN #3  | US1_TX #2<br>I2C0_SCL #1                      | CMU_CLK0 #2<br>LES_ALTEX1 #0<br>ACMP1_O #2<br>ETM_TCLK #0 |

| 36 PD8 BU_VIN                                                                                                                 |                                           |                                               | CMU_CLK1 #1                                               |

| 37 PC6 ACMP0_CH6                                                                                                              |                                           | I2C0_SDA #2<br>LEU1_TX #0                     | LES_CH6 #0<br>ETM_TCLK #2                                 |

| 38 PC7 ACMP0_CH7                                                                                                              |                                           | I2C0_SCL #2<br>LEU1_RX #0                     | LES_CH7 #0<br>ETM_TD0 #2                                  |

| 39 VDD_DREG Power supply for on-chip voltage regulato                                                                         | r.                                        |                                               |                                                           |

| 40 DECOUPLE Decouple output for on-chip voltage regula                                                                        | ator. An external capa                    | acitance of size C <sub>DECOUPLE</sub> is req | uired at this pin.                                        |

| 41 PC8 ACMP1_CH0 TI                                                                                                           | IM2_CC0 #2                                | US0_CS #2                                     | LES_CH8 #0                                                |

| 42 PC9 ACMP1_CH1 TI                                                                                                           | IM2_CC1 #2                                | US0_CLK#2                                     | LES_CH9 #0<br>GPIO_EM4WU2                                 |

| 43 PC10 ACMP1_CH2 TI                                                                                                          | IM2_CC2 #2                                | US0_RX #2                                     | LES_CH10 #0                                               |

| 44 PC11 ACMP1_CH3                                                                                                             |                                           | US0_TX #2                                     | LES_CH11 #0                                               |

| 45 USB_VREGI                                                                                                                  |                                           |                                               |                                                           |

| 46 USB_VREGO                                                                                                                  |                                           |                                               |                                                           |

| 47 PF10                                                                                                                       |                                           | USB_DM                                        |                                                           |

| 48 PF11                                                                                                                       |                                           | USB_DP                                        |                                                           |

|                                                                                                                               | IM0_CC0 #5<br>IM0_OUT0 #2                 | US1_CLK #2<br>I2C0_SDA #5<br>LEU0_TX #3       | DBG_SWCLK #0/1/2/3                                        |

|                                                                                                                               | IM0_CC1 #5<br>IM0_OUT1 #2                 | US1_CS #2<br>I2C0_SCL #5<br>LEU0_RX #3        | DBG_SWDIO #0/1/2/3<br>GPIO_EM4WU3                         |

| 51 PF2 TI                                                                                                                     | IM0_CC2 #5                                | LEU0_TX #4                                    | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4                   |

| 52 USB_VBUS USB 5.0 V VBUS input.                                                                                             |                                           |                                               |                                                           |

| 53 PF12                                                                                                                       |                                           | USB_ID                                        |                                                           |

| 54 PF5 TIM                                                                                                                    | I0_CDTI2 #2/5                             | USB_VBUSEN #0                                 | PRS_CH2 #1                                                |

| 55 IOVDD_5 Digital IO power supply 5.                                                                                         |                                           |                                               |                                                           |

| 56 VSS Ground.                                                                                                                |                                           |                                               |                                                           |

| 57 PE8 PC                                                                                                                     | NT2_S0IN #1                               |                                               | PRS_CH3 #1                                                |

| 58 PE9 PC                                                                                                                     | NT2_S1IN #1                               |                                               |                                                           |

| 59 PE10 TI                                                                                                                    |                                           |                                               | BOOT_TX                                                   |

|       | QFP64 Pin#<br>and Name | Pin Alternate Functionality / Description |             |                                        |                                            |  |  |  |  |

|-------|------------------------|-------------------------------------------|-------------|----------------------------------------|--------------------------------------------|--|--|--|--|

| Pin # | Pin Name               | Analog                                    | Timers      | Communication                          | Other                                      |  |  |  |  |

| 60    | PE11                   |                                           | TIM1_CC1 #1 | US0_RX #0                              | LES_ALTEX5 #0<br>BOOT_RX                   |  |  |  |  |

| 61    | PE12                   |                                           | TIM1_CC2 #1 | US0_RX #3<br>US0_CLK #0<br>I2C0_SDA #6 | CMU_CLK1 #2<br>LES_ALTEX6 #0               |  |  |  |  |

| 62    | PE13                   |                                           |             | US0_TX #3<br>US0_CS #0<br>I2C0_SCL #6  | LES_ALTEX7 #0<br>ACMP0_O #0<br>GPIO_EM4WU5 |  |  |  |  |

| 63    | PE14                   |                                           | TIM3_CC0 #0 | LEU0_TX #2                             |                                            |  |  |  |  |

| 64    | PE15                   |                                           | TIM3_CC1 #0 | LEU0_RX #2                             |                                            |  |  |  |  |

## **4.2 Alternate Functionality Pinout**

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in Table 4.2 (p. 52). The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

#### Note

Some functionality, such as analog interfaces, do not have alternate settings or a LOCA-TION bitfield. In these cases, the pinout is shown in the column corresponding to LOCA-TION 0.

Table 4.2. Alternate functionality overview

| Alternate     |      |   | LOC | ATION |   |   |   |                                                           |

|---------------|------|---|-----|-------|---|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1 | 2   | 3     | 4 | 5 | 6 | Description                                               |

| ACMP0_CH0     | PC0  |   |     |       |   |   |   | Analog comparator ACMP0, channel 0.                       |

| ACMP0_CH1     | PC1  |   |     |       |   |   |   | Analog comparator ACMP0, channel 1.                       |

| ACMP0_CH2     | PC2  |   |     |       |   |   |   | Analog comparator ACMP0, channel 2.                       |

| ACMP0_CH3     | PC3  |   |     |       |   |   |   | Analog comparator ACMP0, channel 3.                       |

| ACMP0_CH4     | PC4  |   |     |       |   |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |   |     |       |   |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |   |     |       |   |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |   |     |       |   |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 |   | PD6 |       |   |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_CH0     | PC8  |   |     |       |   |   |   | Analog comparator ACMP1, channel 0.                       |

| ACMP1_CH1     | PC9  |   |     |       |   |   |   | Analog comparator ACMP1, channel 1.                       |

| ACMP1_CH2     | PC10 |   |     |       |   |   |   | Analog comparator ACMP1, channel 2.                       |

| ACMP1_CH3     | PC11 |   |     |       |   |   |   | Analog comparator ACMP1, channel 3.                       |

| ACMP1_O       | PF2  |   | PD7 |       |   |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |   |     |       |   |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |   |     |       |   |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |   |     |       |   |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |   |     |       |   |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |   |     |       |   |   |   | Analog to digital converter ADC0, input channel number 4. |

| Alternate     |           |   | LOC | ATION |   |   |   |                                                                      |

|---------------|-----------|---|-----|-------|---|---|---|----------------------------------------------------------------------|

| Functionality | 0         | 1 | 2   | 3     | 4 | 5 | 6 | Description                                                          |

| USB_VBUSEN    | PF5       |   |     |       |   |   |   | USB 5 V VBUS enable.                                                 |

| USB_VREGI     | USB_VREGI |   |     |       |   |   |   | USB Input to internal 3.3 V regulator                                |

| USB_VREGO     | USB_VREGO |   |     |       |   |   |   | USB Decoupling for internal 3.3 V USB regulator and regulator output |

### **4.3 GPIO Pinout Overview**

The specific GPIO pins available in *EFM32GG332* is shown in Table 4.3 (p. 56). Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

Table 4.3. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin<br>9 | Pin<br>8 | Pin<br>7 | Pin<br>6 | Pin<br>5 | Pin<br>4 | Pin<br>3 | Pin<br>2 | Pin<br>1 | Pin<br>0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Port A | -         | -         | -         | -         | -         | PA10      | PA9      | PA8      | -        | -        | PA5      | PA4      | PA3      | PA2      | PA1      | PA0      |

| Port B | -         | PB14      | PB13      | -         | PB11      | -         | -        | PB8      | PB7      | -        | -        | -        | -        | -        | -        | -        |

| Port C | -         | -         | -         | -         | PC11      | PC10      | PC9      | PC8      | PC7      | PC6      | PC5      | PC4      | PC3      | PC2      | PC1      | PC0      |

| Port D | -         | -         | -         | -         | -         | -         | -        | PD8      | PD7      | PD6      | PD5      | PD4      | PD3      | PD2      | PD1      | PD0      |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9      | PE8      | -        | -        | -        | -        | -        | -        | -        | -        |

| Port F | -         | -         | -         | PF12      | PF11      | PF10      | -        | -        | -        | -        | PF5      | -        | -        | PF2      | PF1      | PF0      |

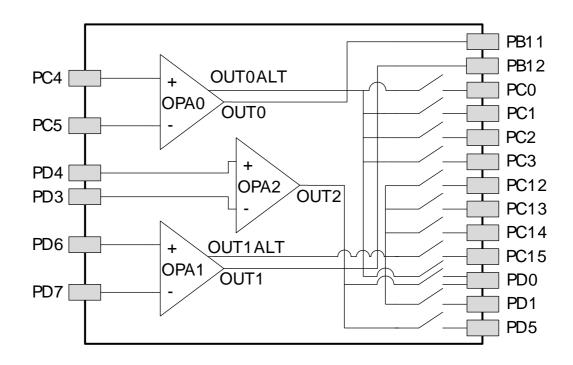

## **4.4 Opamp Pinout Overview**

The specific opamp terminals available in *EFM32GG332* is shown in Figure 4.2 (p. 56) .

Figure 4.2. Opamp Pinout

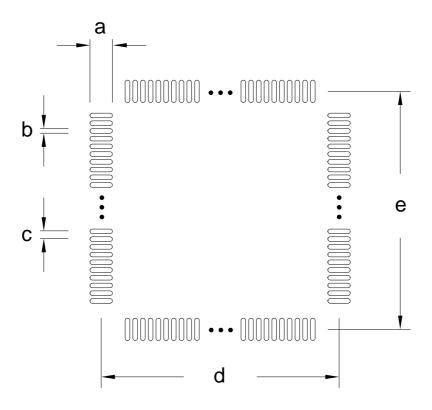

Figure 5.2. TQFP64 PCB Solder Mask

Table 5.2. QFP64 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 1.72      |

| b      | 0.42      |

| С      | 0.50      |

| d      | 11.50     |

| е      | 11.50     |

# **7 Revision History**

### 7.1 Revision 1.40

March 21st, 2016

Added clarification on conditions for INL<sub>ADC</sub> and DNL<sub>ADC</sub> parameters.

Reduced maximum and typical current consumption for all EM0 entries except 48 MHz in the Current Consumption table in the Electrical Characteristics section.

Increased maximum specifications for EM2 current, EM3 current, and EM4 current in the Current Consumption table in the Electrical Characteristics section.

Increased typical specification for EM2 and EM3 current at 85 C in the Current Consumption table in the Electrical Characteristics section.

Added EM2, EM3, and EM4 current consumption vs. temperature graphs.

Added a new EM2 entry and specified the existing specification is for EM0 for the BOD threshold on falling external supply voltage in the Power Management table in the Electrical Characteristics section.

Reduced maximum input leakage current in the GPIO table in the Electrical Characteristics section.

Added a maximum current consumption specification to the LFRCO table in the Electrical Characteristics section.

Added maximum specifications for the active current including references for two channels to the DAC table in the Electrical Characteristics section.

Increased the maximum specification for DAC offset voltage in the DAC table in the Electrical Characteristics section.

Increased the typical specifications for active current with FULLBIAS=1 and capacitive sense internal resistance in the ACMP table in the Electrical Characteristics section.

Added minimum and maximum specifications and updated the typical value for the VCMP offset voltage in the VCMP table in the Electrical Characteristics section.

Removed the maximum specification and reduced the typical value for hysteresis in the VCMP table in the Electrical Characteristics section.

Updated all graphs in the Electrical Characteristics section to display data for 2.0 V as the minimum voltage.

### **7.2 Revision 1.30**

May 23rd, 2014

Removed "preliminary" markings

Updated HFRCO figures.

Corrected single power supply voltage minimum value from 1.85V to 1.98V.

Updated Current Consumption information.

Updated Power Management information.

Updated power requirements in the Power Management section.

Removed minimum load capacitance figure and table. Added reference to application note.

Other minor corrections.

### **7.6 Revision 1.00**

September 11th, 2012

Updated the HFRCO 1 MHz band typical value to 1.2 MHz.

Updated the HFRCO 7 MHz band typical value to 6.6 MHz.

Other minor corrections.

### **7.7 Revision 0.98**

May 25th, 2012

Corrected EM3 current consumption in the Electrical Characteristics section.

### **7.8 Revision 0.96**

February 28th, 2012

Added reference to errata document.

Corrected TQFP64 package drawing.

Updated PCB land pattern, solder mask and stencil design.

### **7.9 Revision 0.95**

September 28th, 2011

Flash configuration for Giant Gecko is now 1024KB or 512KB. For flash sizes below 512KB, see the Leopard Gecko Family.

Corrected operating voltage from 1.8 V to 1.85 V.

Added rising POR level to Electrical Characteristics section.

Updated Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup.

Added Gain error drift and Offset error drift to ADC table.

Added Opamp pinout overview.

Added reference to errata document.

Corrected TQFP64 package drawing.

Updated PCB land pattern, solder mask and stencil design.

### 7.10 Revision 0.90

June 29th, 2011

## A Disclaimer and Trademarks

### A.1 Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

### A.2 Trademark Information

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

# **List of Figures**

| 2.1. Block Diagram                                                                                                                        | . 3 |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2. EFM32GG332 Memory Map with largest RAM and Flash sizes                                                                               | 9   |

| 3.1. EM2 current consumption. RTC prescaled to 1 Hz, 32.768 kHz LFRCO.                                                                    | 12  |

| 3.2. EM3 current consumption.                                                                                                             | 12  |

| 3.3. EM4 current consumption.                                                                                                             |     |

| 3.4. Typical Low-Level Output Current, 2V Supply Voltage                                                                                  | 17  |

| 3.5. Typical High-Level Output Current, 2V Supply Voltage                                                                                 |     |

| 3.6. Typical Low-Level Output Current, 3V Supply Voltage                                                                                  |     |

| 3.7. Typical High-Level Output Current, 3V Supply Voltage                                                                                 |     |

| 3.8. Typical Low-Level Output Current, 3.8V Supply Voltage                                                                                |     |

| 3.9. Typical High-Level Output Current, 3.8V Supply Voltage                                                                               |     |

| 3.10. Calibrated LFRCO Frequency vs Temperature and Supply Voltage                                                                        | 24  |

| 3.11. Calibrated HFRCO 1 MHz Band Frequency vs Supply Voltage and Temperature                                                             | 25  |

| 3.12. Calibrated HFRCO 7 MHz Band Frequency vs Supply Voltage and Temperature                                                             |     |

| 3.13. Calibrated HFRCO 11 MHz Band Frequency vs Supply Voltage and Temperature                                                            |     |

| 3.14. Calibrated HFRCO 14 MHz Band Frequency vs Supply Voltage and Temperature                                                            |     |

| 3.15. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature                                                            |     |

| 3.16. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature                                                            |     |

| 3.17. Integral Non-Linearity (INL)                                                                                                        | 32  |

| 3.18. Differential Non-Linearity (DNL)                                                                                                    | 33  |

| 3.19. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C                                                                                       |     |

| 3.20. ADC Integral Linearity Error vs Code, Vdd = 3V, Temp = 25°C                                                                         |     |

| 3.21. ADC Differential Linearity Error vs Code, Vdd = 3V, Temp = 25°C                                                                     |     |

| 3.22. ADC Absolute Offset, Common Mode = Vdd /2                                                                                           |     |

| 3.23. ADC Dynamic Performance vs Temperature for all ADC References, Vdd = 3V                                                             |     |

| 3.24. ADC Temperature sensor readout                                                                                                      |     |

| 3.25. OPAMP Common Mode Rejection Ratio                                                                                                   |     |

| 3.26. OPAMP Positive Power Supply Rejection Ratio                                                                                         |     |

| 3.27. OPAMP Negative Power Supply Rejection Ratio                                                                                         | 42  |

| 3.28. OPAMP Voltage Noise Spectral Density (Unity Gain) V <sub>out</sub> =1V                                                              | 42  |

| 3.29. OPAMP Voltage Noise Spectral Density (Non-Unity Gain) 3.30. ACMP Characteristics, Vdd = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1 | 42  |

| 3.30. ACMP Characteristics, Vdd = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1                                                             | 44  |

| 3.31. SPI Master Timing                                                                                                                   |     |

| 3.32. SPI Slave Timing                                                                                                                    |     |

| 4.1. EFM32GG332 Pinout (top view, not to scale)                                                                                           |     |

| 4.2. Opamp Pinout                                                                                                                         |     |

| 4.3. TQFP64                                                                                                                               |     |

| 5.1. TQFP64 PCB Land Pattern                                                                                                              |     |

| 5.2. TQFP64 PCB Solder Mask                                                                                                               |     |

| 5.3. TQFP64 PCB Stencil Design                                                                                                            |     |

| 6.1 Example Chip Marking (top view)                                                                                                       | 62  |

www.silabs.com/simplicity

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are not designed or authorized for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labse, Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA