# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 48MHz                                                                |

| Connectivity               | I <sup>2</sup> C, FlexIO, SPI, UART/USART, USB                       |

| Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                      |

| Number of I/O              | 30                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 8K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D 14x16b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 36-XFBGA                                                             |

| Supplier Device Package    | 36-XFBGA (3.5x3.5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl27z32vda4 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **1** Ordering information

The following chips are available for ordering.

| Product      |                          | Memory        |              | Pa           | Package |       | IO and ADC channel             |                            |

|--------------|--------------------------|---------------|--------------|--------------|---------|-------|--------------------------------|----------------------------|

| Part number  | Marking<br>(Line1/Line2) | Flash<br>(KB) | SRAM<br>(KB) | Pin<br>count | Package | GPIOs | GPIOs<br>(INT/HD) <sup>1</sup> | ADC<br>channels<br>(SE/DP) |

| MKL27Z64VLH4 | MKL27Z64 / VLH4          | 64            | 16           | 64           | LQFP    | 51    | 51/6                           | 17/2                       |

| MKL27Z32VLH4 | MKL27Z32 / VLH4          | 32            | 8            | 64           | LQFP    | 51    | 51/6                           | 17/2                       |

| MKL27Z64VDA4 | M27M6                    | 64            | 16           | 36           | XFBGA   | 30    | 30/6                           | 14/3                       |

| MKL27Z32VDA4 | M27M5                    | 32            | 8            | 36           | XFBGA   | 30    | 30/6                           | 14/3                       |

| MKL27Z64VFM4 | M27M6V                   | 64            | 16           | 32           | QFN     | 24    | 24/6                           | 8/0                        |

| MKL27Z32VFM4 | M27M5V                   | 32            | 8            | 32           | QFN     | 24    | 24/6                           | 8/0                        |

| MKL27Z64VMP4 | TBD                      | 64            | 16           | 64           | MAPBGA  | 51    | 51/6                           | 17/2                       |

| MKL27Z32VMP4 | TBD                      | 32            | 8            | 64           | MAPBGA  | 51    | 51/6                           | 17/2                       |

| MKL27Z64VFT4 | TBD                      | 64            | 16           | 48           | QFN     | 37    | 37/6                           | 15/1                       |

| MKL27Z32VFT4 | TBD                      | 32            | 8            | 48           | QFN     | 37    | 37/6                           | 15/1                       |

Table 1. Ordering information

1. INT: interrupt pin numbers; HD: high drive pin numbers

### NOTE

The 48 QFN and 64 MAPBGA packages supporting MKLx7ZxxVFT4 and MKLx7ZxxVMP4 part numbers for this product are not yet available. However, these packages are included in Package Your Way program for Kinetis MCUs. Visit Freescale.com/KPYW for more details.

## 2 Overview

The following figure shows the system diagram of this device

The PMC provides Run (Run), and Very Low Power Run (VLPR) configurations in ARM's Run operation mode. In these modes, the MCU core is active and can access all peripherals. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption. The configuration that matches the power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in ARM's Sleep operation mode. In these modes, even though the MCU core is inactive, all of the peripherals can be enabled and operate as programmed. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS), Low Leakage Stop (LLS), and Very Low Leakage Stop (VLLS) configurations in ARM's Deep Sleep operational mode. In these modes, the MCU core and most of the peripherals are disabled. Depending on the requirements of the application, different portions of the analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up Interrupt Controller (AWIC), and the Low Leakage Wake-Up Controller (LLWU) are used to wake up the MCU from low power states. The NVIC is used to wake up the MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU core from STOP and VLPS modes. The LLWU is used to wake up the MCU core from LLS and VLLSx modes.

For additional information regarding operational modes, power management, the NVIC, AWIC, or the LLWU, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the various operational modes and the modules that can wake MCU from low power modes.

| Core mode  | Device mode         | Descriptions                                                                                                                                                                        |

|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode   | Run                 | In Run mode, all device modules are operational.                                                                                                                                    |

|            | Very Low Power Run  | In VLPR mode, all device modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled.                                             |

| Sleep mode | Wait                | In Wait mode, all peripheral modules are operational. The MCU core is placed into Sleep mode.                                                                                       |

|            | Very Low Power Wait | In VLPW mode, all peripheral modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled. The MCU core is placed into Sleep mode. |

Table 6. Peripherals states in different operational modes

### 2.2.15 USB

This device contains one USB module which implements a USB2.0 full-speed compliant peripheral and interfaces to the on-chip USBFS transceiver. It implements keep-alive feature to avoid re-enumerating when exiting from low power modes and enables HIRC48M to allow crystal-less USB operation.

The USBFS has the following features:

- USB 1.1 and 2.0 compliant full-speed device controller

- 16 bidirectional end points

- DMA or FIFO data stream interfaces

- Low-power consumption

- HIRC48 with clock-recovery is supported to eliminate the 48 MHz crystal. It is used for USB device-only implementation.

- USB keeps alive in low power mode down to VLPS and is able to wake MCU from low power mode

## 2.2.16 FlexIO

The FlexIO is a highly configurable module providing a wide range of protocols including, but not limited to UART, I2C, SPI, I2S, Camera IF, LCD RGB, PWM/ Waveform generation. The module supports programmable baud rates independent of bus clock frequency, with automatic start/stop bit generation.

The FlexIO module has the following features:

- Functional in VLPR/VLPW/Stop/VLPS mode provided the clock it is using remains enabled

- Four 32-bit double buffered shift registers with transmit, receive, and data match modes, and continuous data transfer

- The timing of the shifter' shift, load and store events are controlled by the highly flexible 16-bit timer assigned to the shifter

- Two or more shifter can be concatenated to support large data transfer sizes

- Each 16-bit timers operates independently, supports for reset, enable and disable on a variety of internal or external trigger conditions with programmable trigger polarity

- Flexible pin configuration supporting output disabled, open drain, bidirectional output data and output mode

- Supports interrupt, DMA or polled transmit/receive operation

| Properties    | Abbreviation | Descriptions         |

|---------------|--------------|----------------------|

|               | Y            | Enabled <sup>2</sup> |

| Pin interrupt | Y            | Yes                  |

1. When I2C module is enabled and a pin is functional for I2C, this pin is (pseudo-) open drain enabled. When UART or LPUART module is enabled and a pin is functional for UART or LPUART, this pin is (pseudo-) open drain configurable.

2. PTA20 is a true open drain pin that must never be pulled above VDD.

### 4.3 Module Signal Description Tables

The following sections correlate the chip-level signal name with the signal name used in the module's chapter. They also briefly describe the signal function and direction.

### 4.3.1 Core modules

| Chip signal name | Module signal<br>name | Description                                                                                                               | I/O     |

|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|---------|

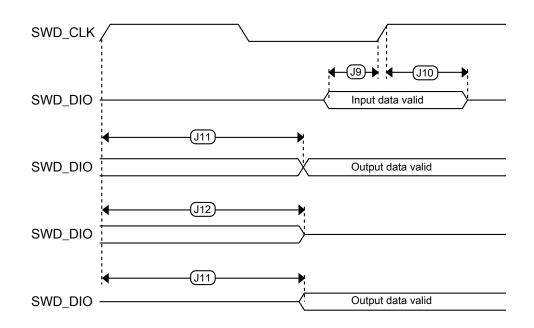

| SWD_DIO          | SWD_DIO               | Serial Wire Debug Data Input/Output                                                                                       | Input / |

|                  |                       | The SWD_DIO pin is used by an external debug tool for communication and device control. This pin is pulled up internally. | Output  |

| SWD_CLK          | SWD_CLK               | Serial Wire Clock                                                                                                         | Input   |

|                  |                       | This pin is the clock for debug logic when in the Serial Wire Debug mode. This pin is pulled down internally.             |         |

Table 9. SWD signal descriptions

### 4.3.2 System modules

#### Table 10. System signal descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                                        | I/O |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| NMI              |                       | Non-maskable interrupt<br><b>NOTE:</b> Driving the MMI signal low forces a non-maskable<br>interrupt, if the MMI function is selected on the<br>corresponding pin. | Ι   |

| RESET            | —                     | Reset bidirectional signal                                                                                                                                         | I/O |

| VDD              | —                     | MCU power                                                                                                                                                          | I   |

| VSS              | _                     | MCU ground                                                                                                                                                         | I   |

#### Pinouts

| Chip signal name | Module signal<br>name | Description             | I/O |

|------------------|-----------------------|-------------------------|-----|

| LPTMR0_ALT[3:1]  | LPTMR0_ALTn           | Pulse Counter Input pin | I   |

#### Table 19. LPTMR0 signal descriptions

#### Table 20. RTC signal descriptions

| Chip signal name        | Module signal<br>name | Description                         | I/O |

|-------------------------|-----------------------|-------------------------------------|-----|

| RTC_CLKOUT <sup>1</sup> | RTC_CLKOUT            | 1 Hz square-wave output or OSCERCLK | 0   |

1. RTC\_CLKOUT can also be driven with OSCERCLK via SIM control bit SIM\_SOPT[RCTCLKOUTSEL]

### 4.3.6 Communication interfaces Table 21. USB FS OTG Signal Descriptions

| Chip signal name | Module signal<br>name | Description                               | I/O |

|------------------|-----------------------|-------------------------------------------|-----|

| USB0_DM          | usb_dm                | USB D- analog data signal on the USB bus. | I/O |

| USB0_DP          | usb_dp                | USB D+ analog data signal on the USB bus. | I/O |

| USB_CLKIN        | _                     | Alternate USB clock input                 | I   |

#### Table 22. SPI0 signal descriptions

| Chip signal name | Module signal<br>name | Description                    | I/O |

|------------------|-----------------------|--------------------------------|-----|

| SPI0_MISO        | MISO                  | Master Data In, Slave Data Out | I/O |

| SPI0_MOSI        | MOSI                  | Master Data Out, Slave Data In | I/O |

| SPI0_SCLK        | SPSCK                 | SPI Serial Clock               | I/O |

| SPI0_PCS0        | SS                    | Slave Select                   | I/O |

#### Table 23. SPI1 signal descriptions

| Chip signal name | Module signal<br>name | Description                    | I/O |

|------------------|-----------------------|--------------------------------|-----|

| SPI1_MISO        | MISO                  | Master Data In, Slave Data Out | I/O |

| SPI1_MOSI        | MOSI                  | Master Data Out, Slave Data In | I/O |

| SPI1_SCLK        | SPSCK                 | SPI Serial Clock               | I/O |

| SPI1_PCS0        | SS                    | Slave Select                   | I/O |

| Chip signal name | Module signal<br>name | Description                                                     | I/O |

|------------------|-----------------------|-----------------------------------------------------------------|-----|

| I2C0_SCL         | SCL                   | Bidirectional serial clock line of the I <sup>2</sup> C system. | I/O |

| I2C0_SDA         | SDA                   | Bidirectional serial data line of the I <sup>2</sup> C system.  | I/O |

#### Table 24. I<sup>2</sup>C0 signal descriptions

#### Table 25. I<sup>2</sup>C1 signal descriptions

| name         |     | Description                                                     | I/O |

|--------------|-----|-----------------------------------------------------------------|-----|

| I2C1_SCL SCL |     | Bidirectional serial clock line of the I <sup>2</sup> C system. | I/O |

| I2C1_SDA     | SDA | Bidirectional serial data line of the I <sup>2</sup> C system.  | I/O |

#### Table 26. LPUART0 signal descriptions

| Chip signal name | Module signal<br>name | Description   | I/O |

|------------------|-----------------------|---------------|-----|

| LPUART0_TX       | TxD                   | Transmit data | I/O |

| LPUART0_RX       | RxD                   | Receive data  | I   |

#### Table 27. LPUART1 signal descriptions

| Chip signal name | Module signal<br>name | Description   | I/O |

|------------------|-----------------------|---------------|-----|

| LPUART1_TX       | TxD                   | Transmit data | I/O |

| LPUART1_RX       | RxD                   | Receive data  | I   |

#### Table 28. UART2 signal descriptions

| Chip signal name | Module signal<br>name | Description   | I/O |

|------------------|-----------------------|---------------|-----|

| UART2_TX         | TxD                   | Transmit data | 0   |

| UART2_RX         | RxD                   | Receive data  | I   |

#### Table 29. FlexIO signal descriptions

| Chip signal name         Module signal name           FXIO0 Dx         FXIO Dn (n=07)         B |                | Description                                                  | I/O |  |  |

|-------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------|-----|--|--|

| FXIO0_Dx                                                                                        | FXIO_Dn (n=07) | Bidirectional FlexIO Shifter<br>and Timer pin inputs/outputs | I/O |  |  |

NOTES:

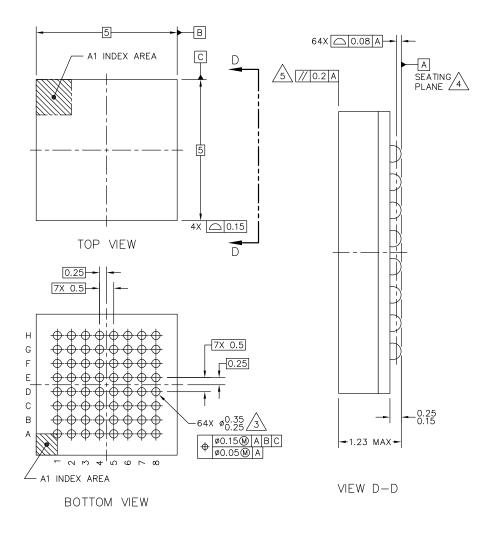

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

/3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

4. DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

5. PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

#### Figure 13. 64-pin MAPBGA package dimension

#### Pinouts

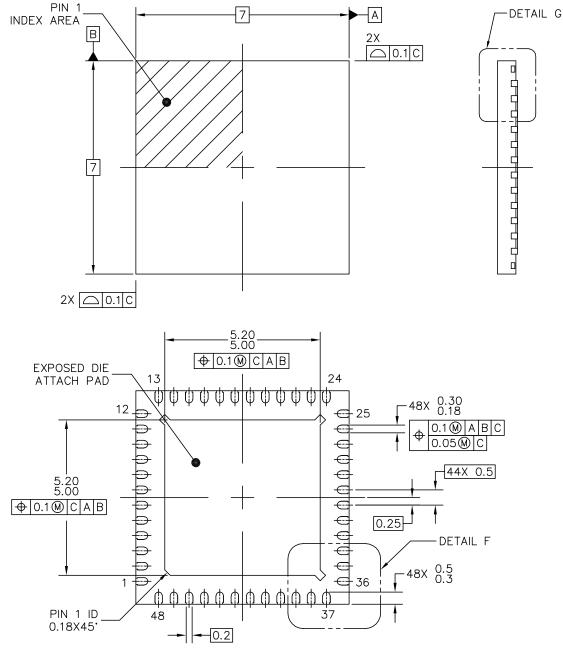

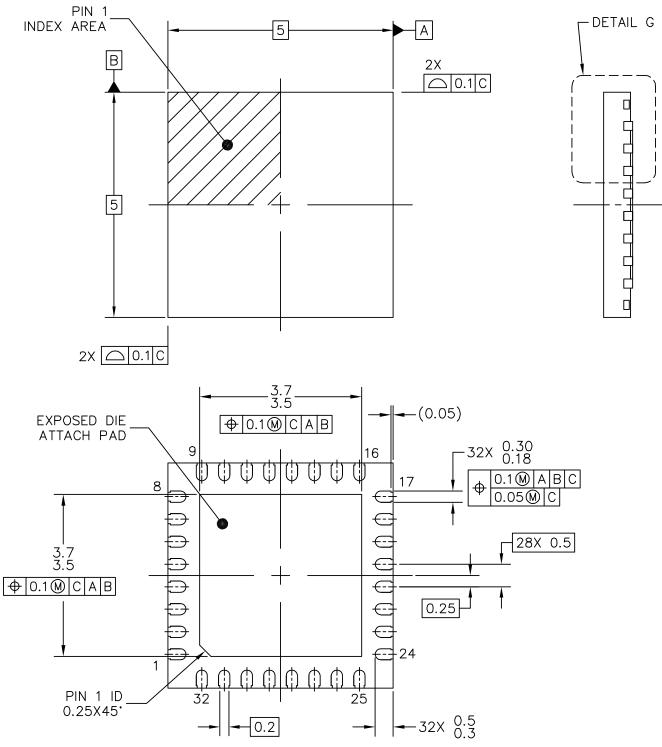

Figure 14. 48-pin QFN package dimension 1

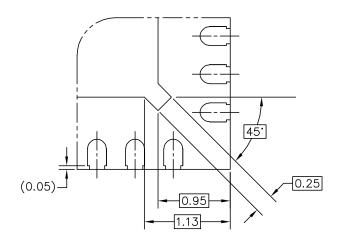

DETAIL F

DETAIL G VIEW ROTATED 90°CW

NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THIS IS A NON-JEDEC REGISTERED PACKAGE.

A COPLANARITY APPLIES TO LEADS AND DIE ATTACH FLAG.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

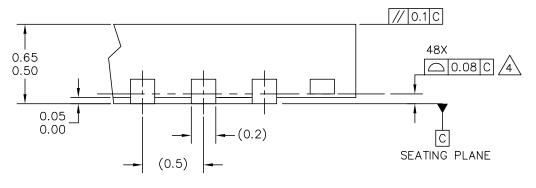

#### Figure 15. 48-pin QFN package dimension 2

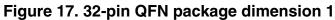

DETAIL G VIEW ROTATED 90°CW

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THIS IS A NON-JEDEC REGISTERED PACKAGE.

4 COPLANARITY APPLIES TO LEADS AND DIE ATTACH FLAG.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

#### Figure 18. 32-pin QFN package dimension 2

## **5** Electrical characteristics

### 5.1 Ratings

Electrical characteristics

### 5.1.1 Thermal handling ratings

Table 31. Thermal handling ratings

| Symbol                               | Description                    | Min. | Max. | Unit | Notes |

|--------------------------------------|--------------------------------|------|------|------|-------|

| T <sub>STG</sub> Storage temperature |                                | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub>                     | T October terrene la cel fre c |      | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

### 5.1.2 Moisture handling ratings

#### Table 32. Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level |      | 3    | _    | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

### 5.1.3 ESD handling ratings

#### Table 33. ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105 °C     | -100  | +100  | mA   | 3     |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

### 5.1.4 Voltage and current absolute operating ratings

Table 34. Voltage and current absolute operating ratings

| Symbol          | Description            | Min. | Max. | Unit |

|-----------------|------------------------|------|------|------|

| V <sub>DD</sub> | Digital supply voltage | -0.3 | 3.8  | V    |

| I <sub>DD</sub> | Digital supply current | —    | 120  | mA   |

| Description                    | Min.                           | Тур.           | Max.               | Unit                                                           | Notes                                                                  |

|--------------------------------|--------------------------------|----------------|--------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| <ul> <li>VLPS → RUN</li> </ul> | —                              | 7.5            | 8                  | μs                                                             |                                                                        |

| • STOP $\rightarrow$ RUN       |                                | 7.5            | 8                  | US                                                             |                                                                        |

| -                              | <ul> <li>VLPS → RUN</li> </ul> | • VLPS → RUN — | • VLPS → RUN — 7.5 | • VLPS $\rightarrow$ RUN $-$ 7.5 8<br>• STOP $\rightarrow$ RUN | • VLPS $\rightarrow$ RUN $-$ 7.5 8 $\mu$ s<br>• STOP $\rightarrow$ RUN |

Table 38. Power mode transition operating behaviors (continued)

### 5.2.2.5 Power consumption operating behaviors

The maximum values stated in the following table represent the characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

### NOTE

The while(1) test is executed with flash cache enabled.

| Symbol                | Description                                                                                                                                     | Min. | Тур. | Max.     | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>      | Analog supply current                                                                                                                           | _    | _    | See note | mA   | 1     |

| I <sub>DD_RUNCO</sub> | Running CoreMark in flash in compute<br>operation mode—48M HIRC mode, 48 MHz<br>core / 24 MHz flash, V <sub>DD</sub> = 3.0 V                    |      | 4.79 | 4.98     |      | 2     |

|                       | • at 25 °C                                                                                                                                      |      | _    |          | mA   |       |

|                       | • at 105 °C                                                                                                                                     |      | 4.94 | 5.14     |      |       |

| I <sub>DD_RUNCO</sub> | Running While(1) loop in flash in compute<br>operation mode—48M HIRC mode, 48 MHz<br>core / 24 MHz flash, V <sub>DD</sub> = 3.0 V               |      |      |          |      |       |

|                       | • at 25 °C                                                                                                                                      | —    | 2.73 | 2.87     | mA   |       |

|                       | • at 105 °C                                                                                                                                     |      | 2.9  | 3.05     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable<br>48 MHz core/24 MHz flash, $V_{DD} = 3.0 V$         |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | _    | 5.45 | 5.67     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | _    | 5.6  | 5.82     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in flash all peripheral clock disable,<br>24 MHz core/12 MHz flash, V <sub>DD</sub> = 3.0 V |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      |      |      |          |      |       |

|                       | • at 105 °C                                                                                                                                     | —    | 3.41 | 3.55     | mA   |       |

|                       |                                                                                                                                                 |      | 3.56 | 3.70     | mA   |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable<br>12 MHz core/6 MHz flash, $V_{DD} = 3.0 \text{ V}$  |      |      |          |      | 2     |

|                       |                                                                                                                                                 | _    | 2.37 | 2.49     | mA   |       |

Table 39.

Power consumption operating behaviors

| Symbol                     | Description                                                                                                                                                                                                                                                  | Temperature (°C) |       |     |     | Unit |     |    |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-----|-----|------|-----|----|

|                            |                                                                                                                                                                                                                                                              | -40              | 25    | 50  | 70  | 85   | 105 |    |

| IEREFSTEN4MHz              | [C: ] External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.                                                                                                                                             | 206              | 224   | 230 | 238 | 245  | 253 | μA |

| I <sub>EREFSTEN32KHz</sub> | External 32 kHz crystal clock adder by<br>means of the OSC0_CR[EREFSTEN                                                                                                                                                                                      |                  |       |     |     |      |     |    |

|                            | and EREFSTEN] bits. Measured by<br>entering all modes with the crystal                                                                                                                                                                                       | 440              | 490   | 540 | 560 | 570  | 580 |    |

|                            | enabled.<br>• VLLS1                                                                                                                                                                                                                                          | 440              | 490   | 540 | 560 | 570  | 580 |    |

|                            | • VLLS3                                                                                                                                                                                                                                                      | 490              | 490   | 540 | 560 | 570  | 680 |    |

|                            | LLS     VLPS                                                                                                                                                                                                                                                 | 510              | 560   | 560 | 560 | 610  | 680 |    |

|                            | • STOP                                                                                                                                                                                                                                                       | 510              | 560   | 560 | 560 | 610  | 680 | nA |

| I <sub>LPTMR</sub>         | LPTMR peripheral adder measured by placing the device in VLLS1 mode with LPTMR enabled using LPO.                                                                                                                                                            | 30               | 30    | 30  | 85  | 100  | 200 |    |

|                            |                                                                                                                                                                                                                                                              |                  |       |     |     |      |     | nA |

| I <sub>USBKPALV</sub>      | IDD adder measured by placing the device in VLPS mode with USB connection kept alive.                                                                                                                                                                        | _                | 1.353 | _   | _   | _    | _   |    |

|                            |                                                                                                                                                                                                                                                              |                  |       |     |     |      |     | m/ |

| I <sub>CMP</sub>           | CMP peripheral adder measured by<br>placing the device in VLLS1 mode with<br>CMP enabled using the 6-bit DAC and a<br>single external input for compare.<br>Includes 6-bit DAC power consumption.                                                            | 16               | 16    | 16  | 16  | 16   | 16  | μA |

| I <sub>RTC</sub>           | RTC peripheral adder measured by<br>placing the device in VLLS1 mode with<br>external 32 kHz crystal enabled by<br>means of the RTC_CR[OSCE] bit and<br>the RTC ALARM set for 1 minute.<br>Includes ERCLK32K (32 kHz external<br>crystal) power consumption. | 430              | 500   | 500 | 530 | 530  | 760 | nA |

| I <sub>UART</sub>          | UART peripheral adder measured by<br>placing the device in STOP or VLPS<br>mode with selected clock source waiting<br>for RX data at 115200 baud rate.<br>Includes selected clock source power<br>consumption.                                               |                  |       |     |     |      |     |    |

|                            |                                                                                                                                                                                                                                                              | 96               | 96    | 96  | 96  | 96   | 96  | μA |

| Table 40  | Low power mod | o poriphoral add  | ore — typical value | (continued) |

|-----------|---------------|-------------------|---------------------|-------------|

| Table 40. | Low power mou | e periprierai aud | ers — typical value | (continued) |

| Board type        | Symbol            | Description                                                                                              | 32 QFN | 36<br>XFBGA | 64 LQFP | Unit | Notes     |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|--------|-------------|---------|------|-----------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 101    | 81.5        | 71      | °C/W | 1, 2, 3   |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 33     | 54.7        | 53      | °C/W | 1, 2, 3,4 |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 84     | 71.3        | 60      | °C/W | 1, 4, 5   |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 28     | 50.0        | 47      | °C/W | 1, 4, 5   |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 13     | 58.0        | 35      | °C/W | 6         |

| —                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 1.7    | 45.3        | 21      | °C/W | 7         |

| _                 | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 3      | 1.2         | 5       | °C/W | 8         |

| _                 | Ψ <sub>JB</sub>   | Thermal characterization<br>parameter, junction to package<br>bottom (natural convection)                | -      | 44.5        | -       | °C/W | 9         |

#### Table 45. Thermal attributes

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Per JEDEC JESD51-6 with the board horizontal.

- 5. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 6. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 7. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 8. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 9. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

## 5.3 Peripheral operating requirements and behaviors

### 5.3.1 Core modules

Figure 23. Serial wire data timing

### 5.3.2 System modules

There are no specifications necessary for the device's system modules.

### 5.3.3 Clock modules

#### 5.3.3.1 MCG-Lite specifications Table 47. IRC48M specifications

| Symbol                     | Description                                                                                     | Min. | Тур.  | Max.  | Unit                 | Notes |

|----------------------------|-------------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| I <sub>DD48M</sub>         | Supply current                                                                                  | —    | 400   | 500   | μA                   |       |

| f <sub>irc48m</sub>        | Internal reference frequency                                                                    | —    | 48    | _     | MHz                  |       |

| Δf <sub>irc48m_ol_lv</sub> | Open loop total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over temperature | _    | ± 0.5 | ± 1.5 | %f <sub>irc48m</sub> |       |

| $\Delta f_{irc48m_ol_hv}$  | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over temperature | _    | ± 0.5 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

| ∆f <sub>irc48m_cl</sub>    | Closed loop total deviation of IRC48M frequency over voltage and temperature                    | _    | _     | ± 0.1 | %f <sub>host</sub>   | 2     |

**Electrical characteristics**

| Symbol              | Description                    | Conditions <sup>1</sup>                                     | Min. | Typ. <sup>2</sup>      | Max. | Unit  | Notes                                                                        |

|---------------------|--------------------------------|-------------------------------------------------------------|------|------------------------|------|-------|------------------------------------------------------------------------------|

|                     |                                | • Avg = 32                                                  |      |                        |      |       |                                                                              |

| SFDR                | Spurious free<br>dynamic range | <ul><li>16-bit differential mode</li><li>Avg = 32</li></ul> | 82   | 95                     |      | dB    | 7                                                                            |

|                     |                                | <ul><li>16-bit single-ended mode</li><li>Avg = 32</li></ul> | 78   | 90                     | —    | dB    |                                                                              |

| EIL                 | Input leakage<br>error         |                                                             |      | $I_{ln} \times R_{AS}$ |      | mV    | I <sub>In</sub> =<br>leakage<br>current                                      |

|                     |                                |                                                             |      |                        |      |       | (refer to<br>the MCU's<br>voltage<br>and<br>current<br>operating<br>ratings) |

|                     | Temp sensor<br>slope           | Across the full temperature range of the device             | 1.55 | 1.62                   | 1.69 | mV/°C | 8                                                                            |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage         | 25 °C                                                       | 706  | 716                    | 726  | mV    | 8                                                                            |

#### Table 56. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

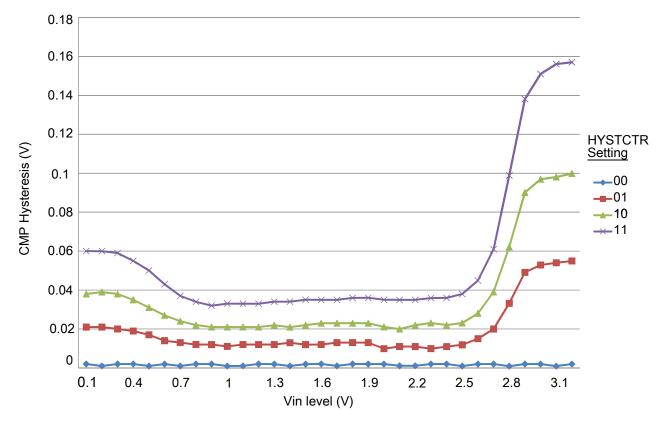

Figure 28. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

### 5.4 Timers

See General switching specifications.

### 5.5 Communication interfaces

### 5.5.1 USB electrical specifications

The USB electricals for the USB device module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit usb.org .

### NOTE

The IRC48M meets the USB jitter specifications for certification in Device mode when the USB clock recovery mode is enabled.

This device cannot support Host mode operation.

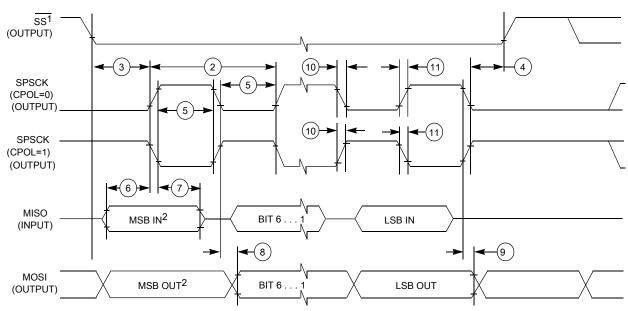

### 5.5.2 SPI switching specifications

The Serial Peripheral Interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. See the SPI chapter of the chip's Reference Manual for information about the modified transfer formats used for communicating with slower peripheral devices.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all SPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                     | Unit               | Note     |

|------|---------------------|--------------------------------|---------------------------|--------------------------|--------------------|----------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2   | Hz                 | 1        |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x                   | ns                 | 2        |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |          |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                        | t <sub>SPSCK</sub> | _        |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       |                          | t <sub>SPSCK</sub> |          |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x                   | ns                 | —        |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |          |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        | —                        | ns                 | <u> </u> |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | —                        | ns                 |          |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 15                       | ns                 |          |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | —                        | ns                 |          |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25 | ns                 |          |

|      | t <sub>FI</sub>     | Fall time input                |                           |                          |                    |          |

| 11   | t <sub>RO</sub>     | Rise time output               | -                         | 25                       | ns                 | —        |

|      | t <sub>FO</sub>     | Fall time output               |                           |                          |                    |          |

Table 61. SPI master mode timing on slew rate disabled pads

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

2.  $t_{periph} = 1/f_{periph}$

#### Table 62. SPI master mode timing on slew rate enabled pads

| Num. | Symbol             | Description            | Min.                      | Max.                          | Unit               | Note |

|------|--------------------|------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>    | Frequency of operation | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub> | SPSCK period           | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>  | Enable lead time       | 1/2                       |                               | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>   | Enable lag time        | 1/2                       |                               | t <sub>SPSCK</sub> | _    |

| Num. | Symbol          | Description                    | Min.                     | Max.                          | Unit | Note |

|------|-----------------|--------------------------------|--------------------------|-------------------------------|------|------|

| 5    | twspsck         | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | 1024 x<br>t <sub>periph</sub> | ns   | _    |

| 6    | t <sub>SU</sub> | Data setup time (inputs)       | 96                       | _                             | ns   | —    |

| 7    | t <sub>HI</sub> | Data hold time (inputs)        | 0                        | _                             | ns   | —    |

| 8    | t <sub>v</sub>  | Data valid (after SPSCK edge)  | —                        | 52                            | ns   | —    |

| 9    | t <sub>HO</sub> | Data hold time (outputs)       | 0                        | _                             | ns   | —    |

| 10   | t <sub>RI</sub> | Rise time input                | —                        | t <sub>periph</sub> - 25      | ns   | —    |

|      | t <sub>FI</sub> | Fall time input                |                          |                               |      |      |

| 11   | t <sub>RO</sub> | Rise time output               | _                        | 36                            | ns   | —    |

|      | t <sub>FO</sub> | Fall time output               |                          |                               |      |      |

Table 62. SPI master mode timing on slew rate enabled pads (continued)

- 1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

- 2.  $t_{periph} = 1/f_{periph}$

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 29. SPI master mode timing (CPHA = 0)