# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, FlexIO, SPI, UART/USART, USB                        |

| Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                       |

| Number of I/O              | 30                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 14x16b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 36-XFBGA                                                              |

| Supplier Device Package    | 36-XFBGA (3.5x3.5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl27z64vda4r |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Voltage range: 1.71 to 3.6 V

- Flash write voltage range: 1.71 to 3.6 V

- Temperature range: -40 to 105 °C

#### Packages

- 64 LQFP 10mm x 10mm, 0.5mm pitch, 1.6mm thickness

- 36 XFBGA 3.5mm x 3.5mm, 0.5mm pitch, 0.5mm thickness

- 32 QFN 5mm x 5mm, 0.5mm pitch, 0.65mm thickness

- 64 MAPBGA 5mm x 5mm, 0.5mm pitch, 1.23mm thickness (Package Your Way)

- 48 QFN 7mm x 7mm, 0.5mm pitch, 0.65mm thickness (Package Your Way)

#### Security and Integrity

- 80-bit unique identification number per chip

- Advanced flash security

- Hardware CRC module

#### I/O

• Up to 51 general-purpose input/output pins

#### Low Power

- Down to 46 µA/MHz in very low power run mode

- Down to 1.68 µA in stop mode (RAM + RTC

- retained)

- · Six flexible static modes

#### NOTE

The 48 QFN and 64 MAPBGA packages supporting MKLx7ZxxVFT4 and MKLx7ZxxVMP4 part numbers for this product are not yet available. However, these packages are included in Package Your Way program for Kinetis MCUs. Visit Freescale.com/KPYW for more details.

#### **Related Resources**

| Туре                | Description                                                                                                                      | Resource                     |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Selector Guide      | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector. | Solution Advisor             |

| Product Brief       | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.   | KL2xPB <sup>1</sup>          |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                 | KL27P64M48SF2RM <sup>1</sup> |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                                       | KL27P64M48SF2 <sup>1</sup>   |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.                         | xN87M <sup>2</sup>           |

| Package             | Package dimensions are provided in package drawings.                                                                             | XFBGA 36-pin: 98ASA00708D    |

| drawing             |                                                                                                                                  | LQFP 64-pin: 98ASS23234W     |

|                     |                                                                                                                                  | QFN 32-pin: 98ASA00615D      |

|                     |                                                                                                                                  | QFN 48-pin: 98ASA00616D      |

|                     |                                                                                                                                  | MAPBGA 64-pin: 98ASA00420D   |

- 1. To find the associated resource, go to http://www.freescale.com and perform a search using this term.

- To find the associated resource, go to http://www.freescale.com and perform a search using this term with the "x" replaced by the revision of the device you are using.

The PMC provides Run (Run), and Very Low Power Run (VLPR) configurations in ARM's Run operation mode. In these modes, the MCU core is active and can access all peripherals. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption. The configuration that matches the power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in ARM's Sleep operation mode. In these modes, even though the MCU core is inactive, all of the peripherals can be enabled and operate as programmed. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS), Low Leakage Stop (LLS), and Very Low Leakage Stop (VLLS) configurations in ARM's Deep Sleep operational mode. In these modes, the MCU core and most of the peripherals are disabled. Depending on the requirements of the application, different portions of the analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up Interrupt Controller (AWIC), and the Low Leakage Wake-Up Controller (LLWU) are used to wake up the MCU from low power states. The NVIC is used to wake up the MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU core from STOP and VLPS modes. The LLWU is used to wake up the MCU core from LLS and VLLSx modes.

For additional information regarding operational modes, power management, the NVIC, AWIC, or the LLWU, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the various operational modes and the modules that can wake MCU from low power modes.

| Core mode  | Device mode         | Descriptions                                                                                                                                                                        |

|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode   | Run                 | In Run mode, all device modules are operational.                                                                                                                                    |

|            | Very Low Power Run  | In VLPR mode, all device modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled.                                             |

| Sleep mode | Wait                | In Wait mode, all peripheral modules are operational. The MCU core is placed into Sleep mode.                                                                                       |

|            | Very Low Power Wait | In VLPW mode, all peripheral modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled. The MCU core is placed into Sleep mode. |

Table 6. Peripherals states in different operational modes

| LLWU pin  | Module source or pin name |

|-----------|---------------------------|

| LLWU_P5   | PTB0                      |

| LLWU_P6   | PTC1                      |

| LLWU_P7   | PTC3                      |

| LLWU_P8   | PTC4                      |

| LLWU_P9   | PTC5                      |

| LLWU_P10  | PTC6                      |

| LLWU_P14  | PTD4                      |

| LLWU_P15  | PTD6                      |

| LLWU_M0IF | LPTMR0                    |

| LLWU_M1IF | CMP0                      |

| LLWU_M2IF | Reserved                  |

| LLWU_M3IF | Reserved                  |

| LLWU_M4IF | Reserved                  |

| LLWU_M5IF | RTC alarm                 |

| LLWU_M6IF | Reserved                  |

| LLWU_M7IF | RTC seconds               |

Table 7. Wakeup source

## 2.1.10 Debug controller

This device supports standard ARM 2-pin SWD debug port. It provides register and memory accessibility from the external debugger interface, basic run/halt control plus 2 breakpoints and 2 watchpoints.

It also supports trace function with the Micro Trace Buffer (MTB), which provides a simple execution trace capability for the Cortex-M0+ processor.

# 2.1.11 COP

The COP monitors internal system operation and forces a reset in case of failure. It can run from bus clock, LPO, 8/2 MHz internal oscillator or external crystal oscillator. Optional window mode can detect deviations in program flow or system frequency.

The COP has the following features:

- Support multiple clock input, 1 kHz clock(LPO), bus clock, 8/2 MHz internal reference clock, external crystal oscillator

- Can work in Stop/VLPS and Debug mode

# 2.2.6 CMP

The device contains one high-speed comparator and two 8-input multiplexers for both the inverting and non-inverting inputs of the comparator. Each CMP input channel connects to both muxes.

The CMP includes one 6-bit DAC, which provides a selectable voltage reference for various user application cases. Besides, the CMP also has several module-to-module interconnects in order to facilitate ADC triggering, TPM triggering, and interfaces.

The CMP has the following features:

- Inputs may range from rail to rail

- Programmable hysteresis control

- Selectable interrupt on rising-edge, falling-edge, or both rising or falling edges of the comparator output

- Selectable inversion on comparator output

- Capability to produce a wide range of outputs such as sampled, digitally filtered

- External hysteresis can be used at the same time that the output filter is used for internal functions

- Two software selectable performance levels: shorter propagation delay at the expense of higher power and Low power with longer propagation delay

- DMA transfer support

- Functional in all modes of operation except in VLLS0 mode

- The filter functions are not available in Stop, VLPS, LLS, or VLLSx modes

- Integrated 6-bit DAC with selectable supply reference source and can be power down to conserve power

- Two 8-to-1 channel mux

# 2.2.7 RTC

The RTC is an always powered-on block that remains active in all low power modes. The time counter within the RTC is clocked by a 32.768 kHz clock sourced from an external crystal using the oscillator or clock directly from RTC\_CLKIN pin.

RTC is reset on power-on reset, and a software reset bit in RTC can also initialize all RTC registers.

The RTC module has the following features

• 32-bit seconds counter with roll-over protection and 32-bit alarm

- Full-duplex or single-wire bidirectional mode

- Programmable transmit bit rate

- Double-buffered transmit and receive data register

- Serial clock phase and polarity options

- Slave select output

- Mode fault error flag with CPU interrupt capability

- Control of SPI operation during wait mode

- Selectable MSB-first or LSB-first shifting

- Programmable 8- or 16-bit data transmission length

- Receive data buffer hardware match feature

- 64-bit FIFO mode for high speed/large amounts of data transfers

- Support DMA

# 2.2.14 I2C

This device contains two I2C modules, which support up to 1 Mbits/s by dual buffer features, and address match to wake MCU from the low power mode.

I2C modules support DMA transfer, and the interrupt condition can trigger DMA request when DMA function is enabled.

The I2C modules have the following features:

- Support for system management bus (SMBus) Specification, version 2

- Software programmable for one of 64 different serial clock frequencies

- Software-selectable acknowledge bit

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation and detection

- Repeated START signal generation and detection

- Acknowledge bit generation and detection

- Bus busy detection

- General call recognition

- 10-bit address extension

- Programmable input glitch filter

- Low power mode wakeup on slave address match

- Range slave address support

- DMA support

- Double buffering support to achieve higher baud rate

# 2.2.17 Port control and GPIO

The Port Control and Interrupt (PORT) module provides support for port control, digital filtering, and external interrupt functions. The GPIO data direction and output data registers control the direction and output data of each pin when the pin is configured for the GPIO function. The GPIO input data register displays the logic value on each pin when the pin is configured for any digital function, provided the corresponding Port Control and Interrupt module for that pin is enabled.

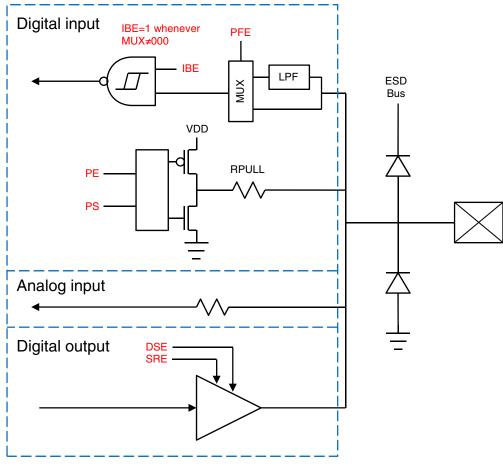

The following figure shows the basic I/O pad structure. This diagram applies to all I/O pins except PTA20/RESET\_b and those configured as pseudo open-drain outputs. PTA20/RESET\_b is a true open-drain pin without p-channel output driver or diode to the ESD bus. Pseudo open-drain pins have the p-channel output driver disabled when configured for open-drain operation. None of the I/O pins, including open-drain and pseudo open-drain pins, are allowed to go above VDD.

Figure 4. I/O simplified block diagram

The PORT module has the following features:

• all PIN support interrupt enable .

- Configurable edge(rising,falling,both) or level sensitive interrupt type

- Support DMA request

- Asynchronous wake-up in low-power modes

- Configurable pullup, pulldown, and pull-disable on select pins

- Configurable high and low drive strength on selected pins

- Configurable fast and slow slew rates on selected pins

- Configurable passive filter on selected pins

- Individual mux control field supporting analog or pin disabled, GPIO, and up to chip-specific digital functions

- Pad configuration fields are functional in all digital pin muxing modes.

The GPIO module has the following features:

- Port Data Input register visible in all digital pin-multiplexing modes

- Port Data Output register with corresponding set/clear/toggle registers

- Port Data Direction register

- GPIO support single-cycle access via fast GPIO.

# 3 Memory map

This device contains various memories and memory-mapped peripherals which are located in a 4 GB memory space. The following figure shows the system memory and peripheral locations

| 64<br>LQFP | 36<br>XFB<br>GA | 32<br>QFN | 48<br>QFN | 64<br>MAP<br>BGA | Pin Name                       | Default   | ALT0      | ALT1                           | ALT2           | ALT3           | ALT4                 | ALT5      | ALT6            | ALT7    |

|------------|-----------------|-----------|-----------|------------------|--------------------------------|-----------|-----------|--------------------------------|----------------|----------------|----------------------|-----------|-----------------|---------|

| 20         | _               | _         | 15        | H4               | PTE24                          | DISABLED  |           | PTE24                          |                | TPM0_CH0       |                      | I2C0_SCL  |                 |         |

| 21         | -               | _         | 16        | H5               | PTE25                          | DISABLED  |           | PTE25                          |                | TPM0_CH1       |                      | I2C0_SDA  |                 |         |

| 22         | F3              | 10        | 17        | D3               | PTA0                           | SWD_CLK   |           | PTA0                           |                | TPM0_CH5       |                      |           |                 | SWD_CLK |

| 23         | F4              | 11        | 18        | D4               | PTA1                           | DISABLED  |           | PTA1                           | LPUART0_<br>RX | TPM2_CH0       |                      |           |                 |         |

| 24         | E4              | 12        | 19        | E5               | PTA2                           | DISABLED  |           | PTA2                           | LPUART0_<br>TX | TPM2_CH1       |                      |           |                 |         |

| 25         | E5              | 13        | 20        | D5               | PTA3                           | SWD_DIO   |           | PTA3                           | I2C1_SCL       | TPM0_CH0       |                      |           |                 | SWD_DIO |

| 26         | F5              | 14        | 21        | G5               | PTA4                           | NMI_b     |           | PTA4                           | I2C1_SDA       | TPM0_CH1       |                      |           |                 | NMI_b   |

| 27         | _               | -         | -         | F5               | PTA5                           | DISABLED  |           | PTA5                           | USB_CLKIN      | TPM0_CH2       |                      |           |                 |         |

| 28         | _               | _         | -         | H6               | PTA12                          | DISABLED  |           | PTA12                          |                | TPM1_CH0       |                      |           |                 |         |

| 29         | _               | -         | -         | G6               | PTA13                          | DISABLED  |           | PTA13                          |                | TPM1_CH1       |                      |           |                 |         |

| 30         | C3              | 15        | 22        | G7               | VDD                            | VDD       | VDD       |                                |                |                |                      |           |                 |         |

| 31         | C4              | 16        | 23        | H7               | VSS                            | VSS       | VSS       |                                |                |                |                      |           |                 |         |

| 32         | F6              | 17        | 24        | H8               | PTA18                          | EXTAL0    | EXTAL0    | PTA18                          |                | lpuart1_<br>RX | TPM_<br>CLKIN0       |           |                 |         |

| 33         | E6              | 18        | 25        | G8               | PTA19                          | XTAL0     | XTAL0     | PTA19                          |                | LPUART1_<br>TX | TPM_<br>CLKIN1       |           | LPTMR0_<br>ALT1 |         |

| 34         | D5              | 19        | 26        | F8               | PTA20                          | RESET_b   |           | PTA20                          |                |                |                      |           |                 | RESET_b |

| 35         | D6              | 20        | 27        | F7               | PTB0/<br>LLWU_P5               | ADC0_SE8  | ADC0_SE8  | PTB0/<br>LLWU_P5               | I2C0_SCL       | TPM1_CH0       | SPI1_MOSI            | SPI1_MISO |                 |         |

| 36         | C6              | 21        | 28        | F6               | PTB1                           | ADC0_SE9  | ADC0_SE9  | PTB1                           | I2C0_SDA       | TPM1_CH1       | SPI1_MISO            | SPI1_MOSI |                 |         |

| 37         | -               | -         | 29        | E7               | PTB2                           | ADC0_SE12 | ADC0_SE12 | PTB2                           | I2C0_SCL       | TPM2_CH0       |                      |           |                 |         |

| 38         | _               | _         | 30        | E8               | PTB3                           | ADC0_SE13 | ADC0_SE13 | PTB3                           | I2C0_SDA       | TPM2_CH1       |                      |           |                 |         |

| 39         | -               | -         | 31        | E6               | PTB16                          | DISABLED  |           | PTB16                          | SPI1_MOSI      | LPUART0_<br>RX | TPM_<br>CLKIN0       | SPI1_MISO |                 |         |

| 40         | -               | -         | 32        | D7               | PTB17                          | DISABLED  |           | PTB17                          | SPI1_MISO      | LPUART0_<br>TX | TPM_<br>CLKIN1       | SPI1_MOSI |                 |         |

| 41         | _               | _         | _         | D6               | PTB18                          | DISABLED  |           | PTB18                          |                | TPM2_CH0       |                      |           |                 |         |

| 42         | -               | -         | -         | C7               | PTB19                          | DISABLED  |           | PTB19                          |                | TPM2_CH1       |                      |           |                 |         |

| 43         | -               | -         | 33        | D8               | PTC0                           | ADC0_SE14 | ADC0_SE14 | PTC0                           |                | EXTRG_IN       | audioUSB_<br>SOF_OUT | CMP0_OUT  |                 |         |

| 44         | C5              | 22        | 34        | C6               | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | ADC0_SE15 | ADC0_SE15 | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | I2C1_SCL       |                | TPM0_CH0             |           |                 |         |

| 45         | B6              | 23        | 35        | B7               | PTC2                           | ADC0_SE11 | ADC0_SE11 | PTC2                           | I2C1_SDA       |                | TPM0_CH1             |           |                 |         |

| 46         | B5              | 24        | 36        | C8               | PTC3/<br>LLWU_P7               | DISABLED  |           | PTC3/<br>LLWU_P7               | SPI1_SCK       | lpuart1_<br>RX | TPM0_CH2             | CLKOUT    |                 |         |

| 47         | _               | —         | -         | E3               | VSS                            | VSS       | VSS       |                                |                |                |                      |           |                 |         |

| 48         | _               | -         | -         | E4               | VDD                            | VDD       | VDD       |                                |                |                |                      |           |                 |         |

| 49         | A6              | 25        | 37        | B8               | PTC4/<br>LLWU_P8               | DISABLED  |           | PTC4/<br>LLWU_P8               | SPI0_PCS0      | LPUART1_<br>TX | TPM0_CH3             | SPI1_PCS0 |                 |         |

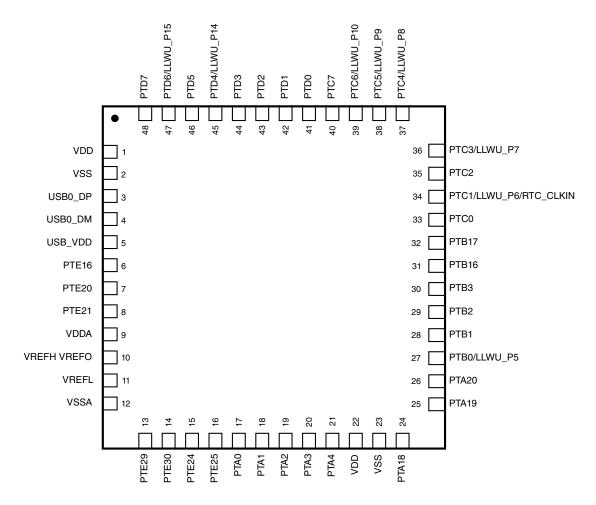

#### Pinouts

| Chip signal name | Module signal<br>name | Description             | I/O |

|------------------|-----------------------|-------------------------|-----|

| LPTMR0_ALT[3:1]  | LPTMR0_ALTn           | Pulse Counter Input pin | I   |

#### Table 19. LPTMR0 signal descriptions

### Table 20. RTC signal descriptions

| Chip signal name        | Module signal<br>name | Description                         | I/O |

|-------------------------|-----------------------|-------------------------------------|-----|

| RTC_CLKOUT <sup>1</sup> | RTC_CLKOUT            | 1 Hz square-wave output or OSCERCLK | 0   |

1. RTC\_CLKOUT can also be driven with OSCERCLK via SIM control bit SIM\_SOPT[RCTCLKOUTSEL]

### 4.3.6 Communication interfaces Table 21. USB FS OTG Signal Descriptions

| Chip signal name | Module signal<br>name | Description                               | I/O |

|------------------|-----------------------|-------------------------------------------|-----|

| USB0_DM          | usb_dm                | USB D- analog data signal on the USB bus. | I/O |

| USB0_DP          | usb_dp                | USB D+ analog data signal on the USB bus. | I/O |

| USB_CLKIN        | _                     | Alternate USB clock input                 | I   |

#### Table 22. SPI0 signal descriptions

| Chip signal name | Module signal<br>name | Description                    | I/O |

|------------------|-----------------------|--------------------------------|-----|

| SPI0_MISO        | MISO                  | Master Data In, Slave Data Out | I/O |

| SPI0_MOSI        | MOSI                  | Master Data Out, Slave Data In | I/O |

| SPI0_SCLK        | SPSCK                 | SPI Serial Clock               | I/O |

| SPI0_PCS0        | SS                    | Slave Select                   | I/O |

#### Table 23. SPI1 signal descriptions

| Chip signal name | Module signal<br>name | Description                    | I/O |

|------------------|-----------------------|--------------------------------|-----|

| SPI1_MISO        | MISO                  | Master Data In, Slave Data Out | I/O |

| SPI1_MOSI        | MOSI                  | Master Data Out, Slave Data In | I/O |

| SPI1_SCLK        | SPSCK                 | SPI Serial Clock               | I/O |

| SPI1_PCS0        | SS                    | Slave Select                   | I/O |

| Chip signal name | Module signal<br>name | Description                                                     | I/O |

|------------------|-----------------------|-----------------------------------------------------------------|-----|

| I2C0_SCL         | SCL                   | Bidirectional serial clock line of the I <sup>2</sup> C system. | I/O |

| I2C0_SDA         | SDA                   | Bidirectional serial data line of the I <sup>2</sup> C system.  | I/O |

### Table 24. I<sup>2</sup>C0 signal descriptions

### Table 25. I<sup>2</sup>C1 signal descriptions

| Chip signal name | Module signal<br>name | Description                                                     | I/O |

|------------------|-----------------------|-----------------------------------------------------------------|-----|

| I2C1_SCL         | SCL                   | Bidirectional serial clock line of the I <sup>2</sup> C system. | I/O |

| I2C1_SDA         | SDA                   | Bidirectional serial data line of the I <sup>2</sup> C system.  | I/O |

### Table 26. LPUART0 signal descriptions

| Chip signal name | Module signal<br>name | Description   | I/O |

|------------------|-----------------------|---------------|-----|

| LPUART0_TX       | TxD                   | Transmit data | I/O |

| LPUART0_RX       | RxD                   | Receive data  | I   |

### Table 27. LPUART1 signal descriptions

| Chip signal name | Module signal<br>name | Description   | I/O |

|------------------|-----------------------|---------------|-----|

| LPUART1_TX       | TxD                   | Transmit data | I/O |

| LPUART1_RX       | RxD                   | Receive data  | I   |

### Table 28. UART2 signal descriptions

| Chip signal name | Module signal<br>name | Description   | I/O |

|------------------|-----------------------|---------------|-----|

| UART2_TX         | TxD                   | Transmit data | 0   |

| UART2_RX         | RxD                   | Receive data  | I   |

### Table 29. FlexIO signal descriptions

| Chip signal name | Chip signal name Module signal name |                                                           | I/O |  |

|------------------|-------------------------------------|-----------------------------------------------------------|-----|--|

| FXIO0_Dx         | FXIO_Dn (n=07)                      | Bidirectional FlexIO Shifter and Timer pin inputs/outputs | I/O |  |

## NOTE

The 48 QFN package for this product is not yet available. However, it is included in Package Your Way program for Kinetis MCUs. Visit freescale.com/KPYW for more details.

The figure below shows the 64 MAPBGA pinouts.

## NOTE

The 64 MAPBGA package for this product is not yet available. However, it is included in Package Your Way program for Kinetis MCUs. Visit freescale.com/KPYW for more details.

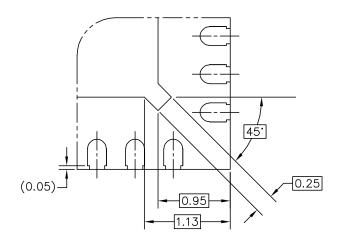

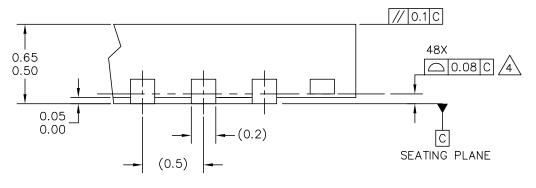

DETAIL F

DETAIL G VIEW ROTATED 90°CW

NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THIS IS A NON-JEDEC REGISTERED PACKAGE.

A COPLANARITY APPLIES TO LEADS AND DIE ATTACH FLAG.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

### Figure 15. 48-pin QFN package dimension 2

**Electrical characteristics**

### 5.2.2.1 Voltage and current operating requirements Table 35. Voltage and current operating requirements

| Symbol                             | Description                                                                                                                  | Min.                 | Max.                 | Unit | Notes |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>                    | Supply voltage                                                                                                               | 1.71                 | 3.6                  | V    | 1     |

| $USB_V_{DD}$                       | Supply voltage                                                                                                               | 3.0                  | 3.6                  | V    | 2     |

| V <sub>DDA</sub>                   | Analog supply voltage                                                                                                        | 1.71                 | 3.6                  | V    |       |

| V <sub>DD</sub> – V <sub>DDA</sub> | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                    | -0.1                 | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$                 | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                                                    | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>                    | Input high voltage                                                                                                           |                      |                      |      |       |

|                                    | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                  | $0.7 \times V_{DD}$  | _                    | V    |       |

|                                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                 | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>                    | Input low voltage                                                                                                            |                      |                      |      |       |

|                                    | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                  | _                    | $0.35 \times V_{DD}$ | V    |       |

|                                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                 | _                    | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>                   | Input hysteresis                                                                                                             | $0.06 \times V_{DD}$ | _                    | V    |       |

| I <sub>ICIO</sub>                  | IO pin negative DC injection current — single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V                               | -3                   | _                    | mA   | 3     |

| I <sub>ICcont</sub>                | Contiguous pin DC injection current —regional limit,<br>includes sum of negative injection currents of 16<br>contiguous pins | -25                  |                      | mA   |       |

|                                    | Negative current injection                                                                                                   |                      |                      |      |       |

| V <sub>ODPU</sub>                  | Open drain pullup voltage level                                                                                              | V <sub>DD</sub>      | V <sub>DD</sub>      | V    | 4     |

| V <sub>RAM</sub>                   | V <sub>DD</sub> voltage required to retain RAM                                                                               | 1.2                  | —                    | V    |       |

1. To use USB for 36XFBGA package, you need to limit the minimum value to 3.0V.

- 2. The power pin for USB and for other part of the chip is bonded together on the 36XFBGA package. The ripple limit for USB\_VDD is 100 mV.

- 3. All I/O pins are internally clamped to V<sub>SS</sub> through a ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> greater than V<sub>IO\_MIN</sub> (= V<sub>SS</sub>-0.3 V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as  $R = (V_{IO_MIN} V_{IN})/|I_{ICIO}|$ .

- 4. Open drain outputs must be pulled to  $V_{DD}$ .

### 5.2.2.2 LVD and POR operating requirements Table 36. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol            | Description                                                   | Min. | Тур. | Max. | Unit | Notes |

|-------------------|---------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>  | Falling V <sub>DD</sub> POR detect voltage                    | 0.8  | 1.1  | 1.5  | V    | —     |

| V <sub>LVDH</sub> | Falling low-voltage detect threshold — high range (LVDV = 01) | 2.48 | 2.56 | 2.64 | V    | _     |

|                   | Low-voltage warning thresholds — high range                   |      |      |      |      | 1     |

| Symbol             | Description                                                | Min. | Тур. | Max. | Unit | Notes |

|--------------------|------------------------------------------------------------|------|------|------|------|-------|

| V <sub>LVW1H</sub> | Level 1 falling (LVWV = 00)                                | 2.62 | 2.70 | 2.78 | V    |       |

| V <sub>LVW2H</sub> | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>            | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>            | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$        | • Level 4 falling (LVWV = 11)                              | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range  | _    | ±60  | _    | mV   | _     |

| V <sub>LVDL</sub>  | Falling low-voltage detect threshold — low range (LVDV=00) | 1.54 | 1.60 | 1.66 | V    | -     |

|                    | Low-voltage warning thresholds — low range                 |      |      |      |      | 1     |

| V <sub>LVW1L</sub> | • Level 1 falling (LVWV = 00)                              | 1.74 | 1.80 | 1.86 | v    |       |

| V <sub>LVW2L</sub> | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>            | 1.84 | 1.90 | 1.96 | v    |       |

| V <sub>LVW3L</sub> | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>            | 1.94 | 2.00 | 2.06 | v    |       |

| V <sub>LVW4L</sub> | • Level 4 falling (LVWV = 11)                              | 2.04 | 2.10 | 2.16 | v    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis — low range   | -    | ±40  | _    | mV   | -     |

| V <sub>BG</sub>    | Bandgap voltage reference                                  | 0.97 | 1.00 | 1.03 | V    | _     |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed     | 900  | 1000 | 1100 | μs   | -     |

Table 36. V<sub>DD</sub> supply LVD and POR operating requirements (continued)

1. Rising thresholds are falling threshold + hysteresis voltage

### 5.2.2.3 Voltage and current operating behaviors Table 37. Voltage and current operating behaviors

| Symbol           | Description                                                                                           | Min.                  | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------|-----------------------|------|------|-------|

| V <sub>OH</sub>  | Output high voltage — normal drive pad                                                                |                       |      |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -5 mA                                  | V <sub>DD</sub> – 0.5 | —    | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -2.5 mA                               | V <sub>DD</sub> – 0.5 | _    | V    |       |

| V <sub>OH</sub>  | Output high voltage — high drive pad                                                                  |                       |      |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -20 mA                                 | V <sub>DD</sub> – 0.5 | —    | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -10 \text{ mA}$ | V <sub>DD</sub> – 0.5 | _    | V    |       |

| I <sub>OHT</sub> | Output high current total for all ports                                                               |                       | 100  | mA   |       |

| V <sub>OL</sub>  | Output low voltage — normal drive pad                                                                 |                       |      |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 5 mA                                   | _                     | 0.5  | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 2.5 mA                                | _                     | 0.5  | V    |       |

| V <sub>OL</sub>  | Output low voltage — high drive pad                                                                   |                       |      |      | 1     |

|                  |                                                                                                       | _                     | 0.5  | V    |       |

**Electrical characteristics**

| Symbol                | Description                                                                                                                 | Min. | Тур.      | Max.       | Unit | Notes |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----------|------------|------|-------|

|                       | • at 50°C                                                                                                                   | -    | 2.21      | 2.80       | μA   |       |

|                       | • at 70°C                                                                                                                   | _    | 3.59      | 4.18       |      |       |

|                       | • at 85°C                                                                                                                   | _    | 8.02      | 9.47       |      |       |

|                       | • at 105 °C                                                                                                                 |      |           |            |      |       |

| I <sub>DD_VLLS0</sub> | Very-low-leakage stop mode 0 current all<br>peripheral disabled<br>(SMC_STOPCTRL[PORPO] = 0) at 3.0 V                       | _    | 262       | 360        |      |       |

|                       | <ul> <li>at 25 °C and below</li> </ul>                                                                                      | _    | 593       | 725        |      |       |

|                       | • at 50 °C                                                                                                                  | _    | 1430      | 2014       | nA   |       |

|                       | • at 70 °C                                                                                                                  | _    | 2930      | 3514       |      |       |

|                       | • at 85 °C                                                                                                                  |      | 7930      | 9895       |      |       |

|                       | • at 105 °C                                                                                                                 |      |           |            |      |       |

| I <sub>DD_VLLS0</sub> | Very-low-leakage stop mode 0 current all<br>peripheral disabled<br>(SMC_STOPCTRL[PORPO] = 1) at 3 V<br>• at 25 °C and below |      | 87<br>417 | 185<br>549 |      | 4     |

|                       | • at 50 °C                                                                                                                  | _    | 1230      | 1230       | nA   |       |

|                       | • at 70 °C                                                                                                                  | _    | 2720      | 3304       |      |       |

|                       | • at 85 °C                                                                                                                  |      | 7780      | 9745       |      |       |

|                       | • at 105 °C                                                                                                                 |      |           |            |      |       |

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

2. MCG\_Lite configured for HIRC mode. CoreMark benchmark compiled using IAR 7.10 with optimization level high, optimized for balanced.

3. RTC uses external 32 kHz crystal as clock source, and the current includes ERCLK32K power consumption.

4. No brownout

Table 40. Low power mode peripheral adders — typical value

| Symbol               | Description Temperature (°C)                                                                                                                                        |     |    | bol Description Temperature (°C) |    |    |     | Unit |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|----------------------------------|----|----|-----|------|

|                      |                                                                                                                                                                     | -40 | 25 | 50                               | 70 | 85 | 105 |      |

| I <sub>IRC8MHz</sub> | 8 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 8 MHz IRC enabled,<br>MCG_SC[FCRDIV]=000b,<br>MCG_MC[LIRC_DIV2]=000b. | 77  | 77 | 77                               | 77 | 77 | 77  | μA   |

| I <sub>IRC2MHz</sub> | 2 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 2 MHz IRC enabled,<br>MCG_SC[FCRDIV]=000b,<br>MCG_MC[LIRC_DIV2]=000b.     | 25  | 25 | 25                               | 25 | 25 | 25  | μΑ   |

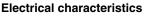

Figure 23. Serial wire data timing

# 5.3.2 System modules

There are no specifications necessary for the device's system modules.

# 5.3.3 Clock modules

#### 5.3.3.1 MCG-Lite specifications Table 47. IRC48M specifications

| Symbol                     | Description                                                                                     | Min. | Тур.  | Max.  | Unit                 | Notes |

|----------------------------|-------------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| I <sub>DD48M</sub>         | Supply current                                                                                  | —    | 400   | 500   | μA                   |       |

| f <sub>irc48m</sub>        | Internal reference frequency                                                                    | —    | 48    | _     | MHz                  |       |

| Δf <sub>irc48m_ol_lv</sub> | Open loop total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over temperature | _    | ± 0.5 | ± 1.5 | %f <sub>irc48m</sub> |       |

| $\Delta f_{irc48m_ol_hv}$  | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over temperature | _    | ± 0.5 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

| ∆f <sub>irc48m_cl</sub>    | Closed loop total deviation of IRC48M frequency over voltage and temperature                    | _    | _     | ± 0.1 | %f <sub>host</sub>   | 2     |

**Electrical characteristics**

| Symbol              | Description                    | Conditions <sup>1</sup>                                     | Min.                              | Typ. <sup>2</sup> | Max. | Unit  | Notes                                                                        |

|---------------------|--------------------------------|-------------------------------------------------------------|-----------------------------------|-------------------|------|-------|------------------------------------------------------------------------------|

|                     |                                | • Avg = 32                                                  |                                   |                   |      |       |                                                                              |

| SFDR                | Spurious free<br>dynamic range | <ul><li>16-bit differential mode</li><li>Avg = 32</li></ul> | 82                                | 95                |      | dB    | 7                                                                            |

|                     |                                | <ul><li>16-bit single-ended mode</li><li>Avg = 32</li></ul> | 78                                | 90                | —    | dB    |                                                                              |

| EIL                 | Input leakage<br>error         |                                                             | I <sub>In</sub> × R <sub>AS</sub> |                   |      | mV    | I <sub>In</sub> =<br>leakage<br>current                                      |

|                     |                                |                                                             |                                   |                   |      |       | (refer to<br>the MCU's<br>voltage<br>and<br>current<br>operating<br>ratings) |

|                     | Temp sensor<br>slope           | Across the full temperature range of the device             | 1.55                              | 1.62              | 1.69 | mV/°C | 8                                                                            |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage         | 25 °C                                                       | 706                               | 716               | 726  | mV    | 8                                                                            |

#### Table 56. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

This device cannot support Host mode operation.

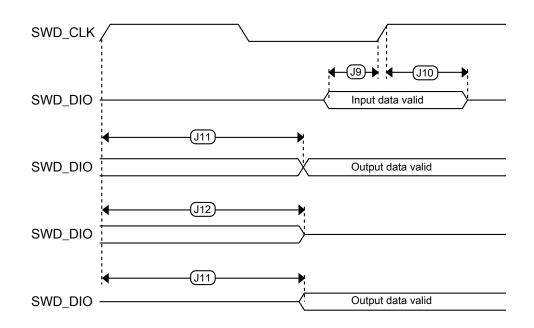

# 5.5.2 SPI switching specifications

The Serial Peripheral Interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. See the SPI chapter of the chip's Reference Manual for information about the modified transfer formats used for communicating with slower peripheral devices.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all SPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                     | Unit               | Note     |

|------|---------------------|--------------------------------|---------------------------|--------------------------|--------------------|----------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2   | Hz                 | 1        |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x                   | ns                 | 2        |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |          |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                        | t <sub>SPSCK</sub> | _        |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       |                          | t <sub>SPSCK</sub> |          |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x                   | ns                 | —        |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |          |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        | —                        | ns                 | <u> </u> |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | —                        | ns                 |          |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 15                       | ns                 |          |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | —                        | ns                 |          |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25 | ns                 |          |

|      | t <sub>FI</sub>     | Fall time input                |                           |                          |                    |          |

| 11   | t <sub>RO</sub>     | Rise time output               | -                         | 25                       | ns                 | —        |

|      | t <sub>FO</sub>     | Fall time output               |                           |                          |                    |          |

Table 61. SPI master mode timing on slew rate disabled pads

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

2.  $t_{periph} = 1/f_{periph}$

### Table 62. SPI master mode timing on slew rate enabled pads

| Num. | Symbol             | Description            | Min.                      | Max.                          | Unit               | Note |

|------|--------------------|------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>    | Frequency of operation | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub> | SPSCK period           | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>  | Enable lead time       | 1/2                       |                               | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>   | Enable lag time        | 1/2                       |                               | t <sub>SPSCK</sub> | _    |

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  |                          | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | —                        | t <sub>periph</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | _                        | ns                  | _    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2                        | —                        | ns                  | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 7                        | —                        | ns                  | _    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | _                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                        | 122                      | ns                  | _    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | _    |

| 12   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> - 25 | ns                  | _    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 36                       | ns                  | -    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

Table 64. SPI slave mode timing on slew rate enabled pads

1. For SPI0 f<sub>periph</sub> is the bus clock (f<sub>BUS</sub>). For SPI1 f<sub>periph</sub> is the system clock (f<sub>SYS</sub>).

- 2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL lines.

- 3. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 4. Input signal Slew = 10 ns and Output Load = 50 pF

- 5. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 6. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 7.  $C_b$  = total capacitance of the one bus line in pF.

To achieve 1MHz I2C clock rates, consider the following recommendations:

- To counter the effects of clock stretching, the I2C baud Rate select bits can be configured for faster than desired baud rate.

- Use high drive pad and DSE bit should be set in PORTx\_PCRn register.

- Minimize loading on the I2C SDA and SCL pins to ensure fastest rise times for the SCL line to avoid clock stretching.

- Use smaller pull up resistors on SDA and SCL to reduce the RC time constant.

| Characteristic                                                                               | Symbol                | Minimum                            | Maximum        | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|------------------------------------|----------------|------|

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                                  | 1 <sup>1</sup> | MHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 0.26                               |                | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 0.5                                | —              | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 0.26                               |                | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 0.26                               |                | μs   |

| Data hold time for I <sub>2</sub> C bus devices                                              | t <sub>HD</sub> ; DAT | 0                                  | —              | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 50                                 | —              | ns   |

| Rise time of SDA and SCL signals                                                             | t <sub>r</sub>        | 20 +0.1C <sub>b</sub>              | 120            | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | 20 +0.1C <sub>b</sub> <sup>2</sup> | 120            | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 0.26                               | —              | μs   |

| Bus free time between STOP and START condition                                               | t <sub>BUF</sub>      | 0.5                                |                | μs   |

| Pulse width of spikes that must be suppressed by the input filter                            | t <sub>SP</sub>       | 0                                  | 50             | ns   |

Table 66.

I <sup>2</sup>C 1Mbit/s timing

1. The maximum SCL clock frequency of 1 Mbit/s can support maximum bus loading when using the high drive pins across the full voltage range.

2.  $C_b$  = total capacitance of the one bus line in pF.