#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core Size32-Bit Single-CoreSpeed48MHzConnectivityi²C, FlexIO, SPI, UART/USART, USBPeripheralsDMA, I²S, PWM, WDTNumber of I/O51Program Memory Size64KB (64K × 8)Program Memory TypeFLASHEEPROM Size.RAM Size16K × 8Voltage - Supply (Vcc/Vdd)1,71 v ~ 3.6VData ConvertersMD 17x16bNemalityInternal                                                                              |                            |                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed48MHzConnectivityPC, FlexIO, SPI, UART/USART, USBPeripheralsDMA, I²S, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10) | Product Status             | Active                                                               |

| Speed48MHzConnectivityI²C, FlexIO, SPI, UART/USART, USBPeripheralsDMA, I²S, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                           | Core Processor             | ARM® Cortex®-M0+                                                     |

| ConnectivityIPC, FlexIO, SPI, UART/USART, USBPeripheralsDMA, IPS, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature4-0°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)              | Core Size                  | 32-Bit Single-Core                                                   |

| PeripheralsDMA, I²S, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                           | Speed                      | 48MHz                                                                |

| Number of I/O51Program Memory Size64KB (64K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size16K × 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                          | Connectivity               | I <sup>2</sup> C, FlexIO, SPI, UART/USART, USB                       |

| Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackageInternal                                                                                | Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                      |

| Program Memory TypeFLASHEEPROM Size-RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                        | Number of I/O              | 51                                                                   |

| EEPROM Size-RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                  | Program Memory Size        | 64KB (64K x 8)                                                       |

| RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                              | Program Memory Type        | FLASH                                                                |

| Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                             | EEPROM Size                | -                                                                    |

| Data ConvertersA/D 17x16bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                   | RAM Size                   | 16K x 8                                                              |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                            | Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Operating Temperature     -40°C ~ 105°C (TA)       Mounting Type     Surface Mount       Package / Case     64-LQFP       Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                          | Data Converters            | A/D 17x16b                                                           |

| Mounting Type     Surface Mount       Package / Case     64-LQFP       Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                             | Oscillator Type            | Internal                                                             |

| Package / Case     64-LQFP       Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                                   | Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Supplier Device Package 64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                        | Mounting Type              | Surface Mount                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                | Package / Case             | 64-LQFP                                                              |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl27z64vlh4                                                                                                                                                                                                                                                                                              | Supplier Device Package    | 64-LQFP (10x10)                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl27z64vlh4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1** Ordering information

The following chips are available for ordering.

| Pro          | duct                     | Mer           | nory         | Pa           | ckage   | IO and ADC channel |                                |                            |

|--------------|--------------------------|---------------|--------------|--------------|---------|--------------------|--------------------------------|----------------------------|

| Part number  | Marking<br>(Line1/Line2) | Flash<br>(KB) | SRAM<br>(KB) | Pin<br>count | Package | GPIOs              | GPIOs<br>(INT/HD) <sup>1</sup> | ADC<br>channels<br>(SE/DP) |

| MKL27Z64VLH4 | MKL27Z64 / VLH4          | 64            | 16           | 64           | LQFP    | 51                 | 51/6                           | 17/2                       |

| MKL27Z32VLH4 | MKL27Z32 / VLH4          | 32            | 8            | 64           | LQFP    | 51                 | 51/6                           | 17/2                       |

| MKL27Z64VDA4 | M27M6                    | 64            | 16           | 36           | XFBGA   | 30                 | 30/6                           | 14/3                       |

| MKL27Z32VDA4 | M27M5                    | 32            | 8            | 36           | XFBGA   | 30                 | 30/6                           | 14/3                       |

| MKL27Z64VFM4 | M27M6V                   | 64            | 16           | 32           | QFN     | 24                 | 24/6                           | 8/0                        |

| MKL27Z32VFM4 | M27M5V                   | 32            | 8            | 32           | QFN     | 24                 | 24/6                           | 8/0                        |

| MKL27Z64VMP4 | TBD                      | 64            | 16           | 64           | MAPBGA  | 51                 | 51/6                           | 17/2                       |

| MKL27Z32VMP4 | TBD                      | 32            | 8            | 64           | MAPBGA  | 51                 | 51/6                           | 17/2                       |

| MKL27Z64VFT4 | TBD                      | 64            | 16           | 48           | QFN     | 37                 | 37/6                           | 15/1                       |

| MKL27Z32VFT4 | TBD                      | 32            | 8            | 48           | QFN     | 37                 | 37/6                           | 15/1                       |

Table 1. Ordering information

1. INT: interrupt pin numbers; HD: high drive pin numbers

#### NOTE

The 48 QFN and 64 MAPBGA packages supporting MKLx7ZxxVFT4 and MKLx7ZxxVMP4 part numbers for this product are not yet available. However, these packages are included in Package Your Way program for Kinetis MCUs. Visit Freescale.com/KPYW for more details.

# 2 Overview

The following figure shows the system diagram of this device

#### 2.1.1 ARM Cortex-M0+ core

The enhanced ARM Cortex M0+ is the member of the Cortex-M series of processors targeting microcontroller cores focused on very cost sensitive, low power applications. It has a single 32-bit AMBA AHB-Lite interface and includes an NVIC component. It also has hardware debug functionality including support for simple program trace capability. The processor supports the ARMv6-M instruction set (Thumb) architecture including all but three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions. It is upward compatible with other Cortex-M profile processors.

## 2.1.2 NVIC

The Nested Vectored Interrupt Controller supports nested interrupts and 4 priority levels for interrupts. In the NVIC, each source in the IPR registers contains two bits. It also differs in number of interrupt sources and supports 32 interrupt vectors.

The Cortex-M family uses a number of methods to improve interrupt latency to up to 15 clock cycles for Cortex-M0+. It also can be used to wake the MCU core from Wait and VLPW modes.

## 2.1.3 AWIC

The asynchronous wake-up interrupt controller (AWIC) is used to detect asynchronous wake-up events in Stop mode and signal to clock control logic to resume system clocking. After clock restarts, the NVIC observes the pending interrupt and performs the normal interrupt or event processing. The AWIC can be used to wake MCU core from Stop and VLPS modes.

Wake-up sources are listed as below:

| Wake-up source          | Description                                                                                                                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Available system resets | RESET pin with filter mode disabled or enabled when LPO is its clock source, COP when its clock source is enabled. COP can also work when its clock source is enabled during Stop mode. |

| Low-voltage detect      | Power management controller—functional in Stop mode                                                                                                                                     |

| Low-voltage warning     | Power management controller—functional in Stop mode                                                                                                                                     |

| Pin interrupts          | Port control module—any enabled pin interrupt is capable of waking the system                                                                                                           |

| ADC                     | The ADC is functional when using internal clock source or external crystal clock                                                                                                        |

| CMP0                    | Interrupt in normal or trigger mode                                                                                                                                                     |

Table 2. AWIC stop wake-up sources

Table continues on the next page...

| Module            | Bus interface clock | Internal clocks | I/O interface clocks |

|-------------------|---------------------|-----------------|----------------------|

| l <sup>2</sup> C1 | System Clock        | —               | I2C1_SCL             |

| LPUART0, LPUART1  | Bus clock           | LPUART0 clock   | —                    |

|                   |                     | LPUART1 clock   |                      |

| UART2             | Bus clock           | —               | —                    |

| FlexIO            | Bus clock           | FlexIO clock    | _                    |

|                   | Human-mach          | ine interfaces  |                      |

| GPIO              | Platform clock      | _               | —                    |

| Table 4. | Module clocks ( | (continued) |

|----------|-----------------|-------------|

|          |                 |             |

### 2.1.7 Security

Security state can be enabled via programming flash configuration field (0x40e). After enabling device security, the SWD port cannot access the memory resources of the MCU, and ROM boot loader is also limited to access flash and not allowed to read out flash information via ROM boot loader commands.

| Access interface                                | Secure state                                             | Unsecure operation                                                                                                                                             |

|-------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWD port                                        | Cannot access memory source by SWD interface             | The debugger can write to the Flash<br>Mass Erase in Progress field of the<br>MDM-AP Control register to trigger a<br>mass erase (Erase All Blocks)<br>command |

| ROM boot loader Interface<br>(UART/I2C/SPI/USB) | Limit access to the flash, cannot read out flash content | Send "FlashEraseAllUnsecureh"<br>command or attempt to unlock flash<br>security using the backdoor key                                                         |

This device features 80-bit unique identification number, which is programmed in factory and loaded to SIM register after power-on reset.

### 2.1.8 Power management

The Power Management Controller (PMC) expands upon ARM's operational modes of Run, Sleep, and Deep Sleep, to provide multiple configurable modes. These modes can be used to optimize current consumption for a wide range of applications. The WFI or WFE instruction invokes a Wait or a Stop mode, depending on the current configuration. For more information on ARM's operational modes, See the ARM® Cortex User Guide.

## 2.2.6 CMP

The device contains one high-speed comparator and two 8-input multiplexers for both the inverting and non-inverting inputs of the comparator. Each CMP input channel connects to both muxes.

The CMP includes one 6-bit DAC, which provides a selectable voltage reference for various user application cases. Besides, the CMP also has several module-to-module interconnects in order to facilitate ADC triggering, TPM triggering, and interfaces.

The CMP has the following features:

- Inputs may range from rail to rail

- Programmable hysteresis control

- Selectable interrupt on rising-edge, falling-edge, or both rising or falling edges of the comparator output

- Selectable inversion on comparator output

- Capability to produce a wide range of outputs such as sampled, digitally filtered

- External hysteresis can be used at the same time that the output filter is used for internal functions

- Two software selectable performance levels: shorter propagation delay at the expense of higher power and Low power with longer propagation delay

- DMA transfer support

- Functional in all modes of operation except in VLLS0 mode

- The filter functions are not available in Stop, VLPS, LLS, or VLLSx modes

- Integrated 6-bit DAC with selectable supply reference source and can be power down to conserve power

- Two 8-to-1 channel mux

## 2.2.7 RTC

The RTC is an always powered-on block that remains active in all low power modes. The time counter within the RTC is clocked by a 32.768 kHz clock sourced from an external crystal using the oscillator or clock directly from RTC\_CLKIN pin.

RTC is reset on power-on reset, and a software reset bit in RTC can also initialize all RTC registers.

The RTC module has the following features

• 32-bit seconds counter with roll-over protection and 32-bit alarm

- 1/16 bit-time noise detection

- DMA interface

# 2.2.12 LPUART

This product contains two Low-Power UART modules, both of their clock sources are selectable from IRC48M, IRC8M/2M or external crystal clock, and can work in Stop and VLPS modes. They also support  $4 \times$  to  $32 \times$  data oversampling rate to meet different applications.

The LPUART module has the following features:

- Programmable baud rates (13-bit modulo divider) with configurable oversampling ratio from  $4 \times$  to  $32 \times$

- Transmit and receive baud rate can operate asynchronous to the bus clock and can be configured independently of the bus clock frequency, support operation in Stop mode

- Interrupt, DMA or polled operation

- Hardware parity generation and checking

- Programmable 8-bit, 9-bit or 10-bit character length

- Programmable 1-bit or 2-bit stop bits

- Three receiver wakeup methods

- Idle line wakeup

- Address mark wakeup

- Receive data match

- Automatic address matching to reduce ISR overhead:

- Address mark matching

- Idle line address matching

- Address match start, address match end

- Optional 13-bit break character generation / 11-bit break character detection

- Configurable idle length detection supporting 1, 2, 4, 8, 16, 32, 64 or 128 idle characters

- Selectable transmitter output and receiver input polarity

# 2.2.13 SPI

This device contains two SPI modules. SPI modules support 8-bit and 16-bit modes. FIFO function is available only on SPI1 module.

The SPI modules have the following features:

- Full-duplex or single-wire bidirectional mode

- Programmable transmit bit rate

- Double-buffered transmit and receive data register

- Serial clock phase and polarity options

- Slave select output

- Mode fault error flag with CPU interrupt capability

- Control of SPI operation during wait mode

- Selectable MSB-first or LSB-first shifting

- Programmable 8- or 16-bit data transmission length

- Receive data buffer hardware match feature

- 64-bit FIFO mode for high speed/large amounts of data transfers

- Support DMA

## 2.2.14 I2C

This device contains two I2C modules, which support up to 1 Mbits/s by dual buffer features, and address match to wake MCU from the low power mode.

I2C modules support DMA transfer, and the interrupt condition can trigger DMA request when DMA function is enabled.

The I2C modules have the following features:

- Support for system management bus (SMBus) Specification, version 2

- Software programmable for one of 64 different serial clock frequencies

- Software-selectable acknowledge bit

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation and detection

- Repeated START signal generation and detection

- Acknowledge bit generation and detection

- Bus busy detection

- General call recognition

- 10-bit address extension

- Programmable input glitch filter

- Low power mode wakeup on slave address match

- Range slave address support

- DMA support

- Double buffering support to achieve higher baud rate

- Configurable edge(rising,falling,both) or level sensitive interrupt type

- Support DMA request

- Asynchronous wake-up in low-power modes

- Configurable pullup, pulldown, and pull-disable on select pins

- Configurable high and low drive strength on selected pins

- Configurable fast and slow slew rates on selected pins

- Configurable passive filter on selected pins

- Individual mux control field supporting analog or pin disabled, GPIO, and up to chip-specific digital functions

- Pad configuration fields are functional in all digital pin muxing modes.

The GPIO module has the following features:

- Port Data Input register visible in all digital pin-multiplexing modes

- Port Data Output register with corresponding set/clear/toggle registers

- Port Data Direction register

- GPIO support single-cycle access via fast GPIO.

# 3 Memory map

This device contains various memories and memory-mapped peripherals which are located in a 4 GB memory space. The following figure shows the system memory and peripheral locations

### NOTE

The 48 QFN and 64 MAPBGA packages for this product are not yet available. However, these packages are included in Package Your Way program for Kinetis MCUs. Visit freescale.com/KPYW for more details.

| 64<br>LQFP | 36<br>XFB<br>GA | 32<br>QFN | 48<br>QFN | 64<br>MAP<br>BGA | Pin Name | Default                    | ALT0                       | ALT1                   | ALT2      | ALT3           | ALT4           | ALT5            | ALT6            | ALT7 |

|------------|-----------------|-----------|-----------|------------------|----------|----------------------------|----------------------------|------------------------|-----------|----------------|----------------|-----------------|-----------------|------|

| -          | C1              | _         | _         | -                | PTE17    | ADC0_DM1/<br>ADC0_SE5a     | ADC0_DM1/<br>ADC0_SE5a     | PTE17                  | SPI0_SCK  | UART2_RX       | TPM_<br>CLKIN1 | LPTMR0_<br>ALT3 | FXIO0_D1        |      |

| -          | D1              | _         | _         | _                | PTE18    | ADC0_DP2/<br>ADC0_SE2      | ADC0_DP2/<br>ADC0_SE2      | PTE18                  | SPI0_MOSI |                | I2C0_SDA       | SPI0_MISO       | FXIO0_D2        |      |

| -          | F2              | 9         | -         |                  | VREF0    | VREF0_B                    | VREF0_B                    |                        |           |                |                |                 |                 |      |

| -          | -               | Ι         | -         | C5               | NC       | NC                         | NC                         |                        |           |                |                |                 |                 |      |

| 1          | A1              | 1         | Ι         | A1               | PTE0     | DISABLED                   |                            | PTE0/<br>CLKOUT32<br>K | SPI1_MISO | LPUART1_<br>TX | RTC_<br>CLKOUT | CMP0_OUT        | I2C1_SDA        |      |

| 2          | 1               | _         | _         | B1               | PTE1     | DISABLED                   |                            | PTE1                   | SPI1_MOSI | lpuart1_<br>RX |                | SPI1_MISO       | I2C1_SCL        |      |

| 3          | -               | —         | 1         |                  | VDD      | VDD                        | VDD                        |                        |           |                |                |                 |                 |      |

| 4          | C4              | 2         | 2         | C4               | VSS      | VSS                        | VSS                        |                        |           |                |                |                 |                 |      |

| 5          | B1              | 3         | 3         | E1               | USB0_DP  | USB0_DP                    | USB0_DP                    |                        |           |                |                |                 |                 |      |

| 6          | D2              | 4         | 4         | D1               | USB0_DM  | USB0_DM                    | USB0_DM                    |                        |           |                |                |                 |                 |      |

| 7          | C3              | 5         | 5         | E2               | USB_VDD  | USB_VDD                    | USB_VDD                    |                        |           |                |                |                 |                 |      |

| 8          | C2              | 6         | 6         | D2               | PTE16    | ADC0_DP1/<br>ADC0_SE1      | ADC0_DP1/<br>ADC0_SE1      | PTE16                  | SPI0_PCS0 | UART2_TX       | TPM_<br>CLKIN0 |                 | FXIO0_D0        |      |

| 9          | E3              | _         | 7         | G1               | PTE20    | ADC0_DP0/<br>ADC0_SE0      | ADC0_DP0/<br>ADC0_SE0      | PTE20                  |           | TPM1_CH0       | LPUART0_<br>TX |                 | FXIO0_D4        |      |

| 10         | E2              | _         | 8         | F1               | PTE21    | ADC0_DM0/<br>ADC0_SE4a     | ADC0_DM0/<br>ADC0_SE4a     | PTE21                  |           | TPM1_CH1       | LPUARTO_<br>RX |                 | FXIO0_D5        |      |

| 11         | E1              | _         | _         | G2               | PTE22    | ADC0_DP3/<br>ADC0_SE3      | ADC0_DP3/<br>ADC0_SE3      | PTE22                  |           | TPM2_CH0       | UART2_TX       |                 | FXIO0_D6        |      |

| 12         | F1              | _         | -         | F2               | PTE23    | ADC0_DM3/<br>ADC0_SE7a     | ADC0_DM3/<br>ADC0_SE7a     | PTE23                  |           | TPM2_CH1       | UART2_RX       |                 | FXIO0_D7        |      |

| 13         | D3              | 7         | 9         | F4               | VDDA     | VDDA                       | VDDA                       |                        |           |                |                |                 |                 |      |

| 14         | D3              | 7         | 10        | G4               | VREFH    | VREFH                      | VREFH                      |                        |           |                |                |                 |                 |      |

| 14         | —               | —         | 10        | G4               | VREFO    | VREFO_A                    | VREFO_A                    |                        |           |                |                |                 |                 |      |

| 15         | D4              | 8         | 11        | G3               | VREFL    | VREFL                      | VREFL                      |                        |           |                |                |                 |                 |      |

| 16         | D4              | 8         | 12        | F3               | VSSA     | VSSA                       | VSSA                       |                        |           |                |                |                 |                 |      |

| 17         | -               | —         | 13        | H1               | PTE29    | CMP0_IN5/<br>ADC0_SE4b     | CMP0_IN5/<br>ADC0_SE4b     | PTE29                  |           | TPM0_CH2       | TPM_<br>CLKIN0 |                 |                 |      |

| 18         | F2              | 9         | 14        | H2               | PTE30    | ADC0_<br>SE23/<br>CMP0_IN4 | ADC0_<br>SE23/<br>CMP0_IN4 | PTE30                  |           | TPM0_CH3       | TPM_<br>CLKIN1 | LPUART1_<br>TX  | LPTMR0_<br>ALT1 |      |

| 19         | -               | _         | _         | H3               | PTE31    | DISABLED                   |                            | PTE31                  |           | TPM0_CH4       |                |                 |                 |      |

| 64 LQFP | 36<br>XFBGA | 32 QFN | 48 QFN | 64 MAPBGA | Pin name | Driver strength | Default status after POR | Pullup/ pulldown setting after POR | Slew rate after POR | Passive pin filter after POR | Open drain | Pin interrupt |

|---------|-------------|--------|--------|-----------|----------|-----------------|--------------------------|------------------------------------|---------------------|------------------------------|------------|---------------|

|         | F2          | 9      |        | -         | VREF0    | -               |                          |                                    |                     |                              |            |               |

| —       | —           |        |        | C5        | NC       |                 |                          |                                    |                     |                              |            |               |

| 1       | A1          | 1      | —      | A1        | PTE0     | ND              | Hi-Z                     | —                                  | FS                  | N                            | N          | Y             |

| 2       | —           | —      | -      | B1        | PTE1     | ND              | Hi-Z                     | —                                  | FS                  | N                            | N          | Y             |

| 3       | —           | —      | 1      | —         | VDD      | —               | —                        | —                                  | —                   |                              | —          | —             |

| 4       | C4          | 2      | 2      | C4        | VSS      |                 |                          |                                    | —                   |                              |            | —             |

| 5       | B1          | 3      | 3      | E1        | USB0_DP  | —               | —                        | —                                  | —                   | _                            |            | —             |

| 6       | D2          | 4      | 4      | D1        | USB0_DM  | —               | —                        | —                                  | _                   | _                            | _          | —             |

| 7       | C3          | 5      | 5      | E2        | USB_VDD  | _               | _                        | —                                  | _                   | _                            | _          | —             |

| 8       | C2          | 6      | 6      | D2        | PTE16    | ND              | Hi-Z                     | —                                  | FS                  | N                            | Ν          | Y             |

| 9       | E3          | —      | 7      | G1        | PTE20    | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 10      | E2          | —      | 8      | F1        | PTE21    | ND              | Hi-Z                     | -                                  | SS                  | N                            | N          | Y             |

| 11      | E1          | —      | —      | G2        | PTE22    | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 12      | F1          | —      | —      | F2        | PTE23    | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 13      | D3          | 7      | 9      | F4        | VDDA     | —               | —                        | —                                  | —                   | —                            | —          | —             |

| 14      | D3          | 7      | 10     | G4        | VREFH    | _               | —                        | —                                  | _                   | —                            | -          | —             |

| 14      | —           | —      | 10     | G4        | VREFO    | —               | —                        | —                                  | —                   | —                            | —          | —             |

| 15      | D4          | 8      | 11     | G3        | VREFL    | _               | —                        | —                                  | —                   | _                            | —          | —             |

| 16      | D4          | 8      | 12     | F3        | VSSA     | _               | _                        | —                                  | _                   | -                            | _          |               |

| 17      | —           | —      | 13     | H1        | PTE29    | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 18      | F2          | 9      | 14     | H2        | PTE30    | ND              | Hi-Z                     | _                                  | SS                  | N                            | N          | Y             |

| 19      | —           | —      | —      | H3        | PTE31    | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 20      | —           | _      | 15     | H4        | PTE24    | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 21      | —           | _      | 16     | H5        | PTE25    | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 22      | F3          | 10     | 17     | D3        | PTA0     | ND              | L                        | PD                                 | SS                  | N                            | N          | Y             |

| 23      | F4          | 11     | 18     | D4        | PTA1     | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 24      | E4          | 12     | 19     | E5        | PTA2     | ND              | Hi-Z                     | —                                  | SS                  | N                            | N          | Y             |

| 25      | E5          | 13     | 20     | D5        | PTA3     | ND              | Н                        | PU                                 | FS                  | N                            | N          | Y             |

| 26      | F5          | 14     | 21     | G5        | PTA4     | ND              | Н                        | PU                                 | SS                  | Y                            | N          | Y             |

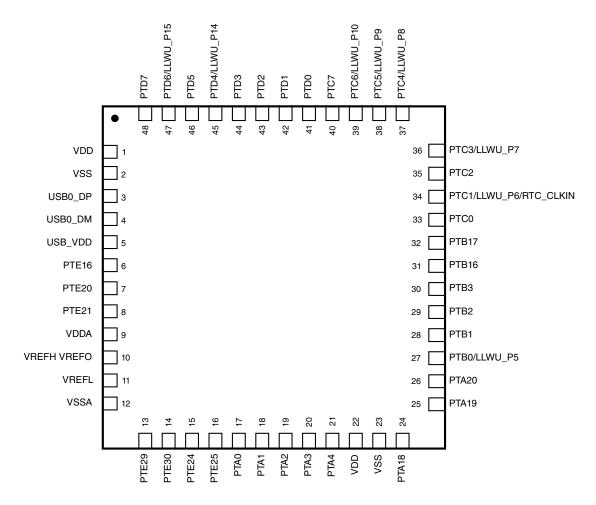

Pinouts

### NOTE

The 48 QFN package for this product is not yet available. However, it is included in Package Your Way program for Kinetis MCUs. Visit freescale.com/KPYW for more details.

The figure below shows the 64 MAPBGA pinouts.

### NOTE

The 64 MAPBGA package for this product is not yet available. However, it is included in Package Your Way program for Kinetis MCUs. Visit freescale.com/KPYW for more details.

|   | 1       | 2                 | 3                 | 4                 | 5                              | 6                |   |

|---|---------|-------------------|-------------------|-------------------|--------------------------------|------------------|---|

| A | PTE0    | PTD7              | PTD4/<br>LLWU_P14 | PTC7              | PTC5/<br>LLWU_P9               | PTC4/<br>LLWU_P8 | A |

| в | USB0_DP | PTD6/<br>LLWU_P15 | PTD5              | PTC6/<br>LLWU_P10 | PTC3/<br>LLWU_P7               | PTC2             | в |

| с | PTE17   | PTE16             | USB_VDD/<br>VDD   | VSS               | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | PTB1             | С |

| D | PTE18   | USB0_DM           | VDDA/<br>VREFH    | VREFL/<br>VSSA    | PTA20                          | PTB0/<br>LLWU_P5 | D |

| E | PTE22   | PTE21             | PTE20             | PTA2              | PTA3                           | PTA19            | E |

| F | PTE23   | VREF0/<br>PTE30   | PTA0              | PTA1              | PTA4                           | PTA18            | F |

|   | 1       | 2                 | 3                 | 4                 | 5                              | 6                | 1 |

Figure 10. 36 XFBGA Pinout diagram (transparent top view)

## 4.5 Package dimensions

The following figures show the dimensions of the package options for the devices supported by this document.

**Electrical characteristics**

| Symbol                | Description                                                                                                                 | Min. | Тур.      | Max.       | Unit | Notes |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----------|------------|------|-------|

|                       | • at 50°C                                                                                                                   | -    | 2.21      | 2.80       | μA   |       |

|                       | • at 70°C                                                                                                                   | _    | 3.59      | 4.18       |      |       |

|                       | • at 85°C                                                                                                                   | _    | 8.02      | 9.47       |      |       |

|                       | • at 105 °C                                                                                                                 |      |           |            |      |       |

| I <sub>DD_VLLS0</sub> | Very-low-leakage stop mode 0 current all<br>peripheral disabled<br>(SMC_STOPCTRL[PORPO] = 0) at 3.0 V                       | _    | 262       | 360        |      |       |

|                       | <ul> <li>at 25 °C and below</li> </ul>                                                                                      | _    | 593       | 725        |      |       |

|                       | • at 50 °C                                                                                                                  | _    | 1430      | 2014       | nA   |       |

|                       | • at 70 °C                                                                                                                  | _    | 2930      | 3514       |      |       |

|                       | • at 85 °C                                                                                                                  |      | 7930      | 9895       |      |       |

|                       | • at 105 °C                                                                                                                 |      |           |            |      |       |

| I <sub>DD_VLLS0</sub> | Very-low-leakage stop mode 0 current all<br>peripheral disabled<br>(SMC_STOPCTRL[PORPO] = 1) at 3 V<br>• at 25 °C and below |      | 87<br>417 | 185<br>549 |      | 4     |

|                       | • at 50 °C                                                                                                                  | _    | 1230      | 1230       | nA   |       |

|                       | • at 70 °C                                                                                                                  | _    | 2720      | 3304       |      |       |

|                       | • at 85 °C                                                                                                                  |      | 7780      | 9745       |      |       |

|                       | • at 105 °C                                                                                                                 |      |           |            |      |       |

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

2. MCG\_Lite configured for HIRC mode. CoreMark benchmark compiled using IAR 7.10 with optimization level high, optimized for balanced.

3. RTC uses external 32 kHz crystal as clock source, and the current includes ERCLK32K power consumption.

4. No brownout

Table 40. Low power mode peripheral adders — typical value

| Symbol               | Description                                                                                                                                                         |     | Temperature (°C) |    |    |    |     |    |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|----|----|----|-----|----|--|--|

|                      |                                                                                                                                                                     | -40 | 25               | 50 | 70 | 85 | 105 |    |  |  |

| I <sub>IRC8MHz</sub> | 8 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 8 MHz IRC enabled,<br>MCG_SC[FCRDIV]=000b,<br>MCG_MC[LIRC_DIV2]=000b. | 77  | 77               | 77 | 77 | 77 | 77  | μA |  |  |

| I <sub>IRC2MHz</sub> | 2 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 2 MHz IRC enabled,<br>MCG_SC[FCRDIV]=000b,<br>MCG_MC[LIRC_DIV2]=000b.     | 25  | 25               | 25 | 25 | 25 | 25  | μΑ |  |  |

Table continues on the next page...

| Board type        | Symbol            | Description                                                                                              | 32 QFN | 36<br>XFBGA | 64 LQFP | Unit | Notes     |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|--------|-------------|---------|------|-----------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 101    | 81.5        | 71      | °C/W | 1, 2, 3   |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 33     | 54.7        | 53      | °C/W | 1, 2, 3,4 |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 84     | 71.3        | 60      | °C/W | 1, 4, 5   |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 28     | 50.0        | 47      | °C/W | 1, 4, 5   |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 13     | 58.0        | 35      | °C/W | 6         |

| —                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 1.7    | 45.3        | 21      | °C/W | 7         |

| _                 | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 3      | 1.2         | 5       | °C/W | 8         |

| _                 | Ψ <sub>JB</sub>   | Thermal characterization<br>parameter, junction to package<br>bottom (natural convection)                | -      | 44.5        | -       | °C/W | 9         |

#### Table 45. Thermal attributes

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Per JEDEC JESD51-6 with the board horizontal.

- 5. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 6. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 7. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 8. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 9. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

## 5.3 Peripheral operating requirements and behaviors

### 5.3.1 Core modules

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                 | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency —<br>high-frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency —<br>high frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           |      | —    | 48   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                | —    | 750  | _    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | —    | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | _    | ms   |       |

#### 5.3.3.2.2 Oscillator frequency specifications Table 50. Oscillator frequency specifications

1. Other frequency limits may apply when external clock is being used as a reference for the FLL

2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

3. Proper PC board layout procedures must be followed to achieve specifications.

4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

### 5.3.4 Memories and memory interfaces

#### 5.3.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

#### 5.3.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

#### 5.3.6.1.2 16-bit ADC electrical characteristics

| Table 56. | 16-bit ADC characteristics | $(V_{REFH} = V_{DDA})$ | V <sub>REFL</sub> = V <sub>SSA</sub> ) |

|-----------|----------------------------|------------------------|----------------------------------------|

|-----------|----------------------------|------------------------|----------------------------------------|

| Symbol                 | Description                     | Conditions <sup>1</sup>                       | Min.               | Typ. <sup>2</sup> | Max.                    | Unit             | Notes                         |  |

|------------------------|---------------------------------|-----------------------------------------------|--------------------|-------------------|-------------------------|------------------|-------------------------------|--|

| I <sub>DDA_ADC</sub>   | Supply current                  |                                               | 0.215              |                   | 1.7                     | mA               | 3                             |  |

|                        | ADC                             | • ADLPC = 1, ADHSC = 0                        | 1.2                | 2.4               | 3.9                     | MHz              | t <sub>ADACK</sub> =          |  |

|                        | asynchronous<br>clock source    | <ul> <li>ADLPC = 1, ADHSC = 1</li> </ul>      | 2.4                | 4.0               | 6.1                     | MHz              | 1/f <sub>ADACI</sub>          |  |

|                        |                                 | <ul> <li>ADLPC = 0, ADHSC = 0</li> </ul>      | 3.0                | 5.2               | 7.3                     | MHz              |                               |  |

|                        |                                 | • ADLPC = 0, ADHSC = 1                        | 4.4                | 6.2               | 9.5                     | MHz              |                               |  |

|                        | Sample Time                     | See Reference Manual chapter for sample times |                    |                   |                         |                  |                               |  |

| TUE                    | Total                           | 12-bit modes                                  | _                  | ±2                | ±6.8                    | LSB <sup>4</sup> | 5                             |  |

|                        | unadjusted<br>error             | <ul> <li>&lt;12-bit modes</li> </ul>          | _                  | ±1.4              | ±2.1                    |                  |                               |  |

|                        | Differential non-<br>linearity  | 12-bit modes                                  | _                  | ±0.7              | -1.1 to<br>+1.9         | LSB <sup>4</sup> | 5                             |  |

|                        | incurty                         | <ul> <li>&lt;12-bit modes</li> </ul>          | _                  | ±0.2              | -0.3 to<br>0.5          |                  |                               |  |

| INL Integral linearity | Integral non-                   | 12-bit modes                                  | —                  | ±0.9              | -2.7 to                 | LSB <sup>4</sup> | 5                             |  |

|                        | linearity                       | <ul> <li>&lt;12-bit modes</li> </ul>          | _                  | ±0.4              | +1.9<br>-0.7 to<br>+0.5 |                  |                               |  |

| E <sub>FS</sub>        | Full-scale error                | 12-bit modes                                  | _                  | -4                | -5.4                    | LSB <sup>4</sup> | V <sub>ADIN</sub> =           |  |

|                        |                                 | <ul> <li>&lt;12-bit modes</li> </ul>          | _                  | -1.4              | -1.8                    |                  | V <sub>DDA</sub> <sup>5</sup> |  |

| EQ                     | Quantization                    | 16-bit modes                                  | —                  | -1 to 0           | _                       | LSB <sup>4</sup> |                               |  |

|                        | error                           | • ≤13-bit modes                               | _                  | _                 | ±0.5                    |                  |                               |  |

| ENOB                   | Effective                       | 16-bit differential mode                      |                    |                   |                         |                  | 6                             |  |

|                        | number of bits                  | • Avg = 32                                    | 12.8               | 14.5              | —                       | bits             |                               |  |

|                        |                                 | • Avg = 4                                     | 11.9               | 13.8              | —                       | bits             |                               |  |

|                        |                                 | 16-bit single-ended mode                      |                    |                   |                         |                  |                               |  |

|                        |                                 | • Avg = 32                                    | 12.2               | 13.9              | —                       | bits             |                               |  |

|                        |                                 | • Avg = 4                                     | 11.4               | 13.1              | _                       | bits             |                               |  |

| SINAD                  | Signal-to-noise plus distortion | See ENOB                                      | 6.02 × ENOB + 1.76 |                   | 1.76                    | dB               |                               |  |

| THD                    | Total harmonic                  | 16-bit differential mode                      |                    |                   |                         |                  | 7                             |  |

|                        | distortion                      | • Avg = 32                                    | -                  | -94               | _                       | dB               |                               |  |

|                        |                                 | 16-bit single-ended mode                      | _                  | -85               | _                       | dB               |                               |  |

Table continues on the next page...

This device cannot support Host mode operation.

## 5.5.2 SPI switching specifications

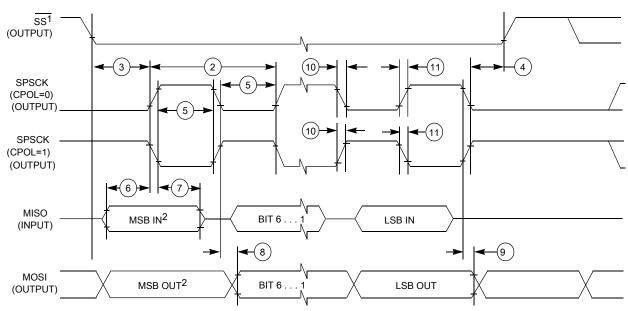

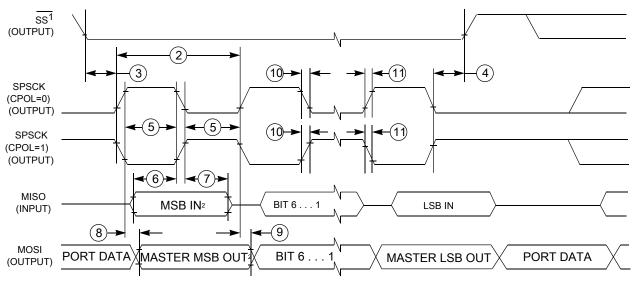

The Serial Peripheral Interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. See the SPI chapter of the chip's Reference Manual for information about the modified transfer formats used for communicating with slower peripheral devices.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all SPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                     | Unit               | Note     |

|------|---------------------|--------------------------------|---------------------------|--------------------------|--------------------|----------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2   | Hz                 | 1        |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x                   | ns                 | 2        |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |          |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                        | t <sub>SPSCK</sub> | _        |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       |                          | t <sub>SPSCK</sub> |          |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x                   | ns                 | —        |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |          |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        | —                        | ns                 | <u> </u> |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | —                        | ns                 |          |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 15                       | ns                 |          |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | —                        | ns                 |          |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25 | ns                 |          |

|      | t <sub>FI</sub>     | Fall time input                |                           |                          |                    |          |

| 11   | t <sub>RO</sub>     | Rise time output               | -                         | 25                       | ns                 | —        |

|      | t <sub>FO</sub>     | Fall time output               |                           |                          |                    |          |

Table 61. SPI master mode timing on slew rate disabled pads

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

2.  $t_{periph} = 1/f_{periph}$

#### Table 62. SPI master mode timing on slew rate enabled pads

| Num. | Symbol             | Description            | Min.                      | Max.                          | Unit               | Note |

|------|--------------------|------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>    | Frequency of operation | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub> | SPSCK period           | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>  | Enable lead time       | 1/2                       |                               | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>   | Enable lag time        | 1/2                       |                               | t <sub>SPSCK</sub> | _    |

Table continues on the next page...

| Num. | Symbol          | Description                    | Min.                     | Max.                          | Unit | Note |

|------|-----------------|--------------------------------|--------------------------|-------------------------------|------|------|

| 5    | twspsck         | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | 1024 x<br>t <sub>periph</sub> | ns   | _    |

| 6    | t <sub>SU</sub> | Data setup time (inputs)       | 96                       | _                             | ns   | —    |

| 7    | t <sub>HI</sub> | Data hold time (inputs)        | 0                        | _                             | ns   | —    |

| 8    | t <sub>v</sub>  | Data valid (after SPSCK edge)  | —                        | 52                            | ns   | —    |

| 9    | t <sub>HO</sub> | Data hold time (outputs)       | 0                        | _                             | ns   | —    |

| 10   | t <sub>RI</sub> | Rise time input                | —                        | t <sub>periph</sub> - 25      | ns   | —    |

|      | t <sub>FI</sub> | Fall time input                |                          |                               |      |      |

| 11   | t <sub>RO</sub> | Rise time output               | _                        | 36                            | ns   | —    |

|      | t <sub>FO</sub> | Fall time output               |                          |                               |      |      |

Table 62. SPI master mode timing on slew rate enabled pads (continued)

- 1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

- 2.  $t_{periph} = 1/f_{periph}$

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 29. SPI master mode timing (CPHA = 0)

#### **Electrical characteristics**

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 30. SPI master mode timing (CPHA = 1)

#### Table 63. SPI slave mode timing on slew rate disabled pads

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  | —                        | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | —                        | t <sub>periph</sub> | —    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | —                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2.5                      | —                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 3.5                      | —                        | ns                  | —    |

| 8    | t <sub>a</sub>      | Slave access time              | _                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | _                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                        | 31                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | —                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | _                        | t <sub>periph</sub> - 25 | ns                  | —    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns                  | —    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

- 2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL lines.

- 3. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 4. Input signal Slew = 10 ns and Output Load = 50 pF

- 5. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 6. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 7.  $C_b$  = total capacitance of the one bus line in pF.

To achieve 1MHz I2C clock rates, consider the following recommendations:

- To counter the effects of clock stretching, the I2C baud Rate select bits can be configured for faster than desired baud rate.

- Use high drive pad and DSE bit should be set in PORTx\_PCRn register.

- Minimize loading on the I2C SDA and SCL pins to ensure fastest rise times for the SCL line to avoid clock stretching.

- Use smaller pull up resistors on SDA and SCL to reduce the RC time constant.

| Characteristic                                                                               | Symbol                | Minimum                            | Maximum        | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|------------------------------------|----------------|------|

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                                  | 1 <sup>1</sup> | MHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 0.26                               |                | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 0.5                                | —              | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 0.26                               |                | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 0.26                               |                | μs   |

| Data hold time for I <sub>2</sub> C bus devices                                              | t <sub>HD</sub> ; DAT | 0                                  | —              | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 50                                 | —              | ns   |

| Rise time of SDA and SCL signals                                                             | t <sub>r</sub>        | 20 +0.1C <sub>b</sub>              | 120            | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | 20 +0.1C <sub>b</sub> <sup>2</sup> | 120            | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 0.26                               | —              | μs   |

| Bus free time between STOP and START condition                                               | t <sub>BUF</sub>      | 0.5                                |                | μs   |

| Pulse width of spikes that must be suppressed by the input filter                            | t <sub>SP</sub>       | 0                                  | 50             | ns   |

Table 66.

I <sup>2</sup>C 1Mbit/s timing

1. The maximum SCL clock frequency of 1 Mbit/s can support maximum bus loading when using the high drive pins across the full voltage range.

2.  $C_b$  = total capacitance of the one bus line in pF.

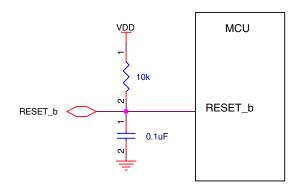

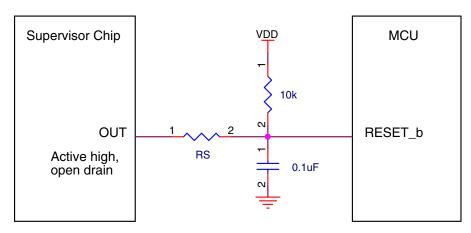

#### Figure 36. Reset circuit

When an external supervisor chip is connected to the RESET\_b pin, a series resistor must be used to avoid damaging the supervisor chip or the RESET\_b pin, as shown in the following figure. The series resistor value (RS below) must be in the range of  $100 \Omega$  to  $1 \text{ k}\Omega$  depending on the external reset chip drive strength. The supervisor chip must have an active high, open-drain output.

Figure 37. Reset signal connection to external reset chip

#### • NMI pin

Do not add a pull-down resistor or capacitor on the NMI\_b pin, because a low level on this pin will trigger non-maskable interrupt. When this pin is enabled as the NMI function, an external pull-up resistor (10 k $\Omega$ ) as shown in the following figure is recommended for robustness.

If the NMI\_b pin is used as an I/O pin, the non-maskable interrupt handler is required to disable the NMI function by remapping to another function. The NMI function is disabled by programming the FOPT[NMI\_DIS] bit to zero.