# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, FlexIO, SPI, UART/USART, USB                        |

| Peripherals                | DMA, I <sup>2</sup> S, PWM, WDT                                       |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K × 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 17x16b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl27z64vlh4r |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1** Ordering information

The following chips are available for ordering.

| Pro          | Memory                   |               | Package      |              | IO and ADC channel |       |                                |                            |

|--------------|--------------------------|---------------|--------------|--------------|--------------------|-------|--------------------------------|----------------------------|

| Part number  | Marking<br>(Line1/Line2) | Flash<br>(KB) | SRAM<br>(KB) | Pin<br>count | Package            | GPIOs | GPIOs<br>(INT/HD) <sup>1</sup> | ADC<br>channels<br>(SE/DP) |

| MKL27Z64VLH4 | MKL27Z64 / VLH4          | 64            | 16           | 64           | LQFP               | 51    | 51/6                           | 17/2                       |

| MKL27Z32VLH4 | MKL27Z32 / VLH4          | 32            | 8            | 64           | LQFP               | 51    | 51/6                           | 17/2                       |

| MKL27Z64VDA4 | M27M6                    | 64            | 16           | 36           | XFBGA              | 30    | 30/6                           | 14/3                       |

| MKL27Z32VDA4 | M27M5                    | 32            | 8            | 36           | XFBGA              | 30    | 30/6                           | 14/3                       |

| MKL27Z64VFM4 | M27M6V                   | 64            | 16           | 32           | QFN                | 24    | 24/6                           | 8/0                        |

| MKL27Z32VFM4 | M27M5V                   | 32            | 8            | 32           | QFN                | 24    | 24/6                           | 8/0                        |

| MKL27Z64VMP4 | TBD                      | 64            | 16           | 64           | MAPBGA             | 51    | 51/6                           | 17/2                       |

| MKL27Z32VMP4 | TBD                      | 32            | 8            | 64           | MAPBGA             | 51    | 51/6                           | 17/2                       |

| MKL27Z64VFT4 | TBD                      | 64            | 16           | 48           | QFN                | 37    | 37/6                           | 15/1                       |

| MKL27Z32VFT4 | TBD                      | 32            | 8            | 48           | QFN                | 37    | 37/6                           | 15/1                       |

Table 1. Ordering information

1. INT: interrupt pin numbers; HD: high drive pin numbers

# NOTE

The 48 QFN and 64 MAPBGA packages supporting MKLx7ZxxVFT4 and MKLx7ZxxVMP4 part numbers for this product are not yet available. However, these packages are included in Package Your Way program for Kinetis MCUs. Visit Freescale.com/KPYW for more details.

# 2 Overview

The following figure shows the system diagram of this device

| Module                               | Bus interface clock | Internal clocks                                        | I/O interface clocks   |  |  |  |  |  |  |

|--------------------------------------|---------------------|--------------------------------------------------------|------------------------|--|--|--|--|--|--|

| ARM Cortex-M0+ core                  | Platform clock      | Core clock                                             | _                      |  |  |  |  |  |  |

| NVIC                                 | Platform clock      | _                                                      | _                      |  |  |  |  |  |  |

| DAP                                  | Platform clock      | _                                                      | SWD_CLK                |  |  |  |  |  |  |

| System modules                       |                     |                                                        |                        |  |  |  |  |  |  |

| DMA                                  | System clock        | _                                                      | _                      |  |  |  |  |  |  |

| DMA Mux                              | Bus clock           | _                                                      | _                      |  |  |  |  |  |  |

| Port control                         | Bus clock           | _                                                      | _                      |  |  |  |  |  |  |

| Crossbar Switch                      | Platform clock      | <u> </u>                                               | _                      |  |  |  |  |  |  |

| Peripheral bridges                   | System clock        | Bus clock                                              | _                      |  |  |  |  |  |  |

| LLWU, PMC, SIM, RCM                  | Bus clock           | LPO                                                    | _                      |  |  |  |  |  |  |

| Mode controller                      | Bus clock           | _                                                      | —                      |  |  |  |  |  |  |

| MCM                                  | Platform clock      | -                                                      | —                      |  |  |  |  |  |  |

| COP watchdog                         | Bus clock           | LPO, Bus Clock, MCGIRCLK,<br>OSCERCLK                  | —                      |  |  |  |  |  |  |

| CRC                                  | Bus clock           | _                                                      | _                      |  |  |  |  |  |  |

|                                      | Clo                 | ocks                                                   |                        |  |  |  |  |  |  |

| MCG_Lite                             | Bus clock           | MCGOUTCLK, MCGPCLK,<br>MCGIRCLK, OSCERCLK,<br>ERCLK32K | _                      |  |  |  |  |  |  |

| OSC                                  | Bus clock           | OSCERCLK                                               | _                      |  |  |  |  |  |  |

|                                      | Memory and m        | emory interfaces                                       |                        |  |  |  |  |  |  |

| Flash Controller                     | Platform clock      | Flash clock                                            | _                      |  |  |  |  |  |  |

| Flash memory                         | Flash clock         | —                                                      | —                      |  |  |  |  |  |  |

| ·                                    | An                  | alog                                                   |                        |  |  |  |  |  |  |

| ADC                                  | Bus clock           | OSCERCLK                                               | —                      |  |  |  |  |  |  |

| CMP                                  | Bus clock           | —                                                      | —                      |  |  |  |  |  |  |

| Internal Voltage Reference<br>(VREF) | Bus clock           | _                                                      | _                      |  |  |  |  |  |  |

| · ·                                  | Tir                 | ners                                                   |                        |  |  |  |  |  |  |

| ТРМ                                  | Bus clock           | TPM clock                                              | TPM_CLKIN0, TPM_CLKIN1 |  |  |  |  |  |  |

| PIT                                  | Bus clock           | —                                                      | —                      |  |  |  |  |  |  |

| LPTMR                                | Bus clock           | LPO, OSCERCLK,<br>MCGPCLK, ERCLK32K                    | —                      |  |  |  |  |  |  |

| RTC                                  | Bus clock           | ERCLK32K                                               | RTC_CLKOUT, RTC_CLKIN  |  |  |  |  |  |  |

|                                      | Communicat          | tion interfaces                                        | ·                      |  |  |  |  |  |  |

| USB FS (Device Only)                 | System clock        | USB FS clock                                           | —                      |  |  |  |  |  |  |

| SPI0                                 | Bus clock           | —                                                      | SPI0_SCK               |  |  |  |  |  |  |

| SPI1                                 | System clock        | —                                                      | SPI1_SCK               |  |  |  |  |  |  |

| I <sup>2</sup> C0                    | System Clock        | —                                                      | I2C0_SCL               |  |  |  |  |  |  |

The PMC provides Run (Run), and Very Low Power Run (VLPR) configurations in ARM's Run operation mode. In these modes, the MCU core is active and can access all peripherals. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption. The configuration that matches the power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in ARM's Sleep operation mode. In these modes, even though the MCU core is inactive, all of the peripherals can be enabled and operate as programmed. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS), Low Leakage Stop (LLS), and Very Low Leakage Stop (VLLS) configurations in ARM's Deep Sleep operational mode. In these modes, the MCU core and most of the peripherals are disabled. Depending on the requirements of the application, different portions of the analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up Interrupt Controller (AWIC), and the Low Leakage Wake-Up Controller (LLWU) are used to wake up the MCU from low power states. The NVIC is used to wake up the MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU core from STOP and VLPS modes. The LLWU is used to wake up the MCU core from LLS and VLLSx modes.

For additional information regarding operational modes, power management, the NVIC, AWIC, or the LLWU, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the various operational modes and the modules that can wake MCU from low power modes.

| Core mode  | Device mode         | Descriptions                                                                                                                                                                        |

|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode   | Run                 | In Run mode, all device modules are operational.                                                                                                                                    |

|            | Very Low Power Run  | In VLPR mode, all device modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled.                                             |

| Sleep mode | Wait                | In Wait mode, all peripheral modules are operational. The MCU core is placed into Sleep mode.                                                                                       |

|            | Very Low Power Wait | In VLPW mode, all peripheral modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled. The MCU core is placed into Sleep mode. |

Table 6. Peripherals states in different operational modes

- 16-bit prescaler with compensation that can correct errors between 0.12 ppm and 3906 ppm

- Register write protection with register lock mechanism

- 1 Hz square wave or second pulse output with optional interrupt

# 2.2.8 PIT

The Periodic Interrupt Timer (PIT) is used to generate periodic interrupt to the CPU. It has two independent channels and each channel has a 32-bit counter. Both channels can be chained together to form a 64-bit counter.

Channel 0 can be used to periodically trigger DMA channel 0, and channel 1 can be used to periodically trigger DMA channel 1. Either channel can be programmed as an ADC trigger source, or TPM trigger source. Channel 0 can be programmed to trigger DAC.

The PIT module has the following features:

- Each 32-bit timers is able to generate DMA trigger

- Each 32-bit timers is able to generate timeout interrupts

- Two timers can be cascaded to form a 64-bit timer

- Each timer can be programmed as ADC/TPM trigger source

- Timer 0 is able to trigger DAC

# 2.2.9 LPTMR

The low-power timer (LPTMR) can be configured to operate as a time counter with optional prescaler, or as a pulse counter with optional glitch filter, across all power modes, including the low-leakage modes. It can also continue operating through most system reset events, allowing it to be used as a time of day counter.

The LPTMR module has the following features:

- 16-bit time counter or pulse counter with compare

- Optional interrupt can generate asynchronous wakeup from any low-power mode

- Hardware trigger output

- Counter supports free-running mode or reset on compare

- Configurable clock source for prescaler/glitch filter

- Configurable input source for pulse counter

- Configurable edge(rising,falling,both) or level sensitive interrupt type

- Support DMA request

- Asynchronous wake-up in low-power modes

- Configurable pullup, pulldown, and pull-disable on select pins

- Configurable high and low drive strength on selected pins

- Configurable fast and slow slew rates on selected pins

- Configurable passive filter on selected pins

- Individual mux control field supporting analog or pin disabled, GPIO, and up to chip-specific digital functions

- Pad configuration fields are functional in all digital pin muxing modes.

The GPIO module has the following features:

- Port Data Input register visible in all digital pin-multiplexing modes

- Port Data Output register with corresponding set/clear/toggle registers

- Port Data Direction register

- GPIO support single-cycle access via fast GPIO.

# 3 Memory map

This device contains various memories and memory-mapped peripherals which are located in a 4 GB memory space. The following figure shows the system memory and peripheral locations

#### Pinouts

| 64<br>LQFP | 36<br>XFB<br>GA | 32<br>QFN | 48<br>QFN | 64<br>MAP<br>BGA | Pin Name          | Default   | ALTO      | ALT1              | ALT2      | ALT3                 | ALT4     | ALT5      | ALT6     | ALT7 |

|------------|-----------------|-----------|-----------|------------------|-------------------|-----------|-----------|-------------------|-----------|----------------------|----------|-----------|----------|------|

| 50         | A5              | 26        | 38        | A8               | PTC5/<br>LLWU_P9  | DISABLED  |           | PTC5/<br>LLWU_P9  | SPI0_SCK  | LPTMR0_<br>ALT2      |          |           | CMP0_OUT |      |

| 51         | B4              | 27        | 39        | A7               | PTC6/<br>LLWU_P10 | CMP0_IN0  | CMP0_IN0  | PTC6/<br>LLWU_P10 | SPI0_MOSI | EXTRG_IN             |          | SPI0_MISO |          |      |

| 52         | A4              | 28        | 40        | B6               | PTC7              | CMP0_IN1  | CMP0_IN1  | PTC7              | SPI0_MISO | audioUSB_<br>SOF_OUT |          | SPI0_MOSI |          |      |

| 53         | _               | -         | _         | A6               | PTC8              | CMP0_IN2  | CMP0_IN2  | PTC8              | I2C0_SCL  | TPM0_CH4             |          |           |          |      |

| 54         | -               | -         | _         | B5               | PTC9              | CMP0_IN3  | CMP0_IN3  | PTC9              | I2C0_SDA  | TPM0_CH5             |          |           |          |      |

| 55         | Ι               | -         | -         | B4               | PTC10             | DISABLED  |           | PTC10             | I2C1_SCL  |                      |          |           |          |      |

| 56         | -               | -         | -         | A5               | PTC11             | DISABLED  |           | PTC11             | I2C1_SDA  |                      |          |           |          |      |

| 57         | -               | -         | 41        | C3               | PTD0              | DISABLED  |           | PTD0              | SPI0_PCS0 |                      | TPM0_CH0 |           | FXIO0_D0 |      |

| 58         | Ι               | -         | 42        | A4               | PTD1              | ADC0_SE5b | ADC0_SE5b | PTD1              | SPI0_SCK  |                      | TPM0_CH1 |           | FXIO0_D1 |      |

| 59         | -               | -         | 43        | C2               | PTD2              | DISABLED  |           | PTD2              | SPI0_MOSI | UART2_RX             | TPM0_CH2 | SPI0_MISO | FXIO0_D2 |      |

| 60         | Ι               | -         | 44        | B3               | PTD3              | DISABLED  |           | PTD3              | SPI0_MISO | UART2_TX             | TPM0_CH3 | SPI0_MOSI | FXIO0_D3 |      |

| 61         | A3              | 29        | 45        | A3               | PTD4/<br>LLWU_P14 | DISABLED  |           | PTD4/<br>LLWU_P14 | SPI1_PCS0 | UART2_RX             | TPM0_CH4 |           | FXIO0_D4 |      |

| 62         | B3              | 30        | 46        | C1               | PTD5              | ADC0_SE6b | ADC0_SE6b | PTD5              | SPI1_SCK  | UART2_TX             | TPM0_CH5 |           | FXIO0_D5 |      |

| 63         | B2              | 31        | 47        | B2               | PTD6/<br>LLWU_P15 | ADC0_SE7b | ADC0_SE7b | PTD6/<br>LLWU_P15 | SPI1_MOSI | LPUART0_<br>RX       | I2C1_SDA | SPI1_MISO | FXIO0_D6 |      |

| 64         | A2              | 32        | 48        | A2               | PTD7              | DISABLED  |           | PTD7              | SPI1_MISO | LPUART0_<br>TX       | I2C1_SCL | SPI1_MOSI | FXIO0_D7 |      |

# 4.2 Pin properties

The following table lists the pin properties.

| 64 LQFP | 36<br>XFBGA | 32 QFN | 48 QFN | 64 MAPBGA | Pin name | Driver strength | Default status after POR | Pullup/ pulldown setting after POR | Slew rate after POR | Passive pin filter after POR | Open drain | Pin interrupt |

|---------|-------------|--------|--------|-----------|----------|-----------------|--------------------------|------------------------------------|---------------------|------------------------------|------------|---------------|

| —       | C1          | —      | —      | _         | PTE17    | ND              | HI-Z                     | —                                  | FS                  | N                            | Ν          | Y             |

|         | D1          | —      | _      |           | PTE18    | ND              | Hi-Z                     | —                                  | FS                  | N                            | Ν          | Y             |

#### Pinouts

| Chip signal name | Module signal<br>name | Description             | I/O |

|------------------|-----------------------|-------------------------|-----|

| LPTMR0_ALT[3:1]  | LPTMR0_ALTn           | Pulse Counter Input pin | I   |

#### Table 19. LPTMR0 signal descriptions

### Table 20. RTC signal descriptions

| Chip signal name        | Module signal<br>name | Description                         | I/O |

|-------------------------|-----------------------|-------------------------------------|-----|

| RTC_CLKOUT <sup>1</sup> | RTC_CLKOUT            | 1 Hz square-wave output or OSCERCLK | 0   |

1. RTC\_CLKOUT can also be driven with OSCERCLK via SIM control bit SIM\_SOPT[RCTCLKOUTSEL]

# 4.3.6 Communication interfaces Table 21. USB FS OTG Signal Descriptions

| Chip signal name | Module signal<br>name | Description                               | I/O |

|------------------|-----------------------|-------------------------------------------|-----|

| USB0_DM          | usb_dm                | USB D- analog data signal on the USB bus. | I/O |

| USB0_DP          | usb_dp                | USB D+ analog data signal on the USB bus. | I/O |

| USB_CLKIN        | _                     | Alternate USB clock input                 | I   |

#### Table 22. SPI0 signal descriptions

| Chip signal name | Module signal<br>name | Description                    | I/O |

|------------------|-----------------------|--------------------------------|-----|

| SPI0_MISO        | MISO                  | Master Data In, Slave Data Out | I/O |

| SPI0_MOSI        | MOSI                  | Master Data Out, Slave Data In | I/O |

| SPI0_SCLK        | SPSCK                 | SPI Serial Clock               | I/O |

| SPI0_PCS0        | SS                    | Slave Select                   | I/O |

#### Table 23. SPI1 signal descriptions

| Chip signal name | Module signal<br>name | Description                    | I/O |

|------------------|-----------------------|--------------------------------|-----|

| SPI1_MISO        | MISO                  | Master Data In, Slave Data Out | I/O |

| SPI1_MOSI        | MOSI                  | Master Data Out, Slave Data In | I/O |

| SPI1_SCLK        | SPSCK                 | SPI Serial Clock               | I/O |

| SPI1_PCS0        | SS                    | Slave Select                   | I/O |

# 4.3.7 Human-machine interfaces (HMI) Table 30. GPIO Signal Descriptions

| Chip signal name | Module signal<br>name | Description                  | I/O |

|------------------|-----------------------|------------------------------|-----|

| PTA[31:0]        | PORTA31-PORTA0        | General-purpose input/output | I/O |

| PTB[31:0]        | PORTB31-PORTB0        | General-purpose input/output | I/O |

| PTC[11:0]        | PORTC11-PORTC0        | General-purpose input/output | I/O |

| PTD[7:0]         | PORTD7-PORTD0         | General-purpose input/output | I/O |

| PTE[31:0]        | PORTE31-PORTE0        | General-purpose input/output | I/O |

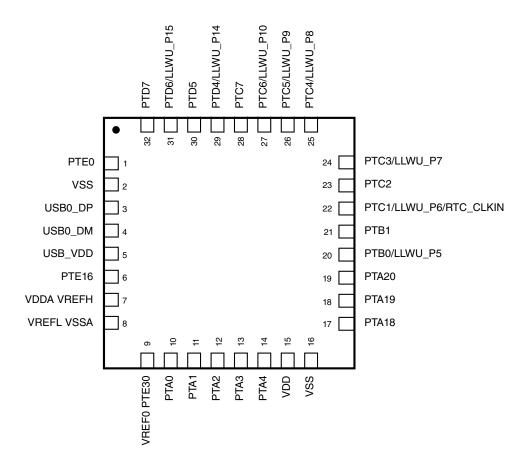

# 4.4 KL27 Family Pinouts

The figure below shows the 32 QFN pinouts.

Figure 6. 32 QFN Pinout diagram (transparent top view)

The figure below shows the 48 QFN pinouts.

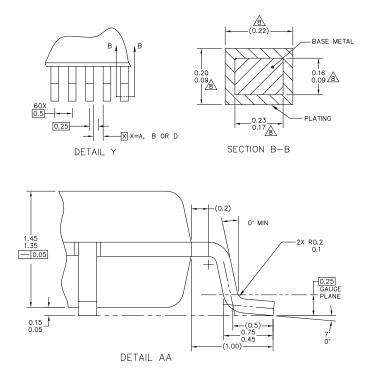

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- A DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

- $\underline{\bigtriangleup}$  dimensions to be determined at seating plane c.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 MM AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 MM.

- THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

- $\triangle$  exact shape of each corner is optional.

### Figure 12. 64-pin LQFP package dimensions 2

| Symbol             | Description                                                | Min. | Тур. | Max. | Unit | Notes |

|--------------------|------------------------------------------------------------|------|------|------|------|-------|

| V <sub>LVW1H</sub> | Level 1 falling (LVWV = 00)                                | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$        | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>            | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>            | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$        | • Level 4 falling (LVWV = 11)                              | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range  | _    | ±60  | _    | mV   | _     |

| V <sub>LVDL</sub>  | Falling low-voltage detect threshold — low range (LVDV=00) | 1.54 | 1.60 | 1.66 | V    | _     |

|                    | Low-voltage warning thresholds — low range                 |      |      |      |      | 1     |

| $V_{LVW1L}$        | • Level 1 falling (LVWV = 00)                              | 1.74 | 1.80 | 1.86 | v    |       |

| $V_{LVW2L}$        | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>            | 1.84 | 1.90 | 1.96 | v    |       |

| V <sub>LVW3L</sub> | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>            | 1.94 | 2.00 | 2.06 | v    |       |

| $V_{LVW4L}$        | • Level 4 falling (LVWV = 11)                              | 2.04 | 2.10 | 2.16 | v    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis — low range   | _    | ±40  | _    | mV   | _     |

| V <sub>BG</sub>    | Bandgap voltage reference                                  | 0.97 | 1.00 | 1.03 | V    | _     |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed     | 900  | 1000 | 1100 | μs   | -     |

Table 36. V<sub>DD</sub> supply LVD and POR operating requirements (continued)

1. Rising thresholds are falling threshold + hysteresis voltage

### 5.2.2.3 Voltage and current operating behaviors Table 37. Voltage and current operating behaviors

| Symbol           | Description                                                             | Min.                  | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------|-----------------------|------|------|-------|

| V <sub>OH</sub>  | Output high voltage — normal drive pad                                  |                       |      |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -5 mA    | V <sub>DD</sub> – 0.5 | —    | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -2.5 mA | V <sub>DD</sub> – 0.5 | _    | V    |       |

| V <sub>OH</sub>  | Output high voltage — high drive pad                                    |                       |      |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -20 mA   | V <sub>DD</sub> – 0.5 | —    | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -10 mA  | V <sub>DD</sub> – 0.5 | _    | V    |       |

| I <sub>OHT</sub> | Output high current total for all ports                                 | —                     | 100  | mA   |       |

| V <sub>OL</sub>  | Output low voltage — normal drive pad                                   |                       |      |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 5 mA     |                       | 0.5  | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 2.5 mA  |                       | 0.5  | V    |       |

| V <sub>OL</sub>  | Output low voltage — high drive pad                                     |                       |      |      | 1     |

|                  |                                                                         | _                     | 0.5  | V    |       |

| Symbol                 | Description                                                                                                                                                                                              | Min. | Тур. | Max.  | Unit | Notes |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|-------|

|                        | clock disable, 2 MHz core / 0.5 MHz flash, V <sub>DD</sub><br>= 3.0 V<br>• at 25 °C                                                                                                                      |      | 91   | 136.5 | μΑ   |       |

| I <sub>DD_VLPR</sub>   | Very-low-power run mode current— 2 MHz<br>LIRC mode, While(1) loop in flash all peripheral<br>clock disable, 125 kHz core / 31.25 kHz flash,<br>V <sub>DD</sub> = 3.0 V<br>• at 25 °C                    | _    | 34   | 51    | μA   |       |

| I <sub>DD_VLPR</sub>   | Very-low-power run mode current— 8 MHz<br>LIRC mode, While(1) loop in flash all peripheral<br>clock disable, 4 MHz core / 1 MHz flash, V <sub>DD</sub> =<br>3.0 V<br>• at 25 °C                          | _    | 212  | 318   | μΑ   |       |

| I <sub>DD_VLPR</sub>   | Very-low-power run mode current—8 MHz<br>LIRC mode, While(1) loop in flash all peripheral<br>clock enable, 4 MHz core / 1 MHz flash, V <sub>DD</sub> =<br>3.0 V<br>• at 25 °C                            | _    | 302  | 392.6 | μΑ   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 48 MHz<br>system/24 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V<br>• at 25 °C |      | 1.81 | 2.12  | mA   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 24 MHz<br>system/12 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V<br>• at 25 °C | _    | 1.27 | 1.46  | mA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core<br>disabled, 4 MHz system/ 1 MHz bus and flash,<br>all peripheral clocks disabled, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                                          | _    | 156  | 193.2 | μA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core<br>disabled, 2 MHz system/ 0.5 MHz bus and<br>flash, all peripheral clocks disabled, V <sub>DD</sub> = 3.0<br>V<br>• at 25 °C                                     |      | 63   | 100.8 | μA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core<br>disabled, 125 kHz system/ 31.25 kHz bus and<br>flash, all peripheral clocks disabled, V <sub>DD</sub> = 3.0<br>V<br>• at 25 °C                                 | _    | 32   | 48    | μA   |       |

| I <sub>DD_PSTOP2</sub> | Partial Stop 2, core and system clock disabled,<br>12 MHz bus and flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                                                                                           | _    | 1.68 | 2.05  | mA   |       |

| I <sub>DD_PSTOP2</sub> | Partial Stop 2, core and system clock disabled,<br>flash doze enabled, 12 MHz bus, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                                                                                 |      |      |       |      |       |

| Table 39. | Power consum | ption operating | behaviors | (continued) |

|-----------|--------------|-----------------|-----------|-------------|

|           |              |                 | ,         |             |

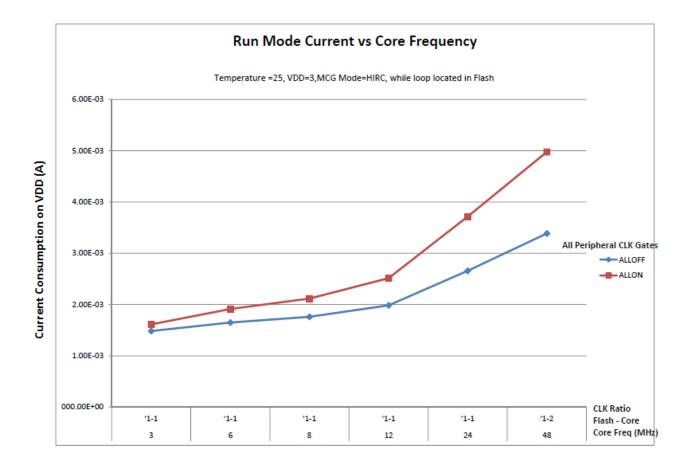

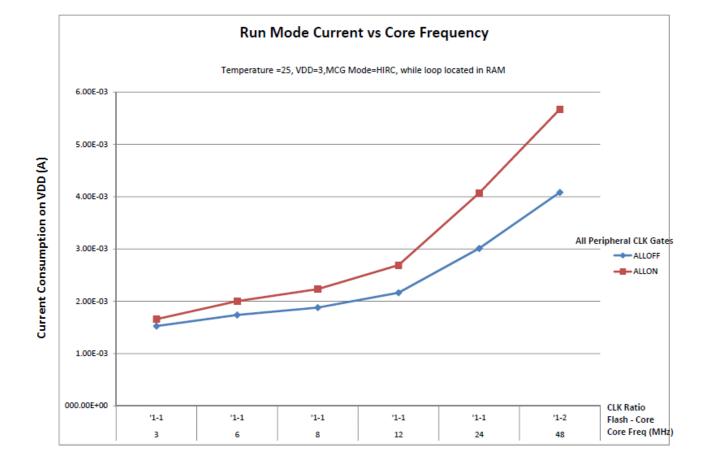

Figure 20. Run mode supply current vs. core frequency

**Electrical characteristics**

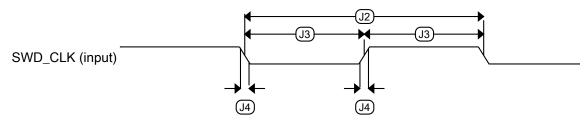

# 5.3.1.1 SWD electricals

| Symbol     | Description                                     | Min. | Max. | Unit |

|------------|-------------------------------------------------|------|------|------|

|            | Operating voltage                               | 1.71 | 3.6  | V    |

| J1         | SWD_CLK frequency of operation                  |      |      |      |

|            | Serial wire debug                               | 0    | 25   | MHz  |

| J2         | SWD_CLK cycle period                            | 1/J1 | _    | ns   |

| J3         | SWD_CLK clock pulse width                       |      |      |      |

|            | Serial wire debug                               | 20   | _    | ns   |

| J4         | SWD_CLK rise and fall times                     |      | 3    | ns   |

| <b>J</b> 9 | SWD_DIO input data setup time to SWD_CLK rise   | 10   | _    | ns   |

| J10        | SWD_DIO input data hold time after SWD_CLK rise | 0    | _    | ns   |

| J11        | SWD_CLK high to SWD_DIO data valid              | _    | 32   | ns   |

| J12        | SWD_CLK high to SWD_DIO high-Z                  | 5    | _    | ns   |

Figure 22. Serial wire clock input timing

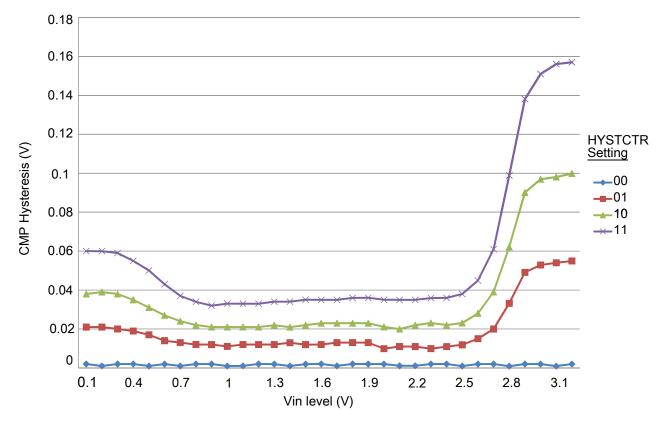

Figure 28. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

# 5.4 Timers

See General switching specifications.

# 5.5 Communication interfaces

# 5.5.1 USB electrical specifications

The USB electricals for the USB device module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit usb.org .

### NOTE

The IRC48M meets the USB jitter specifications for certification in Device mode when the USB clock recovery mode is enabled.

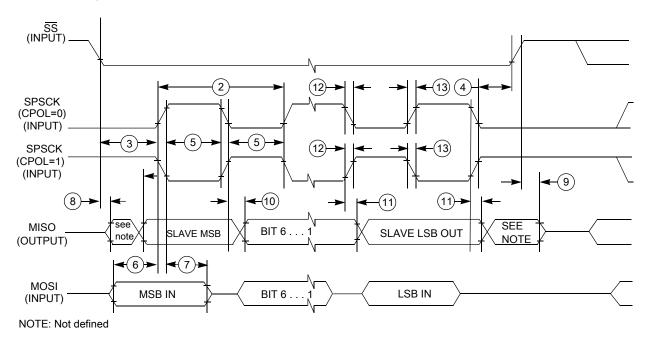

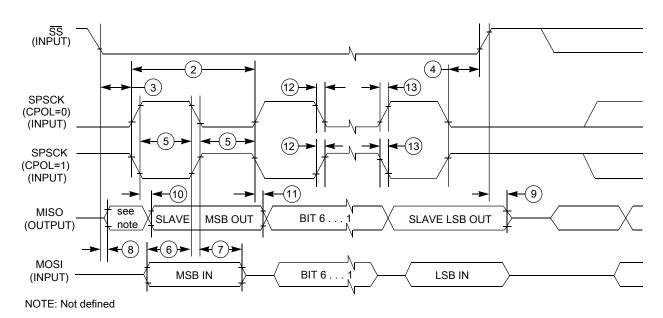

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  |                          | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | —                        | t <sub>periph</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | _                        | ns                  | _    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2                        | —                        | ns                  | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 7                        | —                        | ns                  | _    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | _                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                        | 122                      | ns                  | _    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | _    |

| 12   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> - 25 | ns                  | _    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 36                       | ns                  | -    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

Table 64. SPI slave mode timing on slew rate enabled pads

1. For SPI0 f<sub>periph</sub> is the bus clock (f<sub>BUS</sub>). For SPI1 f<sub>periph</sub> is the system clock (f<sub>SYS</sub>).

- 2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

#### **Electrical characteristics**

Figure 32. SPI slave mode timing (CPHA = 1)

### 5.5.3 Inter-Integrated Circuit Interface (I2C) timing Table 65. I2C timing

| Characteristic                                                                                     | Symbol                | Standa           | rd Mode           | Fast                               | Unit             |     |

|----------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|-----|

|                                                                                                    |                       | Minimum          | Maximum           | Minimum                            | Maximum          |     |

| SCL Clock Frequency                                                                                | f <sub>SCL</sub>      | 0                | 100               | 0                                  | 400 <sup>1</sup> | kHz |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA | 4                | _                 | 0.6                                | _                | μs  |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>      | 4.7              | —                 | 1.25                               | —                | μs  |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>     | 4                | —                 | 0.6                                | —                | μs  |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA | 4.7              | —                 | 0.6                                | —                | μs  |

| Data hold time for I <sup>2</sup> C bus devices                                                    | t <sub>HD</sub> ; DAT | 0 <sup>2</sup>   | 3.45 <sup>3</sup> | 04                                 | 0.9 <sup>2</sup> | μs  |

| Data set-up time                                                                                   | t <sub>SU</sub> ; DAT | 250 <sup>5</sup> | —                 | 100 <sup>3</sup> , <sup>6</sup>    | —                | ns  |

| Rise time of SDA and SCL signals                                                                   | t <sub>r</sub>        | —                | 1000              | 20 +0.1C <sub>b</sub> <sup>7</sup> | 300              | ns  |

| Fall time of SDA and SCL signals                                                                   | t <sub>f</sub>        | _                | 300               | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns  |

| Set-up time for STOP condition                                                                     | t <sub>SU</sub> ; STO | 4                | _                 | 0.6                                | —                | μs  |

| Bus free time between STOP and<br>START condition                                                  | t <sub>BUF</sub>      | 4.7              | _                 | 1.3                                | —                | μs  |

| Pulse width of spikes that must be<br>suppressed by the input filter                               | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns  |

1. The maximum SCL Clock Frequency in Fast mode with maximum bus loading can be achieved only when using the high drive pins across the full voltage range and when using the normal drive pins and VDD ≥ 2.7 V.

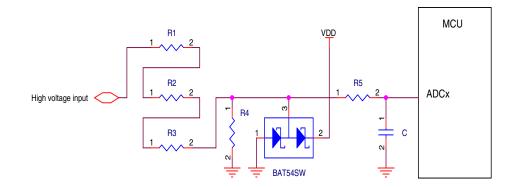

High voltage measurement circuits require voltage division, current limiting, and overvoltage protection as shown the following figure. The voltage divider formed by R1 – R4 must yield a voltage less than or equal to VREFH. The current must be limited to less than the injection current limit. Since the ADC pins do not have diodes to VDD, external clamp diodes must be included to protect against transient over-voltages.

Figure 35. High voltage measurement with an ADC input

# 6.1.4 Digital design

Ensure that all I/O pins cannot get pulled above VDD (Max I/O is VDD+0.3V).

# CAUTION

Do not provide power to I/O pins prior to VDD, especially the RESET\_b pin.

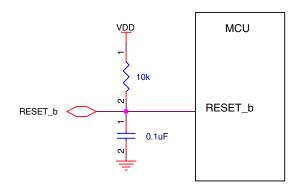

• RESET\_b pin

The RESET\_b pin is an open-drain I/O pin that has an internal pullup resistor. An external RC circuit is recommended to filter noise as shown in the following figure. The resistor value must be in the range of 4.7 k $\Omega$  to 10 k $\Omega$ ; the recommended capacitance value is 0.1  $\mu$ F. The RESET\_b pin also has a selectable digital filter to reject spurious noise.

### Figure 36. Reset circuit

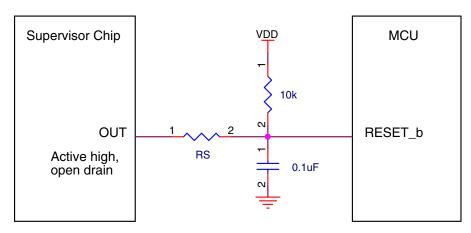

When an external supervisor chip is connected to the RESET\_b pin, a series resistor must be used to avoid damaging the supervisor chip or the RESET\_b pin, as shown in the following figure. The series resistor value (RS below) must be in the range of  $100 \Omega$  to  $1 \text{ k}\Omega$  depending on the external reset chip drive strength. The supervisor chip must have an active high, open-drain output.

Figure 37. Reset signal connection to external reset chip

# • NMI pin

Do not add a pull-down resistor or capacitor on the NMI\_b pin, because a low level on this pin will trigger non-maskable interrupt. When this pin is enabled as the NMI function, an external pull-up resistor (10 k $\Omega$ ) as shown in the following figure is recommended for robustness.

If the NMI\_b pin is used as an I/O pin, the non-maskable interrupt handler is required to disable the NMI function by remapping to another function. The NMI function is disabled by programming the FOPT[NMI\_DIS] bit to zero.

Design considerations

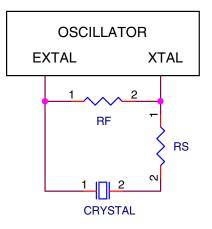

### Figure 41. Crystal connection – Diagram 2

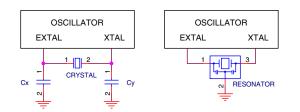

### Figure 42. Crystal connection – Diagram 3

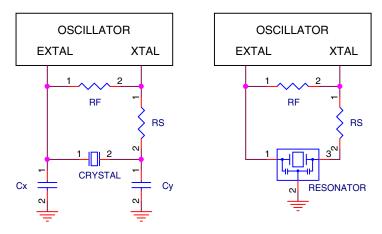

Figure 43. Crystal connection – Diagram 4

# 6.2 Software considerations

All Kinetis MCUs are supported by comprehensive Freescale and third-party hardware and software enablement solutions, which can reduce development costs and time to market. Featured software and tools are listed below. Visit http://www.freescale.com/kinetis/sw for more information and supporting collateral.

Evaluation and Prototyping Hardware

98