# E·XFL

Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

## Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are analyzared to

#### Details

| Betano                  |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Active                                                                     |

| Applications            | USB Microcontroller                                                        |

| Core Processor          | M8B                                                                        |

| Program Memory Type     | OTP (8kB)                                                                  |

| Controller Series       | CY7C634xx                                                                  |

| RAM Size                | 256 x 8                                                                    |

| Interface               | PS/2, USB                                                                  |

| Number of I/O           | 32                                                                         |

| Voltage - Supply        | 4V ~ 5.5V                                                                  |

| Operating Temperature   | 0°C ~ 70°C                                                                 |

| Mounting Type           | Surface Mount                                                              |

| Package / Case          | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package | 48-SSOP                                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c63413c-pvxc |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

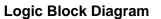

The Cypress microcontrollers use an external 6-MHz ceramic resonator to provide a reference to an internal clock generator. This clock generator reduces the clock-related noise emissions (EMI). The clock generator provides the 6 and 12-MHz clocks that remain internal to the microcontroller.

The CY7C63413C/513C/613C are offered with single EPROM options. The CY7C63413C, CY7C63513C and the CY7C63613C have 8 Kbytes of EPROM.

These parts include Power-on Reset logic, a Watch Dog Timer, a vectored interrupt controller, and a 12-bit free-running timer. The Power-On Reset (POR) logic detects when power is applied to the device, resets the logic to a known state, and begins executing instructions at EPROM address 0x0000. The Watch Dog Timer can be used to ensure the firmware never gets stalled for more than approximately 8 ms. The firmware can get stalled for a variety of reasons, including errors in the code or a hardware failure such as waiting for an interrupt that never occurs. The firmware should clear the Watch Dog Timer periodically. If the Watch Dog Timer is not cleared for approximately 8 ms, the microcontroller will generate a hardware watch dog reset.

The microcontroller supports eight maskable interrupts in the vectored interrupt controller. Interrupt sources include the USB Bus-Reset, the 128- $\mu$ s and 1.024-ms outputs from the free-running timer, three USB endpoints, the DAC port, and the GPIO ports. The timer bits cause an interrupt (if enabled) when the bit toggles from LOW "0" to HIGH "1." The USB endpoints interrupt after either the USB host or the USB controller sends a packet to the USB. The DAC ports have an additional level of masking that allows the user to select which DAC inputs can

cause a DAC interrupt. The GPIO ports also have a level of masking to select which GPIO inputs can cause a GPIO interrupt. For additional flexibility, the input transition polarity that causes an interrupt is programmable for each pin of the DAC port. Input transition polarity can be programmed for each GPIO port as part of the port configuration. The interrupt polarity can be either rising edge ("0" to "1") or falling edge ("1" to "0").

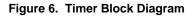

The free-running 12-bit timer clocked at 1 MHz provides two interrupt sources as noted above (128-µs and 1.024-ms). The timer can be used to measure the duration of an event under firmware control by reading the timer twice: once at the start of the event, and once after the event is complete. The difference between the two readings indicates the duration of the event measured in microseconds. The upper four bits of the timer are latched into an internal register when the firmware reads the lower eight bits. A read from the upper four bits actually reads data from the internal register, instead of the timer. This feature eliminates the need for firmware to attempt to compensate if the upper four bits happened to increment right after the lower 8 bits are read.

The CY7C63413C/513C/613C include an integrated USB serial interface engine (SIE) that supports the integrated peripherals. The hardware supports one USB device address with three endpoints. The SIE allows the USB host to communicate with the function integrated into the microcontroller.

Finally, the CY7C63413C/513C/613C support PS/2 operation. With appropriate firmware the D+ and D– USB pins can also be used as PS/2 clock and data signals. Products utilizing these devices can be used for USB and/or PS/2 operation with appropriate firmware.

# CY7C63413C CY7C63513C CY7C63613C

**Pin Configuration**

Note

1. CY7C63613C is not bonded out for all GPIO pins shown in Logic Block Diagram. Refer to pin configuration diagram for bonded out pins. See note on page 12 for firmware code needed for unused GPIO pins.

Ċ

PSP,A instruction. The PSP supports interrupt service under hardware control and CALL, RET, and RETI instructions under firmware control.

During an interrupt acknowledge, interrupts are disabled and the 14-bit program counter, carry flag, and zero flag are written as two bytes of data memory. The first byte is stored in the memory addressed by the program stack pointer, then the PSP is incremented. The second byte is stored in memory addressed by the program stack pointer and the PSP is incremented again. The net effect is to store the program counter and flags on the program "stack" and increment the program stack pointer by two.

The Return From Interrupt (RETI) instruction decrements the program stack pointer, then restores the second byte from memory addressed by the PSP. The program stack pointer is decremented again and the first byte is restored from memory addressed by the PSP. After the program counter and flags have been restored from stack, the interrupts are enabled. The effect is to restore the program counter and flags from the program stack, decrement the program stack pointer by two, and re-enable interrupts.

The Call Subroutine (CALL) instruction stores the program counter and flags on the program stack and increments the PSP by two.

The Return From Subroutine (RET) instruction restores the program counter, but not the flags, from program stack and decrements the PSP by two.

## 8-bit Data Stack Pointer (DSP)

The Data Stack Pointer (DSP) supports PUSH and POP instructions that use the data stack for temporary storage. A PUSH instruction will pre-decrement the DSP, then write data to the memory location addressed by the DSP. A POP instruction will read data from the memory location addressed by the DSP, then post-increment the DSP.

During a reset, the Data Stack Pointer will be set to zero. A PUSH instruction when DSP equal zero will write data at the top of the data RAM (address 0xFF). This would write data to the memory area reserved for a FIFO for USB endpoint 0. In non-USB applications, this works fine and is not a problem. For USB applications, it is strongly recommended that the DSP is loaded after reset just below the USB DMA buffers.

## Address Modes

The CY7C63413C/513C/613C microcontrollers support three addressing modes for instructions that require data operands: data, direct, and indexed.

#### Data

The "Data" address mode refers to a data operand that is actually a constant encoded in the instruction. As an example, consider the instruction that loads A with the constant 0xE8:

#### MOV A,0E8h

This instruction will require two bytes of code where the first byte identifies the "MOV A" instruction with a data operand as the second byte. The second byte of the instruction will be the constant "0xE8". A constant may be referred to by name if a prior "EQU" statement assigns the constant value to the name. For example, the following code is equivalent to the example shown above:

■ DSPINIT: EQU 0E8h

MOV A,DSPINIT

## Direct

"Direct" address mode is used when the data operand is a variable stored in SRAM. In that case, the one byte address of the variable is encoded in the instruction. As an example, consider an instruction that loads A with the contents of memory address location 0x10:

#### MOV A, [10h]

In normal usage, variable names are assigned to variable addresses using "EQU" statements to improve the readability of the assembler source code. As an example, the following code is equivalent to the example shown above:

- buttons: EQU 10h

- MOV A,[buttons]

#### Indexed

"Indexed" address mode allows the firmware to manipulate arrays of data stored in SRAM. The address of the data operand is the sum of a constant encoded in the instruction and the contents of the "X" register. In normal usage, the constant will be the "base" address of an array of data and the X register will contain an index that indicates which element of the array is actually addressed:

- array: EQU 10h

- MOV X,3

- MOV A,[x+array]

This would have the effect of loading A with the fourth element of the SRAM "array" that begins at address 0x10. The fourth element would be at address 0x13.

# Instruction Set Summary

| MNEMONIC       | operand | opcode | cycles | MNEMONIC       | operand | opcode | cycles |

|----------------|---------|--------|--------|----------------|---------|--------|--------|

| HALT           |         | 00     | 7      | NOP            |         | 20     | 4      |

| ADD A,expr     | data    | 01     | 4      | INC A          | acc     | 21     | 4      |

| ADD A,[expr]   | direct  | 02     | 6      | INC X          | x       | 22     | 4      |

| ADD A,[X+expr] | index   | 03     | 7      | INC [expr]     | direct  | 23     | 7      |

| ADC A,expr     | data    | 04     | 4      | INC [X+expr]   | index   | 24     | 8      |

| ADC A,[expr]   | direct  | 05     | 6      | DEC A          | acc     | 25     | 4      |

| ADC A,[X+expr] | index   | 06     | 7      | DEC X          | x       | 26     | 4      |

| SUB A,expr     | data    | 07     | 4      | DEC [expr]     | direct  | 27     | 7      |

| SUB A,[expr]   | direct  | 08     | 6      | DEC [X+expr]   | index   | 28     | 8      |

| SUB A,[X+expr] | index   | 09     | 7      | IORD expr      | address | 29     | 5      |

| SBB A,expr     | data    | 0A     | 4      | IOWR expr      | address | 2A     | 5      |

| SBB A,[expr]   | direct  | 0B     | 6      | POP A          |         | 2B     | 4      |

| SBB A,[X+expr] | index   | 0C     | 7      | POP X          |         | 2C     | 4      |

| OR A,expr      | data    | 0D     | 4      | PUSH A         |         | 2D     | 5      |

| OR A,[expr]    | direct  | 0E     | 6      | PUSH X         |         | 2E     | 5      |

| OR A,[X+expr]  | index   | 0F     | 7      | SWAP A,X       |         | 2F     | 5      |

| AND A,expr     | data    | 10     | 4      | SWAP A,DSP     |         | 30     | 5      |

| AND A,[expr]   | direct  | 11     | 6      | MOV [expr],A   | direct  | 31     | 5      |

| AND A,[X+expr] | index   | 12     | 7      | MOV [X+expr],A | index   | 32     | 6      |

| XOR A,expr     | data    | 13     | 4      | OR [expr],A    | direct  | 33     | 7      |

| XOR A,[expr]   | direct  | 14     | 6      | OR [X+expr],A  | index   | 34     | 8      |

| XOR A,[X+expr] | index   | 15     | 7      | AND [expr],A   | direct  | 35     | 7      |

| CMP A,expr     | data    | 16     | 5      | AND [X+expr],A | index   | 36     | 8      |

| CMP A,[expr]   | direct  | 17     | 7      | XOR [expr],A   | direct  | 37     | 7      |

| CMP A,[X+expr] | index   | 18     | 8      | XOR [X+expr],A | index   | 38     | 8      |

| MOV A,expr     | data    | 19     | 4      | IOWX [X+expr]  | index   | 39     | 6      |

| MOV A,[expr]   | direct  | 1A     | 5      | CPL            |         | 3A     | 4      |

| MOV A,[X+expr] | index   | 1B     | 6      | ASL            |         | 3B     | 4      |

| MOV X,expr     | data    | 1C     | 4      | ASR            |         | 3C     | 4      |

| MOV X,[expr]   | direct  | 1D     | 5      | RLC            |         | 3D     | 4      |

| reserved       |         | 1E     |        | RRC            |         | 3E     | 4      |

| XPAGE          |         | 1F     | 4      | RET            |         | 3F     | 8      |

| MOV A,X        |         | 40     | 4      | DI             |         | 70     | 4      |

| MOV X,A        |         | 41     | 4      | EI             |         | 72     | 4      |

| MOV PSP,A      |         | 60     | 4      | RETI           |         | 73     | 8      |

| CALL           | addr    | 50-5F  | 10     |                |         |        |        |

| JMP            | addr    | 80-8F  | 5      | JC             | addr    | C0-CF  | 5      |

| CALL           | addr    | 90-9F  | 10     | JNC            | addr    | D0-DF  | 5      |

| JZ             | addr    | A0-AF  | 5      | JACC           | addr    | E0-EF  | 7      |

| JNZ            | addr    | B0-BF  | 5      | INDEX          | addr    | F0-FF  | 14     |

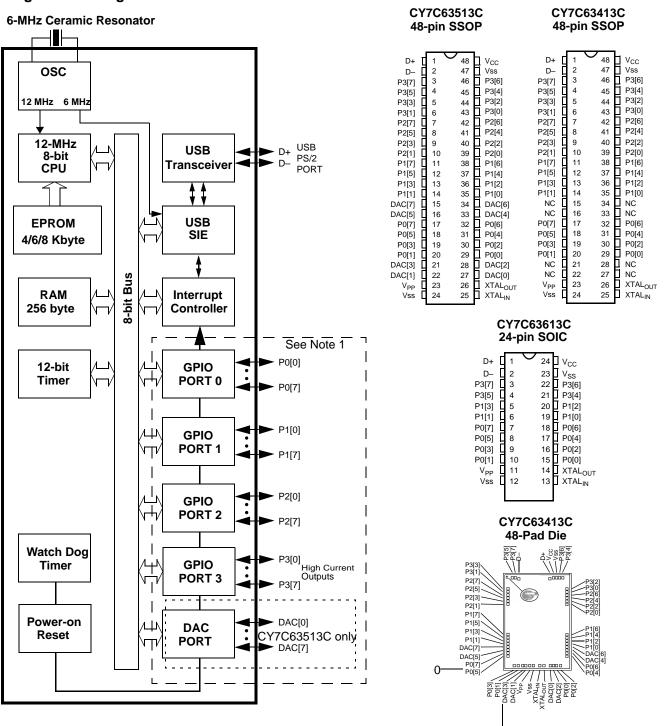

## Figure 2. Clock Oscillator On-chip Circuit

# Clocking

The XTAL<sub>IN</sub> and XTAL<sub>OUT</sub> are the clock pins to the microcontroller. The user can connect a low-cost ceramic resonator or an external oscillator can be connected to these pins to provide a reference frequency for the internal clock distribution and clock doubler.

An external 6-MHz clock can be applied to the XTAL<sub>IN</sub> pin if the XTAL<sub>OUT</sub> pin is left open. Please note that grounding the XTAL<sub>OUT</sub> pin is not permissible as the internal clock is effectively shorted to ground.

## Reset

The USB Controller supports three types of resets. All registers are restored to their default states during a reset. The USB Device Addresses are set to 0 and all interrupts are disabled. In addition, the program stack pointer (PSP) and data stack pointer (DSP) are set to 0x00. For USB applications, the firmware should set the DSP below 0xE8 to avoid a memory conflict with RAM dedicated to USB FIFOs. The assembly instructions to do this are shown below:

Mov A, E8h ; Move 0xE8 hex into Accumulator

Swap A,dsp ; Swap accumulator value into dsp register

The three reset types are:

- 1. Power-On Reset (POR)

- 2. Watch Dog Reset (WDR)

- 3. USB Bus Reset (non hardware reset)

The occurrence of a reset is recorded in the Processor Status and Control Register located at I/O address 0xFF. Bits 4, 5, and 6 are used to record the occurrence of POR, USB Reset, and WDR respectively. The firmware can interrogate these bits to determine the cause of a reset.

The microcontroller begins execution from ROM address 0x0000 after a POR or WDR reset. Although this looks like interrupt vector 0, there is an important difference. Reset processing does NOT push the program counter, carry flag, and zero flag onto program stack. That means the reset handler in firmware should initialize the hardware and begin executing the "main" loop of code. Attempting to execute either a RET or RETI in the reset handler will cause unpredictable execution results.

## Power-On Reset (POR)

Power-On Reset (POR) occurs every time the  $V_{CC}$  voltage to the device ramps from 0V to an internally defined trip voltage (Vrst)

of approximately 1/2 full supply voltage. In addition to the normal reset initialization noted under "Reset," bit 4 (PORS) of the Processor Status and Control Register is set to "1" to indicate to the firmware that a Power-On Reset occurred. The POR event forces the GPIO ports into input mode (high impedance), and the state of Port 3 bit 7 is used to control how the part will respond after the POR releases.

If Port 3 bit 7 is HIGH (pulled to  $V_{CC}$ ) and the USB I/O are at the idle state (DM HIGH and DP LOW) the part will go into a semi-permanent power down/suspend mode, waiting for the USB I/O to go to one of Bus Reset, K (resume) or SE0. If Port 3 bit 7 is still HIGH when the part comes out of suspend, then a 128- $\mu$ s timer starts, delaying CPU operation until the ceramic resonator has stabilized.

If Port 3 bit 7 was LOW (pulled to  $V_{SS}$ ) the part will start a 96-ms timer, delaying CPU operation until  $V_{CC}$  has stabilized, then continuing to run as reset.

Firmware should clear the POR Status (PORS) bit in register 0xFF before going into suspend as this status bit selects the 128- $\mu$ s or 96-ms start-up timer value as follows: IF Port 3 bit 7 is HIGH then 128- $\mu$ s is always used; ELSE if PORS is HIGH then 96-ms is used; ELSE 128- $\mu$ s is used.

## Watch Dog Reset (WDR)

The Watch Dog Timer Reset (WDR) occurs when the Most Significant Bit (MSB) of the 2-bit Watch Dog Timer Register transitions from LOW to HIGH. In addition to the normal reset initialization noted under "Reset," bit 6 of the Processor Status and Control Register is set to "1" to indicate to the firmware that a Watch Dog Reset occurred.

The Watch Dog Timer is a 2-bit timer clocked by a 4.096-ms clock (bit 11) from the free-running timer. Writing any value to the write-only Watch Dog Clear I/O port (0x26) will clear the Watch Dog Timer.

In some applications, the Watch Dog Timer may be cleared in the 1.024-ms timer interrupt service routine. If the 1.024-ms timer interrupt service routine does not get executed for 8.192 ms or more, a Watch Dog Timer Reset will occur. A Watch Dog Timer Reset lasts for 2.048 ms after which the microcontroller begins execution at ROM address 0x0000. The USB transmitter is disabled by a Watch Dog Reset because the USB Device Address Register is cleared. Otherwise, the USB Controller would respond to all address 0 transactions. The USB transmitter remains disabled until the MSB of the USB address register is set.

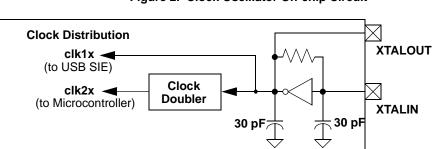

# **General Purpose I/O Ports**

Ports 0 to 2 provide 24 GPI/O pins that can be read or written. Each port (8 bits) can be configured as inputs with internal pull-ups, open drain outputs, or traditional CMOS outputs. Please note an open drain output is also a high-impedance (no pull-up) input. All of the I/O pins within a given port have the same configuration. Ports 0 to 2 are considered low current drive with typical current sink capability of 7 mA.

The internal pull-up resistors are typically 7 k $\Omega$ . Two factors govern the enabling and disabling of the internal pull-up

resistors: the port configuration selected in the GPI/O Configuration register and the state of the output data bit. If the GPI/O Configuration selected is "Resistive" and the output data bit is "1," then the internal pull-up resistor is enabled for that GPI/O pin. Otherwise, Q1 is turned off and the 7-k $\Omega$  pull-up is disabled. Q2 is "ON" to sink current whenever the output data bit is written as a "0." Q3 provides "HIGH" source current when the GPI/O port is configured for CMOS outputs and the output data bit is written as a "1". Q2 and Q3 are sized to sink and source, respectively, roughly the same amount of current to support traditional CMOS outputs with symmetric drive.

## Figure 3. Block Diagram of a GPIO Line

| Table | 2. P        | ort 0 | Data |

|-------|-------------|-------|------|

| Tuble | <u> .</u> . | 011.0 | Dutu |

| Addr  | : 0x00 |       | Port 0 Data |       |       |       |       |

|-------|--------|-------|-------------|-------|-------|-------|-------|

| P0[7] | P0[6]  | P0[5] | P0[4]       | P0[3] | P0[2] | P0[1] | P0[0] |

| R/W   | R/W    | R/W   | R/W         | R/W   | R/W   | R/W   | R/W   |

## Table 3. Port 1 Data

| Addr: | 0x01  | Port 1 Data |       |       |       |       |       |

|-------|-------|-------------|-------|-------|-------|-------|-------|

| P1[7] | P1[6] | P1[5]       | P1[4] | P1[3] | P1[2] | P1[1] | P1[0] |

| R/W   | R/W   | R/W         | R/W   | R/W   | R/W   | R/W   | R/W   |

## Table 7. Port 0 Interrupt Enable

| Addr  | : 0x04 |       | Port 0 Interrupt Enable |   |   |   |       |

|-------|--------|-------|-------------------------|---|---|---|-------|

| P0[7] | P0[6]  | P0[5] | P0[5] P0[4] P0[3] P0[2] |   |   |   | P0[0] |

| W     | W      | W     | W                       | W | W | W | W     |

## Table 8. Port 1 Interrupt Enable

| Addr  | : 0x05 |       | Port 1 Interrupt Enable |       |       |       |       |

|-------|--------|-------|-------------------------|-------|-------|-------|-------|

| P1[7] | P1[6]  | P1[5] | P1[4]                   | P1[3] | P1[2] | P1[1] | P1[0] |

| W     | W      | W     | W                       | W     | W     | W     | W     |

#### Table 9. Port 2 Interrupt Enable

| Addr  | : 0x06 |       | Port 2 Interrupt Enable |       |       |       |       |

|-------|--------|-------|-------------------------|-------|-------|-------|-------|

| P2[7] | P2[6]  | P2[5] | P2[4]                   | P2[3] | P2[2] | P2[1] | P2[0] |

| W     | W      | W     | W                       | W     | W     | W     | W     |

#### Table 10. Port 3 Interrupt Enable

| Addr                                  | : 0x07 |       | Port 3 Interrupt Enable |       |       |       |       |

|---------------------------------------|--------|-------|-------------------------|-------|-------|-------|-------|

| P3[7]                                 | P3[6]  | P3[5] | P3[4]                   | P3[3] | P3[2] | P3[1] | P3[0] |

| W                                     | W      | W     | W                       | W     | W     | W     | W     |

| Table 44 Descible Dert Configurations |        |       |                         |       |       |       |       |

## Table 11. Possible Port Configurations

| Port Configuration bits | Pin Interrupt Bit | Driver Mode | Interrupt Polarity |

|-------------------------|-------------------|-------------|--------------------|

| 11                      | Х                 | Resistive   | -                  |

| 10                      | 0                 | CMOS Output | disabled           |

| 10                      | 1                 | Open Drain  | disabled           |

| 01                      | Х                 | Open Drain  | -                  |

| 00                      | Х                 | Open Drain  | + (default)        |

In "Resistive" mode, a 7-k $\Omega$  pull-up resistor is conditionally enabled for all pins of a GPIO port. The resistor is enabled for any pin that has been written as a "1." The resistor is disabled on any pin that has been written as a "0." An I/O pin will be driven high through a 7-k $\Omega$  pull-up resistor when a "1" has been written to the pin. Or the output pin will be driven LOW, with the pull-up disabled, when a "0" has been written to the pin. An I/O pin that has been written as a "1" can be used as an input pin with an integrated 7-k $\Omega$  pull-up resistor. Resistive mode selects a negative (falling edge) interrupt polarity on all pins that have the GPIO interrupt enabled.

In "CMOS" mode, all pins of the GPIO port are outputs that are actively driven. The current source and sink capacity are roughly the same (symmetric output drive). A CMOS port is not a possible source for interrupts.

A port configured in CMOS mode has interrupt generation disabled, yet the interrupt mask bits serve to control port

direction. If a port's associated Interrupt Mask bits are cleared, those port bits are strictly outputs. If the Interrupt Mask bits are set then those bits will be open drain inputs. As open drain inputs, if their data output values are '1' those port pins will be CMOS inputs (HIGH Z output).

In "Open Drain" mode the internal pull-up resistor and CMOS driver (HIGH) are both disabled. An I/O pin that has been written as a "1" can be used as either a high-impedance input or a three-state output. An I/O pin that has been written as a "0" will drive the output LOW. The interrupt polarity for an open drain GPIO port can be selected as either positive (rising edge) or negative (falling edge).

During reset, all of the bits in the GPIO Configuration Register are written with "0." This selects the default configuration: Open Drain output, positive interrupt polarity for all GPIO ports.

| Addr:                  | Addr: 0x08             |                        | GPIO Configuration Register |                        |                        |                        |                        |

|------------------------|------------------------|------------------------|-----------------------------|------------------------|------------------------|------------------------|------------------------|

| 7                      | 6                      | 5                      | 4                           | 3                      | 2                      | 1                      | 0                      |

| Port 3<br>Config Bit 1 | Port 3<br>Config Bit 0 | Port 2<br>Config Bit 1 | Port 2<br>Config Bit 0      | Port 1<br>Config Bit 1 | Port 1<br>Config Bit 0 | Port 0<br>Config Bit 1 | Port 0<br>Config Bit 0 |

| W                      | W                      | W                      | W                           | W                      | W                      | W                      | W                      |

## Table 12. GPIO Configuration Register

# **DAC Port**

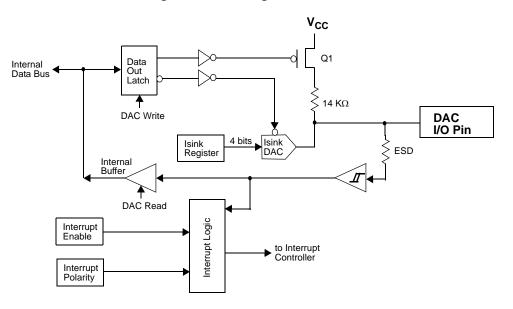

Figure 5. Block Diagram of DAC Port

## Table 13. DAC Port Data

| Addr                                            | : 0x30              |        | DAC Po | ort Data |                            |                             |        |

|-------------------------------------------------|---------------------|--------|--------|----------|----------------------------|-----------------------------|--------|

| Low current outputs<br>0.2 mA to 1.0 mA typical |                     |        |        |          | High curre<br>3.2 mA to 10 | ent outputs<br>6 mA typical |        |

| DAC[7]                                          | DAC[6]              | DAC[5] | DAC[4] | DAC[3]   | DAC[2]                     | DAC[1]                      | DAC[0] |

| R/W                                             | R/W R/W R/W R/W R/W |        |        |          |                            | R/W                         | R/W    |

The DAC port provides the CY7C63513C with 8 programmable current sink I/O pins. Writing a "1" to a DAC I/O pin disables the output current sink (Isink DAC) and drives the I/O pin HIGH through an integrated 14 Kohm resistor. When a "0" is written to a DAC I/O pin, the Isink DAC is enabled and the pull-up resistor is disabled. A "0" output will cause the Isink DAC to sink current to drive the output LOW. The amount of sink current for the DAC I/O pin is programmable over 16 values based on the contents of the DAC Isink Register for that output pin. DAC[1:0] are the two high current outputs that are programmable from a minimum of 3.2 mA to a maximum of 16 mA (typical). DAC[7:2] are low current outputs that are programmable from a minimum of 0.2 mA to a maximum of 1.0 mA (typical).

When a DAC I/O bit is written as a "1," the I/O pin is either an output pulled high through the 14 Kohm resistor or an input with an internal 14 Kohm pull-up resistor. All DAC port data bits are set to "1" during reset.

## **DAC Port Interrupts**

A DAC port interrupt can be enabled/disabled for each pin individually. The DAC Port Interrupt Enable register provides this feature with an interrupt mask bit for each DAC I/O pin. Writing a "1" to a bit in this register enables interrupts from the corresponding bit position. Writing a "0" to a bit in the DAC Port Interrupt Enable register disables interrupts from the corresponding bit position. All of the DAC Port Interrupt Enable register bits are cleared to "0" during a reset.

As an additional benefit, the interrupt polarity for each DAC pin is programmable with the DAC Port Interrupt Polarity register. Writing a "0" to a bit selects negative polarity (falling edge) that will cause an interrupt (if enabled) if a falling edge transition occurs on the corresponding input pin. Writing a "1" to a bit in this register selects positive polarity (rising edge) that will cause an interrupt (if enabled) if a rising edge transition occurs on the corresponding input pin. All of the DAC Port Interrupt Polarity register bits are cleared during a reset.

#### **DAC Isink Registers**

Each DAC I/O pin has an associated DAC Isink register to program the output sink current when the output is driven LOW. The first Isink register (0x38) controls the current for DAC[0], the second (0x39) for DAC[1], and so on until the Isink register at 0x3F controls the current to DAC[7].

## Table 14. DAC Port Interrupt Enable

| Addr   | : 0x31 |        | DAC Port Inte |        |        |        |        |

|--------|--------|--------|---------------|--------|--------|--------|--------|

| DAC[7] | DAC[6] | DAC[5] | DAC[4]        | DAC[3] | DAC[2] | DAC[1] | DAC[0] |

| W      | W      | W      | W             | W      | W      | W      | W      |

## Table 15. DAC Port Interrupt Polarity

| Addr:  | 0x32   |        | DAC Port Inte |        |        |        |        |

|--------|--------|--------|---------------|--------|--------|--------|--------|

| DAC[7] | DAC[6] | DAC[5] | DAC[4]        | DAC[3] | DAC[2] | DAC[1] | DAC[0] |

| W      | W      | W      | W             | W      | W      | W      | W      |

## Table 16. DAC Port Isink

| Addr: 0x38-0x3F | DAC Port Inte | errupt Polarity |          |          |          |  |  |  |  |

|-----------------|---------------|-----------------|----------|----------|----------|--|--|--|--|

| Rese            | erved         | Isink Value     |          |          |          |  |  |  |  |

|                 |               | lsink[3]        | lsink[2] | lsink[1] | lsink[0] |  |  |  |  |

|                 |               | W               | W        | W        | W        |  |  |  |  |

The Bus Activity bit is a "sticky" bit that indicates if any non-idle USB event has occurred on the USB bus. The user firmware should check and clear this bit periodically to detect any loss of bus activity. Writing a "0" to the Bus Activity bit clears it while writing a "1" preserves the current value. In other words, the firmware can clear the Bus Activity bit, but only the SIE can set it. The 1.024-ms timer interrupt service routine is normally used to check and clear the Bus Activity bit. The following table shows how the control bits are encoded for this register.

| Control<br>Bits | Control Action                    |

|-----------------|-----------------------------------|

| 000             | Not forcing (SIE controls driver) |

| 001             | Force K (D+ HIGH, D– LOW)         |

| 010             | Force J (D+ LOW, D- HIGH)         |

| 011             | Force SE0 (D+ LOW, D– LOW)        |

| 100             | Force SE0 (D- LOW, D+ LOW)        |

| 101             | Force D– LOW, D+ HiZ              |

| 110             | Force D– HiZ, D+ LOW              |

| 111             | Force D– HiZ, D+ HiZ              |

# **USB** Device

USB Device Address A includes three endpoints: EPA0, EPA1, and EPA2. End Point 0 (EPA0) allows the USB host to recognize, set up, and control the device. In particular, EPA0 is used to receive and transmit control (including set-up) packets.

## **USB** Ports

The USB Controller provides one USB device address with three endpoints. The USB Device Address Register contents are

## Table 18. USB Device Address Register

cleared during a reset, setting the USB device address to zero and marking this address as disabled. Figure 18 shows the format of the USB Address Register.

Bit 7 (Device Address Enable) in the USB Device Address Register must be set by firmware before the serial interface engine (SIE) will respond to USB traffic to this address. The Device Address in bits [6:0] must be set by firmware during the USB enumeration process to an address assigned by the USB host that does not equal zero. This register is cleared by a hardware reset or the USB bus reset.

## **Device Endpoints (3)**

The USB controller communicates with the host using dedicated FIFOs, one per endpoint. Each endpoint FIFO is implemented as 8 bytes of dedicated SRAM. There are three endpoints defined for Device "A" that are labeled "EPA0," "EPA1," and EPA2."

All USB devices are required to have an endpoint number 0 (EPA0) that is used to initialize and control the USB device. End Point 0 provides access to the device configuration information and allows generic USB status and control accesses. End Point 0 is bidirectional as the USB controller can both receive and transmit data.

The endpoint mode registers are cleared during reset. The EPA0 endpoint mode register uses the format shown in Table 19.

Bits[7:5] in the endpoint 0 mode registers (EPA0) are "sticky" status bits that are set by the SIE to report the type of token that was most recently received. The sticky bits must be cleared by firmware as part of the USB processing.

The endpoint mode registers for EPA1 and EPA2 do not use bits [7:5] as shown in Table 20.

| Addr                        | :0x10                      |                            | USB Device Ac              |                            |                            |                            |                            |

|-----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| Device<br>Address<br>Enable | Device<br>Address<br>Bit 6 | Device<br>Address<br>Bit 5 | Device<br>Address<br>Bit 4 | Device<br>Address<br>Bit 3 | Device<br>Address<br>Bit 2 | Device<br>Address<br>Bit 1 | Device<br>Address<br>Bit 0 |

| R/W                         | R/W                        | R/W                        | R/W                        | R/W                        | R/W                        | R/W                        | R/W                        |

#### Table 19. USB Device EPA0, Mode Register

| Addr                             | :0x12                        | U                             | SB Device EPA |               |               |               |               |

|----------------------------------|------------------------------|-------------------------------|---------------|---------------|---------------|---------------|---------------|

| Endpoint 0<br>Set-up<br>Received | Endpoint 0<br>In<br>Received | Endpoint 0<br>Out<br>Received | Acknowledge   | Mode<br>Bit 3 | Mode<br>Bit 2 | Mode<br>Bit 1 | Mode<br>Bit 0 |

| R/W                              | R/W                          | R/W                           | R/W           | R/W           | R/W           | R/W           | R/W           |

#### Table 20. USB Device Endpoint Mode Register

| Γ | Addr: 0x | 14, 0x16            | US  | B Device Endpo |               |               |                    |     |  |  |

|---|----------|---------------------|-----|----------------|---------------|---------------|--------------------|-----|--|--|

|   | Reserved | Reserved Reserved A |     | Acknowledge    | Mode<br>Bit 3 | Mode<br>Bit 2 | ModeModeBit 1Bit 0 |     |  |  |

|   | R/W      | R/W                 | R/W | R/W            | R/W           | R/W           | R/W                | R/W |  |  |

# 12-bit Free-running Timer

The 12-bit timer provides two interrupts (128  $\mu$ s and 1.024 ms) and allows the firmware to directly time events that are up to 4 ms in duration. The lower 8 bits of the timer can be read directly by the firmware. Reading the lower 8 bits latches the upper 4 bits

into a temporary register. When the firmware reads the upper 4 bits of the timer, it is actually reading the count stored in the temporary register. The effect of this logic is to ensure a stable 12-bit timer value can be read, even when the two reads are separated in time.

## Timer (LSB)

#### Table 22. Timer Register

| Addr:          | 0x24           |                | Timer Reg      |                |                |                |                |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Timer<br>Bit 7 | Timer<br>Bit 6 | Timer<br>Bit 5 | Timer<br>Bit 4 | Timer<br>Bit 3 | Timer<br>Bit 2 | Timer<br>Bit 1 | Timer<br>Bit 0 |

| R              | R              | R              | R R            |                | R              | R              | R              |

## Timer (MSB)

#### Table 23. Timer Register

| Addr:    | 0x25     |          | Timer Regi        |   |                 |                |                |

|----------|----------|----------|-------------------|---|-----------------|----------------|----------------|

| Reserved | Reserved | Reserved | Reserved Reserved |   | Timer<br>Bit 10 | Timer<br>Bit 9 | Timer<br>Bit 8 |

|          |          |          |                   | R | R               | R              | R              |

## **Processor Status and Control Register**

## Table 24. Processor Status and Control Register

| Addr:          | 0xFF               | Proc             | Processor Status and Control Register POI<br>W |                                |                   |             |     |  |  |  |  |

|----------------|--------------------|------------------|------------------------------------------------|--------------------------------|-------------------|-------------|-----|--|--|--|--|

| 7              | 6                  | 5 4              |                                                | 3                              | 2                 | 1           | 0   |  |  |  |  |

| IRQ<br>Pending | Watch Dog<br>Reset | USB Bus<br>Reset | Power-on<br>Reset                              | Suspend, Wait<br>for Interrupt | Interrupt<br>Mask | Single Step | Run |  |  |  |  |

| R              | R/W                | R/W              | R/W                                            | R/W                            | R                 | R/W         | R/W |  |  |  |  |

The "Run" (bit 0) is manipulated by the HALT instruction. When Halt is executed, the processor clears the run bit and halts at the end of the current instruction. The processor remains halted until a reset (Power On or Watch Dog). Notice, when writing to the processor status and control register, the run bit should always be written as a "1."

The "Single Step" (bit 1) is provided to support a hardware debugger. When single step is set, the processor will execute one instruction and halt (clear the run bit). This bit must be cleared for normal operation.

The "Interrupt Mask" (bit 2) shows whether interrupts are enabled or disabled. The firmware has no direct control over this bit as writing a zero or one to this bit position will have no effect on interrupts. Instructions DI, EI, and RETI manipulate the internal hardware that controls the state of the interrupt mask bit in the Processor Status and Control Register.

Writing a "1" to "Suspend, Wait for Interrupts" (bit 3) will halt the processor and cause the microcontroller to enter the "suspend" mode that significantly reduces power consumption. A pending interrupt or bus activity will cause the device to come out of suspend. After coming out of suspend, the device will resume firmware execution at the instruction following the IOWR which put the part into suspend. An IOWR that attempts to put the part into suspend will be ignored if either bus activity or an interrupt is pending.

The "Power-on Reset" (bit 4) is only set to "1" during a power on reset. The firmware can check bits 4 and 6 in the reset handler to determine whether a reset was caused by a Power On condition or a Watch Dog Timeout. PORS is used to determine suspend start-up timer value of 128  $\mu$ s or 96 ms.

The "USB Bus Reset" (bit 5) will occur when a USB bus reset is received. The USB Bus Reset is a singled-ended zero (SE0) that lasts more than 8 microseconds. An SE0 is defined as the condition in which both the D+ line and the D– line are LOW at the same time. When the SIE detects this condition, the USB Bus Reset bit is set in the Processor Status and Control register and an USB Bus Reset interrupt is generated. Please note this is an interrupt to the microcontroller and does not actually reset the processor.

The "Watch Dog Reset" (bit 6) is set during a reset initiated by the Watch Dog Timer. This indicates the Watch Dog Timer went for more than 8 ms between watch dog clears. The "IRQ Pending" (bit 7) indicates one or more of the interrupts has been recognized as active. The interrupt acknowledge sequence should clear this bit until the next interrupt is detected.

During Power-on Reset, the Processor Status and Control Register is set to 00010001, which indicates a Power-on Reset (bit 4 set) has occurred and no interrupts are pending (bit 7 clear) yet.

During a Watch Dog Reset, the Processor Status and Control Register is set to 01000001, which indicates a Watch Dog Reset (bit 6 set) has occurred and no interrupts are pending (bit 7 clear) yet.

## Interrupts

All interrupts are maskable by the Global Interrupt Enable Register and the USB End Point Interrupt Enable Register. Writing a "1" to a bit position enables the interrupt associated with that bit position. During a reset, the contents the Global Interrupt Enable Register and USB End Point Interrupt Enable Register are cleared, effectively disabling all interrupts.

Pending interrupt requests are recognized during the last clock cycle of the current instruction. When servicing an interrupt, the hardware will first disable all interrupts by clearing the Interrupt Enable bit in the Processor Status and Control Register. Next, the interrupt latch of the current interrupt is cleared. This is followed by a CALL instruction to the ROM address associated with the interrupt being serviced (i.e., the Interrupt Vector). The instruction in the interrupt table is typically a JMP instruction to the address of the Interrupt Service Routine (ISR). The user can re-enable interrupts in the interrupt service routine by executing an El instruction. Interrupts can be nested to a level limited only by the available stack space.

The Program Counter value as well as the Carry and Zero flags (CF, ZF) are automatically stored onto the Program Stack by the CALL instruction as part of the interrupt acknowledge process. The user firmware is responsible for insuring that the processor state is preserved and restored during an interrupt. The PUSH A instruction should be used as the first command in the ISR to save the accumulator value and the POP A instruction should be used just before the RETI instruction to restore the accumulator value. The program counter CF and ZF are restored and interrupts are enabled when the RETI instruction is executed.

interrupt priority to different DAC pins and the DAC Interrupt Enable Register is not cleared during the interrupt acknowledge process.

#### **GPIO** Interrupt

Each of the 32 GPIO pins can generate an interrupt, if enabled. The interrupt polarity can be programmed for each GPIO port as part of the GPIO configuration. All of the GPIO pins share a single interrupt vector, which means the firmware will need to read the GPIO ports with enabled interrupts to determine which pin or pins caused an interrupt.

Please note that if one port pin triggered an interrupt, no other port pins can cause a GPIO interrupt until that port pin has returned to its inactive (non-trigger) state or its corresponding port interrupt enable bit is cleared. The USB Controller does not assign interrupt priority to different port pins and the Port Interrupt Enable Registers are not cleared during the interrupt acknowledge process.

## Truth Tables

## Table 27. USB Register Mode Encoding

| Mode                | Encoding | Setup  | In     | Out    | Comments                                                           |

|---------------------|----------|--------|--------|--------|--------------------------------------------------------------------|

| Disable             | 0000     | ignore | ignore | ignore | Ignore all USB traffic to this endpoint                            |

| Nak In/Out          | 0001     | accept | NAK    | NAK    | Forced from Set-up on Control endpoint, from modes other than 0000 |

| Status Out Only     | 0010     | accept | stall  | check  | For Control endpoints                                              |

| Stall In/Out        | 0011     | accept | stall  | stall  | For Control endpoints                                              |

| Ignore In/Out       | 0100     | accept | ignore | ignore | For Control endpoints                                              |

| Isochronous Out     | 0101     | ignore | ignore | always | Available to low speed devices, future USB spec<br>enhancements    |

| Status In Only      | 0110     | accept | TX 0   | stall  | For Control Endpoints                                              |

| Isochronous In      | 0111     | ignore | TX cnt | ignore | Available to low speed devices, future USB spec<br>enhancements    |

| Nak Out             | 1000     | ignore | ignore | NAK    | An ACK from mode 1001> 1000                                        |

| Ack Out             | 1001     | ignore | ignore | ACK    | This mode is changed by SIE on issuance of ACK> 1000               |

| Nak Out - Status In | 1010     | accept | TX 0   | NAK    | An ACK from mode 1011> 1010                                        |

| Ack Out - Status In | 1011     | accept | TX 0   | ACK    | This mode is changed by SIE on issuance of ACK> 1010               |

| Nak In              | 1100     | ignore | NAK    | ignore | An ACK from mode 1101> 1100                                        |

| Ack In              | 1101     | ignore | TX cnt | ignore | This mode is changed by SIE on issuance of ACK> 1100               |

| Nak In - Status Out | 1110     | accept | NAK    | check  | An ACK from mode 1111> 1110 NAck In - Status Out                   |

| Ack In - Status Out | 1111     | accept | TX cnt | Check  | This mode is changed by SIE on issuance of ACK>1110                |

The 'In' column represents the SIE's response to the token type.

A disabled endpoint will remain such until firmware changes it, and all endpoints reset to disabled.

Any Setup packet to an enabled and accepting endpoint will be changed by the SIE to 0001 (NAKing). Any mode which indicates the acceptance of a Setup will acknowledge it.

Most modes that control transactions involving an ending ACK will be changed by the SIE to a corresponding mode which NAKs follow on packets.

A Control endpoint has three extra status bits for PID (Setup, In and Out), but must be placed in the correct mode to function as such. Also a non-Control endpoint can be made to act as a Control endpoint if it is placed in a non appropriate mode.

A 'check' on an Out token during a Status transaction checks to see that the Out is of zero length and has a Data Toggle (DTOG) of 1.

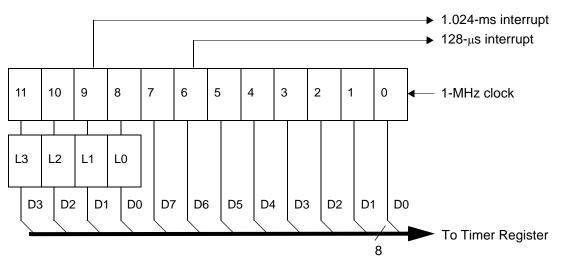

#### Figure 7. Decode table for Table 28: "Details of Modes for Differing Traffic Conditions"

The response of the SIE can be summarized as follows:

- 1. the SIE will only respond to valid transactions, and will ignore non-valid ones;

- 2. the SIE will generate IRQ when a valid transaction is completed or when the DMA buffer is corrupted

- an incoming Data packet is valid if the count is <= 10 (CRC inclusive) and passes all error checking;</li>

- a Setup will be ignored by all non-Control endpoints (in appropriate modes);

- 5. an In will be ignored by an Out configured endpoint and vice versa.

The In and Out PID status is updated at the end of a transaction.

The Setup PID status is updated at the beginning of the Data packet phase.

The entire EndPoint 0 mode and the Count register are locked to CPU writes at the end of any transaction in which an ACK is transferred. These registers are only unlocked upon a CPU read of these registers, and only if that read happens after the transaction completes. This represents about a  $1-\mu$ s window to which to the CPU is locked from register writes to these USB registers. Normally the firmware does a register read at the beginning of the ISR to unlock and get the mode register information. The interlock on the Mode and Count registers ensures that the firmware recognizes the changes that the SIE might have made during the previous transaction.

## Table 28. Details of Modes for Differing Traffic Conditions (continued)

| 0  | 0    | 1     | 0     | Out        | 2     | UC      | valid   | 0       | 1       | updates | UC    | UC | 1   | UC  | 0  | 0    | 1    | 1    | Stall      | yes |

|----|------|-------|-------|------------|-------|---------|---------|---------|---------|---------|-------|----|-----|-----|----|------|------|------|------------|-----|

|    |      |       |       |            |       |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| E  | nd   | Ро    | int   | Mode       |       |         |         |         |         |         | PID   |    |     |     | Se | t En | d P  | oint | Mode       |     |

| 3  | 2    | 1     | 0     | token      | count | buffer  | dval    | DTOG    | DVAL    | COUNT   | Setup | In | Out | ACK | 3  | 2    | 1    | 0    | response   | int |

| 0  | 0    | 1     | 0     | Out        | !=2   | UC      | valid   | updates | 1       | updates | UC    | UC | 1   | UC  | 0  | 0    | 1    | 1    | Stall      | yes |

| 0  | 0    | 1     | 0     | Out        | > 10  | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | UC | UC   | UC   | UC   | ignore     | no  |

| 0  | 0    | 1     | 0     | Out        | х     | UC      | invalid | UC      | UC      | UC      | UC    | UC | UC  | UC  | UC | UC   | UC   | UC   | ignore     | no  |

| 0  | 0    | 1     | 0     | In         | х     | UC      | х       | UC      | UC      | UC      | UC    | 1  | UC  | UC  | 0  | 0    | 1    | 1    | Stall      | yes |

| С  | ut   | enc   | dpo   | int        |       |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| Ν  | orma | al Oi | ut/er | roneous I  | n     |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| 1  | 0    | 0     | 1     | Out        | <= 10 | data    | valid   | updates | 1       | updates | UC    | UC | 1   | 1   | 1  | 0    | 0    | 0    | ACK        | yes |

| 1  | 0    | 0     | 1     | Out        | > 10  | junk    | х       | updates | updates | updates | UC    | UC | 1   | UC  | I  | NoCh | ange |      | ignore     | yes |

| 1  | 0    | 0     | 1     | Out        | х     | junk    | invalid | updates | 0       | updates | UC    | UC | 1   | UC  | I  | NoCh | ange |      | ignore     | yes |

| 1  | 0    | 0     | 1     | In         | х     | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | I  | NoCh | ange | 1    | ignore     | no  |

| Ν  | AK ( | Dut/e | error | neous In   |       |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| 1  | 0    | 0     | 0     | Out        | <= 10 | UC      | valid   | UC      | UC      | UC      | UC    | UC | 1   | UC  | I  | NoCh | ange |      | NAK        | yes |

| 1  | 0    | 0     | 0     | Out        | > 10  | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | 1  | NoCh | ange |      | ignore     | no  |

| 1  | 0    | 0     | 0     | Out        | х     | UC      | invalid | UC      | UC      | UC      | UC    | UC | UC  | UC  | 1  | NoCh | ange |      | ignore     | no  |

| 1  | 0    | 0     | 0     | In         | х     | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | 1  | NoCh | ange |      | ignore     | no  |

| ls | ochr | ono   | us e  | ndpoint (0 | Dut)  |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| 0  | 1    | 0     | 1     | Out        | х     | updates | updates | updates | updates | updates | UC    | UC | 1   | 1   | 1  | NoCh | ange |      | RX         | yes |

| 0  | 1    | 0     | 1     | In         | х     | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | I  | NoCh | ange |      | ignore     | no  |

| Ir | n er | ndp   | oin   | t          |       |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| Ν  | orma | al In | /erro | neous Ou   | ut    |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| 1  | 1    | 0     | 1     | Out        | х     | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | I  | NoCh | ange |      | ignore     | no  |

| 1  | 1    | 0     | 1     | In         | х     | UC      | х       | UC      | UC      | UC      | UC    | 1  | UC  | 1   | 1  | 1    | 0    | 0    | ACK (back) | yes |

| Ν  | AK I | n/er  | rone  | ous Out    |       |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| 1  | 1    | 0     | 0     | Out        | х     | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | I  | NoCh | ange |      | ignore     | no  |

| 1  | 1    | 0     | 0     | In         | х     | UC      | х       | UC      | UC      | UC      | UC    | 1  | UC  | UC  | I  | NoCh | ange |      | NAK        | yes |

| ls | ochr | ono   | us e  | ndpoint (I | n)    |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

| 0  | 1    | 1     | 1     | Out        | х     | UC      | х       | UC      | UC      | UC      | UC    | UC | UC  | UC  | 1  | NoCh | ange |      | ignore     | no  |

| 0  | 1    | 1     | 1     | In         | х     | UC      | х       | UC      | UC      | UC      | UC    | 1  | UC  | UC  | 1  | NoCh | ange |      | ΤX         | yes |

|    |      |       |       |            |       |         |         |         |         |         |       |    |     |     |    |      |      |      |            |     |

# **Absolute Maximum Ratings**

| Storage temperature65 °C to +150 °C                                            |

|--------------------------------------------------------------------------------|

| Ambient temperature with power applied0 °C to +70 °C                           |

| Supply voltage on V <sub>CC</sub> relative to V <sub>SS</sub> –0.5 V to +7.0 V |

| DC input voltage –0.5 V to +V <sub>CC</sub> +0.5 V                             |

| DC voltage applied to outputs in High Z state –0.5 V to + $V_{CC}$ +0.5 V      |

| Maximum output current into Port 0,1,2,3 and DAC[1:0] Pins60 mA                |

| Maximum output current into DAC[7:2] Pins 10 mA                                |

| Power dissipation                                                              |

| Static discharge voltage> 2000V <sup>[3]</sup>                                 |

| Latch-up current> 200 mA                                                       |

## DC Characteristics Fosc = 6 MHz; operating temperature = 0 to 70 °C

|                                 | Parameter                                       | Min   | Max   | Unit            | Conditions                                 |

|---------------------------------|-------------------------------------------------|-------|-------|-----------------|--------------------------------------------|

| General                         |                                                 |       |       |                 | •                                          |

| V <sub>CC (1)</sub>             | Operating voltage                               | 4.0   | 5.5   | V               | Non USB activity <sup>[4]</sup>            |

| V <sub>CC (2)</sub>             | Operating voltage                               | 4.35  | 5.25  | V               | USB activity <sup>[5]</sup>                |

| CC1                             | V <sub>CC</sub> operating supply current        | -     | 40    | mA              | V <sub>CC</sub> = 5.5 V                    |

| CC2                             | V <sub>CC</sub> = 4.35 V                        | -     | 15    | mA              | -                                          |

| SB1                             | Supply current - suspend mode                   | -     | 30    | μΑ              | Oscillator off, D- > Voh min               |

| / <sub>PP</sub>                 | Programming voltage (disabled)                  | -0.4  | 0.4   | V               | -                                          |

| Г <sub>start</sub>              | Resonator start-up interval                     | -     | 256   | μs              | $V_{CC} = 5.0$ V, ceramic resonator        |

| int1                            | Internal timer #1 interrupt period              | 128   | 128   | μs              | -                                          |

| int2                            | Internal timer #2 interrupt period              | 1.024 | 1.024 | ms              | –                                          |

| watch                           | Watch dog timer period                          | 8.192 | 14.33 | ms              | -                                          |

| il                              | Input leakage current                           | _     | 1     | μΑ              | Any pin                                    |

| sm                              | Max I <sub>SS</sub> I/O sink current            | -     | 60    | mA              | Cumulative across all ports <sup>[6]</sup> |

| Power-Or                        | n Reset                                         | •     |       |                 | •                                          |

| VCCS                            | V <sub>CC</sub> reset slew                      | 0.001 | 200   | ms              | Linear ramp: 0 to 4.35 V <sup>[7, 8]</sup> |

| <b>USB</b> Inter                | face                                            |       |       |                 | •                                          |

| / <sub>oh</sub>                 | Static output HIGH                              | 2.8   | 3.6   | V               | 15 k ± 5% Ω to Gnd $^{[5]}$                |

| / <sub>ol</sub>                 | Static output LOW                               | _     | 0.3   | V               | -                                          |

| / <sub>di</sub>                 | Differential input sensitivity                  | 0.2   |       | V               | (D+)-(D-)                                  |

| V <sub>cm</sub>                 | Differential input common mode range            | 0.8   | 2.5   | V               | 9-1                                        |

| ∕ <sub>se</sub>                 | Single-ended receiver threshold                 | 0.8   | 2.0   | V               | -                                          |

| C <sub>in</sub>                 | Transceiver capacitance                         | _     | 20    | pF              | -                                          |

| lo                              | Hi-Z state data line leakage                    | -10   | 10    | μA              | 0 V < V <sub>in</sub> <3.3 V               |

| R <sub>pu</sub>                 | Bus pull-up resistance (V <sub>CC</sub> option) | 7.35K | 7.65  | kΩ              | 7.5 k $\Omega$ ± 2% to V <sub>CC</sub>     |

| ₹ <sub>pu</sub>                 | Bus pull-up resistance (Ext. 3.3 V option)      | 1.425 | 1.575 | kΩ              | 1.5 kΩ ± 5% to 3.0–3.6 V                   |

| ר <u>י</u> ש<br>ק <sub>pd</sub> | Bus pull-down resistance                        | 14.25 | 15.75 | kΩ              | 15 kΩ ± 5%                                 |

|                                 | Purpose I/O Interface                           |       |       |                 | -                                          |

| ۲ <sub>up</sub>                 | Pull-up resistance                              | 4.9 K | 9.1 K | Ohms            |                                            |

| V <sub>ith</sub>                | Input threshold voltage                         | 45%   | 65%   | V <sub>CC</sub> | All ports, LOW to HIGH edge                |

#### Notes

- Notes

Qualified with JEDEC EIA/JESD22-A114-B test method.

Functionality is guaranteed of the V<sub>CC (1)</sub> range, except USB transmitter and DACs.

USB transmitter functionality is guaranteed over the V<sub>CC (2)</sub> range, as well as DAC outputs.

Total current cumulative across all Port pins flowing to V<sub>SS</sub> is limited to minimize Ground-Drop noise effects.

Port 3 bit 7 controls whether the parts goes into suspend after a POR event or waits 128 ms to begin running.

POR will re-occur whenever V<sub>CC</sub> drops to approximately 2.5 V.

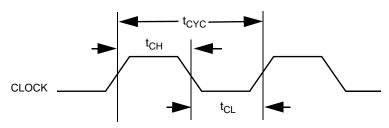

## Figure 8. Clock Timing

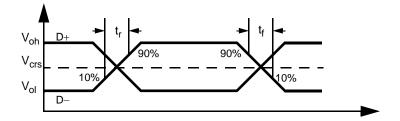

Figure 9. USB Data Signal Timing

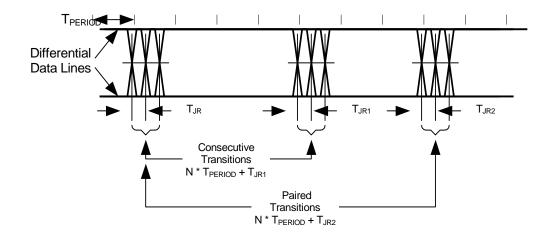

Figure 10. Receiver Jitter Tolerance

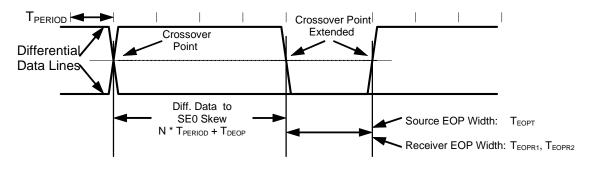

## Figure 11. Differential to EOP Transition Skew and EOP Width

# **Die Pad Locations**

## Table 29. Dle Pad Locations (in microns)

| Pad # | Pin Name        | Х       | Y       | Pad # | Pin Name        | X       | Y       |

|-------|-----------------|---------|---------|-------|-----------------|---------|---------|

| 1     | D+              | 1496.95 | 2995.00 | 48    | V <sub>CC</sub> | 1619.65 | 3023.60 |

| 2     | D-              | 467.40  | 2995.00 | 47    | V <sub>SS</sub> | 1719.65 | 3023.60 |

| 3     | Port3[7]        | 345.15  | 3023.60 | 46    | Port3[6]        | 1823.10 | 3023.60 |

| 4     | Port3[5]        | 242.15  | 3023.60 | 45    | Port3[4]        | 1926.10 | 3023.60 |

| 5     | Port3[3]        | 98.00   | 2661.25 | 44    | Port3[2]        | 2066.30 | 2657.35 |

| 6     | Port3[1]        | 98.00   | 2558.25 | 43    | Port3[0]        | 2066.30 | 2554.35 |

| 7     | Port2[7]        | 98.00   | 2455.25 | 42    | Port2[6]        | 2066.30 | 2451.35 |

| 8     | Port2[5]        | 98.00   | 2352.25 | 41    | Port2[4]        | 2066.30 | 2348.35 |

| 9     | Port2[3]        | 98.00   | 2249.25 | 40    | Port2[2]        | 2066.30 | 2245.35 |

| 10    | Port2[1]        | 98.00   | 2146.25 | 39    | Port2[0]        | 2066.30 | 2142.35 |

| 11    | Por1[7]         | 98.00   | 1134.25 | 38    | Port1[6]        | 2066.30 | 1130.35 |

| 12    | Por1[5]         | 98.00   | 1031.25 | 37    | Port1[4]        | 2066.30 | 1027.35 |

| 13    | Por1[3]         | 98.00   | 928.25  | 36    | Port1[2]        | 2066.30 | 924.35  |

| 14    | Por1[1]         | 98.00   | 825.25  | 35    | Port1[0]        | 2066.30 | 821.35  |

| 15    | DAC7            | 98.00   | 721.05  | 34    | DAC6            | 2066.30 | 719.55  |

| 16    | DAC5            | 98.00   | 618.05  | 33    | DAC4            | 2066.30 | 616.55  |

| 17    | Port0[7]        | 98.00   | 516.25  | 32    | Port0[6]        | 2066.30 | 512.35  |

| 18    | Port0[5]        | 98.00   | 413.25  | 31    | Port0[4]        | 2066.30 | 409.35  |

| 19    | Port0[3]        | 306.30  | 98.00   | 30    | Port0[2]        | 1858.00 | 98.00   |

| 20    | Port0[1]        | 442.15  | 98.00   | 29    | Port0[0]        | 1718.30 | 98.00   |

| 21    | DAC3            | 593.40  | 98.00   | 28    | DAC2            | 1618.50 | 98.00   |

| 22    | DAC1            | 696.40  | 98.00   | 27    | DAC0            | 1513.50 | 98.00   |

| 23    | V <sub>PP</sub> | 824.25  | 98.00   | 26    | XtalOut         | 1301.90 | 98.00   |

| 24    | V <sub>SS</sub> | 949.65  | 98.00   | 25    | Xtalln          | 1160.50 | 98.00   |

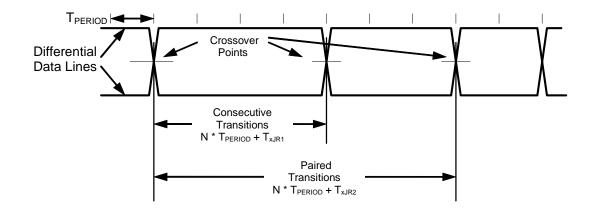

# **Package Diagrams**

51-85061 \*F