# E·XFL

# AMD Xilinx - XC7A100T-1FGG676C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 7925                                                          |

| Number of Logic Elements/Cells | 101440                                                        |

| Total RAM Bits                 | 4976640                                                       |

| Number of I/O                  | 300                                                           |

| Number of Gates                |                                                               |

| Voltage - Supply               | 0.95V ~ 1.05V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 676-BGA                                                       |

| Supplier Device Package        | 676-FBGA (27x27)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc7a100t-1fgg676c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 1: Absolute Maximum Ratings<sup>(1)</sup> (Cont'd)

| Symbol           | Description                                                    | Min | Max  | Units |

|------------------|----------------------------------------------------------------|-----|------|-------|

| Temperature      |                                                                |     |      |       |

| T <sub>STG</sub> | Storage temperature (ambient)                                  | -65 | 150  | °C    |

| т                | Maximum soldering temperature for Pb/Sn component bodies (6)   | -   | +220 | °C    |

| I SOL            | Maximum soldering temperature for Pb-free component bodies (6) | -   | +260 | °C    |

| Tj               | Maximum junction temperature <sup>(6)</sup>                    | 1   | +125 | °C    |

#### Notes:

- 2. The lower absolute voltage specification always applies.

- 3. For I/O operation, refer to UG471: 7 Series FPGAs SelectIO Resources User Guide.

- 4. The maximum limit applied to DC signals.

- 5. For maximum undershoot and overshoot AC specifications, see Table 4.

- 6. For soldering guidelines and thermal considerations, see UG475: 7 Series FPGA Packaging and Pinout Specification.

## Table 2: Recommended Operating Conditions<sup>(1)(2)</sup>

| Symbol                                 | Description                                                                                          |       | Тур  | Max                     | Units    |

|----------------------------------------|------------------------------------------------------------------------------------------------------|-------|------|-------------------------|----------|

| FPGA Logic                             | · · · · · ·                                                                                          |       |      |                         | <u>.</u> |

| M                                      | Internal supply voltage                                                                              | 0.95  | 1.00 | 1.05                    | V        |

| V <sub>CCINT</sub>                     | For -2L (0.9V) devices: internal supply voltage                                                      | 0.87  | 0.90 | 0.93                    | V        |

| V <sub>CCAUX</sub>                     | Auxiliary supply voltage                                                                             | 1.71  | 1.80 | 1.89                    | V        |

| V <sub>CCBRAM</sub>                    | Block RAM supply voltage                                                                             | 0.95  | 1.00 | 1.05                    | V        |

| V <sub>CCO</sub> <sup>(3)(4)</sup>     | Supply voltage for 3.3V HR I/O banks                                                                 | 1.14  | -    | 3.465                   | V        |

| V (5)                                  | I/O input voltage                                                                                    | -0.20 | -    | V <sub>CCO</sub> + 0.20 | V        |

| V <sub>IN</sub> <sup>(5)</sup>         | I/O input voltage for V <sub>REF</sub> and differential I/O standards                                |       | -    | 2.625                   | V        |

| I <sub>IN</sub> <sup>(6)</sup>         | Maximum current through any pin in a powered or unpowered bank when forward biasing the clamp diode. |       | -    | 10                      | mA       |

| V <sub>CCBATT</sub> <sup>(7)</sup>     | Battery voltage                                                                                      | 1.0   | -    | 1.89                    | V        |

| GTP Transceiv                          | ver                                                                                                  |       |      |                         | 1        |

| V <sub>MGTAVCC</sub> <sup>(8)(9)</sup> | Analog supply voltage for the GTP transmitter and receiver circuits                                  | 0.97  | 1.0  | 1.03                    | V        |

| V <sub>MGTAVTT</sub> <sup>(8)(9)</sup> | Analog supply voltage for the CTD transmitter and receiver termination                               |       | 1.2  | 1.23                    | V        |

| XADC                                   |                                                                                                      |       |      |                         |          |

| V <sub>CCADC</sub>                     | XADC supply relative to GNDADC                                                                       | 1.71  | 1.80 | 1.89                    | V        |

| V <sub>REFP</sub>                      | Externally supplied reference voltage                                                                | 1.20  | 1.25 | 1.30                    | V        |

<sup>1.</sup> Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

## Table 3: DC Characteristics Over Recommended Operating Conditions (Cont'd)

| Symbol | Description                         | Min | Typ <mark>(1)</mark> | Max | Units |

|--------|-------------------------------------|-----|----------------------|-----|-------|

| n      | Temperature diode ideality factor   | -   | 1.010                | -   | -     |

| r      | Temperature diode series resistance | _   | 2                    | _   | Ω     |

#### Notes:

1. Typical values are specified at nominal voltage, 25°C.

2. This measurement represents the die capacitance at the pad, not including the package.

3. Maximum value specified for worst case process at 25°C.

4. Termination resistance to a  $V_{CCO}/2$  level.

## Table 4: VIN Maximum Allowed AC Voltage Overshoot and Undershoot for 3.3V HR I/O Banks<sup>(1)</sup>

| AC Voltage Overshoot    | % of UI @-40°C to 100°C | AC Voltage Undershoot | % of UI @-40°C to 100°C |

|-------------------------|-------------------------|-----------------------|-------------------------|

| V <sub>CCO</sub> + 0.40 | 100                     | -0.40                 | 100                     |

| V <sub>CCO</sub> + 0.45 | 100                     | -0.45                 | 61.7                    |

| V <sub>CCO</sub> + 0.50 | 100                     | -0.50                 | 25.8                    |

| V <sub>CCO</sub> + 0.55 | 100                     | -0.55                 | 11.0                    |

| V <sub>CCO</sub> + 0.60 | 46.6                    | -0.60                 | 4.77                    |

| V <sub>CCO</sub> + 0.65 | 21.2                    | -0.65                 | 2.10                    |

| V <sub>CCO</sub> + 0.70 | 9.75                    | -0.70                 | 0.94                    |

| V <sub>CCO</sub> + 0.75 | 4.55                    | -0.75                 | 0.43                    |

| V <sub>CCO</sub> + 0.80 | 2.15                    | -0.80                 | 0.20                    |

| V <sub>CCO</sub> + 0.85 | 1.02                    | -0.85                 | 0.09                    |

| V <sub>CCO</sub> + 0.90 | 0.49                    | -0.90                 | 0.04                    |

| V <sub>CCO</sub> + 0.95 | 0.24                    | -0.95                 | 0.02                    |

#### Notes:

1. A total of 200 mA per bank should not be exceeded.

## Table 5: Typical Quiescent Supply Current

| Symbol                                                     | Description                                  | Device   | 1.0V |        |     | 0.9V | Units |

|------------------------------------------------------------|----------------------------------------------|----------|------|--------|-----|------|-------|

|                                                            |                                              |          | -3   | -2/-2L | -1  | -2L  |       |

| ICCINTQ                                                    | Quiescent V <sub>CCINT</sub> supply current  | XC7A100T | 155  | 155    | 155 | 108  | mA    |

|                                                            |                                              | XC7A200T | 328  | 328    | 328 | 232  | mA    |

| I <sub>CCOQ</sub> Quiescent V <sub>CCO</sub> supply curren | Quiescent V <sub>CCO</sub> supply current    | XC7A100T | 4    | 4      | 4   | 4    | mA    |

|                                                            |                                              | XC7A200T | 5    | 5      | 5   | 5    | mA    |

| ICCAUXQ                                                    | Quiescent V <sub>CCAUX</sub> supply current  | XC7A100T | 36   | 36     | 36  | 36   | mA    |

|                                                            |                                              | XC7A200T | 73   | 73     | 73  | 73   | mA    |

| ICCBRAMQ                                                   | Quiescent V <sub>CCBRAM</sub> supply current | XC7A100T | 4    | 4      | 4   | 4    | mA    |

|                                                            |                                              | XC7A200T | 11   | 11     | 11  | 11   | mA    |

#### Notes:

1. Typical values are specified at nominal voltage, 85°C junction temperature (T<sub>j</sub>) with single-ended SelectIO resources.

2. Typical values are for blank configured devices with no output current loads, no active input pull-up resistors, all I/O pins are 3-state and floating.

3. Use the Xilinx Power Estimator (XPE) spreadsheet tool (download at <a href="http://www.xilinx.com/power">http://www.xilinx.com/power</a>) to calculate static power consumption for conditions other than those specified.

# Power-On/Off Power Supply Sequencing

The recommended power-on sequence is V<sub>CCINT</sub>, V<sub>CCBRAM</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> to achieve minimum current draw and ensure that the I/Os are 3-stated at power-on. The recommended power-off sequence is the reverse of the power-on sequence. If V<sub>CCINT</sub> and V<sub>CCBRAM</sub> have the same recommended voltage levels then both can be powered by the same supply and ramped simultaneously. If V<sub>CCAUX</sub> and V<sub>CCO</sub> have the same recommended voltage levels then both can be powered by the same powered by the same supply and ramped simultaneously.

For V<sub>CCO</sub> voltages of 3.3V in HR I/O banks and configuration bank 0:

- The voltage difference between V<sub>CCO</sub> and V<sub>CCAUX</sub> must not exceed 2.625V for longer than T<sub>VCCO2VCCAUX</sub> for each power-on/off cycle to maintain device reliability levels.

- The T<sub>VCCO2VCCAUX</sub> time can be allocated in any percentage between the power-on and power-off ramps.

The recommended power-on sequence to achieve minimum current draw for the GTP transceivers is  $V_{CCINT}$ ,  $V_{MGTAVCC}$ ,  $V_{MGTAVCC}$ ,  $V_{CCINT}$ ,  $V_{MGTAVCT}$ . There is no recommended sequencing for  $V_{MGTVCCAUX}$ . Both  $V_{MGTAVCC}$  and  $V_{CCINT}$  can be ramped simultaneously. The recommended power-off sequence is the reverse of the power-on sequence to achieve minimum current draw.

If these recommended sequences are not met, current drawn from V<sub>MGTAVTT</sub> can be higher than specifications during power-up and power-down.

- When V<sub>MGTAVTT</sub> is powered before V<sub>MGTAVCC</sub> and V<sub>MGTAVTT</sub> V<sub>MGTAVCC</sub> > 150 mV and V<sub>MGTAVCC</sub> < 0.7V, the V<sub>MGTAVTT</sub> current draw can increase by 460 mA per transceiver during V<sub>MGTAVCC</sub> ramp up. The duration of the current draw can be up to 0.3 x T<sub>MGTAVCC</sub> (ramp time from GND to 90% of V<sub>MGTAVCC</sub>). The reverse is true for power-down.

- When V<sub>MGTAVTT</sub> is powered before V<sub>CCINT</sub> and V<sub>MGTAVTT</sub> V<sub>CCINT</sub> > 150 mV and V<sub>CCINT</sub> < 0.7V, the V<sub>MGTAVTT</sub> current draw can increase by 50 mA per transceiver during V<sub>CCINT</sub> ramp up. The duration of the current draw can be up to 0.3 x T<sub>VCCINT</sub> (ramp time from GND to 90% of V<sub>CCINT</sub>). The reverse is true for power-down.

# **DC Input and Output Levels**

Values for V<sub>IL</sub> and V<sub>IH</sub> are recommended input voltages. Values for I<sub>OL</sub> and I<sub>OH</sub> are guaranteed over the recommended operating conditions at the V<sub>OL</sub> and V<sub>OH</sub> test points. Only selected standards are tested. These are chosen to ensure that all standards meet their specifications. The selected standards are tested at a minimum V<sub>CCO</sub> with the respective V<sub>OL</sub> and V<sub>OH</sub> voltage levels shown. Other standards are sample tested.

| I/O Standard | V <sub>IL</sub> |                          | V <sub>I</sub>           | V <sub>IH</sub>          |                             | V <sub>OH</sub>             | I <sub>OL</sub> | I <sub>OH</sub> |

|--------------|-----------------|--------------------------|--------------------------|--------------------------|-----------------------------|-----------------------------|-----------------|-----------------|

| i/O Standard | V, Min          | V, Max                   | V, Min                   | V, Max                   | V, Max                      | V, Min                      | mA, Max         | mA, Min         |

| HSTL_I       | -0.300          | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> – 0.400    | 8.00            | -8.00           |

| HSTL_I_18    | -0.300          | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> – 0.400    | 8.00            | -8.00           |

| HSTL_II      | -0.300          | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> – 0.400    | 16.00           | -16.00          |

| HSTL_II_18   | -0.300          | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> – 0.400    | 16.00           | -16.00          |

| HSUL_12      | -0.300          | V <sub>REF</sub> – 0.130 | V <sub>REF</sub> + 0.130 | V <sub>CCO</sub> + 0.300 | 20% V <sub>CCO</sub>        | 80% V <sub>CCO</sub>        | 0.10            | -0.10           |

| LVCMOS12     | -0.300          | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> – 0.400    | Note 3          | Note 3          |

| LVCMOS15     | -0.300          | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 25% V <sub>CCO</sub>        | 75% V <sub>CCO</sub>        | Note 4          | Note 4          |

| LVCMOS18     | -0.300          | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 0.450                       | V <sub>CCO</sub> – 0.450    | Note 5          | Note 5          |

| LVCMOS25     | -0.300          | 0.7                      | 1.700                    | V <sub>CCO</sub> + 0.300 | 0.400                       | $V_{CCO} - 0.400$           | Note 4          | Note 4          |

| LVCMOS33     | -0.300          | 0.8                      | 2.000                    | 3.450                    | 0.400                       | $V_{CCO} - 0.400$           | Note 4          | Note 4          |

| LVTTL        | -0.300          | 0.8                      | 2.000                    | 3.450                    | 0.400                       | 2.400                       | Note 5          | Note 5          |

| MOBILE_DDR   | -0.300          | 20% V <sub>CCO</sub>     | 80% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>        | 0.10            | -0.10           |

| PCI33_3      | -0.500          | 30% V <sub>CCO</sub>     | 50% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.500 | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>        | 1.50            | -0.50           |

| SSTL135      | -0.300          | V <sub>REF</sub> – 0.090 | V <sub>REF</sub> + 0.090 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2-0.150   | V <sub>CCO</sub> /2 + 0.150 | 13.00           | -13.00          |

| SSTL135_R    | -0.300          | V <sub>REF</sub> - 0.090 | V <sub>REF</sub> + 0.090 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 - 0.150 | V <sub>CCO</sub> /2 + 0.150 | 8.90            | -8.90           |

| SSTL15       | -0.300          | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 - 0.175 | V <sub>CCO</sub> /2 + 0.175 | 13.00           | -13.00          |

| SSTL15_R     | -0.300          | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2-0.175   | V <sub>CCO</sub> /2 + 0.175 | 8.90            | -8.90           |

| SSTL18_I     | -0.300          | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2-0.470   | $V_{CCO}/2 + 0.470$         | 8.00            | -8.00           |

| SSTL18_II    | -0.300          | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCO</sub> + 0.300 | $V_{CCO}/2 - 0.600$         | $V_{CCO}/2 + 0.600$         | 13.40           | -13.40          |

| Table 8 <sup>.</sup> | SelectIO D | C Input and | Output | Levels <sup>(1)(2)</sup> |

|----------------------|------------|-------------|--------|--------------------------|

|                      |            | ο πιραι απα | Juipui |                          |

Notes:

1. Tested according to relevant specifications.

- 2. 3.3V and 2.5V standards are only supported in 3.3V I/O banks.

- 3. Supported drive strengths of 4, 8, or 12 mA in HR I/O banks.

- 4. Supported drive strengths of 4, 8, 12, or 16 mA in HR I/O banks.

5. Supported drive strengths of 4, 8, 12, 16, or 24 mA in HR I/O banks.

6. For detailed interface specific DC voltage levels, see UG471: 7 Series FPGAs SelectIO Resources User Guide.

# LVDS DC Specifications (LVDS\_25)

See <u>UG471</u>: 7 Series FPGAs SelectIO Resources User Guide for more information on the LVDS\_25 standard in the HR I/O banks.

| Table | 11: | LVDS_ | _25 | DC | Specifications |

|-------|-----|-------|-----|----|----------------|

|-------|-----|-------|-----|----|----------------|

| Symbol             | DC Parameter                                                                                                | Conditions                                               | Min   | Тур   | Max   | Units |

|--------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CCO</sub>   | Supply Voltage                                                                                              |                                                          | 2.375 | 2.500 | 2.625 | V     |

| V <sub>OH</sub>    | Output High Voltage for Q and $\overline{Q}$                                                                | $R_T = 100 \ \Omega$ across Q and $\overline{Q}$ signals | -     | -     | 1.675 | V     |

| V <sub>OL</sub>    | Output Low Voltage for Q and $\overline{Q}$                                                                 | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals   | 0.700 | -     | -     | V     |

| V <sub>ODIFF</sub> | Differential Output Voltage $(Q - \overline{Q})$ ,<br>Q = High $(\overline{Q} - Q)$ , $\overline{Q}$ = High | $R_T = 100 \ \Omega$ across Q and $\overline{Q}$ signals | 247   | 350   | 600   | mV    |

| V <sub>OCM</sub>   | Output Common-Mode Voltage $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals                           |                                                          | 1.000 | 1.250 | 1.425 | V     |

| V <sub>IDIFF</sub> | Differential Input Voltage $(Q - \overline{Q}), Q = High (\overline{Q} - Q), \overline{Q} = High$           |                                                          |       | 350   | 600   | mV    |

| V <sub>ICM</sub>   | Input Common-Mode Voltage                                                                                   |                                                          |       | 1.200 | 1.425 | V     |

# **AC Switching Characteristics**

All values represented in this data sheet are based on the speed specifications in v1.07 from the 14.4/2012.4 device pack for ISE® Design Suite14.4 and Vivado® Design Suite 2012.4 for the -3, -2, -2L (1.0V), and -1 speed grades and v1.05 from the 14.4/2012.4 device pack for the -2L (0.9V) speed grade.

Switching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows:

## Advance Product Specification

These specifications are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

## Preliminary Product Specification

These specifications are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data.

## Production Product Specification

These specifications are released once enough production silicon of a particular device family member has been characterized to provide full correlation between specifications and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

# **Testing of AC Switching Characteristics**

Internal timing parameters are derived from measuring internal test patterns. All AC switching characteristics are representative of worst-case supply voltage and junction temperature conditions.

For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer and back-annotate to the simulation net list. Unless otherwise noted, values apply to all Artix-7 FPGAs.

# **Speed Grade Designations**

Since individual family members are produced at different times, the migration from one category to another depends completely on the status of the fabrication process for each device. Table 12 correlates the current status of each Artix-7 device on a per speed grade basis.

## Table 12: Artix-7 Device Speed Grade Designations

| Device   | Speed Grade Designations |             |                        |  |  |  |  |

|----------|--------------------------|-------------|------------------------|--|--|--|--|

| Device   | Advance                  | Preliminary | Production             |  |  |  |  |

| XC7A100T | -2L (0.9V)               |             | -3, -2, -2L (1.0V), -1 |  |  |  |  |

| XC7A200T | -2L (0.9V)               |             | -3, -2, -2L (1.0V), -1 |  |  |  |  |

# **Production Silicon and ISE Software Status**

In some cases, a particular family member (and speed grade) is released to production before a speed specification is released with the correct label (Advance, Preliminary, Production). Any labeling discrepancies are corrected in subsequent speed specification releases.

Table 13 lists the production released Artix-7 device, speed grade, and the minimum corresponding supported speed specification version and ISE software revisions. The ISE software and speed specifications listed are the minimum releases required for production. All subsequent releases of software and speed specifications are valid.

## Table 13: Artix-7 Device Production Software and Speed Specification Release

|          | Speed Grade        |                                                                   |    |     |  |  |

|----------|--------------------|-------------------------------------------------------------------|----|-----|--|--|

| Device   |                    | 0.9V                                                              |    |     |  |  |

|          | -3                 | -2/-2L                                                            | -1 | -2L |  |  |

| XC7A100T | ISE 14.4 and Vivad | ISE 14.4 and Vivado 2012.4 with the 14.4/2012.4 device pack v1.07 |    |     |  |  |

| XC7A200T | ISE 14.4 and Vivad | ISE 14.4 and Vivado 2012.4 with the 14.4/2012.4 device pack v1.07 |    |     |  |  |

Notes:

1. Blank entries indicate a device and/or speed grade in advance or preliminary status.

www.xilinx.com

# **Performance Characteristics**

This section provides the performance characteristics of some common functions and designs implemented in Artix-7 devices. The numbers reported here are worst-case values; they have all been fully characterized. These values are subject to the same guidelines as the AC Switching Characteristics, page 9.

## Table 14: Networking Applications Interface Performances

| Description                                                |      | 1.0V   | 0.9V | Units |      |

|------------------------------------------------------------|------|--------|------|-------|------|

|                                                            | -3   | -2/-2L | -1   | -2L   |      |

| SDR LVDS transmitter (using OSERDES; DATA_WIDTH = 4 to 8)  | 680  | 680    | 600  | 600   | Mb/s |

| DDR LVDS transmitter (using OSERDES; DATA_WIDTH = 4 to 14) | 1250 | 1250   | 950  | 950   | Mb/s |

| SDR LVDS receiver (SFI-4.1) <sup>(1)</sup>                 | 680  | 680    | 600  | 600   | Mb/s |

| DDR LVDS receiver (SPI-4.2) <sup>(1)</sup>                 | 1250 | 1250   | 950  | 950   | Mb/s |

#### Notes:

1. LVDS receivers are typically bounded with certain applications where specific dynamic phase-alignment (DPA) algorithms dominate deterministic performance.

## Table 15: Maximum Physical Interface (PHY) Rate for Memory Interfaces<sup>(1)(2)</sup>

|                        |      | Speed Grade |          |          |      |  |  |

|------------------------|------|-------------|----------|----------|------|--|--|

| Memory Standard        |      | 1.0V        |          |          |      |  |  |

|                        | -3   | -2/-2L      | -1       | -2L      |      |  |  |

| 4:1 Memory Controllers |      |             |          |          |      |  |  |

| DDR3                   | 1066 | 800         | 800      | 800      | Mb/s |  |  |

| DDR3L                  | 800  | 800         | 667      | 667      | Mb/s |  |  |

| DDR2                   | 800  | 800         | 667      | 667      | Mb/s |  |  |

| LPDDR2                 | 667  | 667         | 533      | 533      | Mb/s |  |  |

| 2:1 Memory Controllers |      | •           | <u>.</u> | <u>.</u> |      |  |  |

| DDR3                   | 800  | 700         | 620      | 620      | Mb/s |  |  |

| DDR3L                  | 800  | 700         | 620      | 620      | Mb/s |  |  |

| DDR2                   | 800  | 700         | 620      | 620      | Mb/s |  |  |

Notes:

1. V<sub>REF</sub> tracking is required. For more information, see UG586, 7 Series FPGAs Memory Interface Solutions User Guide.

2. When using the internal  $V_{\text{REF}}$  the maximum data rate is 800 Mb/s (400 MHz).

# Input/Output Logic Switching Characteristics

Table 18: ILOGIC Switching Characteristics

|                                          |                                                              |           | Speed     | Grade     |            |         |

|------------------------------------------|--------------------------------------------------------------|-----------|-----------|-----------|------------|---------|

| Symbol                                   | Description                                                  |           | 1.0V      |           | 0.9V       | Units   |

|                                          |                                                              | -3        | -2/-2L    | -1        | -2L        |         |

| Setup/Hold                               |                                                              |           |           | ·         |            |         |

| T <sub>ICE1CK</sub> /T <sub>ICKCE1</sub> | CE1 pin setup/hold with respect to CLK                       | 0.48/0.02 | 0.54/0.02 | 0.76/0.02 | 0.40/0.07  | ns      |

| T <sub>ISRCK</sub> /T <sub>ICKSR</sub>   | SR pin setup/hold with respect to CLK                        | 0.60/0.01 | 0.70/0.01 | 1.13/0.01 | 0.88/-0.35 | ns      |

| T <sub>IDOCK</sub> /T <sub>IOCKD</sub>   | D pin setup/hold with respect to CLK without Delay           | 0.01/0.27 | 0.01/0.29 | 0.01/0.33 | 0.01/0.33  | ns      |

| TIDOCKD/TIOCKDD                          | DDLY pin setup/hold with respect to CLK (using IDELAY)       | 0.02/0.27 | 0.02/0.29 | 0.02/0.33 | 0.01/0.33  | ns      |

| Combinatorial                            | -                                                            | 1         | 1         |           |            | I       |

| T <sub>IDI</sub>                         | D pin to O pin propagation delay, no Delay                   | 0.11      | 0.11      | 0.13      | 0.14       | ns      |

| T <sub>IDID</sub>                        | DDLY pin to O pin propagation delay (using IDELAY)           | 0.11      | 0.12      | 0.14      | 0.15       | ns      |

| Sequential Delays                        | S                                                            |           | ľ         |           |            |         |

| T <sub>IDLO</sub>                        | D pin to Q1 pin using flip-flop as a latch without Delay     | 0.41      | 0.44      | 0.51      | 0.54       | ns      |

| T <sub>IDLOD</sub>                       | DDLY pin to Q1 pin using flip-flop as a latch (using IDELAY) | 0.41      | 0.44      | 0.51      | 0.55       | ns      |

| T <sub>ICKQ</sub>                        | CLK to Q outputs                                             | 0.53      | 0.57      | 0.66      | 0.71       | ns      |

| T <sub>RQ_ILOGIC</sub>                   | SR pin to OQ/TQ out                                          | 0.96      | 1.08      | 1.32      | 1.32       | ns      |

| T <sub>GSRQ_ILOGIC</sub>                 | Global set/reset to Q outputs                                | 7.60      | 7.60      | 10.51     | 11.39      | ns      |

| Set/Reset                                |                                                              |           |           |           |            |         |

| T <sub>RPW_ILOGIC</sub>                  | Minimum pulse width, SR inputs                               | 0.61      | 0.72      | 0.72      | 0.68       | ns, Min |

# Table 19: OLOGIC Switching Characteristics

|                                          |                                           |            | Speed      | Grade      |            |         |

|------------------------------------------|-------------------------------------------|------------|------------|------------|------------|---------|

| Symbol                                   | Description                               |            | 1.0V       |            | 0.9V       | Units   |

|                                          |                                           | -3         | -2/-2L     | -1         | -2L        |         |

| Setup/Hold                               | ·                                         |            |            |            |            |         |

| T <sub>ODCK</sub> /T <sub>OCKD</sub>     | D1/D2 pins setup/hold with respect to CLK | 0.67/-0.11 | 0.71/-0.11 | 0.84/0.11  | 0.60/0.18  | ns      |

| T <sub>OOCECK</sub> /T <sub>OCKOCE</sub> | OCE pin setup/hold with respect to CLK    | 0.32/0.58  | 0.34/0.58  | 0.51/0.58  | 0.21/-0.10 | ns      |

| T <sub>OSRCK</sub> /T <sub>OCKSR</sub>   | SR pin setup/hold with respect to CLK     | 0.37/0.21  | 0.44/0.21  | 0.80/0.21  | 0.62/-0.25 | ns      |

| Т <sub>отск</sub> /Т <sub>оскт</sub>     | T1/T2 pins setup/hold with respect to CLK | 0.69/0.14  | 0.73/-0.14 | 0.89/-0.14 | 0.60/-0.18 | ns      |

| T <sub>OTCECK</sub> /T <sub>OCKTCE</sub> | TCE pin setup/hold with respect to CLK    | 0.32/0.01  | 0.34/0.01  | 0.51/0.01  | 0.22/-0.10 | ns      |

| Combinatorial                            |                                           |            |            |            |            |         |

| T <sub>ODQ</sub>                         | D1 to OQ out or T1 to TQ out              | 0.83       | 0.96       | 1.16       | 1.36       | ns      |

| Sequential Delays                        |                                           | •          | •          | •          | •          | •       |

| Т <sub>ОСКQ</sub>                        | CLK to OQ/TQ out                          | 0.47       | 0.49       | 0.56       | 0.63       | ns      |

| T <sub>RQ_OLOGIC</sub>                   | SR pin to OQ/TQ out                       | 0.72       | 0.80       | 0.95       | 1.12       | ns      |

| T <sub>GSRQ_OLOGIC</sub>                 | Global set/reset to Q outputs             | 7.60       | 7.60       | 10.51      | 11.39      | ns      |

| Set/Reset                                |                                           |            |            |            |            |         |

| T <sub>RPW_OLOGIC</sub>                  | Minimum pulse width, SR inputs            | 0.64       | 0.74       | 0.74       | 0.68       | ns, Min |

www.xilinx.com

# Input Serializer/Deserializer Switching Characteristics

# Table 20: ISERDES Switching Characteristics

|                                                                |                                                                                | Speed Grade |            |            |            |       |

|----------------------------------------------------------------|--------------------------------------------------------------------------------|-------------|------------|------------|------------|-------|

| Symbol                                                         | Description                                                                    |             | 1.0V       |            | 0.9V       | Units |

|                                                                |                                                                                | -3          | -2/-2L     | -1         | -2L        |       |

| Setup/Hold for Control Lines                                   |                                                                                |             |            |            |            |       |

| TISCCK_BITSLIP/ TISCKC_BITSLIP                                 | BITSLIP pin setup/hold with respect to CLKDIV                                  | 0.01/0.14   | 0.02/0.15  | 0.02/0.17  | 0.02/0.21  | ns    |

| T <sub>ISCCK_CE</sub> / T <sub>ISCKC_CE</sub> <sup>(2)</sup>   | CE pin setup/hold with respect to CLK (for CE1)                                | 0.45/-0.01  | 0.50/-0.01 | 0.72/-0.01 | 0.35/-0.11 | ns    |

| T <sub>ISCCK_CE2</sub> / T <sub>ISCKC_CE2</sub> <sup>(2)</sup> | CE pin setup/hold with respect to CLKDIV (for CE2)                             | -0.10/0.33  | -0.10/0.36 | -0.10/0.40 | -0.17/0.40 | ns    |

| Setup/Hold for Data Lines                                      |                                                                                |             |            |            |            |       |

| T <sub>ISDCK_D</sub> /T <sub>ISCKD_D</sub>                     | D pin setup/hold with respect to CLK                                           | -0.02/0.12  | -0.02/0.14 | -0.02/0.17 | -0.04/0.19 | ns    |

| TISDCK_DDLY /TISCKD_DDLY                                       | DDLY pin setup/hold with respect to CLK (using IDELAY) <sup>(1)</sup>          | -0.02/0.12  | -0.02/0.14 | -0.02/0.17 | -0.03/0.19 | ns    |

| TISDCK_D_DDR /TISCKD_D_DDR                                     | D pin setup/hold with respect to CLK at DDR mode                               | -0.02/0.12  | -0.02/0.14 | -0.02/0.17 | -0.04/0.19 | ns    |

| TISDCK_DDLY_DDR/<br>TISCKD_DDLY_DDR                            | D pin setup/hold with respect to CLK at DDR mode (using IDELAY) <sup>(1)</sup> | 0.12/0.12   | 0.14/0.14  | 0.17/0.17  | 0.19/0.19  | ns    |

| Sequential Delays                                              | •                                                                              | - <u>!</u>  |            |            |            | •     |

| T <sub>ISCKO_Q</sub>                                           | CLKDIV to out at Q pin                                                         | 0.53        | 0.54       | 0.66       | 0.67       | ns    |

| Propagation Delays                                             | ·                                                                              |             |            |            |            |       |

| T <sub>ISDO_DO</sub>                                           | D input to DO output pin                                                       | 0.11        | 0.11       | 0.13       | 0.14       | ns    |

## Notes:

1. Recorded at 0 tap value.

2. T<sub>ISCCK\_CE2</sub> and T<sub>ISCKC\_CE2</sub> are reported as T<sub>ISCCK\_CE</sub>/T<sub>ISCKC\_CE</sub> in TRACE report.

# **Output Serializer/Deserializer Switching Characteristics**

# Table 21: OSERDES Switching Characteristics

|                                                             |                                               |            | Speed      | Grade      |            |       |

|-------------------------------------------------------------|-----------------------------------------------|------------|------------|------------|------------|-------|

| Symbol                                                      | Description                                   |            | 1.0V       |            | 0.9V       | Units |

|                                                             | -                                             | -3         | -2/-2L     | -1         | -2L        |       |

| Setup/Hold                                                  | ·                                             |            |            |            |            |       |

| T <sub>OSDCK_D</sub> /T <sub>OSCKD_D</sub>                  | D input setup/hold with respect to CLKDIV     | 0.42/0.03  | 0.45/0.03  | 0.63/0.03  | 0.44/-0.25 | ns    |

| T <sub>OSDCK_T</sub> /T <sub>OSCKD_T</sub> <sup>(1)</sup>   | T input setup/hold with respect to CLK        | 0.69/0.13  | 0.73/-0.13 | 0.88/-0.13 | 0.60/-0.25 | ns    |

| T <sub>OSDCK_T2</sub> /T <sub>OSCKD_T2</sub> <sup>(1)</sup> | T input setup/hold with respect to CLKDIV     | 0.31/-0.13 | 0.34/-0.13 | 0.39/-0.13 | 0.46/-0.25 | ns    |

| T <sub>OSCCK_OCE</sub> /T <sub>OSCKC_OCE</sub>              | OCE input setup/hold with respect to CLK      | 0.32/0.58  | 0.34/0.58  | 0.51/0.58  | 0.21/-0.15 | ns    |

| T <sub>OSCCK_S</sub>                                        | SR (reset) input setup with respect to CLKDIV | 0.47       | 0.52       | 0.85       | 0.70       | ns    |

| T <sub>OSCCK_TCE</sub> /T <sub>OSCKC_TCE</sub>              | TCE input setup/hold with respect to CLK      | 0.32/0.01  | 0.34/0.01  | 0.51/0.01  | 0.22/-0.15 | ns    |

| Sequential Delays                                           |                                               |            |            |            |            |       |

| T <sub>OSCKO_OQ</sub>                                       | Clock to out from CLK to OQ                   | 0.40       | 0.42       | 0.48       | 0.54       | ns    |

| Т <sub>ОSCKO_TQ</sub>                                       | Clock to out from CLK to TQ                   | 0.47       | 0.49       | 0.56       | 0.63       | ns    |

| Combinatorial                                               |                                               |            | 1          |            |            |       |

| T <sub>OSDO_TTQ</sub>                                       | T input to TQ Out                             | 0.83       | 0.92       | 1.11       | 1.18       | ns    |

Notes:

1.  $T_{OSDCK_{T2}}$  and  $T_{OSCKD_{T2}}$  are reported as  $T_{OSDCK_{T}}/T_{OSCKD_{T}}$  in TRACE report.

# Input/Output Delay Switching Characteristics

# Table 22: Input/Output Delay Switching Characteristics

|                             |                                                                                                       |           | Speed     | Grade                  |           |               |

|-----------------------------|-------------------------------------------------------------------------------------------------------|-----------|-----------|------------------------|-----------|---------------|

| Symbol                      | Description                                                                                           |           | 1.0V      |                        | 0.9V      | Units         |

|                             |                                                                                                       | -3        | -2/-2L    | -1                     | -2L       |               |

| IDELAYCTRL                  |                                                                                                       |           |           |                        |           |               |

| T <sub>DLYCCO_RDY</sub>     | Reset to ready for IDELAYCTRL                                                                         | 3.67      | 3.67      | 3.67                   | 3.22      | μs            |

| F <sub>IDELAYCTRL_REF</sub> | Attribute REFCLK frequency = 200.00 <sup>(1)</sup>                                                    | 200.00    | 200.00    | 200.00                 | 200.00    | MHz           |

|                             | Attribute REFCLK frequency = 300.00 <sup>(1)</sup>                                                    | 300.00    | 300.00    | N/A                    | N/A       | MHz           |

| IDELAYCTRL_REF_PRECISION    | REFCLK precision                                                                                      | ±10       | ±10       | ±10                    | ±10       | MHz           |

| T <sub>IDELAYCTRL_RPW</sub> | Minimum Reset pulse width                                                                             | 59.28     | 59.28     | 59.28                  | 52.00     | ns            |

| IDELAY                      | 1                                                                                                     | 1         | I         |                        | I         |               |

| TIDELAYRESOLUTION           | IDELAY chain delay resolution                                                                         |           | 1/(32 x 2 | 2 x F <sub>REF</sub> ) |           | ps            |

|                             | Pattern dependent period jitter in delay chain for clock pattern. <sup>(2)</sup>                      | 0         | 0         | 0                      | 0         | ps<br>per tap |

| T <sub>IDELAYPAT_JIT</sub>  | Pattern dependent period jitter in delay<br>chain for random data pattern<br>(PRBS 23) <sup>(3)</sup> | ±5        | ±5        | ±5                     | ±5        | ps<br>per tap |

|                             | Pattern dependent period jitter in delay<br>chain for random data pattern<br>(PRBS 23) <sup>(4)</sup> | ±9        | ±9        | ±9                     | ±9        | ps<br>per tap |

| T <sub>IDELAY_CLK_MAX</sub> | Maximum frequency of CLK input to IDELAY                                                              | 680.00    | 680.00    | 600.00                 | 520.00    | MHz           |

| TIDCCK_CE / TIDCKC_CE       | CE pin setup/hold with respect to C for IDELAY                                                        | 0.12/0.11 | 0.16/0.13 | 0.21/0.16              | 0.14/0.16 | ns            |

| TIDCCK_INC/ TIDCKC_INC      | INC pin setup/hold with respect to C for IDELAY                                                       | 0.12/0.16 | 0.14/0.18 | 0.16/0.22              | 0.10/0.23 | ns            |

| TIDCCK_RST / TIDCKC_RST     | RST pin setup/hold with respect to C for IDELAY                                                       | 0.15/0.09 | 0.16/0.11 | 0.18/0.14              | 0.22/0.19 | ns            |

| T <sub>IDDO_IDATAIN</sub>   | Propagation delay through IDELAY                                                                      | Note 5    | Note 5    | Note 5                 | Note 5    | ps            |

Notes:

- 1. Average Tap Delay at 200 MHz = 78 ps, at 300 MHz = 52 ps.

- 2. When HIGH\_PERFORMANCE mode is set to TRUE or FALSE.

- 3. When HIGH\_PERFORMANCE mode is set to TRUE.

- 4. When HIGH\_PERFORMANCE mode is set to FALSE.

- 5. Delay depends on IDELAY tap setting. See TRACE report for actual values.

# CLB Distributed RAM Switching Characteristics (SLICEM Only)

# Table 25: CLB Distributed RAM Switching Characteristics

|                                                    |                                                            |           | Speed     | Grade     |           |         |

|----------------------------------------------------|------------------------------------------------------------|-----------|-----------|-----------|-----------|---------|

| Symbol                                             | Description                                                |           | 1.0V      |           | 0.9V      | Units   |

|                                                    |                                                            | -3        | -2/-2L    | -1        | -2L       |         |

| Sequential Delays                                  |                                                            |           |           |           |           |         |

| Т <sub>SHCKO</sub>                                 | Clock to A – B outputs                                     | 0.98      | 1.09      | 1.32      | 1.54      | ns, Max |

| T <sub>SHCKO_1</sub>                               | Clock to AMUX – BMUX outputs                               | 1.37      | 1.53      | 1.86      | 2.18      | ns, Max |

| Setup and Hold Time                                | s Before/After Clock CLK                                   |           |           |           |           |         |

| T <sub>DS_LRAM</sub> /T <sub>DH_LRAM</sub>         | A – D inputs to CLK                                        | 0.54/0.28 | 0.60/0.30 | 0.72/0.35 | 0.96/0.40 | ns, Min |

| T <sub>AS_LRAM</sub> /T <sub>AH_LRAM</sub>         | Address An inputs to clock                                 | 0.27/0.55 | 0.30/0.60 | 0.37/0.70 | 0.43/0.71 | ns, Min |

|                                                    | Address An inputs through MUXs and/or carry logic to clock | 0.69/0.18 | 0.77/0.21 | 0.94/0.26 | 1.11/0.29 | ns, Min |

| T <sub>WS_LRAM</sub> /T <sub>WH_LRAM</sub>         | WE input to clock                                          | 0.38/0.10 | 0.43/0.12 | 0.53/0.17 | 0.62/0.13 | ns, Min |

| T <sub>CECK_LRAM</sub> /<br>T <sub>CKCE_LRAM</sub> | CE input to CLK                                            | 0.39/0.10 | 0.44/0.11 | 0.53/0.17 | 0.63/0.12 | ns, Min |

| Clock CLK                                          | ·                                                          |           |           |           |           |         |

| T <sub>MPW_LRAM</sub>                              | Minimum pulse width                                        | 1.05      | 1.13      | 1.25      | 0.82      | ns, Min |

| T <sub>MCP</sub>                                   | Minimum clock period                                       | 2.10      | 2.26      | 2.50      | 1.64      | ns, Min |

#### Notes:

- 1. A Zero "0" Hold Time listing indicates no hold time or a negative hold time.

- 2. T<sub>SHCKO</sub> also represents the CLK to XMUX output. Refer to TRACE report for the CLK to XMUX path.

# CLB Shift Register Switching Characteristics (SLICEM Only)

## Table 26: CLB Shift Register Switching Characteristics

|                                                        |                                     |           | Speed     | Grade     |           |         |

|--------------------------------------------------------|-------------------------------------|-----------|-----------|-----------|-----------|---------|

| Symbol                                                 | Description                         |           | 1.0V      |           |           | Units   |

|                                                        |                                     | -3        | -2/-2L    | -1        | -2L       |         |

| Sequential Delays                                      |                                     |           |           |           |           |         |

| T <sub>REG</sub>                                       | Clock to A – D outputs              | 1.19      | 1.33      | 1.61      | 1.89      | ns, Max |

| T <sub>REG_MUX</sub>                                   | Clock to AMUX – DMUX output         | 1.58      | 1.77      | 2.15      | 2.53      | ns, Max |

| T <sub>REG_M31</sub>                                   | Clock to DMUX output via M31 output | 1.12      | 1.23      | 1.46      | 1.68      | ns, Max |

| Setup and Hold Tir                                     | nes Before/After Clock CLK          |           |           | 1         | LL        |         |

| T <sub>WS_SHFREG</sub> /<br>T <sub>WH_SHFREG</sub>     | WE input                            | 0.37/0.10 | 0.41/0.12 | 0.51/0.17 | 0.59/0.13 | ns, Min |

| T <sub>CECK_SHFREG</sub> /<br>T <sub>CKCE_SHFREG</sub> | CE input to CLK                     | 0.37/0.10 | 0.42/0.11 | 0.52/0.17 | 0.60/0.12 | ns, Min |

| T <sub>DS_SHFREG</sub> /<br>T <sub>DH_SHFREG</sub>     | A – D inputs to CLK                 | 0.33/0.34 | 0.37/0.37 | 0.44/0.43 | 0.54/0.47 | ns, Min |

| Clock CLK                                              |                                     | L         | 1         | 1         |           |         |

| T <sub>MPW_SHFREG</sub>                                | Minimum pulse width                 | 0.77      | 0.86      | 0.98      | 1.04      | ns, Min |

#### Notes:

1. A Zero "0" Hold Time listing indicates no hold time or a negative hold time.

## Table 27: Block RAM and FIFO Switching Characteristics (Cont'd)

|                                                    |                                                                                                                                                   | Speed Grade |            |            |            |         |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|------------|------------|---------|

| Symbol                                             | Description                                                                                                                                       |             | 1.0V       |            | 0.9V       | Units   |

|                                                    |                                                                                                                                                   | -3          | -2/-2L     | -1         | -2L        |         |

| T <sub>RCCK_RSTRAM</sub> /T <sub>RCKC_RSTRAM</sub> | Synchronous RSTRAM input                                                                                                                          | 0.32/0.42   | 0.34/0.43  | 0.36/0.46  | 0.40/0.47  | ns, Min |

| T <sub>RCCK_WEA</sub> /T <sub>RCKC_WEA</sub>       | Write enable (WE) input (block RAM only)                                                                                                          | 0.44/0.18   | 0.48/0.19  | 0.54/0.20  | 0.64/0.23  | ns, Min |

| T <sub>RCCK_WREN</sub> /T <sub>RCKC_WREN</sub>     | WREN FIFO inputs                                                                                                                                  | 0.46/0.30   | 0.46/0.35  | 0.47/0.43  | 0.77/0.44  | ns, Min |

| T <sub>RCCK_RDEN</sub> /T <sub>RCKC_RDEN</sub>     | RDEN FIFO inputs                                                                                                                                  | 0.42/0.30   | 0.43/0.35  | 0.43/0.43  | 0.71/0.44  | ns, Min |

| Reset Delays                                       |                                                                                                                                                   |             |            |            |            |         |

| T <sub>RCO_FLAGS</sub>                             | Reset RST to FIFO flags/pointers <sup>(10)</sup>                                                                                                  | 0.90        | 0.98       | 1.10       | 1.25       | ns, Max |

| T <sub>RREC_RST</sub> /T <sub>RREM_RST</sub>       | FIFO reset recovery and removal timing <sup>(11)</sup>                                                                                            | 1.87/-0.81  | 2.07/-0.81 | 2.37/-0.81 | 2.44/-0.71 | ns, Max |

| Maximum Frequency                                  |                                                                                                                                                   |             |            | P          | Г          |         |

| F <sub>MAX_BRAM_WF_NC</sub>                        | Block RAM (write first and no change modes) when not in SDP RF mode                                                                               | 509.68      | 460.83     | 388.20     | 315.66     | MHz     |

| F <sub>MAX_BRAM_RF_PERFORMANCE</sub>               | Block RAM (read first, performance<br>mode) when in SDP RF mode but no<br>address overlap between port A and<br>port B                            | 509.68      | 460.83     | 388.20     | 315.66     | MHz     |

| F <sub>MAX_BRAM_RF_DELAYED_WRITE</sub>             | Block RAM (read first, delayed write<br>mode) when in SDP RF mode and<br>there is possibility of overlap between<br>port A and port B addresses   | 447.63      | 404.53     | 339.67     | 268.96     | MHz     |

| F <sub>MAX_CAS_WF_NC</sub>                         | Block RAM cascade (write first, no change mode) when cascade but not in RF mode                                                                   | 467.07      | 418.59     | 345.78     | 273.30     | MHz     |

| F <sub>MAX_CAS_RF_PERFORMANCE</sub>                | Block RAM cascade (read first,<br>performance mode) when in cascade<br>with RF mode and no possibility of<br>address overlap/one port is disabled | 467.07      | 418.59     | 345.78     | 273.30     | MHz     |

| F <sub>MAX_CAS_RF_DELAYED_WRITE</sub>              | When in cascade RF mode and there is<br>a possibility of address overlap<br>between port A and port B                                             | 405.35      | 362.19     | 297.35     | 226.60     | MHz     |

| F <sub>MAX_FIFO</sub>                              | FIFO in all modes without ECC                                                                                                                     | 509.68      | 460.83     | 388.20     | 315.66     | MHz     |

| F <sub>MAX_ECC</sub>                               | Block RAM and FIFO in ECC configuration                                                                                                           | 410.34      | 365.10     | 297.53     | 215.38     | MHz     |

## Notes:

- 1. TRACE will report all of these parameters as T<sub>RCKO DO</sub>.

- 2. T<sub>RCKO\_DOR</sub> includes T<sub>RCKO\_DOW</sub>, T<sub>RCKO\_DOPR</sub>, and T<sub>RCKO\_DOPW</sub> as well as the B port equivalent timing parameters.

- 3. These parameters also apply to synchronous FIFO with DO\_REG = 0.

- 4.  $T_{RCKO_{DO}}$  includes  $T_{RCKO_{DOP}}$  as well as the B port equivalent timing parameters.

- 5. These parameters also apply to multirate (asynchronous) and synchronous FIFO with DO\_REG = 1.

- 6. T<sub>RCKO\_FLAGS</sub> includes the following parameters: T<sub>RCKO\_AEMPTY</sub>, T<sub>RCKO\_AFULL</sub>, T<sub>RCKO\_EMPTY</sub>, T<sub>RCKO\_FULL</sub>, T<sub>RCKO\_RDERR</sub>, T<sub>RCKO\_WRERR</sub>.

- 7. T<sub>RCKO\_POINTERS</sub> includes both T<sub>RCKO\_RDCOUNT</sub> and T<sub>RCKO\_WRCOUNT</sub>.

- 8. The ADDR setup and hold must be met when EN is asserted (even when WE is deasserted). Otherwise, block RAM data corruption is possible.

- 9. These parameters include both A and B inputs as well as the parity inputs of A and B.

- 10. T<sub>RCO FLAGS</sub> includes the following flags: AEMPTY, AFULL, EMPTY, FULL, RDERR, WRERR, RDCOUNT, and WRCOUNT.

- 11. RDEN and WREN must be held Low prior to and during reset. The FIFO reset must be asserted for at least five positive clock edges of the slowest clock (WRCLK or RDCLK).

# **PLL Switching Characteristics**

# Table 35: PLL Specification

|                                                          |                                                       |           | Speed        | Grade         |              |          |

|----------------------------------------------------------|-------------------------------------------------------|-----------|--------------|---------------|--------------|----------|

| Symbol                                                   | Description                                           |           | 1.0V         |               | 0.9V         | Units    |

|                                                          |                                                       | -3        | -2/-2L       | -1            | -2L          | +        |

| PLL_F <sub>INMAX</sub>                                   | Maximum input clock frequency                         | 800.00    | 800.00       | 800.00        | 800.00       | MHz      |

| PLL_F <sub>INMIN</sub>                                   | Minimum input clock frequency                         | 19.00     | 19.00        | 19.00         | 19.00        | MHz      |

| PLL_F <sub>INJITTER</sub>                                | Maximum input clock period jitter                     | < 2       | 20% of clock | c input perio | od or 1 ns N | lax      |

| PLL_FINDUTY                                              | Allowable input duty cycle: 19-49 MHz                 | 25        | 25           | 25            | 25           | %        |

|                                                          | Allowable input duty cycle: 50—199 MHz                | 30        | 30           | 30            | 30           | %        |

|                                                          | Allowable input duty cycle: 200-399 MHz               | 35        | 35           | 35            | 35           | %        |

|                                                          | Allowable input duty cycle: 400-499 MHz               | 40        | 40           | 40            | 40           | %        |

|                                                          | Allowable input duty cycle: >500 MHz                  | 45        | 45           | 45            | 45           | %        |

| PLL_F <sub>VCOMIN</sub>                                  | Minimum PLL VCO frequency                             | 800.00    | 800.00       | 800.00        | 800.00       | MHz      |

| PLL_F <sub>VCOMAX</sub>                                  | Maximum PLL VCO frequency                             | 2133.00   | 1866.00      | 1600.00       | 1600.00      | MHz      |

| PLL_FBANDWIDTH                                           | Low PLL bandwidth at typical <sup>(1)</sup>           | 1.00      | 1.00         | 1.00          | 1.00         | MHz      |

|                                                          | High PLL bandwidth at typical <sup>(1)</sup>          | 4.00      | 4.00         | 4.00          | 4.00         | MHz      |

| PLL_T <sub>STATPHAOFFSET</sub>                           | Static phase offset of the PLL outputs <sup>(2)</sup> | 0.12      | 0.12         | 0.12          | 0.12         | ns       |

| PLL_T <sub>OUTJITTER</sub>                               | PLL output jitter                                     |           | 1            | Note 3        | 1            | 1        |

| PLL_T <sub>OUTDUTY</sub>                                 | PLL output clock duty-cycle precision <sup>(4)</sup>  | 0.20      | 0.20         | 0.20          | 0.25         | ns       |

| PLL_T <sub>LOCKMAX</sub>                                 | PLL maximum lock time                                 | 100.00    | 100.00       | 100.00        | 100.00       | μs       |

| PLL_F <sub>OUTMAX</sub>                                  | PLL maximum output frequency                          | 800.00    | 800.00       | 800.00        | 800.00       | MHz      |

| PLL_F <sub>OUTMIN</sub>                                  | PLL minimum output frequency <sup>(5)</sup>           | 6.25      | 6.25         | 6.25          | 6.25         | MHz      |

| PLL_T <sub>EXTFDVAR</sub>                                | External clock feedback variation                     | < 2       | 20% of clock | k input perio | od or 1 ns N | lax      |

| PLL_RST <sub>MINPULSE</sub>                              | Minimum reset pulse width                             | 5.00      | 5.00         | 5.00          | 5.00         | ns       |

| PLL_F <sub>PFDMAX</sub>                                  | Maximum frequency at the phase frequency detector     | 550.00    | 500.00       | 450.00        | 450.00       | MHz      |

| PLL_F <sub>PFDMIN</sub>                                  | Minimum frequency at the phase frequency detector     | 19.00     | 19.00        | 19.00         | 19.00        | MHz      |

| PLL_T <sub>FBDELAY</sub>                                 | Maximum delay in the feedback path                    |           | 3 ns Max     | or one CLI    | KIN cycle    | I        |

| Dynamic Reconfigura                                      | tion Port (DRP) for PLL Before and After DCLK         | L         |              |               |              |          |

| T <sub>PLLDCK_DADDR</sub> /<br>T <sub>PLLCKD_DADDR</sub> | Setup and hold of D address                           | 1.25/0.15 | 1.40/0.15    | 1.63/0.15     | 1.43/0.00    | ns, Min  |

| T <sub>PLLDCK_DI</sub> /T <sub>PLLCKD_DI</sub>           | Setup and hold of D input                             | 1.25/0.15 | 1.40/0.15    | 1.63/0.15     | 1.43/0.00    | ns, Min  |

| T <sub>PLLDCK_DEN</sub> /<br>T <sub>PLLCKD_DEN</sub>     | Setup and hold of D enable                            | 1.76/0.00 | 1.97/0.00    | 2.29/0.00     | 2.40/0.00    | ns, Min  |

| T <sub>PLLDCK_DWE</sub> /<br>T <sub>PLLCKD_DWE</sub>     | Setup and hold of D write enable                      | 1.25/0.15 | 1.40/0.15    | 1.63/0.15     | 1.43/0.00    | ns, Min  |

| T <sub>PLLCKO_DRDY</sub>                                 | CLK to out of DRDY                                    | 0.65      | 0.72         | 0.99          | 0.99         | ns, Max  |

| F <sub>DCK</sub>                                         | DCLK frequency                                        | 200.00    | 200.00       | 200.00        | 100.00       | MHz, Max |

#### Notes:

1. The PLL does not filter typical spread-spectrum input clocks because they are usually far below the bandwidth filter frequencies.

2. The static offset is measured between any PLL outputs with identical phase.

3. Values for this parameter are available in the Clocking Wizard. See <a href="http://www.xilinx.com/products/intellectual-property/clocking\_wizard.htm">http://www.xilinx.com/products/intellectual-property/clocking\_wizard.htm</a>.

4. Includes global clock buffer.

5. Calculated as  $F_{VCO}/128$  assuming output duty cycle is 50%.

# **Device Pin-to-Pin Output Parameter Guidelines**

All devices are 100% functionally tested. Values are expressed in nanoseconds unless otherwise noted.

## Table 36: Clock-Capable Clock Input to Output Delay Without MMCM/PLL (Near Clock Region)

|                                                        |                                            | Device                |            |            |         |       |    |

|--------------------------------------------------------|--------------------------------------------|-----------------------|------------|------------|---------|-------|----|

| Symbol                                                 | Description                                |                       |            | 1.0V       | 0.9V    | Units |    |

|                                                        |                                            |                       | -3         | -2/-2L     | -1      | -2L   | 1  |

| SSTL15 Clock-Capa                                      | able Clock Input to Output Delay using Out | out Flip-Flop, Fast § | Slew Rate, | without MM | CM/PLL. |       |    |

| T <sub>ICKOF</sub> Clock-capable clock input and OUTFF | XC7A100T                                   | 5.14                  | 5.74       | 6.72       | 7.64    | ns    |    |

|                                                        | without MMCM/PLL (near clock region)       | XC7A200T              | 5.47       | 6.11       | 7.16    | 8.10  | ns |

#### Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

## Table 37: Clock-Capable Clock Input to Output Delay Without MMCM/PLL (Far Clock Region)

| Symbol                | Description                                                             | Device                | Speed Grade |            |         |       |    |  |

|-----------------------|-------------------------------------------------------------------------|-----------------------|-------------|------------|---------|-------|----|--|

|                       |                                                                         |                       |             | 1.0V       | 0.9V    | Units |    |  |

|                       |                                                                         |                       | -3          | -2/-2L     | -1      | -2L   |    |  |

| SSTL15 Clock-Capa     | ble Clock Input to Output Delay using Outp                              | out Flip-Flop, Fast S | Slew Rate,  | without MM | CM/PLL. |       |    |  |

| T <sub>ICKOFFAR</sub> | Clock-capable clock input and OUTFF without MMCM/PLL (far clock region) | XC7A100T              | 5.38        | 6.01       | 7.02    | 7.96  | ns |  |

|                       |                                                                         | XC7A200T              | 6.17        | 6.89       | 8.05    | 9.05  | ns |  |

#### Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

## Table 38: Clock-Capable Clock Input to Output Delay With MMCM

| Symbol                   | Description                                   | Device              |            |           |      |       |    |

|--------------------------|-----------------------------------------------|---------------------|------------|-----------|------|-------|----|

|                          |                                               |                     |            | 1.0V      | 0.9V | Units |    |

|                          |                                               |                     | -3         | -2/-2L    | -1   | -2L   |    |

| SSTL15 Clock-Capa        | able Clock Input to Output Delay using Out    | put Flip-Flop, Fast | Slew Rate, | with MMCM |      | ·     |    |

| T <sub>ICKOFMMCMCC</sub> | Clock-capable clock input and OUTFF with MMCM | XC7A100T            | 0.89       | 0.94      | 0.96 | 1.81  | ns |

|                          |                                               | XC7A200T            | 0.90       | 0.97      | 1.01 | 1.86  | ns |

Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

2. MMCM output jitter is already included in the timing calculation.

www.xilinx.com

## Table 44: Data Input Setup and Hold Times Relative to a Forwarded Clock Input Pin Using BUFIO

| Symbol                               | Description                                      |              | 1.0V        | 0.9V       | Units      |    |

|--------------------------------------|--------------------------------------------------|--------------|-------------|------------|------------|----|

|                                      |                                                  | -3           | -2/-2L      | -1         | -2L        |    |

| Input Setup and Hold Time            | Relative to a Forwarded Clock Input Pin Using Bl | UFIO for SST | L15 Standar | d.         |            |    |

| T <sub>PSCS</sub> /T <sub>PHCS</sub> | Setup and hold of I/O clock                      | -0.38/1.31   | -0.38/1.46  | -0.38/1.76 | -0.16/1.89 | ns |

## Table 45: Sample Window

| Symbol                  | Description                                                      |      | 1.0V   | 0.9V | Units |    |

|-------------------------|------------------------------------------------------------------|------|--------|------|-------|----|

|                         |                                                                  | -3   | -2/-2L | -1   | -2L   | *  |

| T <sub>SAMP</sub>       | Sampling error at receiver pins <sup>(1)</sup>                   | 0.59 | 0.64   | 0.70 | 0.70  | ns |

| T <sub>SAMP_BUFIO</sub> | BUFIO Sampling error at receiver pins using BUFIO <sup>(2)</sup> |      | 0.40   | 0.46 | 0.46  | ns |

#### Notes:

- 1. This parameter indicates the total sampling error of the Artix-7 FPGAs DDR input registers, measured across voltage, temperature, and process. The characterization methodology uses the MMCM to capture the DDR input registers' edges of operation. These measurements include:

- CLK0 MMCM jitter

- MMCM accuracy (phase offset)

- MMCM phase shift resolution

- These measurements do not include package or clock tree skew.

- This parameter indicates the total sampling error of the Artix-7 FPGAs DDR input registers, measured across voltage, temperature, and process. The characterization methodology uses the BUFIO clock network and IDELAY to capture the DDR input registers' edges of operation. These measurements do not include package or clock tree skew.

# **Additional Package Parameter Guidelines**

The parameters in this section provide the necessary values for calculating timing budgets for Artix-7 FPGA clock transmitter and receiver data-valid windows.

#### Table 46: Package Skew

| Symbol               | Description                 | Device   | Package | Value | Units |

|----------------------|-----------------------------|----------|---------|-------|-------|

| T <sub>PKGSKEW</sub> | Package skew <sup>(1)</sup> | XC7A100T | CSG324  | 113   | ps    |

|                      |                             |          | FTG256  | 120   | ps    |

|                      |                             |          | FGG484  | 144   | ps    |

|                      |                             |          | FGG676  | 153   | ps    |

|                      |                             | XC7A200T | SBG484  | 111   | ps    |

|                      |                             |          | FBG484  | 109   | ps    |

|                      |                             |          | FBG676  | 121   | ps    |

|                      |                             |          | FFG1156 | 151   | ps    |

#### Notes:

- 1. These values represent the worst-case skew between any two SelectIO resources in the package: shortest delay to longest delay from die pad to ball.

- 2. Package delay information is available for these device/package combinations. This information can be used to deskew the package.

# **GTP Transceiver Specifications**

# **GTP Transceiver DC Input and Output Levels**

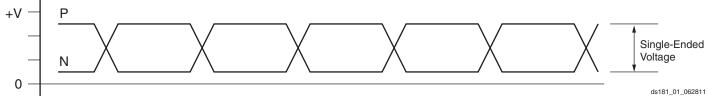

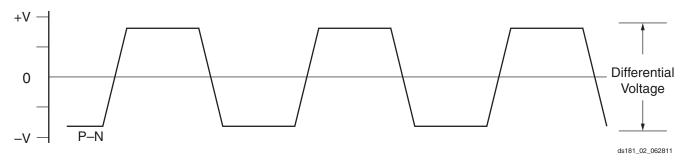

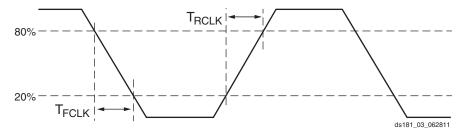

Table 47 summarizes the DC output specifications of the GTP transceivers in Artix-7 FPGAs. Consult UG482: 7 Series

FPGAs GTP Transceiver User Guide for further details.

Table 47: GTP Transceiver DC Specifications

| Symbol                                                           | DC Parameter                                              | Conditions                                                                     | Min  | Тур                                      | Max                  | Units |

|------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|------|------------------------------------------|----------------------|-------|

| DV <sub>PPOUT</sub>                                              | Differential peak-to-peak output voltage <sup>(1)</sup>   | Transmitter output swing is set to maximum setting                             | _    | _                                        | 1000                 | mV    |

| V <sub>CMOUTDC</sub>                                             | DC common mode output voltage                             | Equation based                                                                 | Ņ    | V <sub>MGTAVTT</sub> – DV <sub>PPO</sub> | UT/4                 | mV    |