Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 7925                                                          |

| Number of Logic Elements/Cells | 101440                                                        |

| Total RAM Bits                 | 4976640                                                       |

| Number of I/O                  | 300                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 0.95V ~ 1.05V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 676-BGA                                                       |

| Supplier Device Package        | 676-FBGA (27x27)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc7a100t-2fgg676i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1: Absolute Maximum Ratings(1) (Cont'd)

| Symbol           | Description                                                    | Min | Max  | Units |

|------------------|----------------------------------------------------------------|-----|------|-------|

| Temperature      |                                                                |     |      |       |

| T <sub>STG</sub> | Storage temperature (ambient)                                  | -65 | 150  | °C    |

| т                | Maximum soldering temperature for Pb/Sn component bodies (6)   | _   | +220 | °C    |

| ISOL             | Maximum soldering temperature for Pb-free component bodies (6) | _   | +260 | °C    |

| Tj               | Maximum junction temperature <sup>(6)</sup>                    | _   | +125 | °C    |

- Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

- 2. The lower absolute voltage specification always applies.

- 3. For I/O operation, refer to UG471: 7 Series FPGAs SelectIO Resources User Guide.

- The maximum limit applied to DC signals.

- 5. For maximum undershoot and overshoot AC specifications, see Table 4.

- 6. For soldering guidelines and thermal considerations, see UG475: 7 Series FPGA Packaging and Pinout Specification.

Table 2: Recommended Operating Conditions(1)(2)

| Symbol                                 | Description                                                                                          | Min   | Тур  | Max                     | Units |

|----------------------------------------|------------------------------------------------------------------------------------------------------|-------|------|-------------------------|-------|

| FPGA Logic                             |                                                                                                      |       |      |                         |       |

| V                                      | Internal supply voltage                                                                              | 0.95  | 1.00 | 1.05                    | V     |

| V <sub>CCINT</sub>                     | For -2L (0.9V) devices: internal supply voltage                                                      | 0.87  | 0.90 | 0.93                    | V     |

| V <sub>CCAUX</sub>                     | Auxiliary supply voltage                                                                             | 1.71  | 1.80 | 1.89                    | V     |

| V <sub>CCBRAM</sub>                    | Block RAM supply voltage                                                                             | 0.95  | 1.00 | 1.05                    | ٧     |

| V <sub>CCO</sub> (3)(4)                | Supply voltage for 3.3V HR I/O banks                                                                 | 1.14  | _    | 3.465                   | V     |

| V (5)                                  | I/O input voltage                                                                                    | -0.20 | _    | V <sub>CCO</sub> + 0.20 | V     |

| V <sub>IN</sub> <sup>(5)</sup>         | I/O input voltage for V <sub>REF</sub> and differential I/O standards                                | -0.20 | _    | 2.625                   | ٧     |

| I <sub>IN</sub> <sup>(6)</sup>         | Maximum current through any pin in a powered or unpowered bank when forward biasing the clamp diode. | -     | _    | 10                      | mA    |

| V <sub>CCBATT</sub> <sup>(7)</sup>     | Battery voltage                                                                                      | 1.0   | _    | 1.89                    | ٧     |

| GTP Transceiv                          | ver                                                                                                  |       | 1    | -1                      |       |

| V <sub>MGTAVCC</sub> <sup>(8)(9)</sup> | Analog supply voltage for the GTP transmitter and receiver circuits                                  | 0.97  | 1.0  | 1.03                    | V     |

| V <sub>MGTAVTT</sub> <sup>(8)(9)</sup> | Analog supply voltage for the GTP transmitter and receiver termination circuits                      | 1.17  | 1.2  | 1.23                    | V     |

| XADC                                   |                                                                                                      |       |      |                         |       |

| V <sub>CCADC</sub>                     | XADC supply relative to GNDADC                                                                       | 1.71  | 1.80 | 1.89                    | V     |

| V <sub>REFP</sub>                      | Externally supplied reference voltage                                                                | 1.20  | 1.25 | 1.30                    | ٧     |

## Table 2: Recommended Operating Conditions(1)(2) (Cont'd)

| Symbol         | Description                                                                 | Min | Тур | Max | Units |

|----------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

| Temperature    |                                                                             |     |     |     |       |

|                | Junction temperature operating range for commercial (C) temperature devices | 0   | _   | 85  | °C    |

| T <sub>j</sub> | Junction temperature operating range for extended (E) temperature devices   | 0   | _   | 100 | °C    |

|                | Junction temperature operating range for industrial (I) temperature devices | -40 | _   | 100 | °C    |

- 1. All voltages are relative to ground.

- 2. For the design of the power distribution system consult UG483, 7 Series FPGAs PCB Design and Pin Planning Guide.

- 3. Configuration data is retained even if  $V_{\mbox{\footnotesize CCO}}$  drops to 0V.

- 4. Includes V<sub>CCO</sub> of 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V.

- 5. The lower absolute voltage specification always applies.

- 6. A total of 200 mA per bank should not be exceeded.

- 7. V<sub>CCBATT</sub> is required only when using bitstream encryption. If battery is not used, connect V<sub>CCBATT</sub> to either ground or V<sub>CCAUX</sub>.

- 8. Each voltage listed requires the filter circuit described in UG482: 7 Series FPGAs GTP Transceiver User Guide.

- 9. Voltages are specified for the temperature range of  $T_i = 0^{\circ}C$  to  $+85^{\circ}C$ .

Table 3: DC Characteristics Over Recommended Operating Conditions

| Symbol                              | Description                                                                                                                                                                         | Min  | Typ <sup>(1)</sup> | Max | Units |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----|-------|

| V <sub>DRINT</sub>                  | Data retention V <sub>CCINT</sub> voltage (below which configuration data might be lost)                                                                                            | 0.75 | -                  | _   | V     |

| $V_{DRI}$                           | Data retention V <sub>CCAUX</sub> voltage (below which configuration data might be lost)                                                                                            | 1.5  | _                  | _   | V     |

| I <sub>REF</sub>                    | V <sub>REF</sub> leakage current per pin                                                                                                                                            | _    | _                  | 15  | μΑ    |

| IL                                  | Input or output leakage current per pin (sample-tested)                                                                                                                             | _    | _                  | 15  | μΑ    |

| C <sub>IN</sub> <sup>(2)</sup>      | Die input capacitance at the pad                                                                                                                                                    | _    | _                  | 8   | pF    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 3.3V                                                                                                         | 90   | _                  | 330 | μΑ    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 2.5V                                                                                                         | 68   | _                  | 250 | μΑ    |

| I <sub>RPU</sub>                    | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 1.8V                                                                                                         | 34   | _                  | 220 | μA    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 1.5V                                                                                                         | 23   | _                  | 150 | μA    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 1.2V                                                                                                         | 12   | _                  | 120 | μA    |

|                                     | Pad pull-down (when selected) @ V <sub>IN</sub> = 3.3V                                                                                                                              | 68   | _                  | 330 | μA    |

| I <sub>RPD</sub>                    | Pad pull-down (when selected) @ V <sub>IN</sub> = 1.8V                                                                                                                              | 45   | _                  | 180 | μA    |

| I <sub>CCADC</sub>                  | Analog supply current, analog circuits in powered up state                                                                                                                          | _    | _                  | 25  | mA    |

| I <sub>BATT</sub> (3)               | Battery supply current                                                                                                                                                              | _    | _                  | 150 | nA    |

|                                     | Thevenin equivalent resistance of programmable input termination to $V_{\rm CCO}/2$ (UNTUNED_SPLIT_40) for commercial (C), and industrial (I), and extended (E) temperature devices | 28   | 40                 | 55  | Ω     |

| R <sub>IN_TERM</sub> <sup>(4)</sup> | Thevenin equivalent resistance of programmable input termination to $V_{CCO}/2$ (UNTUNED_SPLIT_50) for commercial (C), and industrial (I), and extended (E) temperature devices     | 35   | 50                 | 65  | Ω     |

|                                     | Thevenin equivalent resistance of programmable input termination to $V_{CCO}/2$ (UNTUNED_SPLIT_60) for commercial (C), and industrial (I), and extended (E) temperature devices     | 44   | 60                 | 83  | Ω     |

Table 3: DC Characteristics Over Recommended Operating Conditions (Cont'd)

| Symbol | Description                         | Min | Typ <sup>(1)</sup> | Max | Units |

|--------|-------------------------------------|-----|--------------------|-----|-------|

| n      | Temperature diode ideality factor   |     | 1.010              | _   | _     |

| r      | Temperature diode series resistance | _   | 2                  | _   | Ω     |

- 1. Typical values are specified at nominal voltage, 25°C.

- 2. This measurement represents the die capacitance at the pad, not including the package.

- 3. Maximum value specified for worst case process at 25°C.

- Termination resistance to a V<sub>CCO</sub>/2 level.

Table 4: V<sub>IN</sub> Maximum Allowed AC Voltage Overshoot and Undershoot for 3.3V HR I/O Banks<sup>(1)</sup>

| AC Voltage Overshoot    | % of UI @-40°C to 100°C | AC Voltage Undershoot | % of UI @-40°C to 100°C |

|-------------------------|-------------------------|-----------------------|-------------------------|

| V <sub>CCO</sub> + 0.40 | 100                     | -0.40                 | 100                     |

| V <sub>CCO</sub> + 0.45 | 100                     | -0.45                 | 61.7                    |

| V <sub>CCO</sub> + 0.50 | 100                     | -0.50                 | 25.8                    |

| V <sub>CCO</sub> + 0.55 | 100                     | -0.55                 | 11.0                    |

| V <sub>CCO</sub> + 0.60 | 46.6                    | -0.60                 | 4.77                    |

| V <sub>CCO</sub> + 0.65 | 21.2                    | -0.65                 | 2.10                    |

| V <sub>CCO</sub> + 0.70 | 9.75                    | -0.70                 | 0.94                    |

| V <sub>CCO</sub> + 0.75 | 4.55                    | -0.75                 | 0.43                    |

| V <sub>CCO</sub> + 0.80 | 2.15                    | -0.80                 | 0.20                    |

| V <sub>CCO</sub> + 0.85 | 1.02                    | -0.85                 | 0.09                    |

| V <sub>CCO</sub> + 0.90 | 0.49                    | -0.90                 | 0.04                    |

| V <sub>CCO</sub> + 0.95 | 0.24                    | -0.95                 | 0.02                    |

### Notes:

1. A total of 200 mA per bank should not be exceeded.

Table 5: Typical Quiescent Supply Current

| Symbol                   | Description                                  | Device   |     | 1.0V   |     | 0.9V | Units |

|--------------------------|----------------------------------------------|----------|-----|--------|-----|------|-------|

|                          |                                              |          | -3  | -2/-2L | -1  | -2L  |       |

| I <sub>CCINTQ</sub> Quie | Quiescent V <sub>CCINT</sub> supply current  | XC7A100T | 155 | 155    | 155 | 108  | mA    |

|                          |                                              | XC7A200T | 328 | 328    | 328 | 232  | mA    |

| I <sub>CCOQ</sub>        | Quiescent V <sub>CCO</sub> supply current    | XC7A100T | 4   | 4      | 4   | 4    | mA    |

|                          |                                              | XC7A200T | 5   | 5      | 5   | 5    | mA    |

| I <sub>CCAUXQ</sub>      | Quiescent V <sub>CCAUX</sub> supply current  | XC7A100T | 36  | 36     | 36  | 36   | mA    |

|                          |                                              | XC7A200T | 73  | 73     | 73  | 73   | mA    |

| I <sub>CCBRAMQ</sub>     | Quiescent V <sub>CCBRAM</sub> supply current | XC7A100T | 4   | 4      | 4   | 4    | mA    |

|                          |                                              | XC7A200T | 11  | 11     | 11  | 11   | mA    |

- 1. Typical values are specified at nominal voltage, 85°C junction temperature (T<sub>i</sub>) with single-ended SelectIO resources.

- 2. Typical values are for blank configured devices with no output current loads, no active input pull-up resistors, all I/O pins are 3-state and floating.

- Use the Xilinx Power Estimator (XPE) spreadsheet tool (download at <a href="http://www.xilinx.com/power">http://www.xilinx.com/power</a>) to calculate static power consumption for conditions other than those specified.

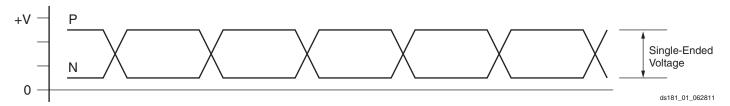

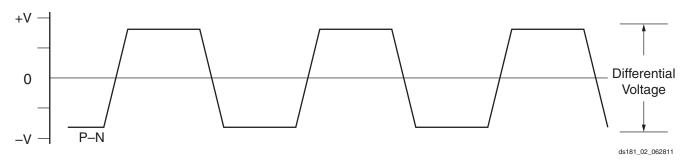

## LVDS DC Specifications (LVDS 25)

See <u>UG471</u>: 7 Series FPGAs SelectIO Resources User Guide for more information on the LVDS\_25 standard in the HR I/O banks.

Table 11: LVDS 25 DC Specifications

| Symbol             | DC Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Conditions                                                                                          | Min   | Тур   | Max   | Units |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CCO</sub>   | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                     | 2.375 | 2.500 | 2.625 | V     |

| V <sub>OH</sub>    | Output High Voltage for Q and Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Output High Voltage for Q and $\overline{Q}$ $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals |       |       |       | V     |

| V <sub>OL</sub>    | Output Low Voltage for Q and Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | or Q and $\overline{Q}$ $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals                      |       |       |       | V     |

| V <sub>ODIFF</sub> | Differential Output Voltage $(Q - \overline{Q})$ , $Q = \text{High } (\overline{Q} - Q)$ , $\overline{Q} = \text{High } Q = Hig$ |                                                                                                     | 247   | 350   | 600   | mV    |

| V <sub>OCM</sub>   | Output Common-Mode Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals                                              | 1.000 | 1.250 | 1.425 | V     |

| V <sub>IDIFF</sub> | Differential Input Voltage $(Q - \overline{Q})$ , $Q = High (\overline{Q} - Q)$ , $\overline{Q} = High$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                     |       | 350   | 600   | mV    |

| V <sub>ICM</sub>   | Input Common-Mode Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     | 0.300 | 1.200 | 1.425 | V     |

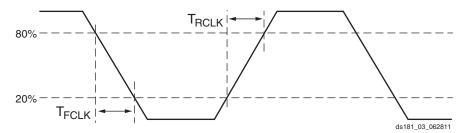

## **AC Switching Characteristics**

All values represented in this data sheet are based on the speed specifications in v1.07 from the 14.4/2012.4 device pack for ISE® Design Suite14.4 and Vivado® Design Suite 2012.4 for the -3, -2, -2L (1.0V), and -1 speed grades and v1.05 from the 14.4/2012.4 device pack for the -2L (0.9V) speed grade.

Switching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows:

### Advance Product Specification

These specifications are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation are considered relatively stable and conservative, some underreporting might still occur.

### **Preliminary Product Specification**

These specifications are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data.

### **Production Product Specification**

These specifications are released once enough production silicon of a particular device family member has been characterized to provide full correlation between specifications and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

## **Testing of AC Switching Characteristics**

Internal timing parameters are derived from measuring internal test patterns. All AC switching characteristics are representative of worst-case supply voltage and junction temperature conditions.

For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer and back-annotate to the simulation net list. Unless otherwise noted, values apply to all Artix-7 FPGAs.

## **Speed Grade Designations**

Since individual family members are produced at different times, the migration from one category to another depends completely on the status of the fabrication process for each device. Table 12 correlates the current status of each Artix-7 device on a per speed grade basis.

Table 12: Artix-7 Device Speed Grade Designations

| Device   | Speed Grade Designations |             |                        |  |  |  |  |  |

|----------|--------------------------|-------------|------------------------|--|--|--|--|--|

| Device   | Advance                  | Preliminary | Production             |  |  |  |  |  |

| XC7A100T | -2L (0.9V)               |             | -3, -2, -2L (1.0V), -1 |  |  |  |  |  |

| XC7A200T | -2L (0.9V)               |             | -3, -2, -2L (1.0V), -1 |  |  |  |  |  |

### **Production Silicon and ISE Software Status**

In some cases, a particular family member (and speed grade) is released to production before a speed specification is released with the correct label (Advance, Preliminary, Production). Any labeling discrepancies are corrected in subsequent speed specification releases.

Table 13 lists the production released Artix-7 device, speed grade, and the minimum corresponding supported speed specification version and ISE software revisions. The ISE software and speed specifications listed are the minimum releases required for production. All subsequent releases of software and speed specifications are valid.

Table 13: Artix-7 Device Production Software and Speed Specification Release

|          | Speed Grade        |                              |                     |     |  |  |  |  |  |

|----------|--------------------|------------------------------|---------------------|-----|--|--|--|--|--|

| Device   |                    | 0.9V                         |                     |     |  |  |  |  |  |

|          | -3                 | -2/-2L                       | -1                  | -2L |  |  |  |  |  |

| XC7A100T | ISE 14.4 and Vivad | o 2012.4 with the 14.4/2012. | 4 device pack v1.07 |     |  |  |  |  |  |

| XC7A200T | ISE 14.4 and Vivad | o 2012.4 with the 14.4/2012. | 4 device pack v1.07 |     |  |  |  |  |  |

#### Notes:

1. Blank entries indicate a device and/or speed grade in advance or preliminary status.

## **IOB Pad Input/Output/3-State**

Table 16 summarizes the values of standard-specific data input delay adjustments, output delays terminating at pads (based on standard) and 3-state delays.

- T<sub>IOPI</sub> is described as the delay from IOB pad through the input buffer to the I-pin of an IOB pad. The delay varies

depending on the capability of the SelectIO input buffer.

- T<sub>IOOP</sub> is described as the delay from the O pin to the IOB pad through the output buffer of an IOB pad. The delay varies depending on the capability of the SelectIO output buffer.

- T<sub>IOTP</sub> is described as the delay from the T pin to the IOB pad through the output buffer of an IOB pad, when 3-state is disabled. The delay varies depending on the SelectIO capability of the output buffer. In HR I/O banks, the IN\_TERM termination turn-on time is always faster than T<sub>IOTP</sub> when the INTERMDISABLE pin is used.

Table 16: 3.3V IOB High Range (HR) Switching Characteristics

|                          |      | T <sub>IOPI</sub> |       |      | T <sub>IOOP</sub> |        |       | T <sub>IOTP</sub> |      |        |       |      |         |

|--------------------------|------|-------------------|-------|------|-------------------|--------|-------|-------------------|------|--------|-------|------|---------|

| I/O Standard             |      | Speed             | Grade |      |                   | Speed  | Grade |                   |      | Speed  | Grade |      | - Units |

| " O Staridard            |      | 1.0V              |       | 0.9V |                   | 1.0V   |       | 0.9V              |      | 1.0V   |       | 0.9V | Onits   |

|                          | -3   | -2/-2L            | -1    | -2L  | -3                | -2/-2L | -1    | -2L               | -3   | -2/-2L | -1    | -2L  |         |

| LVTTL_S4                 | 1.26 | 1.34              | 1.41  | 1.58 | 3.80              | 3.93   | 4.18  | 4.41              | 4.37 | 4.59   | 5.01  | 5.06 | ns      |

| LVTTL_S8                 | 1.26 | 1.34              | 1.41  | 1.58 | 3.54              | 3.66   | 3.92  | 4.15              | 4.11 | 4.32   | 4.75  | 4.80 | ns      |

| LVTTL_S12                | 1.26 | 1.34              | 1.41  | 1.58 | 3.52              | 3.65   | 3.90  | 4.13              | 4.09 | 4.31   | 4.73  | 4.78 | ns      |

| LVTTL_S16                | 1.26 | 1.34              | 1.41  | 1.58 | 3.07              | 3.19   | 3.45  | 3.68              | 3.64 | 3.85   | 4.28  | 4.33 | ns      |

| LVTTL_S24                | 1.26 | 1.34              | 1.41  | 1.58 | 3.29              | 3.41   | 3.67  | 3.90              | 3.86 | 4.07   | 4.50  | 4.55 | ns      |

| LVTTL_F4                 | 1.26 | 1.34              | 1.41  | 1.58 | 3.26              | 3.38   | 3.64  | 3.86              | 3.83 | 4.04   | 4.46  | 4.51 | ns      |

| LVTTL_F8                 | 1.26 | 1.34              | 1.41  | 1.58 | 2.74              | 2.87   | 3.12  | 3.35              | 3.31 | 3.52   | 3.95  | 4.00 | ns      |

| LVTTL_F12                | 1.26 | 1.34              | 1.41  | 1.58 | 2.73              | 2.85   | 3.10  | 3.33              | 3.29 | 3.51   | 3.93  | 3.98 | ns      |

| LVTTL_F16                | 1.26 | 1.34              | 1.41  | 1.58 | 2.55              | 2.68   | 2.93  | 3.16              | 3.12 | 3.34   | 3.76  | 3.81 | ns      |

| LVTTL_F24                | 1.26 | 1.34              | 1.41  | 1.58 | 2.52              | 2.65   | 2.90  | 3.22              | 3.09 | 3.31   | 3.73  | 3.87 | ns      |

| LVDS_25                  | 0.73 | 0.81              | 0.88  | 0.90 | 1.29              | 1.41   | 1.67  | 1.86              | 1.86 | 2.07   | 2.49  | 2.51 | ns      |

| MINI_LVDS_25             | 0.73 | 0.81              | 0.88  | 0.90 | 1.27              | 1.40   | 1.65  | 1.88              | 1.84 | 2.06   | 2.48  | 2.53 | ns      |

| BLVDS_25                 | 0.73 | 0.81              | 0.88  | 0.90 | 1.84              | 1.96   | 2.21  | 2.44              | 2.40 | 2.62   | 3.04  | 3.09 | ns      |

| RSDS_25 (point to point) | 0.73 | 0.81              | 0.88  | 0.90 | 1.27              | 1.40   | 1.65  | 1.88              | 1.84 | 2.06   | 2.48  | 2.53 | ns      |

| PPDS_25                  | 0.73 | 0.81              | 0.88  | 0.90 | 1.29              | 1.41   | 1.67  | 1.88              | 1.86 | 2.07   | 2.49  | 2.53 | ns      |

| TMDS_33                  | 0.73 | 0.81              | 0.88  | 0.90 | 1.41              | 1.54   | 1.79  | 1.99              | 1.98 | 2.20   | 2.62  | 2.64 | ns      |

| PCl33_3                  | 1.24 | 1.32              | 1.39  | 1.57 | 3.10              | 3.22   | 3.48  | 3.71              | 3.67 | 3.88   | 4.31  | 4.36 | ns      |

| HSUL_12                  | 0.67 | 0.75              | 0.82  | 0.87 | 1.80              | 1.93   | 2.18  | 2.41              | 2.37 | 2.59   | 3.01  | 3.06 | ns      |

| DIFF_HSUL_12             | 0.68 | 0.76              | 0.83  | 0.88 | 1.80              | 1.93   | 2.18  | 2.21              | 2.37 | 2.59   | 3.01  | 2.86 | ns      |

| HSTL_I_S                 | 0.67 | 0.75              | 0.82  | 0.87 | 1.62              | 1.74   | 1.99  | 2.19              | 2.19 | 2.40   | 2.82  | 2.84 | ns      |

| HSTL_II_S                | 0.65 | 0.73              | 0.80  | 0.85 | 1.41              | 1.54   | 1.79  | 1.99              | 1.98 | 2.20   | 2.62  | 2.64 | ns      |

| HSTL_I_18_S              | 0.67 | 0.75              | 0.82  | 0.87 | 1.29              | 1.41   | 1.67  | 1.86              | 1.86 | 2.07   | 2.49  | 2.51 | ns      |

| HSTL_II_18_S             | 0.66 | 0.75              | 0.81  | 0.87 | 1.41              | 1.54   | 1.79  | 1.97              | 1.98 | 2.20   | 2.62  | 2.62 | ns      |

| DIFF_HSTL_I_S            | 0.68 | 0.76              | 0.83  | 0.85 | 1.59              | 1.71   | 1.96  | 2.13              | 2.15 | 2.37   | 2.79  | 2.78 | ns      |

| DIFF_HSTL_II_S           | 0.68 | 0.76              | 0.83  | 0.85 | 1.51              | 1.63   | 1.88  | 2.07              | 2.08 | 2.29   | 2.71  | 2.72 | ns      |

| DIFF_HSTL_I_18_S         | 0.71 | 0.79              | 0.86  | 0.87 | 1.38              | 1.51   | 1.76  | 1.96              | 1.95 | 2.17   | 2.59  | 2.61 | ns      |

| DIFF_HSTL_II_18_S        | 0.70 | 0.78              | 0.85  | 0.87 | 1.46              | 1.58   | 1.84  | 2.00              | 2.03 | 2.24   | 2.67  | 2.65 | ns      |

| HSTL_I_F                 | 0.67 | 0.75              | 0.82  | 0.87 | 1.10              | 1.22   | 1.48  | 1.69              | 1.67 | 1.88   | 2.31  | 2.34 | ns      |

## **Input/Output Logic Switching Characteristics**

Table 18: ILOGIC Switching Characteristics

|                                          |                                                                          |           | Speed     | Grade     |            |         |

|------------------------------------------|--------------------------------------------------------------------------|-----------|-----------|-----------|------------|---------|

| Symbol                                   | Description                                                              |           | 1.0V      |           | 0.9V       | Units   |

|                                          |                                                                          | -3        | -2/-2L    | -1        | -2L        |         |

| Setup/Hold                               |                                                                          |           |           |           |            |         |

| T <sub>ICE1CK</sub> /T <sub>ICKCE1</sub> | CE1 pin setup/hold with respect to CLK                                   | 0.48/0.02 | 0.54/0.02 | 0.76/0.02 | 0.40/-0.07 | ns      |

| T <sub>ISRCK</sub> /T <sub>ICKSR</sub>   | ISRCK/T <sub>ICKSR</sub> SR pin setup/hold with respect to CLK           |           | 0.70/0.01 | 1.13/0.01 | 0.88/-0.35 | ns      |

| T <sub>IDOCK</sub> /T <sub>IOCKD</sub>   | CK/T <sub>IOCKD</sub> D pin setup/hold with respect to CLK without Delay |           | 0.01/0.29 | 0.01/0.33 | 0.01/0.33  | ns      |

| T <sub>IDOCKD</sub> /T <sub>IOCKDD</sub> | DDLY pin setup/hold with respect to CLK (using IDELAY)                   | 0.02/0.27 | 0.02/0.29 | 0.02/0.33 | 0.01/0.33  | ns      |

| Combinatorial                            |                                                                          |           | 1         | 1         |            |         |

| T <sub>IDI</sub>                         | D pin to O pin propagation delay, no Delay                               | 0.11      | 0.11      | 0.13      | 0.14       | ns      |

| T <sub>IDID</sub>                        | DDLY pin to O pin propagation delay (using IDELAY)                       | 0.11      | 0.12      | 0.14      | 0.15       | ns      |

| Sequential Delays                        | s                                                                        |           | ı         | 1         |            |         |

| T <sub>IDLO</sub>                        | D pin to Q1 pin using flip-flop as a latch without Delay                 | 0.41      | 0.44      | 0.51      | 0.54       | ns      |

| T <sub>IDLOD</sub>                       | DDLY pin to Q1 pin using flip-flop as a latch (using IDELAY)             | 0.41      | 0.44      | 0.51      | 0.55       | ns      |

| T <sub>ICKQ</sub>                        | CLK to Q outputs                                                         | 0.53      | 0.57      | 0.66      | 0.71       | ns      |

| T <sub>RQ_ILOGIC</sub>                   | SR pin to OQ/TQ out                                                      | 0.96      | 1.08      | 1.32      | 1.32       | ns      |

| T <sub>GSRQ_ILOGIC</sub>                 | Global set/reset to Q outputs                                            | 7.60      | 7.60      | 10.51     | 11.39      | ns      |

| Set/Reset                                |                                                                          |           |           |           |            |         |

| T <sub>RPW_ILOGIC</sub>                  | Minimum pulse width, SR inputs                                           | 0.61      | 0.72      | 0.72      | 0.68       | ns, Min |

Table 19: OLOGIC Switching Characteristics

|                                          |                                           |            | Speed      | Grade     |            |         |

|------------------------------------------|-------------------------------------------|------------|------------|-----------|------------|---------|

| Symbol                                   | Description                               |            | 1.0V       |           | 0.9V       | Units   |

|                                          |                                           | -3         | -2/-2L     | -1        | -2L        |         |

| Setup/Hold                               |                                           | ·          |            |           |            |         |

| T <sub>ODCK</sub> /T <sub>OCKD</sub>     | D1/D2 pins setup/hold with respect to CLK | 0.67/–0.11 | 0.71/0.11  | 0.84/0.11 | 0.60/0.18  | ns      |

| T <sub>OOCECK</sub> /T <sub>OCKOCE</sub> | OCE pin setup/hold with respect to CLK    | 0.32/0.58  | 0.34/0.58  | 0.51/0.58 | 0.21/-0.10 | ns      |

| T <sub>OSRCK</sub> /T <sub>OCKSR</sub>   | SR pin setup/hold with respect to CLK     | 0.37/0.21  | 0.44/0.21  | 0.80/0.21 | 0.62/-0.25 | ns      |

| T <sub>OTCK</sub> /T <sub>OCKT</sub>     | T1/T2 pins setup/hold with respect to CLK | 0.69/-0.14 | 0.73/-0.14 | 0.89/0.14 | 0.60/-0.18 | ns      |

| T <sub>OTCECK</sub> /T <sub>OCKTCE</sub> | TCE pin setup/hold with respect to CLK    | 0.32/0.01  | 0.34/0.01  | 0.51/0.01 | 0.22/-0.10 | ns      |

| Combinatorial                            |                                           |            |            |           |            |         |

| T <sub>ODQ</sub>                         | D1 to OQ out or T1 to TQ out              | 0.83       | 0.96       | 1.16      | 1.36       | ns      |

| Sequential Delays                        |                                           |            | *          |           | *          |         |

| T <sub>OCKQ</sub>                        | CLK to OQ/TQ out                          | 0.47       | 0.49       | 0.56      | 0.63       | ns      |

| T <sub>RQ_OLOGIC</sub>                   | SR pin to OQ/TQ out                       | 0.72       | 0.80       | 0.95      | 1.12       | ns      |

| T <sub>GSRQ_OLOGIC</sub>                 | Global set/reset to Q outputs             | 7.60       | 7.60       | 10.51     | 11.39      | ns      |

| Set/Reset                                |                                           | ,<br>,     |            |           |            |         |

| T <sub>RPW_OLOGIC</sub>                  | Minimum pulse width, SR inputs            | 0.64       | 0.74       | 0.74      | 0.68       | ns, Min |

## **Output Serializer/Deserializer Switching Characteristics**

Table 21: OSERDES Switching Characteristics

|                                                                                                       |                                               |            | Speed      | Grade      |            |       |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------|------------|------------|------------|-------|

| Symbol                                                                                                | Description                                   |            | 1.0V       |            | 0.9V       | Units |

|                                                                                                       |                                               | -3         | -2/-2L     | -1         | -2L        |       |

| Setup/Hold                                                                                            |                                               |            |            |            |            | •     |

| T <sub>OSDCK_D</sub> /T <sub>OSCKD_D</sub>                                                            | D input setup/hold with respect to CLKDIV     | 0.42/0.03  | 0.45/0.03  | 0.63/0.03  | 0.44/-0.25 | ns    |

| T <sub>OSDCK_T</sub> /T <sub>OSCKD_T</sub> <sup>(1)</sup> T input setup/hold with respect to CLK      |                                               | 0.69/0.13  | 0.73/-0.13 | 0.88/-0.13 | 0.60/-0.25 | ns    |

| T <sub>OSDCK_T2</sub> /T <sub>OSCKD_T2</sub> <sup>(1)</sup> T input setup/hold with respect to CLKDIV |                                               | 0.31/-0.13 | 0.34/-0.13 | 0.39/0.13  | 0.46/-0.25 | ns    |

| T <sub>OSCCK_OCE</sub> /T <sub>OSCKC_OCE</sub>                                                        | OCE input setup/hold with respect to CLK      | 0.32/0.58  | 0.34/0.58  | 0.51/0.58  | 0.21/-0.15 | ns    |

| T <sub>OSCCK_S</sub>                                                                                  | SR (reset) input setup with respect to CLKDIV | 0.47       | 0.52       | 0.85       | 0.70       | ns    |

| T <sub>OSCCK_TCE</sub> /T <sub>OSCKC_TCE</sub>                                                        | TCE input setup/hold with respect to CLK      | 0.32/0.01  | 0.34/0.01  | 0.51/0.01  | 0.22/-0.15 | ns    |

| Sequential Delays                                                                                     |                                               | 1          | 1          | 1          | 1          | 1     |

| T <sub>OSCKO_OQ</sub>                                                                                 | Clock to out from CLK to OQ                   | 0.40       | 0.42       | 0.48       | 0.54       | ns    |

| T <sub>OSCKO_TQ</sub>                                                                                 | Clock to out from CLK to TQ                   | 0.47       | 0.49       | 0.56       | 0.63       | ns    |

| Combinatorial                                                                                         |                                               | 1          | 1          | 1          | 1          | 1     |

| T <sub>OSDO_TTQ</sub>                                                                                 | T input to TQ Out                             | 0.83       | 0.92       | 1.11       | 1.18       | ns    |

<sup>1.</sup>  $T_{OSDCK\_T2}$  and  $T_{OSCKD\_T2}$  are reported as  $T_{OSDCK\_T}/T_{OSCKD\_T}$  in TRACE report.

## **Input/Output Delay Switching Characteristics**

Table 22: Input/Output Delay Switching Characteristics

|                                                 |                                                                                                 |                                | Speed     | Grade     |           |               |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|-----------|-----------|-----------|---------------|

| Symbol                                          | Description                                                                                     |                                | 1.0V      |           | 0.9V      | Units         |

|                                                 |                                                                                                 | -3                             | -2/-2L    | -1        | -2L       |               |

| IDELAYCTRL                                      |                                                                                                 |                                |           |           |           |               |

| T <sub>DLYCCO_RDY</sub>                         | Reset to ready for IDELAYCTRL                                                                   | 3.67                           | 3.67      | 3.67      | 3.22      | μs            |

| F <sub>IDELAYCTRL_REF</sub>                     | Attribute REFCLK frequency = 200.00 <sup>(1)</sup>                                              | 200.00                         | 200.00    | 200.00    | 200.00    | MHz           |

|                                                 | Attribute REFCLK frequency = 300.00 <sup>(1)</sup>                                              | 300.00                         | 300.00    | N/A       | N/A       | MHz           |

| IDELAYCTRL_REF_PRECISION                        | REFCLK precision                                                                                | ±10                            | ±10       | ±10       | ±10       | MHz           |

| T <sub>IDELAYCTRL_RPW</sub>                     | PW Minimum Reset pulse width 59.28 59.28 59.28 52.00                                            |                                | ns        |           |           |               |

| IDELAY                                          |                                                                                                 |                                |           |           |           |               |

| T <sub>IDELAYRESOLUTION</sub>                   | IDELAY chain delay resolution                                                                   | 1/(32 x 2 x F <sub>REF</sub> ) |           |           |           | ps            |

|                                                 | Pattern dependent period jitter in delay chain for clock pattern. (2)                           | 0                              | 0         | 0         | 0         | ps<br>per tap |

| T <sub>IDELAYPAT_JIT</sub>                      | Pattern dependent period jitter in delay chain for random data pattern (PRBS 23) <sup>(3)</sup> | ±5                             | ±5        | ±5        | ±5        | ps<br>per tap |

|                                                 | Pattern dependent period jitter in delay chain for random data pattern (PRBS 23) <sup>(4)</sup> | ±9                             | ±9        | ±9        | ±9        | ps<br>per tap |

| T <sub>IDELAY_CLK_MAX</sub>                     | Maximum frequency of CLK input to IDELAY                                                        | 680.00                         | 680.00    | 600.00    | 520.00    | MHz           |

| T <sub>IDCCK_CE</sub> / T <sub>IDCKC_CE</sub>   | CE pin setup/hold with respect to C for IDELAY                                                  | 0.12/0.11                      | 0.16/0.13 | 0.21/0.16 | 0.14/0.16 | ns            |

| TIDCCK_INC/ TIDCKC_INC                          | INC pin setup/hold with respect to C for IDELAY                                                 | 0.12/0.16                      | 0.14/0.18 | 0.16/0.22 | 0.10/0.23 | ns            |

| T <sub>IDCCK_RST</sub> / T <sub>IDCKC_RST</sub> | RST pin setup/hold with respect to C for IDELAY                                                 | 0.15/0.09                      | 0.16/0.11 | 0.18/0.14 | 0.22/0.19 | ns            |

| T <sub>IDDO_IDATAIN</sub>                       | Propagation delay through IDELAY                                                                | Note 5                         | Note 5    | Note 5    | Note 5    | ps            |

- 1. Average Tap Delay at 200 MHz = 78 ps, at 300 MHz = 52 ps.

- 2. When HIGH\_PERFORMANCE mode is set to TRUE or FALSE.

- 3. When HIGH\_PERFORMANCE mode is set to TRUE.

- 4. When HIGH\_PERFORMANCE mode is set to FALSE.

- 5. Delay depends on IDELAY tap setting. See TRACE report for actual values.

## **CLB Switching Characteristics**

Table 24: CLB Switching Characteristics

|                                                  |                                                                                |           | Speed     | Grade     |            |         |

|--------------------------------------------------|--------------------------------------------------------------------------------|-----------|-----------|-----------|------------|---------|

| Symbol                                           | Description                                                                    |           | 1.0V      |           | 0.9V       | Units   |

|                                                  |                                                                                | -3        | -2/-2L    | -1        | -2L        |         |

| Combinatorial De                                 | lays                                                                           |           |           |           |            |         |

| T <sub>ILO</sub>                                 | An – Dn LUT address to A                                                       | 0.10      | 0.11      | 0.13      | 0.15       | ns, Max |

| T <sub>ILO_2</sub>                               | An – Dn LUT address to AMUX/CMUX                                               | 0.27      | 0.30      | 0.36      | 0.41       | ns, Max |

| T <sub>ILO_3</sub>                               | An – Dn LUT address to BMUX_A                                                  | 0.42      | 0.46      | 0.55      | 0.65       | ns, Max |

| T <sub>ITO</sub>                                 | An – Dn inputs to A – D Q outputs                                              | 0.94      | 1.05      | 1.27      | 1.51       | ns, Max |

| T <sub>AXA</sub>                                 | AX inputs to AMUX output                                                       | 0.62      | 0.69      | 0.84      | 1.01       | ns, Max |

| T <sub>AXB</sub>                                 | AX inputs to BMUX output                                                       | 0.58      | 0.66      | 0.83      | 0.98       | ns, Max |

| T <sub>AXC</sub>                                 | AX inputs to CMUX output                                                       | 0.60      | 0.68      | 0.82      | 0.98       | ns, Max |

| T <sub>AXD</sub>                                 | AX inputs to DMUX output                                                       | 0.68      | 0.75      | 0.90      | 1.08       | ns, Max |

| T <sub>BXB</sub>                                 | BX inputs to BMUX output                                                       | 0.51      | 0.57      | 0.69      | 0.82       | ns, Max |

| T <sub>BXD</sub>                                 | BX inputs to DMUX output                                                       | 0.62      | 0.69      | 0.82      | 0.99       | ns, Max |

| T <sub>CXC</sub>                                 | CX inputs to CMUX output                                                       | 0.42      | 0.48      | 0.58      | 0.69       | ns, Max |

| T <sub>CXD</sub>                                 | CX inputs to DMUX output                                                       | 0.53      | 0.59      | 0.71      | 0.86       | ns, Max |

| T <sub>DXD</sub>                                 | DX inputs to DMUX output                                                       | 0.52      | 0.58      | 0.70      | 0.84       | ns, Max |

| Sequential Delays                                | B                                                                              | 1         | 1         | 1         | 1          |         |

| T <sub>CKO</sub>                                 | Clock to AQ – DQ outputs                                                       | 0.40      | 0.44      | 0.53      | 0.62       | ns, Max |

| T <sub>SHCKO</sub>                               | Clock to AMUX – DMUX outputs                                                   | 0.47      | 0.53      | 0.66      | 0.73       | ns, Max |

| Setup and Hold T                                 | imes of CLB Flip-Flops Before/After Clock CLK                                  | 1         | 1         | 1         | 1          |         |

| T <sub>AS</sub> /T <sub>AH</sub>                 | A <sub>N</sub> – D <sub>N</sub> input to CLK on A – D flip-flops               | 0.07/0.12 | 0.09/0.14 | 0.11/0.18 | 0.11/0.20  | ns, Min |

| T <sub>DICK</sub> /T <sub>CKDI</sub>             | A <sub>X</sub> – D <sub>X</sub> input to CLK on A – D flip-flops               | 0.06/0.19 | 0.07/0.21 | 0.09/0.26 | 0.09/0.31  | ns, Min |

|                                                  | $A_X - D_X$ input through MUXs and/or carry logic to CLK on $A - D$ flip-flops | 0.59/0.08 | 0.66/0.09 | 0.81/0.11 | 0.97/0.12  | ns, Min |

| T <sub>CECK_CLB</sub> /<br>T <sub>CKCE_CLB</sub> | CE input to CLK on A – D flip-flops                                            | 0.15/0.00 | 0.17/0.00 | 0.21/0.01 | 0.34/-0.01 | ns, Min |

| T <sub>SRCK</sub> /T <sub>CKSR</sub>             | SR input to CLK on A - D flip-flops                                            | 0.38/0.03 | 0.43/0.04 | 0.53/0.05 | 0.62/0.05  | ns, Min |

| Set/Reset                                        |                                                                                | ı         | ı         | ı         | l .        |         |

| T <sub>SRMIN</sub>                               | SR input minimum pulse width                                                   | 0.52      | 0.78      | 1.04      | 0.95       | ns, Min |

| T <sub>RQ</sub>                                  | Delay from SR input to AQ - DQ flip-flops                                      | 0.53      | 0.59      | 0.71      | 0.83       | ns, Max |

| T <sub>CEO</sub>                                 | Delay from CE input to AQ – DQ flip-flops                                      | 0.52      | 0.58      | 0.70      | 0.83       | ns, Max |

| F <sub>TOG</sub>                                 | Toggle frequency (for export control)                                          | 1412      | 1286      | 1098      | 1098       | MHz     |

Table 27: Block RAM and FIFO Switching Characteristics (Cont'd)

|                                                    |                                                                                                                                          |            | Speed      | Grade      |            |         |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|------------|---------|--|

| Symbol                                             | Description                                                                                                                              |            | 1.0V       |            | 0.9V       | Units   |  |

|                                                    |                                                                                                                                          | -3         | -2/-2L     | -1         | -2L        |         |  |

| T <sub>RCCK_RSTRAM</sub> /T <sub>RCKC_RSTRAM</sub> | Synchronous RSTRAM input                                                                                                                 | 0.32/0.42  | 0.34/0.43  | 0.36/0.46  | 0.40/0.47  | ns, Min |  |

| T <sub>RCCK_WEA</sub> /T <sub>RCKC_WEA</sub>       | Write enable (WE) input (block RAM only)                                                                                                 | 0.44/0.18  | 0.48/0.19  | 0.54/0.20  | 0.64/0.23  | ns, Min |  |

| T <sub>RCCK_WREN</sub> /T <sub>RCKC_WREN</sub>     | WREN FIFO inputs                                                                                                                         | 0.46/0.30  | 0.46/0.35  | 0.47/0.43  | 0.77/0.44  | ns, Min |  |

| T <sub>RCCK_RDEN</sub> /T <sub>RCKC_RDEN</sub>     | RDEN FIFO inputs                                                                                                                         | 0.42/0.30  | 0.43/0.35  | 0.43/0.43  | 0.71/0.44  | ns, Min |  |

| Reset Delays                                       |                                                                                                                                          | 1          |            | !          |            |         |  |

| T <sub>RCO_FLAGS</sub>                             | Reset RST to FIFO flags/pointers <sup>(10)</sup>                                                                                         | 0.90       | 0.98       | 1.10       | 1.25       | ns, Max |  |

| T <sub>RREC_RST</sub> /T <sub>RREM_RST</sub>       | FIFO reset recovery and removal timing <sup>(11)</sup>                                                                                   | 1.87/-0.81 | 2.07/–0.81 | 2.37/–0.81 | 2.44/-0.71 | ns, Max |  |

| Maximum Frequency                                  |                                                                                                                                          | 1          |            |            | 1          |         |  |

| F <sub>MAX_BRAM_WF_NC</sub>                        | Block RAM (write first and no change modes) when not in SDP RF mode                                                                      | 509.68     | 460.83     | 388.20     | 315.66     | MHz     |  |

| F <sub>MAX_BRAM_RF_PERFORMANCE</sub>               | Block RAM (read first, performance<br>mode) when in SDP RF mode but no<br>address overlap between port A and<br>port B                   | 509.68     | 460.83     | 388.20     | 315.66     | MHz     |  |

| F <sub>MAX_BRAM_RF_DELAYED_WRITE</sub>             | Block RAM (read first, delayed write mode) when in SDP RF mode and there is possibility of overlap between port A and port B addresses   | 447.63     | 404.53     | 339.67     | 268.96     | MHz     |  |