Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15356-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                | Function              | Input<br>Type    | Output Type | Description                                                                                      |  |  |

|-----------------------------------------------------|-----------------------|------------------|-------------|--------------------------------------------------------------------------------------------------|--|--|

| RD1/AND1/SDA2 <sup>(1)</sup> /SDI2 <sup>(1,4)</sup> | RD1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND1                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

|                                                     | SDA2 <sup>(1)</sup>   | l <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C serial data input/output.                                                 |  |  |

|                                                     | SDI2 <sup>(1,4)</sup> | TTL/ST           | _           | MSSP2 SPI serial data input (default input location, SDI2 is a PPS remappable input and output). |  |  |

| RD2/AND2                                            | RD2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND2                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD3/AND3                                            | RD3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND3                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD4/AND4                                            | RD4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND4                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD5/AND5                                            | RD5                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND5                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD6/AND6                                            | RD6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND6                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD7/AND7                                            | RD7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND7                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE0/ANE0                                            | RE0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANE0                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE1/ANE1                                            | RE1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANE1                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE2/ANE2                                            | RE2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANE2                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE3/MCLR/IOCE3                                      | RE3                   | TTL/ST           | -           | General purpose input only (when $\overline{\text{MCLR}}$ is disabled by the Configuration bit). |  |  |

|                                                     | MCLR                  | ST               | _           | Master clear input with internal weak pull-up resistor.                                          |  |  |

|                                                     | IOCE3                 | TTL/ST           | _           | Interrupt-on-change input.                                                                       |  |  |

| RF0/ANF0                                            | RF0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF0                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RF1/ANF1                                            | RF1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF1                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RF2/ANF2                                            | RF2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF2                  | AN               | —           | ADC Channel D0 input.                                                                            |  |  |

| RF3/ANF3                                            | RF3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF3                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RF4/ANF4                                            | RF4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF4                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

HV = High Voltage

XTAL

Note

= Crystal levels This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal. 1:

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options 2: as described in Table 15-5, Table 15-6 and Table 15-7.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| Address | Name    | Bit 7  | Bit 6       | Bit 5             | Bit 4        | Bit 3             | Bit 2     | Bit 1                 | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|---------|--------|-------------|-------------------|--------------|-------------------|-----------|-----------------------|---------|-----------------------|----------------------------|

| Bank 16 |         |        |             |                   |              |                   |           |                       |         |                       |                            |

|         |         |        |             | CPULCOR           | E REGISTERS. | see Table 4-3 for | specifics |                       |         |                       |                            |

|         |         | •      |             |                   |              |                   | opeeniee  |                       |         |                       |                            |

| 80Ch    | WDTCON0 | —      | —           | WDTPS<4:0> SWDTEN |              |                   |           |                       |         |                       | dd dddo                    |

| 80Dh    | WDTCON1 | -      |             | WDTCS<2:0>        |              | —                 |           | WINDOW<2:0            | )>      | -ववव -ववव             | -वेवेवे -वेवेवे            |

| 80Eh    | WDTPSL  |        |             |                   | PSCNT        | <7:0>             |           |                       |         | 0000 0000             | 0000 0000                  |

| 80Fh    | WDTPSH  |        | PSCNT<15:8> |                   |              |                   |           |                       |         | 0000 0000             | 0000 0000                  |

| 810h    | WDTTMR  | —      |             | WDTTM             | R<3:0>       |                   | STATE     | PSCNT17               | PSCNT16 | xxxx x000             | xxxx x000                  |

| 811h    | BORCON  | SBOREN | _           | -                 | -            | —                 | —         | _                     | BORRDY  | 1 q                   | uı                         |

| 812h    | VREGCON | —      | —           |                   | _            | —                 |           | VREGPM <sup>(1)</sup> | _       | 0-                    | 0-                         |

| 813h    | PCON0   | STKOVF | STKUNF      | WDTWV             | RWDT         | RMCLR             | RI        | POR                   | BOR     | 0011 110q             | वववव ववपा                  |

| 814h    | PCON1   | —      | _           |                   |              | _                 |           | MEMV                  |         | 1-                    | u-                         |

| 815h    | —       |        |             |                   | Unimpler     | nented            |           |                       |         | —                     |                            |

| 816h    | —       |        |             |                   | Unimpler     | mented            |           |                       |         | —                     | -                          |

| 817h    | —       |        |             |                   | Unimpler     | mented            |           |                       |         | —                     | -                          |

| 818h    | —       |        |             |                   | Unimpler     | mented            |           |                       |         | —                     | —                          |

| 819h    | —       |        |             |                   | Unimpler     | mented            |           |                       |         | —                     | —                          |

| 81Ah    | NVMADRL |        |             |                   | NVMAD        | R<7:0>            |           |                       |         | xxxx xxxx             | սսսս սսսս                  |

| 81Bh    | NVMADRH | —      |             |                   |              | NVMADR<14:8       | >         |                       |         | -xxx xxxx             | -uuu uuuu                  |

| 81Ch    | NVMDATL |        |             |                   | NVMDA        | Γ<7:0>            |           |                       |         | 0000 0000             | 0000 0000                  |

| 81Dh    | NVMDATH | _      | _           |                   |              | NVMD              | AT<13:8>  |                       |         | 00 0000               | 00 0000                    |

| 81Eh    | NVMCON1 | _      | NVMREGS     | LWLO              | FREE         | WRERR             | WREN      | WR                    | RD      | -000 x000             | -000 q000                  |

| 81Fh    | NVMCON2 |        |             |                   | NVMCON       | 2<7:0>            |           |                       |         | XXXX XXXX             | սսսս սսսս                  |

####

x = unknown, u = unchanged, g = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

Note 1: Present only on PIC16F15356/75/76/85/86.

### 5.0 DEVICE CONFIGURATION

Device configuration consists of the Configuration Words, User ID, Device ID, Device Information Area (DIA), (see Section 6.0 "Device Information Area"), and the Device Configuration Information (DCI) regions, (see Section 7.0 "Device Configuration Information").

### 5.1 Configuration Words

The devices have several Configuration Words starting at address 8007h. The Configuration bits establish configuration values prior to the execution of any software; Configuration bits enable or disable device-specific features.

In terms of programming, these important Configuration bits should be considered:

#### 1. LVP: Low-Voltage Programming Enable bit

- <u>1</u> = ON Low-Voltage Programming is enabled. MCLR/VPP pin function is MCLR. MCLRE Configuration bit is ignored.

- 0 = OFF HV on MCLR/VPP must be used for programming.

- 2. CP: User Nonvolatile Memory (NVM) Program Memory Code Protection bit

- 1 = OFF User NVM code protection disabled

- 0 = ON User NVM code protection enabled

#### **REGISTER 9-7: OSCTUNE: HFINTOSC TUNING REGISTER**

| U-0   | U-0 | R/W-1/1 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|-----|---------|------------|---------|---------|---------|---------|--|

| —     | —   |         | HFTUN<5:0> |         |         |         |         |  |

| bit 7 |     |         |            |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 <b>U</b> | nimplemented: Read as '0'.                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01               | FTUN<5:0>: HFINTOSC Frequency Tuning bits 1 1111 = Maximum frequency 1 1110 =                                                                                                                                       |

|                  | <ul> <li>0 0001 =</li> <li>0 0000 = Center frequency. Oscillator module is running at the calibrated frequency (default value).</li> <li>1 1111 =</li> <li>0 0001 =</li> <li>0 0000 = Minimum frequency.</li> </ul> |

### REGISTER 10-14: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| _     | _   |     |     | _   | _   | TMR2IF     | TMR1IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7-2<br>bit 1 | Unimplemented: Read as '0'<br>TRM2IF: Timer2 Interrupt Flag bit<br>1 = The TMR2 postscaler overflowed, or in 1:1 mode, a TMR2 to PR2 match occurred (must be cleared<br>in software)<br>0 = No TMR2 event has occurred |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0            | <b>TRM1IF:</b> Timer1 Overflow Interrupt Flag bit<br>1 = Timer1 overflow occurred (must be cleared in software)<br>0 = No Timer1 overflow occurred                                                                     |

| Note:            | Interrupt flag bits are set when an interrupt                                                                                                                                                                          |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

© 2016 Microchip Technology Inc.

|                  |                                                                     |                                    |                 | INEQUED        |                  |                |              |  |

|------------------|---------------------------------------------------------------------|------------------------------------|-----------------|----------------|------------------|----------------|--------------|--|

| R/W/HS-0/0       | R/W/HS-0/0                                                          | R/W/HS-0/0                         | R/W/HS-0/0      | U-0            | U-0              | U-0            | R/W/HS-0/0   |  |

| CLC4IF           | CLC3IF                                                              | CLC2IF                             | CLC1IF          | —              |                  | —              | TMR1GIF      |  |

| bit 7            |                                                                     |                                    |                 |                |                  |                | bit 0        |  |

|                  |                                                                     |                                    |                 |                |                  |                |              |  |

| Legend:          |                                                                     |                                    |                 |                |                  |                |              |  |

| R = Readable     | bit                                                                 | W = Writable                       | bit             | U = Unimpler   | mented bit, read | as '0'         |              |  |

| u = Bit is uncha | anged                                                               | x = Bit is unkr                    | iown            | -n/n = Value a | at POR and BOI   | R/Value at all | other Resets |  |

| '1' = Bit is set |                                                                     | '0' = Bit is clea                  | ared            | HS = Hardwa    | are set          |                |              |  |

|                  |                                                                     |                                    |                 |                |                  |                |              |  |

| bit 7            | CLC4IF: CLC                                                         | 4 Interrupt Flag                   | g bit           |                |                  |                |              |  |

|                  |                                                                     |                                    |                 | curred (must l | be cleared in so | ftware)        |              |  |

|                  | 0 = No CLC4                                                         | interrupt event                    | has occurred    |                |                  |                |              |  |

| bit 6            | CLC3IF: CLC                                                         | 3 Interrupt Flag                   | g bit           |                |                  |                |              |  |

|                  |                                                                     |                                    |                 | curred (must b | be cleared in so | ftware)        |              |  |

|                  | 0 = No CLC3                                                         | interrupt event                    | has occurred    |                |                  |                |              |  |

| bit 5            | CLC2IF: CLC                                                         | 2 Interrupt Flag                   | g bit           |                |                  |                |              |  |

|                  |                                                                     | UT interrupt co<br>interrupt event |                 | curred (must b | be cleared in so | ftware)        |              |  |

| bit 4            |                                                                     | 1 Interrupt Flag                   |                 |                |                  |                |              |  |

|                  |                                                                     |                                    | 5               | curred (must l | be cleared in so | ftware)        |              |  |

|                  | 0 = No CLC1                                                         | interrupt event                    | has occurred    |                |                  | ,              |              |  |

| bit 3-1          | Unimplemen                                                          | ted: Read as '                     | כ'              |                |                  |                |              |  |

| bit 0            | TMR1GIF: Tir                                                        | mer1 Gate Inte                     | rrupt Flag bit  |                |                  |                |              |  |

|                  | 1 = The Timer1 Gate has gone inactive (the acquisition is complete) |                                    |                 |                |                  |                |              |  |

|                  | 0 = The Time                                                        | r1 Gate has no                     | t gone inactive | 9              |                  |                |              |  |

|                  |                                                                     |                                    |                 |                |                  |                |              |  |

| Note: Inte       | errupt flag bits a                                                  | re set when an                     | interrupt       |                |                  |                |              |  |

|                  | aprillag bito u                                                     |                                    | apt             |                |                  |                |              |  |

#### REGISTER 10-15: PIR5: PERIPHERAL INTERRUPT REQUEST REGISTER 5

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |  |

### REGISTER 14-37: WPUE: WEAK PULL-UP PORTE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1/1              | R/W-1/1              | R/W-1/1              | R/W-1/1              |

|-------|-----|-----|-----|----------------------|----------------------|----------------------|----------------------|

| —     | —   | _   | —   | WPUE3 <sup>(2)</sup> | WPUE2 <sup>(1)</sup> | WPUE1 <sup>(1)</sup> | WPUE0 <sup>(1)</sup> |

| bit 7 | •   |     |     |                      |                      |                      | bit 0                |

|       |     |     |     |                      |                      |                      |                      |

### Legend:

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 3-0 | WPUE<3:0>: Weak Pull-up Register bits |

|---------|---------------------------------------|

|         | 1 = Pull-up enabled                   |

|         | 0 = Pull-up disabled                  |

Note 1: Present on PIC16(L)F15375/76/85/86 only.

- 2: If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

- 3: The weak pull-up device is automatically disabled if the pin is configured as an output.

### REGISTER 14-38: ODCONE: PORTE OPEN-DRAIN CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

|       |     | —   | _   | —   | ODCE2   | ODCE1   | ODCE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0' bit 3-0 ODCE<3:0>: PORTE Open-Drain Enable bits For RE<3:0> pins, respectively 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

Note 1: Present on PIC16(L)F15375/76/85/86 only.

| REGISTER                      | 16-6: PMD5                                          | 5 – PMD CON      | ITROL REGI | STER 5         |                  |                  |             |

|-------------------------------|-----------------------------------------------------|------------------|------------|----------------|------------------|------------------|-------------|

| U-0                           | U-0                                                 | U-0              | R/W-0/0    | R/W-0/0        | R/W-0/0          | R/W-0/0          | U-0         |

| —                             | —                                                   | —                | CLC4MD     | CLC3MD         | CLC2MD           | CLC1MD           | —           |

| bit 7                         |                                                     |                  |            |                |                  |                  | bit 0       |

|                               |                                                     |                  |            |                |                  |                  |             |

| Legend:                       |                                                     |                  |            |                |                  |                  |             |

| R = Readabl                   | e bit                                               | W = Writable     | bit        | U = Unimplem   | nented bit, read | l as '0'         |             |

| u = Bit is und                | changed                                             | x = Bit is unkr  | nown       | -n/n = Value a | t POR and BO     | R/Value at all o | ther Resets |

| '1' = Bit is se               | t                                                   | '0' = Bit is cle | ared       | q = Value dep  | ends on condit   | ion              |             |

|                               |                                                     |                  |            |                |                  |                  |             |

| bit 7-5                       | Unimplemen                                          | ted: Read as '   | D'         |                |                  |                  |             |

| bit 4                         | CLC4MD: Dis                                         | able CLC4 bit    |            |                |                  |                  |             |

|                               | 1 = CLC4 mc                                         | dule disabled    |            |                |                  |                  |             |

|                               | 0 = CLC4 mc                                         | dule enabled     |            |                |                  |                  |             |

| bit 3                         | CLC3MD: Dis                                         | able CLC3 bit    |            |                |                  |                  |             |

|                               | 1 = CLC3 mc                                         |                  |            |                |                  |                  |             |

|                               | 0 = CLC3 mc                                         | dule enabled     |            |                |                  |                  |             |

| bit 2                         | CLC2MD: Dis                                         | able CLC2 bit    |            |                |                  |                  |             |

|                               | 1 = CLC2 module disabled                            |                  |            |                |                  |                  |             |

|                               | 0 = CLC2 module enabled                             |                  |            |                |                  |                  |             |

| bit 1 CLC1MD: Disable CLC bit |                                                     |                  |            |                |                  |                  |             |

|                               | 1 = CLC1 module disabled<br>0 = CLC1 module enabled |                  |            |                |                  |                  |             |

|                               |                                                     |                  | <u>.</u>   |                |                  |                  |             |

| bit 0                         | Unimplemen                                          | ted: Read as '   | J          |                |                  |                  |             |

| Name     | Bit 7 | Bit 6                   | Bit 5 | Bit 4    | Bit 3 | Bit 2      | Bit 1    | Bit 0  | Register<br>on Page |

|----------|-------|-------------------------|-------|----------|-------|------------|----------|--------|---------------------|

| INTCON   | GIE   | PEIE                    | —     | —        | _     | —          | —        | INTEDG | 146                 |

| PIR7     | _     | —                       | NVMIF | NCO1IF   | _     | _          | _        | CWG1IF | 162                 |

| PIE7     | —     | —                       | NVMIE | NCO1IE   |       | —          | —        | CWG1IE | 154                 |

| NCO1CON  | N1EN  | _                       | N1OUT | N1POL    | _     | —          | _        | N1PFM  | 294                 |

| NCO1CLK  |       | N1PWS<2:0> — N1CKS<3:0> |       |          |       |            |          |        |                     |

| NCO1ACCL |       |                         |       | NCO1ACC< | :7:0> |            |          |        | 296                 |

| NCO1ACCH |       |                         |       | NCO1ACC< | 15:8> |            |          |        | 296                 |

| NCO1ACCU | —     | _                       | —     | —        | 296   |            |          |        |                     |

| NCO1INCL |       |                         |       | NCO1INC< | 7:0>  |            |          |        | 297                 |

| NCO1INCH |       |                         |       | NCO1INC< | 15:8> |            |          |        | 297                 |

| NCO1INCU | —     | —                       | —     | —        |       | NCO1AINC   | 2<19:16> |        | 297                 |

| RxyPPS   | _     | _                       | _     |          | R     | xyPPS<4:0> |          |        | 242                 |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCO

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for NCO module.

### 24.9 Register Definitions: ZCD Control

### REGISTER 24-1: ZCDCON: ZERO-CROSS DETECTION CONTROL REGISTER

| R/W-q/q                                                                                                                                                                                                                                                            | U-0                                                                                                                                                       | R-x/x                                                                                     | R/W-0/0        | U-0                               | U-0             | R/W-0/0           | R/W-0/0      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|-----------------------------------|-----------------|-------------------|--------------|--|

| SEN                                                                                                                                                                                                                                                                | —                                                                                                                                                         | OUT                                                                                       | POL            | —                                 | _               | INTP              | INTN         |  |

| bit 7                                                                                                                                                                                                                                                              |                                                                                                                                                           |                                                                                           |                |                                   |                 |                   |              |  |

|                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                                           |                |                                   |                 |                   |              |  |

| Legend:                                                                                                                                                                                                                                                            |                                                                                                                                                           |                                                                                           |                |                                   |                 |                   |              |  |

| R = Readable                                                                                                                                                                                                                                                       | bit                                                                                                                                                       | W = Writable                                                                              | bit            | U = Unimpler                      | nented bit, rea | d as '0'          |              |  |

| u = Bit is unch                                                                                                                                                                                                                                                    | anged                                                                                                                                                     | x = Bit is unk                                                                            | nown           | -n/n = Value a                    | at POR and BC   | OR/Value at all o | other Resets |  |

| '1' = Bit is set                                                                                                                                                                                                                                                   |                                                                                                                                                           | '0' = Bit is cle                                                                          | ared           | q = value dep                     | ends on Confi   | guration bits     |              |  |

| <ul> <li>bit 7 SEN: Zero-Cross Detection Enable bit</li> <li>1 = Zero-cross detect is enabled. ZCD pin is forced to output to source and sink current.</li> <li>0 = Zero-cross detect is disabled. ZCD pin operates according to PPS and TRIS controls.</li> </ul> |                                                                                                                                                           |                                                                                           |                |                                   |                 |                   |              |  |

| bit 6                                                                                                                                                                                                                                                              | Unimplemer                                                                                                                                                | ted: Read as                                                                              | ʻ0'            |                                   |                 |                   |              |  |

| bit 5                                                                                                                                                                                                                                                              | POL bit = 1:<br>1 = ZCD pin<br>0 = ZCD pin<br>POL bit = 0:<br>1 = ZCD pin                                                                                 | ross Detection<br>is sourcing cur<br>is sinking curr<br>is sinking curr<br>is sourcing cu | rrent<br>ent   | it                                |                 |                   |              |  |

| bit 4                                                                                                                                                                                                                                                              | 1 = ZCD log                                                                                                                                               | ross Detection<br>ic output is inve<br>ic output is not                                   | erted          | Polarity bit                      |                 |                   |              |  |

| bit 3-2                                                                                                                                                                                                                                                            | Unimplemer                                                                                                                                                | ted: Read as                                                                              | ʻ0'            |                                   |                 |                   |              |  |

| bit 1                                                                                                                                                                                                                                                              | INTP: Zero-C                                                                                                                                              | Cross Positive I                                                                          | Edge Interrupt | Enable bit                        |                 |                   |              |  |

|                                                                                                                                                                                                                                                                    | <ul> <li>1 = ZCDIF bit is set on low-to-high ZCDx_output transition</li> <li>0 = ZCDIF bit is unaffected by low-to-high ZCDx_output transition</li> </ul> |                                                                                           |                |                                   |                 |                   |              |  |

| bit 0                                                                                                                                                                                                                                                              | INTN: Zero-C                                                                                                                                              | Cross Negative                                                                            | Edge Interrup  | ot Enable bit                     |                 |                   |              |  |

|                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                                           |                | _output transiti<br>v ZCDx_output |                 |                   |              |  |

|                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                                           |                |                                   |                 |                   |              |  |

#### TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| PIE3    | RC2IE | TX2IE | RC1IE | TX1IE | BCL2IE | SSP2IE | BCL1IE | SSP1IE | 150                 |

| PIR3    | RC2IF | TX2IF | RC1IF | TX1IF | BCL2IF | SSP2IF | BCL1IF | SSP1IF | 158                 |

| ZCDxCON | EN    | _     | OUT   | POL   |        |        | INTP   | INTN   | 314                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 24-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name       | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|------------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| 0.01/5/0.0 | 13:8 | _       | _       | DEBUG    | STVREN   | PPS1WAY  | ZCDDIS   | BORV    |         | 100                 |

| CONFIG2    | 7:0  | BOREN   | N <1:0> | LPBOREN  |          | —        |          | PWRTE   | MCLRE   | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

| R/W-0/0         | U-0                        | R-0                                                              | R/W-0/0        | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|-----------------|----------------------------|------------------------------------------------------------------|----------------|-------------------|------------------|------------------|--------------|--|--|

| <b>T0EN</b>     | TOEN — TOOUT T016BIT       |                                                                  |                |                   | TOOUTI           | PS<3:0>          |              |  |  |

| bit 7           |                            |                                                                  |                |                   |                  |                  | bit          |  |  |

|                 |                            |                                                                  |                |                   |                  |                  |              |  |  |

| Legend:         |                            |                                                                  |                |                   |                  |                  |              |  |  |

| R = Readable    | e bit                      | W = Writable                                                     | bit            | U = Unimplen      | nented bit, read | l as '0'         |              |  |  |

| u = Bit is unc  | changed                    | x = Bit is unk                                                   | nown           | -n/n = Value a    | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is se | t                          | '0' = Bit is cle                                                 | ared           |                   |                  |                  |              |  |  |

|                 |                            |                                                                  |                |                   |                  |                  |              |  |  |

| bit 7           | TOEN: Time                 | r0 Enable bit                                                    |                |                   |                  |                  |              |  |  |

|                 |                            | dule is enabled                                                  |                |                   |                  |                  |              |  |  |

|                 |                            | dule is disabled                                                 |                | vest power mod    | de               |                  |              |  |  |

| bit 6           | Unimpleme                  | nted: Read as                                                    | 0'             |                   |                  |                  |              |  |  |

| bit 5           |                            | <b>T0OUT:</b> Timer0 Output bit (read-only)<br>Timer0 output bit |                |                   |                  |                  |              |  |  |

| bit 4           | T016BIT: Tir               | mer0 Operating                                                   | as 16-bit Time | er Select bit     |                  |                  |              |  |  |

|                 |                            | is a 16-bit timer                                                |                |                   |                  |                  |              |  |  |

|                 | 0 = Timer0 i               | s an 8-bit timer                                                 |                |                   |                  |                  |              |  |  |

| bit 3-0         | T0OUTPS<                   | <b>3:0&gt;:</b> Timer0 ou                                        | tput postscale | r (divider) seled | ct bits          |                  |              |  |  |

|                 | 1111 = 1:16                |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 1110 = 1:15<br>1101 = 1:14 |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 1101 - 1.14<br>1100 = 1:13 |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 1011 = 1:12                |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 1010 = 1:11                |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 1001 = 1:10                | Postscaler                                                       |                |                   |                  |                  |              |  |  |

|                 | 1000 <b>= 1:9</b>          | Postscaler                                                       |                |                   |                  |                  |              |  |  |

|                 | 0111 <b>= 1:8  </b>        |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 0110 = 1:7                 |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 0101 = 1:6 Postscaler      |                                                                  |                |                   |                  |                  |              |  |  |

|                 |                            | 0100 = 1:5 Postscaler<br>0011 = 1:4 Postscaler                   |                |                   |                  |                  |              |  |  |

|                 | 0011 = 1.41<br>0010 = 1:31 |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 0001 = 1:2                 |                                                                  |                |                   |                  |                  |              |  |  |

|                 | 0000 = 1:1                 |                                                                  |                |                   |                  |                  |              |  |  |

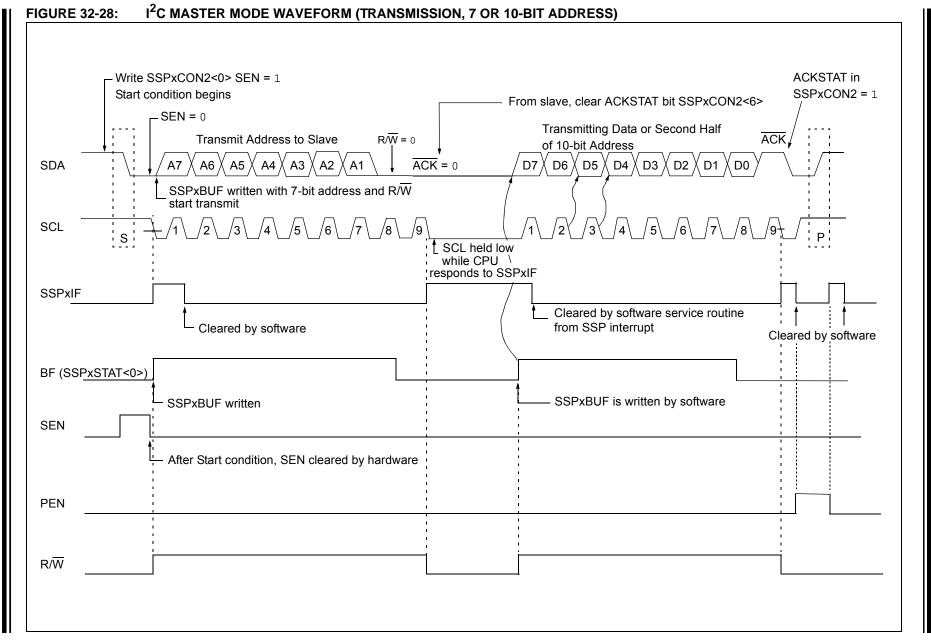

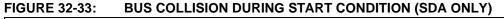

### 32.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 32-33).

- b) SCL is sampled low before SDA is asserted low (Figure 32-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- the BCL1IF flag is set and

- the MSSP module is reset to its Idle state (Figure 32-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 32-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

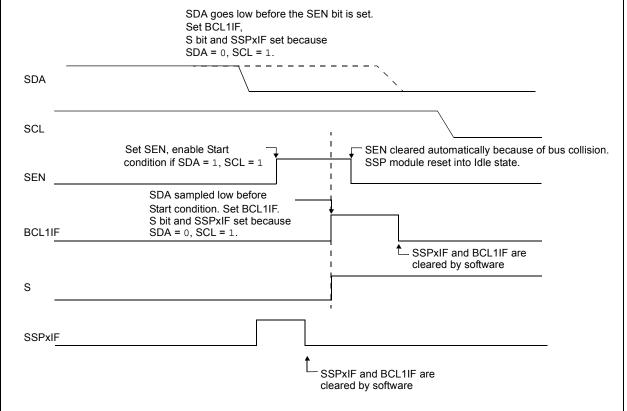

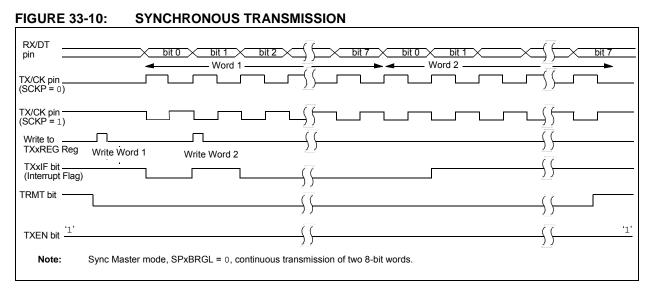

FIGURE 33-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### 33.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCxSTA register) or the Continuous Receive Enable bit (CREN of the RCxSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence. To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RXxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCxREG. The RXxIF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

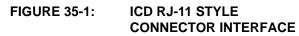

### 35.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16(L)F153XX*Memory Programming Specification*" (DS40001838).

### 35.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

### 35.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'. The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete, MCLR must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the MCLR Reset function is automatically enabled and cannot be disabled. See **Section 8.5"MCLR**" for more information.

### 35.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 35-1.

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 35-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 35-3 for more information.

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

Bit Test f, Skip if Set

instruction is executed.

If bit 'b' in register 'f' is '0', the next

If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle

$0 \le f \le 127$  $0 \le b < 7$ skip if (f<b>) = 1

instruction.

None

| BRA              | Relative Branch                                                    | BTFSS            |

|------------------|--------------------------------------------------------------------|------------------|

| Syntax:          | [ label ] BRA label                                                | Syntax:          |

|                  | [ <i>label</i> ] BRA \$+k                                          | Operands:        |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255                                        |                  |

|                  | $-256 \le k \le 255$                                               | Operation:       |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                      | Status Affected: |

| Status Affected: | None                                                               | Description:     |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have |                  |

|                  | incremented to fetch the next                                      |                  |

|                  | instruction, the new address will be                               |                  |

|                  | PC + 1 + k. This instruction is a                                  |                  |

|                  | 2-cycle instruction. This branch has a                             |                  |

|                  | limited range.                                                     |                  |

#### BRW Relative Branch with W

| Syntax:          | [ <i>label</i> ] BRW                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| RETLW            | Return with literal in W                                                                                                                                                      |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                  |  |  |

| Status Affected: | None                                                                                                                                                                          |  |  |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. |  |  |

| Words:           | 1                                                                                                                                                                             |  |  |

| Cycles:          | 2                                                                                                                                                                             |  |  |

| Example:         | CALL TABLE;W contains table<br>;offset value<br>• ;W now has table value                                                                                                      |  |  |

| TABLE            | •<br>•<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>•<br>RETLW kn ; End of table                                                               |  |  |

|                  | Before Instruction                                                                                                                                                            |  |  |

W =

W =

**Return from Subroutine**

Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a 2-cycle instruction.

After Instruction

[label] RETURN

None

None

$\text{TOS} \rightarrow \text{PC}$

RETURN

Operands:

Operation:

Description:

Status Affected:

Syntax:

0x07

value of k8

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                        |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |

|                  | C = 0                                                                                                                                                                                                             |  |  |  |

|                  | After Instruction                                                                                                                                                                                                 |  |  |  |