#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15356-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name             | Function              | Input<br>Type | Output Type | Description                                        |

|------------------|-----------------------|---------------|-------------|----------------------------------------------------|

| T <sup>(2)</sup> | C1OUT                 | _             | CMOS/OD     | Comparator 1 output.                               |

|                  | C2OUT                 | _             | CMOS/OD     | Comparator 2 output.                               |

|                  | NCO10UT               | _             | CMOS/OD     | Numerically Controller Oscillator output.          |

|                  | TMR0                  | _             | CMOS/OD     | Timer0 output.                                     |

|                  | CCP1                  | _             | CMOS/OD     | Capture/Compare/PWM1 output (compare/PWM functions |

|                  | CCP2                  | _             | CMOS/OD     | Capture/Compare/PWM2 output (compare/PWM functions |

|                  | PWM3OUT               |               | CMOS/OD     | PWM3 output.                                       |

|                  | PWM4OUT               | _             | CMOS/OD     | PWM4 output.                                       |

|                  | PWM5OUT               | _             | CMOS/OD     | PWM5 output.                                       |

|                  | CWG1A                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output A.       |

|                  | CWG1B                 |               | CMOS/OD     | Complementary Waveform Generator 1 output B.       |

|                  | CWG1C                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output C.       |

|                  | CWG1D                 |               | CMOS/OD     | Complementary Waveform Generator 1 output D.       |

|                  | CWG2A                 |               | CMOS/OD     | Complementary Waveform Generator 2 output A.       |

|                  | CWG2B                 |               | CMOS/OD     | Complementary Waveform Generator 2 output B.       |

|                  | CWG2C                 |               | CMOS/OD     | Complementary Waveform Generator 2 output C.       |

|                  | CWG2D                 |               | CMOS/OD     | Complementary Waveform Generator 2 output D.       |

|                  | SDO1                  | -             | CMOS/OD     | MSSP1 SPI serial data output.                      |

|                  | SDO2                  | _             | CMOS/OD     | MSSP2 SPI serial data output.                      |

|                  | SCL1 <sup>(3,4)</sup> |               | CMOS/OD     | MSSP1 SPI serial clock output.                     |

|                  | SCL2 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP2 SPI serial clock output.                     |

|                  | SDA1 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP1 I <sup>2</sup> C serial data input/output.   |

|                  | SDA2 <sup>(3,4)</sup> |               | CMOS/OD     | MSSP2 I <sup>2</sup> C serial data input/output.   |

|                  | DT <sup>(3)</sup>     |               | CMOS/OD     | EUSART Synchronous mode data output.               |

|                  | CK1                   | _             | CMOS/OD     | EUSART1 Synchronous mode clock output.             |

|                  | CK2                   |               | CMOS/OD     | EUSART2 Synchronous mode clock output.             |

|                  | TX1                   | _             | CMOS/OD     | EUSART1 Asynchronous mode transmitter data output. |

|                  | TX2                   |               | CMOS/OD     | EUSART2 Asynchronous mode transmitter data output. |

|                  | CLC1OUT               | _             | CMOS/OD     | Configurable Logic Cell 1 output.                  |

|                  | CLC2OUT               |               | CMOS/OD     | Configurable Logic Cell 2 output.                  |

|                  | CLC3OUT               | _             | CMOS/OD     | Configurable Logic Cell 3 output.                  |

|                  | CLC4OUT               | _             | CMOS/OD     | Configurable Logic Cell 4 output.                  |

|                  | CLKR                  |               | CMOS/OD     | Clock Reference module output.                     |

#### **TABLE 1-3**: PIC16(L)F15375/76 PINOUT DESCRIPTION (CONTINUED)

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage

Note

= Crystal levels XTAL This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options

as described in Table 15-5, Table 15-6 and Table 15-6.

I<sup>2</sup>C

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

= Schmitt Trigger input with I<sup>2</sup>C

#### TABLE 4-4: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANKS 0-7

|      | BANK 0               |      | BANK 1        |      | BANK 2        |      | BANK 3        |      | BANK 4        |      | BANK 5        |      | BANK 6        |      | BANK 7        |

|------|----------------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|

| 000h |                      | 080h |               | 100h |               | 180h |               | 200h |               | 280h |               | 300h |               | 380h |               |

|      | Core Register        |      | Core Register |      | Core Register |      | Core Register |      | Core Register |      | Core Register |      | Core Register |      | Core Register |

|      | (Table 4-3)          |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |

| 00Bh |                      | 08Bh |               | 10Bh |               | 18Bh |               | 20Bh |               | 28Bh |               | 30Bh |               | 38Bh |               |

| 00Ch | PORTA                | 08Ch | —             | 10Ch | —             | 18Ch | SSP1BUF       | 20Ch | TMR1L         | 28Ch | TMR2          | 30Ch | CCPR1L        | 38Ch | PWM6DCL       |

| 00Dh | PORTB                | 08Dh | _             | 10Dh | —             | 18Dh | SSP1ADD       | 20Dh | TMR1H         | 28Dh | PR2           | 30Dh | CCPR1H        | 38Dh | PWM6DCH       |

| 00Eh | PORTC                | 08Eh | —             | 10Eh |               | 18Eh | SSP1MASK      | 20Eh | T1CON         | 28Eh | T2CON         | 30Eh | CCP1CON       | 38Eh | PWM6CON       |

| 00Fh | PORTD <sup>(2)</sup> | 08Fh | —             | 10Fh | —             | 18Fh | SSP1STAT      | 20Fh | T1GCON        | 28Fh | T2HLT         | 30Fh | CCP1CAP       | 38Fh | —             |

| 010h | PORTE                | 090h | —             | 110h | —             | 190h | SSP1CON1      | 210h | T1GATE        | 290h | T2CLK         | 310h | CCPR2L        | 390h | —             |

| 011h | PORTF <sup>(3)</sup> | 091h | —             | 111h | —             | 191h | SSP1CON2      | 211h | T1CLK         | 291h | T2ERS         | 311h | CCPR2H        | 391h | —             |

| 012h | TRISA                | 092h | _             | 112h | _             | 192h | SSP1CON3      | 212h | _             | 292h | _             | 312h | CCP2CON       | 392h | —             |

| 013h | TRISB                | 093h | _             | 113h | _             | 193h | _             | 213h | _             | 293h | _             | 313h | CCP2CAP       | 393h | _             |

| 014h | TRISC                | 094h | —             | 114h | —             | 194h | —             | 214h | —             | 294h | —             | 314h | PWM3DCL       | 394h | —             |

| 015h | TRISD <sup>(2)</sup> | 095h | —             | 115h | —             | 195h | —             | 215h | _             | 295h | _             | 315h | PWM3DCH       | 395h | —             |

| 016h | TRISE                | 096h | —             | 116h | —             | 196h | SSP2BUF       | 216h | —             | 296h | —             | 316h | PWM3CON       | 396h | —             |

| 017h | TRISF <sup>(3)</sup> | 097h | —             | 117h | —             | 197h | SSP2ADD       | 217h | —             | 297h | —             | 317h | —             | 397h | —             |

| 018h | LATA                 | 098h | _             | 118h | _             | 198h | SSP2MASK      | 218h | —             | 298h | —             | 318h | PWM4DCL       | 398h | _             |

| 019h | LATB                 | 099h |               | 119h | RC1REG1       | 199h | SSP2STAT      | 219h |               | 299h | _             | 319h | PWM4DCH       | 399h | —             |

| 01Ah | LATC                 | 09Ah | _             | 11Ah | TX1REG1       | 19Ah | SSP2CON1      | 21Ah |               | 29Ah |               | 31Ah | PWM4CON       | 39Ah | —             |

| 01Bh | LATD <sup>(2)</sup>  | 09Bh | ADRESL        | 11Bh | SP1BRG1L      | 19Bh | SSP2CON2      | 21Bh | —             | 29Bh | —             | 31Bh | —             | 39Bh | —             |

| 01Ch | LATE                 | 09Ch | ADRESH        | 11Ch | SP1BRG1H      | 19Ch | SSP2CON3      | 21Ch |               | 29Ch |               | 31Ch | PWM5DCL       | 39Ch | —             |

| 01Dh | LATF <sup>(3)</sup>  | 09Dh | ADCON0        | 11Dh | RC1STA1       | 19Dh | —             | 21Dh | _             | 29Dh | -             | 31Dh | PWM5DCH       | 39Dh | —             |

| 01Eh | -                    | 09Eh | ADCON1        | 11Eh | TX1STA1       | 19Eh | _             | 21Eh | —             | 29Eh | —             | 31Eh | PWM5CON       | 39Eh | _             |

| 01Fh | —                    | 09Fh | ADACT         | 11Fh | BAUD1CON1     | 19Fh | —             | 21Fh |               | 29Fh | _             | 31Fh | —             | 39Fh | —             |

| 020h |                      | 0A0h |               | 120h |               | 1A0h |               | 220h |               | 2A0h |               | 320h |               | 3A0h |               |

|      |                      |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

|      |                      |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

|      |                      |      | General       |

|      | <b>.</b> .           |      | Purpose       |

|      | General              |      | Register      |

|      | Purpose<br>Register  |      | 80 Bytes      |

|      | 96 Bytes             |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

|      | 30 Dytes             |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

|      |                      | 0EFh |               | 16Fh |               | 1EFh |               | 26Fh |               | 2EFh |               | 36Fh |               | 3EFh |               |

|      |                      | 0F0h | Common RAM    | 170h | Common RAM    | 1F0h | Common RAM    | 270h | Common RAM    | 2F0h | Common RAM    | 370h | Common RAM    | 3F0h | Common RAM    |

|      |                      |      | Accesses      |

| 07Fh |                      | 0FFh | 70h-7Fh       | 17Fh | 70h-7Fh       | 1FFh | 70h-7Fh       | 27Fh | 70h-7Fh       | 2FFh | 70h-7Fh       | 37Fh | 70h-7Fh       | 3FFh | 70h-7Fh       |

Note 1: Unimplemented locations read as '0'.

2: Present only in PIC16(L)F15375/76/85/86.

3: Present only in PIC16(L)F15385/86.

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

|                     |                       |               | <b>NEOIOTEN</b> |       | Brance      |             | ,                     |                            |   |         |         |

|---------------------|-----------------------|---------------|-----------------|-------|-------------|-------------|-----------------------|----------------------------|---|---------|---------|

| Address             | Name                  | Bit 7         | Bit 6           | Bit 5 | Bit 4       | Bit 3       | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |   |         |         |

| Bank 62 (Continued) |                       |               |                 |       |             |             |                       |                            |   |         |         |

| 1F2Ah               | RD2PPS <sup>(1)</sup> | _             | _               | _     |             |             | RD2PPS<4:0            | >                          |   | 00 0000 | uu uuuu |

| 1F2Bh               | RD3PPS <sup>(1)</sup> | —             | _               | _     |             |             | RD3PPS<4:0            | >                          |   | 00 0000 | uu uuuu |

| 1F2Ch               | RD4PPS <sup>(1)</sup> | —             | _               | _     |             |             | 00 0000               | uu uuuu                    |   |         |         |

| 1F2Dh               | RD5PPS <sup>(1)</sup> | _             | _               | _     |             |             | 00 0000               | uu uuuu                    |   |         |         |

| 1F2Eh               | RD6PPS <sup>(1)</sup> | _             | _               | _     |             |             | RD6PPS<4:0            | >                          |   | 00 0000 | uu uuuu |

| 1F2Fh               | RD7PPS <sup>(1)</sup> | _             | _               | _     |             |             | RD7PPS<4:0            | >                          |   | 00 0000 | uu uuuu |

| 1F30h               | RE0PPS                | _             | _               | _     |             |             | RD5PPS<4:0            | >                          |   | 00 0000 | uu uuuu |

| 1F31h               | RE1PPS                | _             | _               | _     |             | RD6PPS<4:0> |                       |                            |   |         | uu uuuu |

| 1F32h               | RE2PPS                | _             | _               | _     | RD7PPS<4:0> |             |                       |                            |   | 00 0000 | uu uuuu |

| 1F33h<br><br>1F37h  | _                     | Unimplemented |                 |       |             |             |                       | _                          | _ |         |         |

© 2016 Microchip Technology Inc.

Legend: x = unknown, u = unchanged, g = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note 1: Present only on PIC16(L)F15375/76/85/86.

#### 4.4 PCL and PCLATH

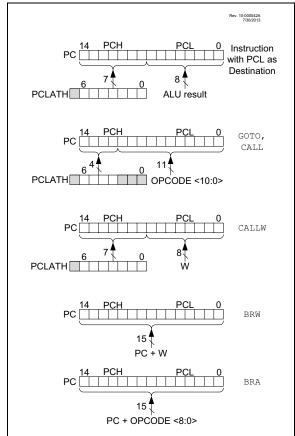

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-4 shows the five situations for the loading of the PC.

FIGURE 4-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 4.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 4.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 4.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 + the signed value of the operand of the BRA instruction.

### 5.2 Register Definitions: Configuration Words

| REGISTER          | 5-1: CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NFIGURATIO                                                                                        | N WORD 1:                                                                          | OSCILLATO                                                                 | RS                             |                                             |                   |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------|---------------------------------------------|-------------------|--|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/P-1                                                                                             | U-1                                                                                | R/P-1                                                                     | U-1                            | U-1                                         | R/P-1             |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FCMEN                                                                                             | _                                                                                  | CSWEN                                                                     | _                              | _                                           | CLKOUTEN          |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 13                                                                                            |                                                                                    |                                                                           |                                |                                             | bit 8             |  |

| 11.1              | R/P-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/P-1                                                                                             | R/P-1                                                                              | 11.1                                                                      | R/P-1                          | R/P-1                                       | R/P-1             |  |

| U-1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                   |                                                                                    | U-1                                                                       |                                |                                             |                   |  |

|                   | RSTOSC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RSTOSC1                                                                                           | RSTOSC0                                                                            | —                                                                         | FEXTOSC2                       | FEXTOSC1                                    | FEXTOSC0          |  |

| bit 7             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                   |                                                                                    |                                                                           |                                |                                             | bit (             |  |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| R = Readable      | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P = Programma                                                                                     | able bit                                                                           | x = Bit is unkno                                                          | own                            | U = Unimpleme<br>'1'                        | nted bit, read as |  |

| '0' = Bit is clea | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                  |                                                                                    | W = Writable b                                                            | it                             | n = Value when blank or after Bulk<br>Erase |                   |  |

| bit 13            | FCMEN: Fail-<br>1 = FSCM tir<br>0 = FSCM tir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                   | or Enable bit                                                                      |                                                                           |                                |                                             |                   |  |

| bit 12            | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 11            | 1 = Writing to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | k Switch Enable<br>NOSC and NDI<br>C and NDIV bits                                                | / is allowed                                                                       | ged by user soft                                                          | ware                           |                                             |                   |  |

| bit 10-9          | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 8             | If FEXTOSC =<br>1 = CLKOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clock Out Enable<br><u>EC (high, mid or</u><br>function is disable<br>function is enable<br>pred. | <u>low) or Not En</u><br>ed; I/O or oscill                                         | ator function on (                                                        |                                |                                             |                   |  |

| bit 7             | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 6-4           | This value is t           111 =         EXTC           110 =         HFIN           101 =         LFIN           100 =         SOSC           011 =         Reserved           010 =         EXTC           001 =         EXTC           001 =         EXTC                                                                                                                                                                                                                                                                                                                                                             | OSC operating per<br>TOSC with HFFR<br>TOSC                                                       | value for COSC<br>FEXTOSC bits<br>Q = 3 ' b010<br>with EXTOSC of<br>with EXTOSC of | and selects the<br>(device manufa<br>pperating per FE<br>pperating per FE | cturing default)<br>XTOSC bits | ed by user softwa                           | re.               |  |

| bit 3             | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 2-0           | Unimplemented: Read as '1'<br>FEXTOSC<2:0>:FEXTOSC External Oscillator Mode Selection bits<br>111 = EC (External Clock) above 8 MHz; PFM set to high power (device manufacturing default)<br>100 = EC (External Clock) for 100 kHz to 8 MHz; PFM set to medium power<br>101 = EC (External Clock) below 100 kHz<br>100 = Oscillator not enabled<br>011 = Reserved (do not use)<br>010 = HS (Crystal oscillator) above 4 MHz; PFM set to high power<br>001 = XT (Crystal oscillator) above 100 kHz, below 4 MHz; PFM set to medium power<br>000 = LP (Crystal oscillator) optimized for 32.768 kHz; PFM set to low power |                                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

#### REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

#### 10.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) of the PIEx[y] registers for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIEx registers)

The PIR1, PIR2, PIR3, PIR4, PIR5, PIR6, and PIR7 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 10.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupts operation, refer to its peripheral chapter.

| Note 1: | Individual interrupt flag bits are set, regardless of the state of any other enable bits.                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| 2:      | All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced |

when the GIE bit is set again.

#### 10.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The interrupt is sampled during Q1 of the instruction cycle. The actual interrupt latency then depends on the instruction that is executing at the time the interrupt is detected. See Figure 10-2 and Figure 10-3 for more details.

# PIC16(L)F15356/75/76/85/86

| R/W-0/0          | R/W-0/0                                                           | R/W-0/0                             | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0     |

|------------------|-------------------------------------------------------------------|-------------------------------------|-----------------|-----------------|------------------|----------|-------------|

| RC2IE            | TX2IE                                                             | RC1IE                               | TX1IE           | BCL2IE          | SSP2IE           | BCL1IE   | SSP1IE      |

| bit 7            |                                                                   |                                     | I               |                 |                  |          | bit (       |

| Legend:          |                                                                   |                                     |                 |                 |                  |          |             |

| R = Readable     | bit                                                               | W = Writable                        | bit             | U = Unimpler    | mented bit, read | l as '0' |             |

| u = Bit is unch  | nanged                                                            | x = Bit is unkr                     | nown            | •               | at POR and BO    |          | ther Resets |

| '1' = Bit is set | -                                                                 | '0' = Bit is cle                    | ared            |                 |                  |          |             |

|                  |                                                                   |                                     |                 |                 |                  |          |             |

| bit 7            | RC2IE: USA                                                        | RT Receive Inte                     | errupt Enable   | bit             |                  |          |             |

|                  |                                                                   | the USART rec                       |                 |                 |                  |          |             |

|                  |                                                                   | the USART rec                       | •               |                 |                  |          |             |

| bit 6            |                                                                   | RT Transmit Inte                    | •               |                 |                  |          |             |

|                  |                                                                   | the USART tra<br>the USART tra      |                 |                 |                  |          |             |

| bit 5            |                                                                   | RT Receive Inte                     | •               |                 |                  |          |             |

| bit 0            |                                                                   | the USART rec                       | •               |                 |                  |          |             |

|                  |                                                                   | the USART rec                       |                 |                 |                  |          |             |

| bit 4            | TX1IE: USAF                                                       | RT Transmit Inte                    | errupt Enable   | bit             |                  |          |             |

|                  | 1 = Enables                                                       | the USART tra                       | nsmit interrup  | t               |                  |          |             |

|                  | 0 = Disables                                                      | the USART tra                       | insmit interrup | ot              |                  |          |             |

| bit 3            |                                                                   | SP2 Bus Collisi                     |                 |                 |                  |          |             |

|                  |                                                                   | us Collision inte                   |                 |                 |                  |          |             |

| hit O            |                                                                   | us Collision inte                   | •               |                 | abla bit         |          |             |

| bit 2            |                                                                   | chronous Seria<br>us collision Inte |                 | z) interrupt En |                  |          |             |

|                  |                                                                   | the MSSP Inte                       |                 |                 |                  |          |             |

| bit 1            |                                                                   | SP1 Bus Collisi                     | •               | nable bit       |                  |          |             |

|                  |                                                                   | us collision inte                   |                 |                 |                  |          |             |

|                  | 0 = MSSP bus collision interrupt disabled                         |                                     |                 |                 |                  |          |             |

| bit 0            | it 0 SSP1IE: Synchronous Serial Port (MSSP1) Interrupt Enable bit |                                     |                 |                 |                  |          |             |

|                  |                                                                   | the MSSP inter                      |                 |                 |                  |          |             |

|                  | 0 = Disables                                                      | the MSSP inte                       | rrupt           |                 |                  |          |             |

|                  |                                                                   |                                     |                 |                 |                  |          |             |

| Note: Bit        | PEIE of the IN                                                    |                                     | must bo         |                 |                  |          |             |

#### REGISTER 10-5: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by PIE1-PIE7.

#### 11.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-on-Interrupt bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 11-1, the interrupt occurs during the  $2^{nd}$  instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-On-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

#### 11.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0). If the SLEEP instruction is executed while the IDLEN bit is set (IDLEN = 1), the CPU will enter the IDLE mode (Section 11.2.3 "Low-Power Sleep Mode").

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The  $\overline{PD}$  bit of the STATUS register is cleared

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set

- 4. CPU Clock and System Clock

- 5. 31 kHz LFINTOSC, HFINTOSC and SOSC are unaffected and peripherals using them may continue operation in Sleep.

- 6. ADC is unaffected if the dedicated FRC oscillator is selected the conversion will be left abandoned if FOSC is selected and ADRES will have an incorrect value

- 7. I/O ports maintain the status they had before Sleep was executed (driving high, low, or high-impedance). This does not apply in the case of any asynchronous peripheral which is active and may affect the I/O port value

- 8. Resets other than WDT are not affected by Sleep mode

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or VSS externally to avoid switching currents caused by floating inputs.

Any module with a clock source that is not Fosc can be enabled. Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module", Section 18.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 11.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled.

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled.

- 5. Any external interrupt.

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 8.12 "Memory Execution Violation**".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSC<7:0>: Analog Select between Analog or Digital Function on Pins RC<7:0>, respectively<sup>(1)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 14-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### 14.9 Register Definitions: PORTD

#### REGISTER 14-25: PORTD: PORTD REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-----------------------------------------|---------|-------------------------------------------------------|------------------------------------|---------|---------|---------|---------|

| RD7                                     | RD6     | RD5                                                   | RD4                                | RD3     | RD2     | RD1     | RD0     |

| bit 7                                   |         |                                                       |                                    |         |         |         | bit 0   |

|                                         |         |                                                       |                                    |         |         |         |         |

| Legend:                                 |         |                                                       |                                    |         |         |         |         |

| R = Readable bit W = Writable bit       |         |                                                       | U = Unimplemented bit, read as '0' |         |         |         |         |

| u = Bit is unchanged x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |         |

| '1' = Bit is set                        |         | '0' = Bit is clea                                     | ared                               |         |         |         |         |

bit 7-0 **RD<7:0>**: PORTD General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

#### REGISTER 14-26: TRISD: PORTD TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISD<7:0>: PORTD Tri-State Control bits

1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

#### REGISTER 14-27: LATD: PORTD DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATD<7:0>: PORTD Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

| Quitout Signal        | RxyPPS                   | Remappable to Pins of PORTx           PIC16(L)F15375/76 |       |       |       |       |  |  |

|-----------------------|--------------------------|---------------------------------------------------------|-------|-------|-------|-------|--|--|

| Output Signal<br>Name | RxyPP5<br>Register Value |                                                         |       |       |       |       |  |  |

|                       | -                        | PORTA                                                   | PORTB | PORTC | PORTD | PORTE |  |  |

| CLKR                  | 0x1B                     |                                                         | •     | •     |       |       |  |  |

| NCO1OUT               | 0x1A                     | •                                                       |       |       | •     |       |  |  |

| TMR0                  | 0x19                     |                                                         | •     | •     |       |       |  |  |

| SDO2/SDA2             | 0x18                     |                                                         | •     |       | •     |       |  |  |

| SCK2/SCL2             | 0x17                     |                                                         | •     |       | •     |       |  |  |

| SDO1/SDA1             | 0x16                     |                                                         | •     | •     |       |       |  |  |

| SCK1/SCL1             | 0x15                     |                                                         | •     | •     |       |       |  |  |

| C2OUT                 | 0x14                     | ٠                                                       |       |       |       | ٠     |  |  |

| C1OUT                 | 0x13                     | ٠                                                       |       |       | •     |       |  |  |

| DT2                   | 0x12                     |                                                         | •     |       | •     |       |  |  |

| TX2/CK2               | 0x11                     |                                                         | •     |       | ٠     |       |  |  |

| DT1                   | 0x10                     |                                                         | •     | •     |       |       |  |  |

| TX1/CK1               | 0x0F                     |                                                         | •     | •     |       |       |  |  |

| PWM6OUT               | 0x0E                     | ٠                                                       |       |       | ٠     |       |  |  |

| PWM5OUT               | 0x0D                     | ٠                                                       |       | •     |       |       |  |  |

| PWM4OUT               | 0x0C                     |                                                         | •     |       | •     |       |  |  |

| PWM3OUT               | 0x0B                     |                                                         | •     |       | ٠     |       |  |  |

| CCP2                  | 0x0A                     |                                                         | •     | •     |       |       |  |  |

| CCP1                  | 0x09                     |                                                         | •     | •     |       |       |  |  |

| CWG1D                 | 0x08                     |                                                         | •     |       | •     |       |  |  |

| CWG1C                 | 0x07                     |                                                         | •     |       | •     |       |  |  |

| CWG1B                 | 0x06                     |                                                         | •     |       | •     |       |  |  |

| CWG1A                 | 0x05                     |                                                         | •     | •     |       |       |  |  |

| CLC4OUT               | 0x04                     |                                                         | •     |       | •     |       |  |  |

| CLC3OUT               | 0x03                     |                                                         | •     |       | •     |       |  |  |

| CLC2OUT               | 0x02                     | •                                                       |       | •     |       |       |  |  |

| CLC1OUT               | 0x01                     | •                                                       |       | •     |       |       |  |  |

#### TABLE 15-6: PPS OUTPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15375/76)

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u     | R/W-0/u | R/W-0/u |

|-------|-----|-----|---------|---------|-------------|---------|---------|

| —     | —   | _   |         |         | RxyPPS<4:0> | •       |         |

| bit 7 |     |     |         |         |             |         | bit 0   |

|       |     |     |         |         |             |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 4-0 **RxyPPS<4:0>:** Pin Rxy Output Source Selection bits See Table 15-5 through Table 15-7.

Note 1: TRIS control is overridden by the peripheral as required.

#### REGISTER 15-3: PPSLOCK: PPS LOCK REGISTER

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |

|-------------|-----|-----|-----|-----|-----|-----|-----------|

| —           | _   |     | —   | —   | —   | —   | PPSLOCKED |

| bit 7 bit 0 |     |     |     |     |     |     |           |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1= PPS is locked. PPS selections can not be changed.

0= PPS is not locked. PPS selections can be changed.

© 2016 Microchip Technology Inc.

### 17.0 INTERRUPT-ON-CHANGE

All pins on ports A, B and C and lower four bits of PORTE can be configured to operate as Interrupt-on-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual pin, or combination of pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 17-1 is a block diagram of the IOC module.

#### 17.1 Enabling the Module

To allow individual pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 17.2 Individual Pin Configuration

For each pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting the associated bits in both of the IOCxP and IOCxN registers.

#### 17.3 Interrupt Flags

The bits located in the IOCxF registers are status flags that correspond to the interrupt-on-change pins of each port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIR0 register reflects the status of all IOCxF bits.

#### 17.3.1 CLEARING INTERRUPT FLAGS

The individual status flags, (IOCxF register bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 17-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

#### 17.4 Operation in Sleep

The interrupt-on-change interrupt event will wake the device from Sleep mode, if the IOCIE bit is set.

#### **REGISTER 20-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

|                  |         |                 |         | •              |                  |                  |              |

|------------------|---------|-----------------|---------|----------------|------------------|------------------|--------------|

| R/W-x/u          | R/W-x/u | R/W-x/u         | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|                  |         |                 | ADRE    | S<9:2>         |                  |                  |              |

| bit 7            |         |                 |         |                |                  |                  | bit 0        |

|                  |         |                 |         |                |                  |                  |              |

| Legend:          |         |                 |         |                |                  |                  |              |

| R = Readable I   | bit     | W = Writable    | bit     | U = Unimpler   | mented bit, read | d as '0'         |              |

| u = Bit is uncha | anged   | x = Bit is unkr | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

'1' = Bit is set

#### **REGISTER 20-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

'0' = Bit is cleared

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u R/W-x/u R |   | R/W-x/u R/W-x/u |   | R/W-x/u |

|------------|---------|---------|-------------------|---|-----------------|---|---------|

| ADRES<1:0> |         | —       | —                 | — | —               | — | —       |

| bit 7      |         |         |                   |   |                 |   | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ADRES<1:0>**: ADC Result Register bits Lower two bits of 10-bit conversion result

Lower two bits of 10-bit conversion

bit 5-0 Reserved: Do not use.

© 2016 Microchip Technology Inc.

#### 21.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected.

#### 21.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT1/2 pins.

- The DAC1R<4:0> range select bits are cleared.

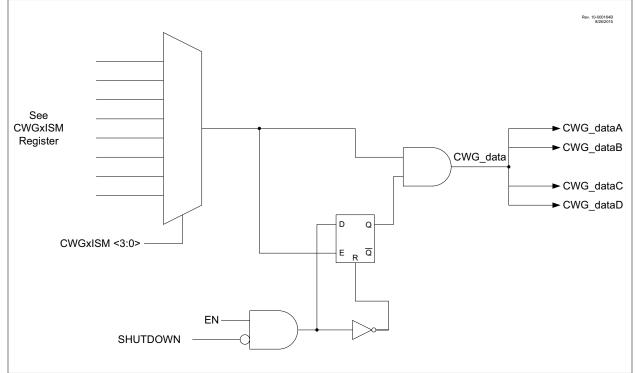

#### 30.1.4 STEERING MODES

In Steering modes, the data input can be steered to any or all of the four CWG output pins. In Synchronous Steering mode, changes to steering selection registers take effect on the next rising input.

In Non-Synchronous mode, steering takes effect on the next instruction cycle. Additional details are provided in **Section 30.9 "CWG Steering Mode"**.

#### 30.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWG1CLKCON register.

# PIC16(L)F15356/75/76/85/86

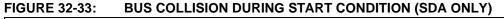

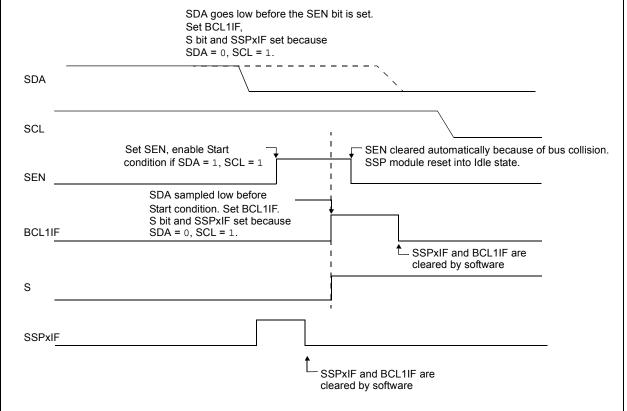

## 32.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 32-33).

- b) SCL is sampled low before SDA is asserted low (Figure 32-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- the BCL1IF flag is set and

- the MSSP module is reset to its Idle state (Figure 32-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 32-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### 33.3 EUSART Baud Rate Generator (BRG)