Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15356-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | Name | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0     Value on:<br>POR, BOR     Value on:<br>MCLR |  |  |  |  |  |  |  |  |

|-------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 3ank 21-59                                      |      |                                                                                                                             |  |  |  |  |  |  |  |  |

| CPU CORE REGISTERS; see Table 4-3 for specifics |      |                                                                                                                             |  |  |  |  |  |  |  |  |

| x0Ch/<br>x8Ch<br><br>x1Fh/<br>x9Fh              |      |                                                                                                                             |  |  |  |  |  |  |  |  |

| Address | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3            | Bit 2     | Bit 1       | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|----------|----------|----------|---------------|------------------|-----------|-------------|----------|-----------------------|----------------------------|

| Bank 60 |          |          |          |          |               |                  |           |             |          |                       |                            |

|         |          |          |          | CPU COF  | RE REGISTERS; | see Table 4-3 fo | specifics |             |          |                       |                            |

| 1E0Ch   | _        |          |          |          | Unimpler      | mented           |           |             |          | —                     | _                          |

| 1E0Dh   | _        |          |          |          | Unimpler      | nented           |           |             |          | _                     | _                          |

| 1E0Eh   | _        |          |          |          | Unimpler      | nented           |           |             |          | —                     | _                          |

| 1E0Fh   | CLCDATA  | —        | —        | —        | —             | MLC4OUT          | MLC3OUT   | MLC2OUT     | MLC1OUT  | xxxx                  | uuuu                       |

| 1E10h   | CLCCON   | LC1EN    | —        | LC1OUT   | LC1INTP       | LC1INTN          |           | LC1MODE<2:0 | )>       | 0-00 0000             | 0-00 0000                  |

| 1E11h   | CLC1POL  | LC1POL   | —        | —        | —             | LC1G4POL         | LC1G3POL  | LC1G2POL    | LC1G1POL | 0 xxxx                | 0 uuuu                     |

| 1E12h   | CLC1SEL0 |          | _        |          |               | LC1              | 01S<5:0>  |             |          | xx xxxx               | uu uuuu                    |

| 1E13h   | CLC1SEL1 |          | _        |          |               | LC1              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E14h   | CLC1SEL2 |          | _        |          |               | LC1              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E15h   | CLC1SEL3 |          | _        |          |               | LC1              | 04S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E16h   | CLC1GLS0 | LC1G1D4T | LC1G4D3N | LC1G1D3T | LC1G1D3N      | LC1G1D2T         | LC1G1D2N  | LC1G1D1T    | LC1G1D1N | xxxx xxxx             | uuuu uuu                   |

| 1E17h   | CLC1GLS1 | LC1G2D4T | LC1G4D3N | LC1G2D3T | LC1G2D3N      | LC1G2D2T         | LC1G2D2N  | LC1G2D1T    | LC1G2D1N | xxxx xxxx             | uuuu uuu                   |

| 1E18h   | CLC1GLS2 | LC1G3D4T | LC1G4D3N | LC1G3D3T | LC1G3D3N      | LC1G3D2T         | LC1G3D2N  | LC1G3D1T    | LC1G3D1N | xxxx xxxx             | uuuu uuu                   |

| 1E19h   | CLC1GLS3 | LC1G4D4T | LC1G4D3N | LC1G4D3T | LC1G4D3N      | LC1G4D2T         | LC1G4D2N  | LC1G4D1T    | LC1G4D1N | xxxx xxxx             | uuuu uuu                   |

| 1E1Ah   | CLC2CON  | LC2EN    | _        | LC2OUT   | LC2INTP       | LC2INTN          |           | LC2MODE<2:0 | )>       | 0-00 0000             | 0-00 000                   |

| 1E1Bh   | CLC2POL  | LC2POL   | _        | —        | _             | LC2G4POL         | LC2G3POL  | LC2G2POL    | LC2G1POL | 0 xxxx                | 0 uuu                      |

| 1E1Ch   | CLC2SEL0 |          | _        |          |               | LC2              | 01S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Dh   | CLC2SEL1 | _        | _        |          |               | LC2              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Eh   | CLC2SEL2 | _        | _        |          |               | LC2              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Fh   | CLC2SEL3 | _        | _        |          |               | LC2              | 04S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E20h   | CLC2GLS0 | LC2G1D4T | LC2G4D3N | LC2G1D3T | LC2G1D3N      | LC2G1D2T         | LC2G1D2N  | LC2G1D1T    | LC2G1D1N | xxxx xxxx             | uuuu uuu                   |

| 1E21h   | CLC2GLS1 | LC2G2D4T | LC2G4D3N | LC2G2D3T | LC2G2D3N      | LC2G2D2T         | LC2G2D2N  | LC2G2D1T    | LC2G2D1N | xxxx xxxx             | นนนน นนนา                  |

| 1E22h   | CLC2GLS2 | LC2G3D4T | LC2G4D3N | LC2G3D3T | LC2G3D3N      | LC2G3D2T         | LC2G3D2N  | LC2G3D1T    | LC2G3D1N | xxxx xxxx             | uuuu uuu                   |

| 1E23h   | CLC2GLS3 | LC2G4D4T | LC2G4D3N | LC2G4D3T | LC2G4D3N      | LC2G4D2T         | LC2G4D2N  | LC2G4D1T    | LC2G4D1N | xxxx xxxx             | uuuu uuu                   |

| 1E24h   | CLC3CON  | LC3EN    | —        | LC3OUT   | LC3INTP       | LC3INTN          |           | LC3MODE     |          | 0-00 0000             | 0-00 000                   |

| 1E25h   | CLC3POL  | LC3POL   | _        | —        | _             | LC3G4POL         | LC3G3POL  | LC3G2POL    | LC3G1POL | 0 xxxx                | 0 uuu                      |

| 1E26h   | CLC3SEL0 | _        |          |          |               | LC3              | 01S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E27h   | CLC3SEL1 | _        |          |          |               | LC3              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E28h   | CLC3SEL2 | _        |          |          |               | LC3              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E29h   | CLC3SEL3 | _        | _        |          |               | LC3              | 04S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E2Ah   | CLC3GLS0 | LC3G1D4T | LC3G4D3N | LC3G1D3T | LC3G1D3N      | LC3G1D2T         | LC3G1D2N  | LC3G1D1T    | LC3G1D1N | xxxx xxxx             | uuuu uuu                   |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

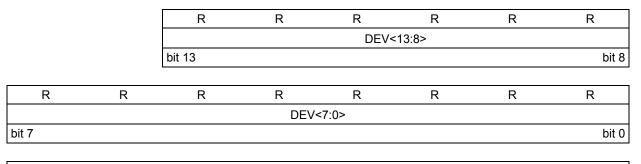

#### 5.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. These locations can also be read from the NVMCON register.

#### 5.7 Register Definitions: Device and Revision

#### REGISTER 5-6: DEVID: DEVICE ID REGISTER

#### Legend:

R = Readable bit

'1' = Bit is set

bit 13-0 **DEV<13:0>:** Device ID bits

| Device       | DEVID<13:0> Values                 |  |  |  |  |  |  |

|--------------|------------------------------------|--|--|--|--|--|--|

| PIC16F15356  | 11 0000 1011 0000 ( <b>30B0h</b> ) |  |  |  |  |  |  |

| PIC16LF15356 | 11 0000 1011 0001 ( <b>30B1h</b> ) |  |  |  |  |  |  |

| PIC16F15375  | 11 0000 1011 0010 ( <b>30B2h</b> ) |  |  |  |  |  |  |

| PIC16LF15375 | 11 0000 1011 0011 ( <b>30B3h</b> ) |  |  |  |  |  |  |

| PIC16F15376  | 11 0000 1011 0100 ( <b>30B4h</b> ) |  |  |  |  |  |  |

| PIC16LF15376 | 11 0000 1011 0101 ( <b>30B5h</b> ) |  |  |  |  |  |  |

| PIC16F15385  | 11 0000 1011 0110 ( <b>30B6h</b> ) |  |  |  |  |  |  |

| PIC16LF15385 | 11 0000 1011 0111 ( <b>30B7h</b> ) |  |  |  |  |  |  |

| PIC16F15386  | 11 0000 1011 1000 ( <b>30B8h</b> ) |  |  |  |  |  |  |

| PIC16LF15386 | 11 0000 1011 1001 ( <b>30B9h</b> ) |  |  |  |  |  |  |

'0' = Bit is cleared

#### 8.4 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) is an important part of the Reset subsystem. Refer to Figure 8-1 to see how the BOR and LPBOR interact with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset.

#### 8.4.1 ENABLING LPBOR

The LPBOR is controlled by the  $\overrightarrow{LPBOR}$  bit of the Configuration Word (Register 5-1). When the device is erased, the LPBOR module defaults to disabled.

#### 8.4.2 LPBOR MODULE OUTPUT

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The same bit is set for either the BOR or the LPBOR (refer to Register 8-3). This signal is OR'd with the output of the BOR module to provide the generic BOR signal, which goes to the PCON register and to the power control block. Refer to Figure 8-1 for the OR gate connections of the BOR and LPBOR Reset signals, which eventually generates one common BOR Reset.

## 8.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 8-2).

TABLE 8-2:

MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

#### 8.5.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up. Refer to **Section 2.3 "Master Clear (MCLR) Pin"** for recommended MCLR connections.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

**Note:** A Reset does not drive the MCLR pin low.

#### 8.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 14.1 "I/O Priorities"** for more information.

#### 8.6 Windowed Watchdog Timer (WWDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period and the window is open. The TO and PD bits in the STATUS register and the WDT bit in PCON are changed to indicate a WDT Reset caused by the timer overflowing, and WDTWV bit in the PCON register is changed to indicate a WDT Reset caused by a window violation. See **Section 12.0 "Windowed Watchdog Timer (WWDT)"** for more information.

#### 8.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 8-4 for default conditions after a RESET instruction has occurred.

#### 8.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 4.5.2** "**Overflow/Underflow Reset**" for more information.

#### 8.9 Programming Mode Exit

Upon exit of In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) mode, the device will behave as if a POR had just occurred (the device does not reset upon run time self-programming/erase operations).

#### 8.10 Power-up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\mathsf{PWRTE}}$  bit of the Configuration Words.

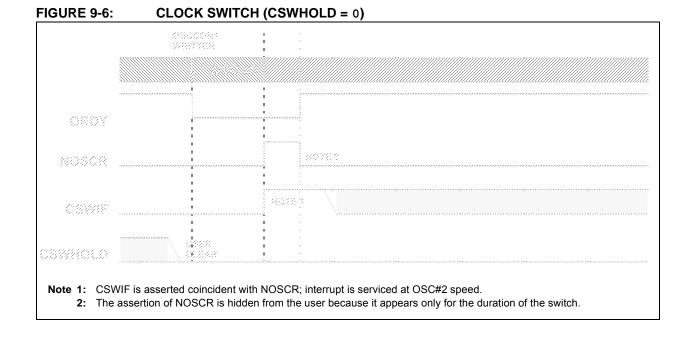

The Power-up Timer provides a nominal 64 ms time out on POR or Brown-out Reset. The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in the Configuration Words. The Power-up Timer starts after the release of the POR and BOR. For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*" (DS00607). Changing the clock post-divider without changing the clock source (e.g., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

#### 9.3.2 PLL INPUT SWITCH

Switching between the PLL and any non-PLL source is managed as described above. The input to the PLL is established when NOSC selects the PLL, and maintained by the COSC setting.

When NOSC and COSC select the PLL with different input sources, the system continues to run using the COSC setting, and the new source is enabled per NOSC. When the new oscillator is ready (and CSWHOLD = 0), system operation is suspended while the PLL input is switched and the PLL acquires lock.

Note: If the PLL fails to lock, the FSCM will trigger.

#### 9.3.3 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

#### 10.3 Interrupts During Sleep

Interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 11.0 "Power-Saving Operation Modes"** for more details.

#### 10.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. Refer to Figure 10-3. This interrupt is enabled by setting the INTE bit of the PIE0 register. The INTEDG bit of the INTCON register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the PIR0 register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

#### 10.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

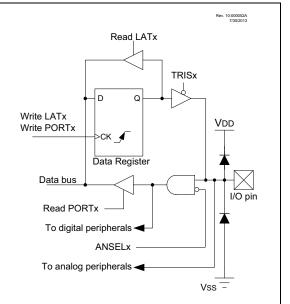

# 14.0 I/O PORTS

# TABLE 14-1:PORT AVAILABILITY PER<br/>DEVICE

| Device            |   | PORTB | PORTC | PORTD | PORTE | PORTF |

|-------------------|---|-------|-------|-------|-------|-------|

| PIC16(L)F15356    | • | •     | •     |       | •     |       |

| PIC16(L)F15375/76 | ٠ | ٠     | ٠     | ٠     | ٠     |       |

| PIC16(L)F15385/86 | ٠ | ٠     | •     | ٠     | ٠     | •     |

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 14-1.

#### FIGURE 14-1: GENERIC I/O PORT OPERATION

#### 14.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 15.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

#### 14.2 PORTA Registers

#### 14.2.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 14-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 14.2.8 shows how to initialize PORTA.

Reading the PORTA register (Register 14-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The PORT data latch LATA (Register 14-3) holds the output port data, and contains the latest value of a LATA or PORTA write.

#### EXAMPLE 14-1: INITIALIZING PORTA

| ; initia | ports are in | illustrates<br>ORTA register. The<br>itialized in the same |

|----------|--------------|------------------------------------------------------------|

| BANKSEL  | PORTA        | ;                                                          |

| CLRF     | PORTA        | ;Init PORTA                                                |

| BANKSEL  | LATA         | ;Data Latch                                                |

| CLRF     | LATA         | ;                                                          |

| BANKSEL  | ANSELA       | ;                                                          |

| CLRF     | ANSELA       | ;digital I/O                                               |

| BANKSEL  | TRISA        | ;                                                          |

| MOVLW    | B'00111000'  | ;Set RA<5:3> as inputs                                     |

| MOVWF    | TRISA        | ;and set RA<2:0> as                                        |

|          |              | ;outputs                                                   |

#### 14.2.2 DIRECTION CONTROL

The TRISA register (Register 14-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.2.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 14-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

#### 14.2.4 SLEW RATE CONTROL

The SLRCONA register (Register 14-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.2.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 14-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

| Note: | Changing the input threshold selection should be performed while all peripheral |

|-------|---------------------------------------------------------------------------------|

|       | modules are disabled. Changing the                                              |

|       | threshold level during the time a module is                                     |

|       | active may inadvertently generate a                                             |

|       | transition associated with an input pin,                                        |

|       | regardless of the actual voltage level on                                       |

|       | that pin.                                                                       |

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSF7   | ANSF6   | ANSF5   | ANSF4   | ANSF3   | ANSF2   | ANSF1   | ANSF0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSF<7:0>**: Analog Select between Analog or Digital Function on Pins RF<7:0>, respectively<sup>(1)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 14-45: WPUF: WEAK PULL-UP PORTF REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUF7   | WPUF6   | WPUF5   | WPUF4   | WPUF3   | WPUF2   | WPUF1   | WPUF0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUF<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### **30.0 COMPLEMENTARY WAVEFORM** GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous ECCP functions.

The CWG has the following features:

- · Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- Output polarity control

- Output steering

- Synchronized to rising event

- Immediate effect

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

The CWG modules available are shown in Table 30-1.

#### TABLE 30-1: AVAILABLE CWG MODULES

| Device                     | CWG1 |

|----------------------------|------|

| PIC16(L)F15356/75/76/85/86 | •    |

#### 30.1 Fundamental Operation

The CWG module can operate in six different modes, as specified by MODE of the CWG1CON0 register:

- Half-Bridge mode (Figure 30-9)

- Push-Pull mode (Figure 30-2)

- Full-Bridge mode, Forward (Figure 30-3)

- Full-Bridge mode, Reverse (Figure 30-3)

- Steering mode (Figure 30-10)

- Synchronous Steering mode (Figure 30-11)

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. Thus, all output modes support auto-shutdown, which is covered in **30.10** "Auto-Shutdown".

#### 30.1.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 30-9. A non-overlap (dead-band) time is inserted between the two outputs as described in **Section 30.5 "Dead-Band Control"**.

The unused outputs CWG1C and CWG1D drive similar signals, with polarity independently controlled by the POLC and POLD bits of the CWG1CON1 register, respectively.

#### 30.1.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 30-2. This alternation creates the push-pull effect required for driving some transformer-based power supply designs.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWG1A.

The unused outputs CWG1C and CWG1D drive copies of CWG1A and CWG1B, respectively, but with polarity controlled by the POLC and POLD bits of the CWG1CON1 register, respectively.

#### 30.1.3 FULL-BRIDGE MODES

In Forward and Reverse Full-Bridge modes, three outputs drive static values while the fourth is modulated by the input data signal. In Forward Full-Bridge mode, CWG1A is driven to its active state, CWG1B and CWG1C are driven to their inactive state, and CWG1D is modulated by the input signal. In Reverse Full-Bridge mode, CWG1C is driven to its active state, CWG1A and CWG1D are driven to their inactive states, and CWG1B is modulated by the input signal. In Full-Bridge mode, the dead-band period is used when there is a switch from forward to reverse or vice-versa. This dead-band control is described in Section 30.5 "Dead-Band Control", with additional details in Section 30.6 "Rising Edge and Reverse Dead Band" and Section 30.7 "Falling Edge and Forward Dead Band".

The mode selection may be toggled between forward and reverse toggling the MODE<0> bit of the CWG1CON0 while keeping MODE<2:1> static, without disabling the CWG module.

| R/W-0/0          | R/W-0/0             | R/W-0/0                           | R/W-0/0          | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |

|------------------|---------------------|-----------------------------------|------------------|---------------------|---------------------|---------------------|---------------------|

| OVRD             | OVRC                | OVRB                              | OVRA             | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |

| bit 7            |                     |                                   |                  |                     |                     |                     | bit 0               |

|                  |                     |                                   |                  |                     |                     |                     |                     |

| Legend:          |                     |                                   |                  |                     |                     |                     |                     |

| R = Readable     |                     | W = Writable                      | bit              | U = Unimpler        | mented bit, read    | as '0'              |                     |

| u = Bit is unch  | anged               | x = Bit is unkr                   | nown             | -n/n = Value        | at POR and BOF      | R/Value at all o    | ther Resets         |

| '1' = Bit is set |                     | '0' = Bit is cle                  | ared             | q = Value de        | pends on conditi    | on                  |                     |

|                  |                     |                                   |                  |                     |                     |                     |                     |

| bit 7            | OVRD: Steeri        | ng Data D bit                     |                  |                     |                     |                     |                     |

| bit 6            | OVRC: Steeri        | ng Data C bit                     |                  |                     |                     |                     |                     |

| bit 5            | OVRB: Steeri        | ng Data B bit                     |                  |                     |                     |                     |                     |

| bit 4            | OVRA: Steeri        | ng Data A bit                     |                  |                     |                     |                     |                     |

| bit 3            | STRD: Steeri        | ng Enable D bi                    | t <sup>(2)</sup> |                     |                     |                     |                     |

|                  |                     | output has the<br>output is assig | _                |                     | polarity control    | from POLD bit       |                     |

| bit 2            |                     | ng Enable C bi                    |                  |                     |                     |                     |                     |

|                  | 1 = CWG1C           | 0                                 | CWG1_data        |                     | polarity control    | from POLC bit       |                     |

| bit 1            |                     | ng Enable B bi                    |                  |                     |                     |                     |                     |

|                  | 1 = CWG1B           | •                                 | CWG1_data        |                     | polarity control    | from POLB bit       |                     |

| bit 0            | STRA: Steeri        | ng Enable A bi                    | t(2)             |                     |                     |                     |                     |

|                  |                     | output has the output is assig    | _                |                     | polarity control    | from POLA bit       |                     |

| Note 1: Th       | ne bits in this reg | gister apply onl                  | ly when MOD      | E<2:0> = 00x.       |                     |                     |                     |

# REGISTER 30-7: CWG1STR: CWG1 STEERING CONTROL REGISTER<sup>(1)</sup>

2: This bit is effectively double-buffered when MODE<2:0> = 001.

#### 32.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 32.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 32-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

#### 32.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPxCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPxCON1<3:0> =<br>0100), the SPI module will reset if the $\overline{SS}$<br>pin is set to VDD. |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable SS pin control.                                                                                       |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.                                                                                    |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

PIC16(L)F15356/75/76/85/86

#### 33.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 9.2.2.2** "Internal Oscillator Frequency **Adjustment**" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 33.3.1** "**Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

# PIC16(L)F15356/75/76/85/86

© 2016 Microchip Technology Inc.

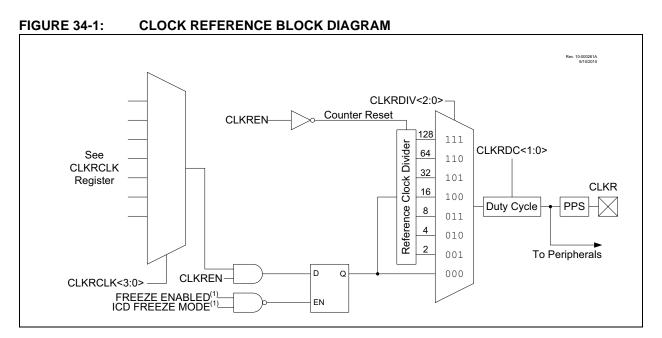

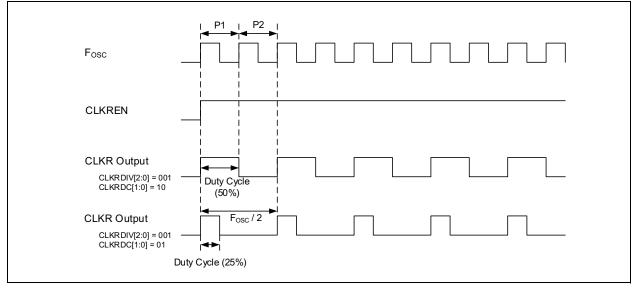

| R/W-0/0                                                 | U-0                                                                          | U-0                                                                         | R/W-0/0       | R/W-0/0          | R/W-0/0       | R/W-0/0          | R/W-0/0      |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------|------------------|---------------|------------------|--------------|--|--|--|

| CLKREN                                                  | _                                                                            | —                                                                           | CLKR          | DC<1:0>          | (             | CLKRDIV<2:0>     |              |  |  |  |

| bit 7                                                   |                                                                              |                                                                             |               |                  |               |                  | bit C        |  |  |  |

| Legend:                                                 |                                                                              |                                                                             |               |                  |               |                  |              |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit |                                                                              |                                                                             |               | nented bit, read | l as '0'      |                  |              |  |  |  |

| u = Bit is unch                                         | anged                                                                        | x = Bit is unkr                                                             | iown          | -n/n = Value a   | at POR and BO | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set                                        |                                                                              | '0' = Bit is clea                                                           | ared          |                  |               |                  |              |  |  |  |

|                                                         |                                                                              |                                                                             |               |                  |               |                  |              |  |  |  |

| bit 7                                                   | CLKREN: Reference Clock Module Enable bit                                    |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         | 1 = Referen                                                                  | ce clock modul                                                              | e enabled     |                  |               |                  |              |  |  |  |

|                                                         | 0 = Referen                                                                  | ce clock modul                                                              | e is disabled |                  |               |                  |              |  |  |  |

| bit 6-5                                                 | Unimplemen                                                                   | ted: Read as '                                                              | כי            |                  |               |                  |              |  |  |  |

| bit 4-3                                                 | CLKRDC<1:0>: Reference Clock Duty Cycle bits <sup>(1)</sup>                  |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         | 11 = Clock outputs duty cycle of 75%                                         |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         | 10 = Clock outputs duty cycle of 50%                                         |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         | 01 = Clock outputs duty cycle of 25%<br>00 = Clock outputs duty cycle of 0%  |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         |                                                                              |                                                                             |               |                  |               |                  |              |  |  |  |

| bit 2-0                                                 | CLKRDIV<2:0>: Reference Clock Divider bits                                   |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         | 111 = Base clock value divided by 128                                        |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         | 110 = Base clock value divided by 64<br>101 = Base clock value divided by 32 |                                                                             |               |                  |               |                  |              |  |  |  |

|                                                         |                                                                              |                                                                             | ,             |                  |               |                  |              |  |  |  |

|                                                         |                                                                              | 100 = Base clock value divided by 16<br>011 = Base clock value divided by 8 |               |                  |               |                  |              |  |  |  |

|                                                         |                                                                              | lock value divid                                                            | •             |                  |               |                  |              |  |  |  |

|                                                         |                                                                              | lock value divid                                                            | led by 2      |                  |               |                  |              |  |  |  |

|                                                         | 000 <b>= Base c</b>                                                          | lock value                                                                  |               |                  |               |                  |              |  |  |  |

#### REGISTER 34-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

**Note 1:** Bits are valid for reference clock divider values of two or larger, the base clock cannot be further divided.

#### TABLE 37-23: SPI MODE REQUIREMENTS

| Standard      | tandard Operating Conditions (unless otherwise stated) |                                          |                                |      |                |           |                                |  |

|---------------|--------------------------------------------------------|------------------------------------------|--------------------------------|------|----------------|-----------|--------------------------------|--|

| Param.<br>No. | Symbol                                                 | Symbol Characteristic                    |                                | Тур† | Max.           | Units     | Conditions                     |  |

| SP70*         | TssL2scH,<br>TssL2scL                                  | SS↓ to SCK↓ or SCK↑ input                | 2.25*Tcy                       | —    | —              | ns        | $\square$                      |  |

| SP71*         | TscH                                                   | SCK input high time (Slave mode)         | Tcy + 20                       | —    | —              | ng        |                                |  |

| SP72*         | TscL                                                   | SCK input low time (Slave mode)          | Tcy + 20                       | —    | _              | ns        |                                |  |

| SP73*         | TDIV2scH,<br>TDIV2scL                                  | Setup time of SDI data input to SCK edge | 100                            | - /  |                | ns        |                                |  |

| SP74*         | TscH2DIL,<br>TscL2DIL                                  | Hold time of SDI data input to SCK edge  | 100                            | -<   |                | <b>AS</b> | >                              |  |

| SP75*         | TDOR                                                   | SDO data output rise time                | _                              | 10   | 25             | ns        | $3.0V \le VDD \le 5.5V$        |  |

|               |                                                        |                                          | - <                            | 25   | \ <b>5</b> 0 < | ns        | $1.8V \le V\text{DD} \le 5.5V$ |  |

| SP76*         | TDOF                                                   | SDO data output fall time                | _                              | 10   | 25             | ns        |                                |  |

| SP77*         | TssH2doZ                                               | SS↑ to SDO output high-impedance         | 10                             |      | 50             | ns        |                                |  |

| SP78*         | TscR                                                   | SCK output rise time                     | $\gamma \neq L$                | -10  | 25             | ns        | $3.0V \le V\text{DD} \le 5.5V$ |  |

|               |                                                        | (Master mode)                            | $\overline{\langle - \rangle}$ | 25   | 50             | ns        | $1.8V \le V\text{DD} \le 5.5V$ |  |

| SP79*         | TscF                                                   | SCK output fall time (Master mode)       | \_\<br>_                       | 10   | 25             | ns        |                                |  |

| SP80*         | TscH2doV,                                              | SDO data output valid after SCK edge     |                                | _    | 50             | ns        | $3.0V \le V\text{DD} \le 5.5V$ |  |

|               | TscL2DoV                                               |                                          | $\sim - \sim$                  | 1 —  | 145            | ns        | $1.8V \le V\text{DD} \le 5.5V$ |  |

| SP81*         | TDOV2sCH,<br>TDOV2sCL                                  | SDO data output setup to SCK edge        |                                | —    | —              | ns        |                                |  |

| SP82*         | TssL2DoV                                               | SDO data output valid after SS↓ edge     | $\searrow$ -                   | _    | 50             | ns        |                                |  |

| SP83*         | TscH2ssH,<br>TscL2ssH                                  | SS ↑ after SCK edge                      | 1.5 TCY + 40                   | —    | —              | ns        |                                |  |

These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16(L)F15356/75/76/85/86

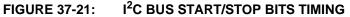

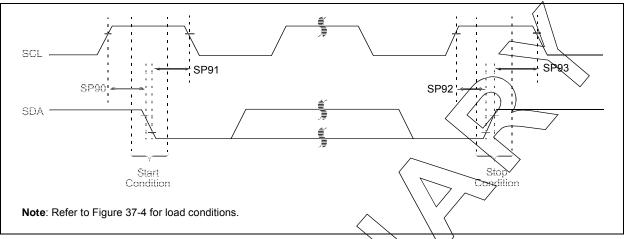

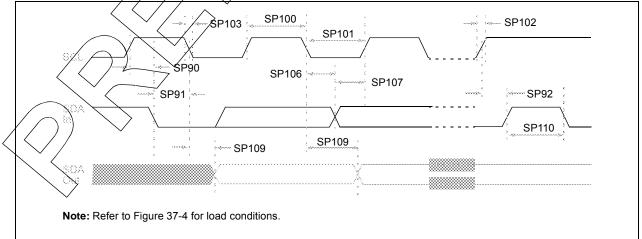

# TABLE 37-24: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Charact         | eristic      | Min. | Тур          | Max. | Units | Conditions                         |

|---------------|---------|-----------------|--------------|------|--------------|------|-------|------------------------------------|

| SP90*         | TSU:STA | Start condition | 100 kHz mode | 4700 | $\checkmark$ | _    | ns    | Only relevant for Repeated Start   |

|               |         | Setup time      | 400 kHz mode | 600  |              | _    |       | condition                          |

| SP91*         | THD:STA | Start condition | 100 kHzmode  | 4000 | _            | _    | ns    | After this period, the first clock |

|               |         | Hold time       | 400 kHz modę | 600  | _            | _    |       | pulse is generated                 |

| SP92*         | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _            | _    | ns    |                                    |

|               |         | Setup time      | 400 kHz mode | 600  | _            | _    |       |                                    |

| SP93          | THD:STO | Stop condition  | 100 kHz mode | 4000 | _            | _    | ns    |                                    |

|               |         | Hold time       | 400 kHz mode | 600  | -            | —    |       |                                    |

These parameters are characterized but not tested.

#### 12C BUS DATA TIMING **FIGURE 37-22:**

## APPENDIX A: DATA SHEET REVISION HISTORY

#### Revision A (12/2016)

Initial release of the document.